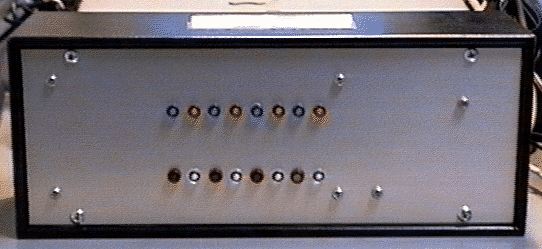

8入力8出力ビデオマトリクス・スイッチャ

1997年2月 長嶋洋一

■概要■

本機は、RCA端子によるNTSCビデオ信号の8入力8出力のスイッチマトリクスをMIDI

でリアルタイム制御するマシンである。ビデオ信号をフレームバッファに格納せずにそ

のままアナログ的にスイッチングしているので、厳密にはフレーム内の非同期ノイズを

発生するが、センサ等を用いたマルチメディア・パフォーマンスにおいては十分な機能

を持っている。スイッチングのデバイスにはMAXIM社のMAX456を、MIDI制御系には

カードマイコンAKI-80を用いている。

■システム(ハードウェア)■

本機の回路図は以下のようになっている。

■ファームウェア■

本機のAKI-80内に組み込まれたファームウェアのソースプログラムは以下の通りであ

る。

;-----------------------------------------------------------------------

; 8-in 8-out Matrix Video Signal Switcher : Feb. 1996

;-----------------------------------------------------------------------

;##### RAM Map #####

dseg

org 0000h

rx_fifo ds 4096

rx_top ds 2

rx_end ds 2

rsb ds 1

dcb ds 1

channel ds 1

keyno ds 1

select ds 8

timer ds 3

disp_sel ds 1

freeze ds 1

;##### I/O Map #####

cseg

sio_a equ 0018h

sio_b equ 001ah

pio_a equ 001ch

pio_b equ 001eh

;##### MACRO #####

io_set macro @1,@2

ld a,@2

out (@1+1),a

endm

io_put macro @1,@2

ld a,@2

out (@1+0),a

endm

move macro @1,@2

ld a,@1

ld (@2),a

endm

;##### RESET #####

org 0000h

ld sp,09fffh

di

jp main

;##### INT / NMI #####

org 0020h

dw _midi_

_midi_:

ex af,af'

exx

ld de,(rx_top)

ld a,10000000b

or d

ld h,a

ld l,e

in a,(sio_a+0)

ld (hl),a

inc de

res 4,d

ld (rx_top),de

exx

ex af,af'

ei

reti

org 0066h

retn

;##### Main #####

main:

ld hl,08000h

ld a,0a0h

_ram_clear_loop:

ld (hl),0

inc hl

cp h

jr nc,_ram_clear_loop

io_set pio_a,0cfh ; Mode 3

io_set pio_a,00000000b ; 0:Out / 1:In

io_set pio_a,007h ; Interrupt Disable

io_set pio_b,0cfh ; Mode 3

io_set pio_b,00000000b ; 0:Out / 1:In

io_set pio_b,007h ; Interrupt Disable

io_set sio_b,00011000b ; Channel Reset B

io_set sio_b,00000100b ; Resister Point = 4

io_set sio_b,11000100b ; Mode

io_set sio_b,00000001b ; Resister Point = 1

io_set sio_b,00000000b ; Interrupt Mode

io_set sio_b,00000010b ; Resister Point = 2

io_set sio_b,20h ; Vector Address

io_set sio_a,00011000b ; Channel Reset A

io_set sio_a,00000100b ; Resister Point = 4

io_set sio_a,11000100b ; Mode

io_set sio_a,00000001b ; Resister Point = 1

io_set sio_a,00010000b ; Interrupt Mode

io_set sio_a,00000011b ; Resister Point = 3

io_set sio_a,11000001b ; Receive Start

im 2

ei

in a,(sio_a+0) ; dummy read

xor a

out (pio_b),a

ld a,11000110b

out (pio_a),a

ld a,10000110b

out (pio_a),a

ld a,11000110b

out (pio_a),a

move 0,select+0

call maxim_init

move 1,select+1

call maxim_init

move 2,select+2

call maxim_init

move 3,select+3

call maxim_init

move 4,select+4

call maxim_init

move 5,select+5

call maxim_init

move 6,select+6

call maxim_init

move 7,select+7

call maxim_init

loop:

call display

call rx_data_check

jr loop

rx_data_check:

ld de,(rx_end)

ld hl,(rx_top)

and a ; CY <-- 0

sbc hl,de

ret z

ld a,10000000b

or d

ld h,a

ld l,e

ld b,(hl)

inc de

res 4,d

ld (rx_end),de

bit 7,b

jr z,50$ ; running

ld a,b

cp 0f8h

ret nc

cp 0f0h

jr c,10$

xor a

ld (rsb),a

ret

10$:

ld a,b

and 00001111b

ld (channel),a

ld a,b

and 11110000b

ld (rsb),a

xor a

ld (dcb),a

ret

50$:

ld a,(rsb)

cp 0

ret z

cp 0c0h

ret z

cp 0d0h

ret z

ld a,(dcb)

cp 0

jr nz,90$

inc a

ld (dcb),a

ld a,b

ld (keyno),a

ret

90$:

xor a

ld (dcb),a

ld a,(rsb)

cp 0a0h

ret nz

ld a,(channel)

cp 00fh

ret nz

ld a,(keyno)

cp 0

jp z,_sel_0

cp 1

jp z,_sel_1

cp 2

jp z,_sel_2

cp 3

jp z,_sel_3

cp 4

jp z,_sel_4

cp 5

jp z,_sel_5

cp 6

jp z,_sel_6

cp 7

jp z,_sel_7

ret

_sel_0:

ld a,b

and 00000111b

ld (select+0),a

jp _sel_disp

_sel_1:

ld a,b

and 00000111b

ld (select+1),a

jp _sel_disp

_sel_2:

ld a,b

and 00000111b

ld (select+2),a

jp _sel_disp

_sel_3:

ld a,b

and 00000111b

ld (select+3),a

jp _sel_disp

_sel_4:

ld a,b

and 00000111b

ld (select+4),a

jp _sel_disp

_sel_5:

ld a,b

and 00000111b

ld (select+5),a

jp _sel_disp

_sel_6:

ld a,b

and 00000111b

ld (select+6),a

jp _sel_disp

_sel_7:

ld a,b

and 00000111b

ld (select+7),a

jp _sel_disp

_sel_disp:

ld c,a

ld a,(keyno)

ld b,a

ld a,c

call maxim_set

ld a,(keyno)

call display_main

ld a,1

ld (freeze),a

xor a

ld (timer+2),a

ret

display:

ld a,(timer+0)

inc a

ld (timer+0),a

cp 0

ret nz

ld a,(timer+1)

inc a

ld (timer+1),a

cp 80 ; ***********:

ret c

xor a

ld (timer+1),a

ld a,(freeze)

cp 0

jr z,_display_go

ld a,(timer+2)

inc a

ld (timer+2),a

cp 3

ret c

xor a

ld (timer+2),a

ld (freeze),a

_display_go:

ld a,(disp_sel)

inc a

and 00000111b

ld (disp_sel),a

display_main:

and 00000111b

ld l,a

rlca

rlca

rlca

ld e,a

ld h,0

ld bc,select

add hl,bc

ld a,(hl)

or e

out (pio_b),a

ret

maxim_init:

ld b,a ; [a]=input, [b]=output

maxim_set:

and 00000111b

or 01000000b

ld e,a

ld a,b

and 00000111b

rlca

rlca

rlca

or e

out (pio_a),a

and 00111111b

out (pio_a),a

or 01000000b

out (pio_a),a

ret

end

■ソフトウェア■

本機を制御するコントローラとしては、MIDIを経由していればシーケンサでも構わな

いが、サンプルとして以下の[matrix_test]というMAXパッチを用意している。これを

アレンジして、任意のマルチメディア・パフォーマンスに対応したMAXパッチを作るこ

とができる。

なお、制御するのは「あるビデオ出力チャンネルは、どのビデオ入力からの信号が割り

当てられるか」という関係であり、「このビデオ入力をどこに出力させるか」という逆

方向の対応ではないことに注意すること。この逆に、全てのビデオ出力が同じビデオ入

力に割り当てられて同じものが出力される、という設定は可能である。

以下に示すのは、1996年11月3日に神戸・ジーベックホールで行った研究発表イベン

トのインスタレーションとして、本機を使用した作品のパッチ例である。

■使用上の注意事項■

本機の使用方法の注意点はただ一つである。本機の電源を投入する際には、それより前

に全てのビデオ入力信号が正常状態で入力されていなければならない。つまり、立ち上

がり時にビデオスイッチLSIが「正常にビデオ入力されていない」と認識したチャンネ

ルのビデオ入力は、その後に与えられても、正常なビデオ出力として得られないで異常

な信号として出力されてしまう。このために、起動時には、本機に接続される全てのビ

デオ信号機器を正常に立ち上げてから、最後に本機の電源を投入すること。

■機能仕様■

MIDIチャンネル「16」のポリフォニック・プレッシャーとして、

・ノート「0」のバリュー(0-7) --- 出力[1]に与えられる入力[1-8]

・ノート「1」のバリュー(0-7) --- 出力[2]に与えられる入力[1-8]

・ノート「2」のバリュー(0-7) --- 出力[3]に与えられる入力[1-8]

・ノート「3」のバリュー(0-7) --- 出力[4]に与えられる入力[1-8]

・ノート「4」のバリュー(0-7) --- 出力[5]に与えられる入力[1-8]

・ノート「5」のバリュー(0-7) --- 出力[6]に与えられる入力[1-8]

・ノート「6」のバリュー(0-7) --- 出力[7]に与えられる入力[1-8]

・ノート「7」のバリュー(0-7) --- 出力[8]に与えられる入力[1-8]

という対応でスイッチマトリクスを設定する。このノート番号については、下位3ビッ

トのビットパターンでマスクせずに、絶対的な値として比較しているので注意。また、

バリューについては下位3ビットのビットパターンでマスクしているので、たとえばデー

タ[8]はデータ[0]というように解釈される。

|