# 18. ROM

18

## 第18章 目次

|        |                      |     |

|--------|----------------------|-----|

| 18.1   | 概要                   | 615 |

| 18.1.1 | ブロック図                | 616 |

| 18.2   | PROMモード              | 617 |

| 18.2.1 | PROMモードの設定           | 617 |

| 18.2.2 | ソケットアダプタの端子対応とメモリマップ | 617 |

| 18.3   | PROMのプログラミング         | 620 |

| 18.3.1 | 書き込み／ベリファイ           | 621 |

| 18.3.2 | 書き込み時の注意             | 624 |

| 18.3.3 | 書き込み後の信頼性            | 625 |

| 18.4   | フラッシュメモリの概要          | 626 |

| 18.4.1 | フラッシュメモリの動作原理        | 626 |

| 18.4.2 | モード端子の設定とROM空間       | 627 |

| 18.4.3 | 特長                   | 628 |

| 18.4.4 | ブロック図                | 629 |

| 18.4.5 | 端子構成                 | 630 |

| 18.4.6 | レジスタ構成               | 630 |

|        |                            |     |

|--------|----------------------------|-----|

| 18.5   | フラッシュメモリの各レジスタの説明          | 631 |

| 18.5.1 | フラッシュメモリコントロールレジスタ (FLMCR) | 631 |

| 18.5.2 | 消去ブロック指定レジスタ1 (EBR1)       | 634 |

| 18.5.3 | 消去ブロック指定レジスタ2 (EBR2)       | 635 |

| 18.5.4 | RAMコントロールレジスタ (RAMCR)      | 637 |

| 18.6   | オンボードプログラミングモード            | 639 |

| 18.6.1 | ブートモード                     | 639 |

| 18.6.2 | ユーザプログラムモード                | 645 |

| 18.7   | フラッシュメモリの書き込み／消去           | 647 |

| 18.7.1 | 書き込みモード                    | 648 |

| 18.7.2 | 書き込みペリファイモード               | 648 |

| 18.7.3 | 書き込みのフローチャートとプログラム例        | 649 |

| 18.7.4 | 消去モード                      | 652 |

| 18.7.5 | 消去ペリファイモード                 | 652 |

| 18.7.6 | 消去のフローチャートとプログラム例          | 653 |

| 18.7.7 | プレライトペリファイモード              | 667 |

| 18.7.8 | プロテクトモード                   | 668 |

| 18.7.9 | NMI入力禁止条件                  | 672 |

| 18.8   | RAMによるフラッシュメモリのエミュレーション    | 673 |

| 18.9   | フラッシュメモリのPROMモード           | 675 |

| 18.9.1 | PROMモードの設定                 | 675 |

| 18.9.2 | ソケットアダプタの端子対応とメモリマップ       | 675 |

| 18.9.3 | PROMモードの動作                 | 678 |

| 18.10  | フラッシュメモリの書き込み／消去時の注意       | 685 |

| 18.11  | マスクROM品発注時の注意              | 692 |

---

## 18.1 概要

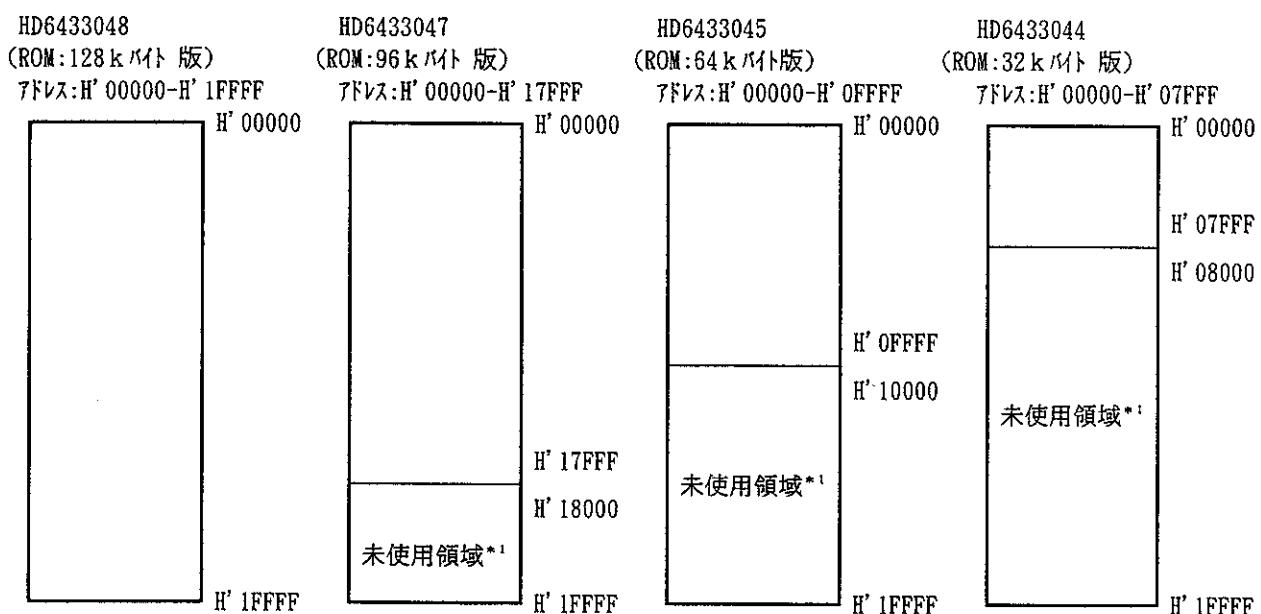

H 8 / 3 0 4 8 は 128k バイト、H 8 / 3 0 4 7 は 96k バイト、H 8 / 3 0 4 5 は 64k バイト、H 8 / 3 0 4 4 は 32k バイトの ROM を内蔵しています。ROM は、CPU と 16 ビット幅のデータバスで接続されており、アクセスはバイトデータ、リードデータにかかわらず 2 ステートで行われます。したがって、データの高速転送が可能です。

内蔵 ROM の有効または無効の設定は表 18.1 に示すように、モード端子 (MD<sub>2</sub> ~ MD<sub>0</sub>) により設定します。

表 18.1 動作モードと ROM

| モード名                           | モード端子 |     |     | 内蔵 ROM         |

|--------------------------------|-------|-----|-----|----------------|

|                                | MD2   | MD1 | MD0 |                |

| モード 1 (内蔵 ROM 無効拡張 1M バイトモード)  | 0     | 0   | 1   | 無効<br>(外部アドレス) |

| モード 2 (内蔵 ROM 無効拡張 1M バイトモード)  | 0     | 1   | 0   |                |

| モード 3 (内蔵 ROM 無効拡張 16M バイトモード) | 0     | 1   | 1   |                |

| モード 4 (内蔵 ROM 無効拡張 16M バイトモード) | 1     | 0   | 0   |                |

| モード 5 (内蔵 ROM 有効拡張 1M バイトモード)  | 1     | 0   | 1   | 有効             |

| モード 6 (内蔵 ROM 有効拡張 16M バイトモード) | 1     | 1   | 0   |                |

| モード 7 (シングルチップモード)             | 1     | 1   | 1   |                |

なお、PROM 版 (H 8 / 3 0 4 8 ZTAT) およびフラッシュメモリ版 (H 8 / 3 0 4 8 F - ZTAT) は、PROM モードに設定することにより汎用 PROM ライタを用いて、自由にプログラムの書き込みができます。

### 18.1.1 ブロック図

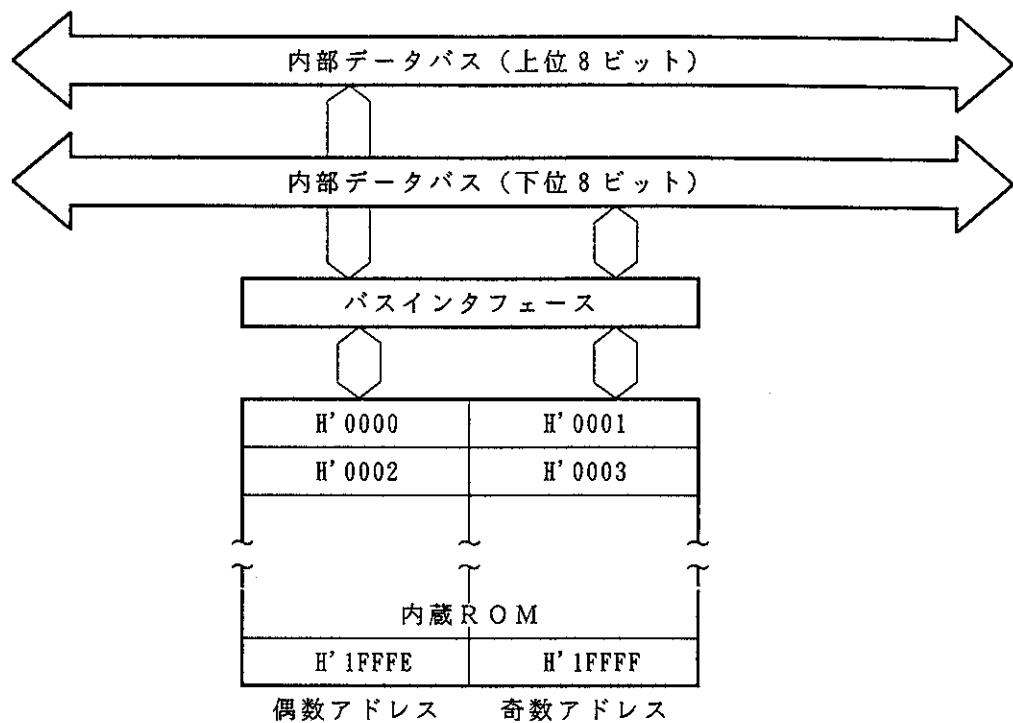

ROMのブロック図を図18.1に示します。

図18.1 ROMのブロック図 (H8/3048、モード7の場合)

## 18.2 PROMモード

### 18.2.1 PROMモードの設定

H8/3048のPROM版の場合、PROMモードに設定するとマイクロコンピュータとしての機能が停止して、HN27C101と同一の方法で内蔵PROMのプログラムを行うことができます。ただし、ページプログラミング方式はサポートしていません。PROMモードの設定方法を表18.2に示します。

表18.2 PROMモード設定

| 端子名                                                               | 設定         |

|-------------------------------------------------------------------|------------|

| モード端子 (MD <sub>2</sub> 、MD <sub>1</sub> 、MD <sub>0</sub> ) の 3 端子 | "Low" レベル  |

| STBY端子                                                            |            |

| P5 <sub>1</sub> 、P5 <sub>0</sub> 端子                               | "High" レベル |

### 18.2.2 ソケットアダプタの端子対応とメモリマップ

PROMのプログラムは、表18.3で示すように各パッケージに対応した、ソケットアダプタを付けて32ピンに変換し、汎用PROMライタで行います。ソケットアダプタの端子対応図を図18.2に示します。また、メモリマップを図18.3に示します。

表18.3 ソケットアダプタ

| 製品名     | パッケージ名               | ソケットアダプタの型名  |

|---------|----------------------|--------------|

| H8/3048 | 100ピンQFP (FP-100B)   | HS3042ESH51H |

|         | 100ピンTQFP (TFP-100B) | HS3042ESNS1H |

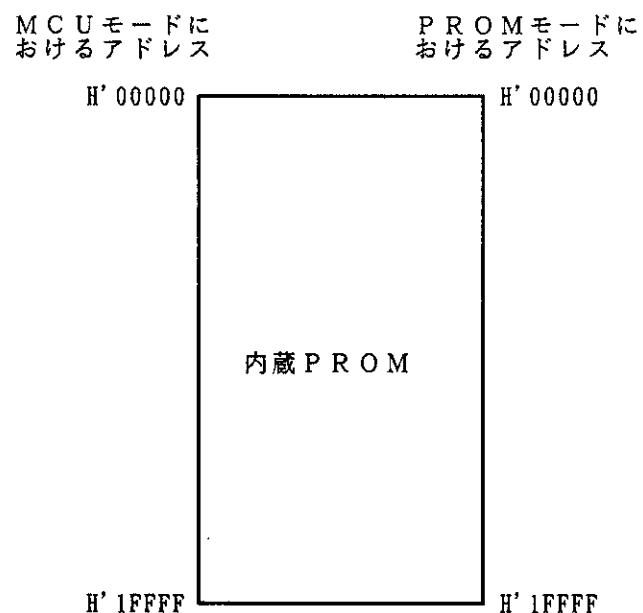

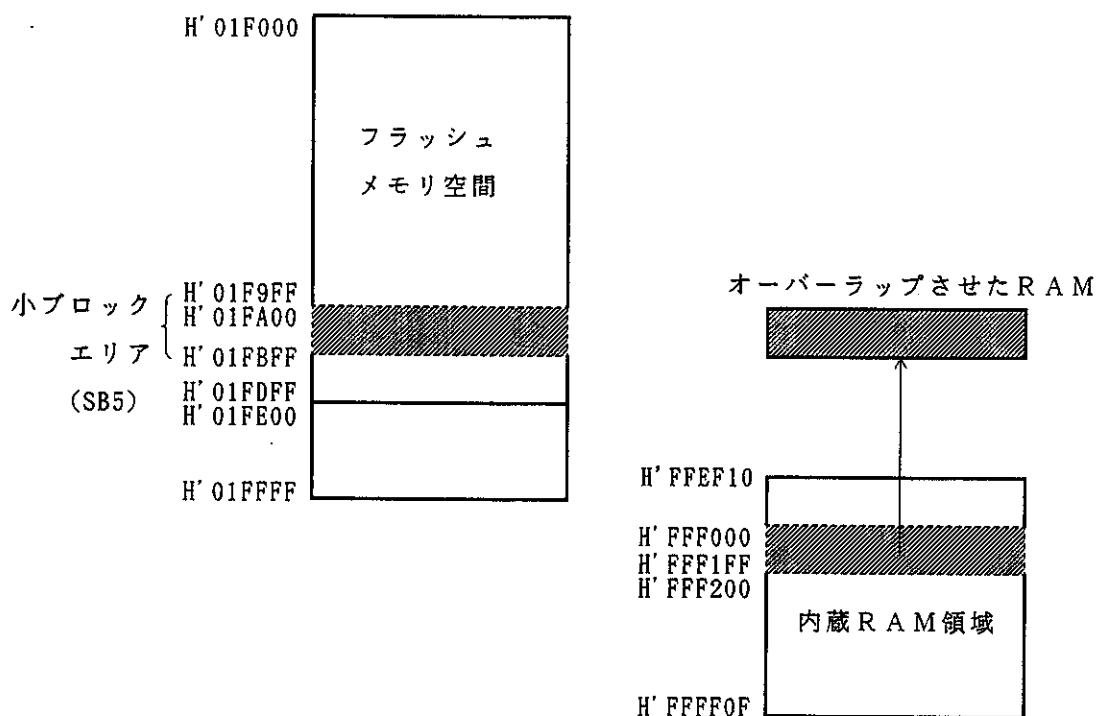

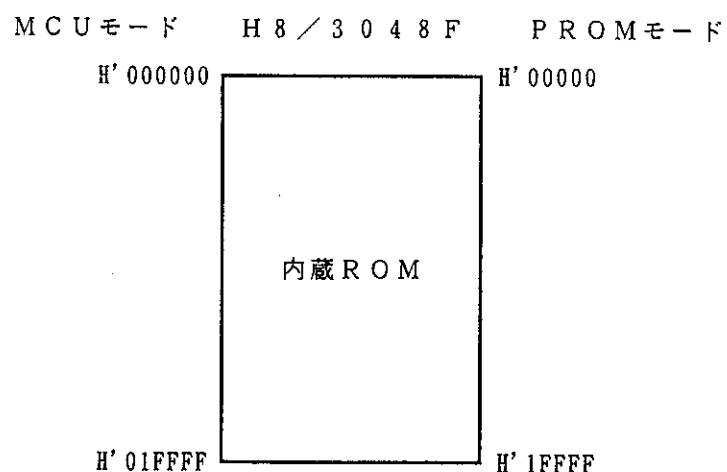

H8/3048のPROMの容量は、128kバイトです。PROMモードのときのメモリマップを図18.3に示します。内蔵PROM内の未使用のアドレス領域のデータは、H'FFとしてください。

H8/3048をPROMライタでプログラムする際に、アドレスはH'00000～H'1FFFFに設定してください。

H 8 / 3 0 4 8

| FP-100B、TFP-100B | 端子               |

|------------------|------------------|

| 10               | RES0             |

| 64               | NMI              |

| 58               | P6 <sub>0</sub>  |

| 87               | P8 <sub>0</sub>  |

| 88               | P8 <sub>1</sub>  |

| 27               | P3 <sub>0</sub>  |

| 28               | P3 <sub>1</sub>  |

| 29               | P3 <sub>2</sub>  |

| 30               | P3 <sub>3</sub>  |

| 31               | P3 <sub>4</sub>  |

| 32               | P3 <sub>5</sub>  |

| 33               | P3 <sub>6</sub>  |

| 34               | P3 <sub>7</sub>  |

| 36               | P1 <sub>0</sub>  |

| 37               | P1 <sub>1</sub>  |

| 38               | P1 <sub>2</sub>  |

| 39               | P1 <sub>3</sub>  |

| 40               | P1 <sub>4</sub>  |

| 41               | P1 <sub>5</sub>  |

| 42               | P1 <sub>6</sub>  |

| 43               | P1 <sub>7</sub>  |

| 45               | P2 <sub>0</sub>  |

| 46               | P2 <sub>1</sub>  |

| 47               | P2 <sub>2</sub>  |

| 48               | P2 <sub>3</sub>  |

| 49               | P2 <sub>4</sub>  |

| 50               | P2 <sub>5</sub>  |

| 51               | P2 <sub>6</sub>  |

| 52               | P2 <sub>7</sub>  |

| 53               | P5 <sub>0</sub>  |

| 54               | P5 <sub>1</sub>  |

| 77               | V <sub>REF</sub> |

| 76               | AV <sub>cc</sub> |

| 1                | V <sub>cc</sub>  |

| 35               | V <sub>cc</sub>  |

| 68               | V <sub>cc</sub>  |

| 73               | MD <sub>0</sub>  |

| 74               | MD <sub>1</sub>  |

| 75               | MD <sub>2</sub>  |

| 62               | STBY             |

| 86               | AV <sub>ss</sub> |

| 11               | V <sub>ss</sub>  |

| 22               | V <sub>ss</sub>  |

| 44               | V <sub>ss</sub>  |

| 57               | V <sub>ss</sub>  |

| 65               | V <sub>ss</sub>  |

| 92               | V <sub>ss</sub>  |

PROMソケット

| 端子               | HN27C101 (32ビン) |

|------------------|-----------------|

| V <sub>pp</sub>  | 1               |

| EA <sub>0</sub>  | 26              |

| EA <sub>15</sub> | 3               |

| EA <sub>16</sub> | 2               |

| PGM              | 31              |

| EO <sub>0</sub>  | 13              |

| EO <sub>1</sub>  | 14              |

| EO <sub>2</sub>  | 15              |

| EO <sub>3</sub>  | 17              |

| EO <sub>4</sub>  | 18              |

| EO <sub>5</sub>  | 19              |

| EO <sub>6</sub>  | 20              |

| EO <sub>7</sub>  | 21              |

| EA <sub>0</sub>  | 12              |

| EA <sub>1</sub>  | 11              |

| EA <sub>2</sub>  | 10              |

| EA <sub>3</sub>  | 9               |

| EA <sub>4</sub>  | 8               |

| EA <sub>5</sub>  | 7               |

| EA <sub>6</sub>  | 6               |

| EA <sub>7</sub>  | 5               |

| EA <sub>8</sub>  | 27              |

| OE               | 24              |

| EA <sub>10</sub> | 23              |

| EA <sub>11</sub> | 25              |

| EA <sub>12</sub> | 4               |

| EA <sub>13</sub> | 28              |

| EA <sub>14</sub> | 29              |

| CE               | 22              |

| V <sub>cc</sub>  | 32              |

| V <sub>ss</sub>  | 16              |

記号説明

|                                   |                   |

|-----------------------------------|-------------------|

| V <sub>pp</sub>                   | : プログラム電源 (12.5V) |

| EO <sub>0</sub> ~ EO <sub>7</sub> | : データ入出力          |

| EA <sub>0</sub> ~ EA <sub>7</sub> | : アドレス入力          |

| OE                                | : 出力イネーブル         |

| CE                                | : チップイネーブル        |

| PGM                               | : プログラム           |

【注】 図中に記載されていない端子はすべてオープンにしてください。

本図は、端子対応を示すもので、ソケットアダプタの全回路を示すものではありません。新規に設計をする場合は、高速 CMOS LSI としての基板設計（電源電圧安定化、ノイズ対策など）が必要です。

図18.2 ソケットアダプタの端子対応図

図18.3 H8/3048のPROMモード時のメモリマップ

### 18.3 PROMのプログラミング

PROMモード時の書き込み、ペリファイなどのモード選択は、表18.4に示すような設定によって行います。

表18.4 PROMモード時のモード選択

| モード       | ピン | $\overline{CE}$ | $\overline{OE}$ | $\overline{PGM}$ | $V_{PP}$ | $V_{CC}$      | $E0_7 \sim E0_0$ | $EA_{15} \sim EA_0$ |

|-----------|----|-----------------|-----------------|------------------|----------|---------------|------------------|---------------------|

| 書込み       | L  | H               | L               | $V_{PP}$         | $V_{CC}$ | データ入力         | アドレス入力           |                     |

| ペリファイ     | L  | L               | H               | $V_{PP}$         | $V_{CC}$ | データ出力         | アドレス入力           |                     |

| プログラミング禁止 | L  | L               | L               | $V_{PP}$         | $V_{CC}$ | ハイイン<br>ピーダンス | アドレス入力           |                     |

|           | L  | H               | H               |                  |          |               |                  |                     |

|           | H  | L               | L               |                  |          |               |                  |                     |

|           | H  | H               | H               |                  |          |               |                  |                     |

〈記号説明〉

L : "Low" レベル

H : "High" レベル

$V_{PP}$  : " $V_{PP}$ " レベル

$V_{CC}$  : " $V_{CC}$ " レベル

なお、書き込み・読み出しが標準のEPROM HN27C101と同じ仕様になっています。

ただし、ページプログラミング方式はサポートしていませんので、ページプログラミングモードに設定しないでください。ページプログラミングモードのみをサポートしているPROMライタは使用できません。PROMライタを選択する場合には、1バイト毎の高速プログラミングモードをサポートしていることを確認してください。また、アドレスは必ずH'00000~H'1FFFFに設定してください。

### 18.3.1 書込み／ベリファイ

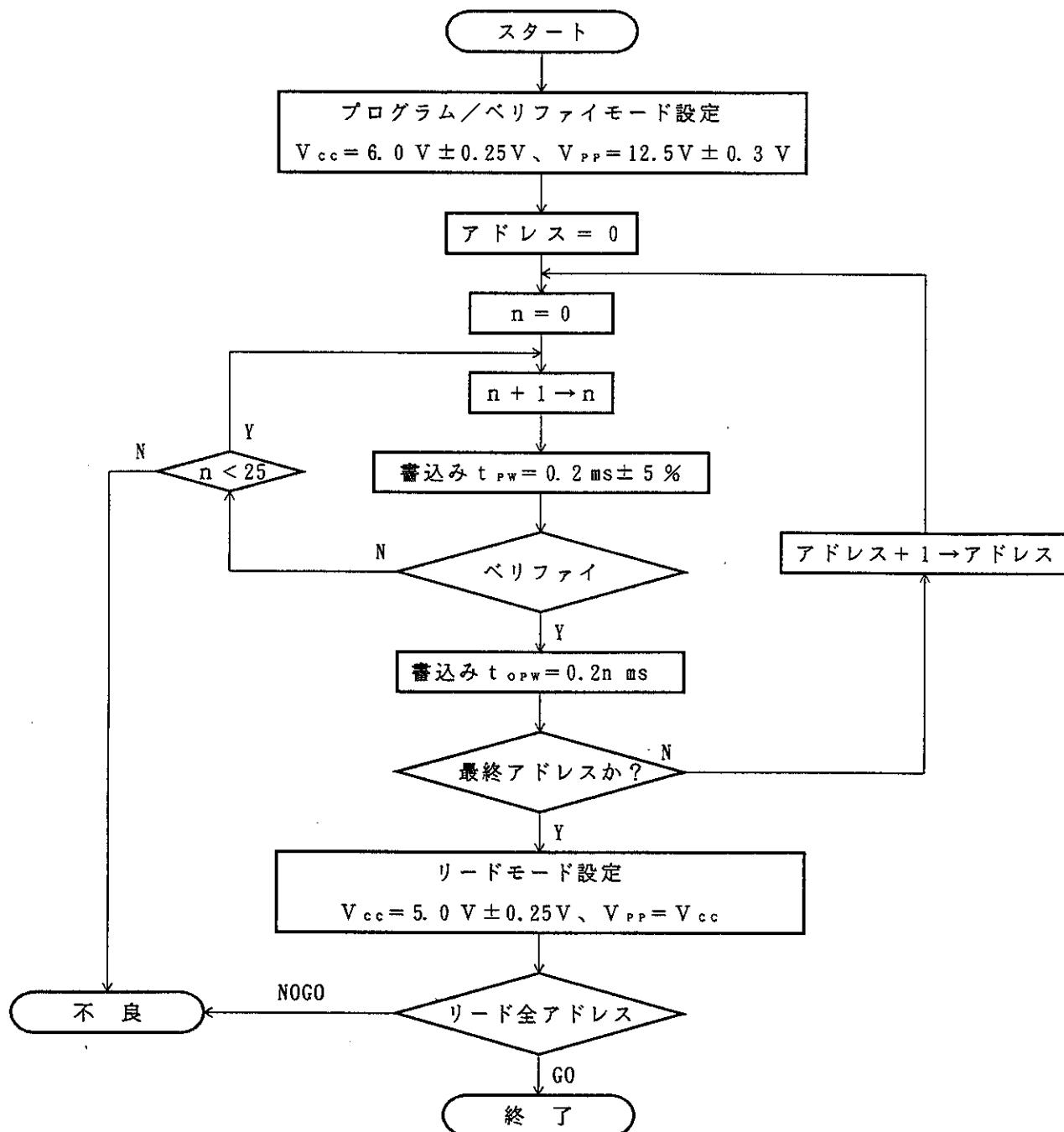

書込み／ベリファイは効率のよい高速プログラミング方式で行うことができます。この方式は、デバイスへの電圧ストレス、あるいは書込みデータの信頼性を損なうことなく高速に書込みを行うことができます。未使用のアドレス領域のデータはH'FFです。

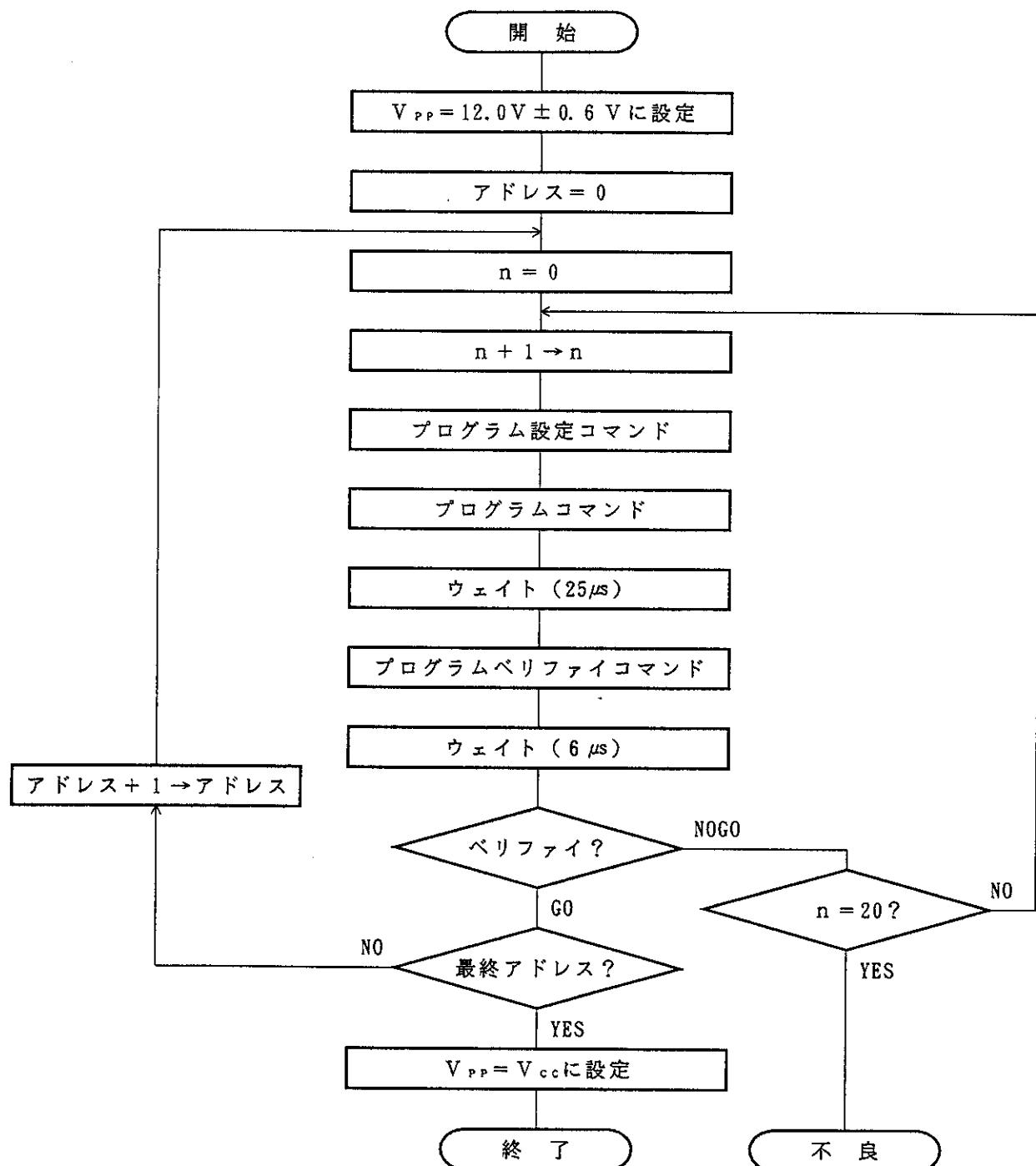

高速プログラミングの基本的なフローを図18.4に示します。

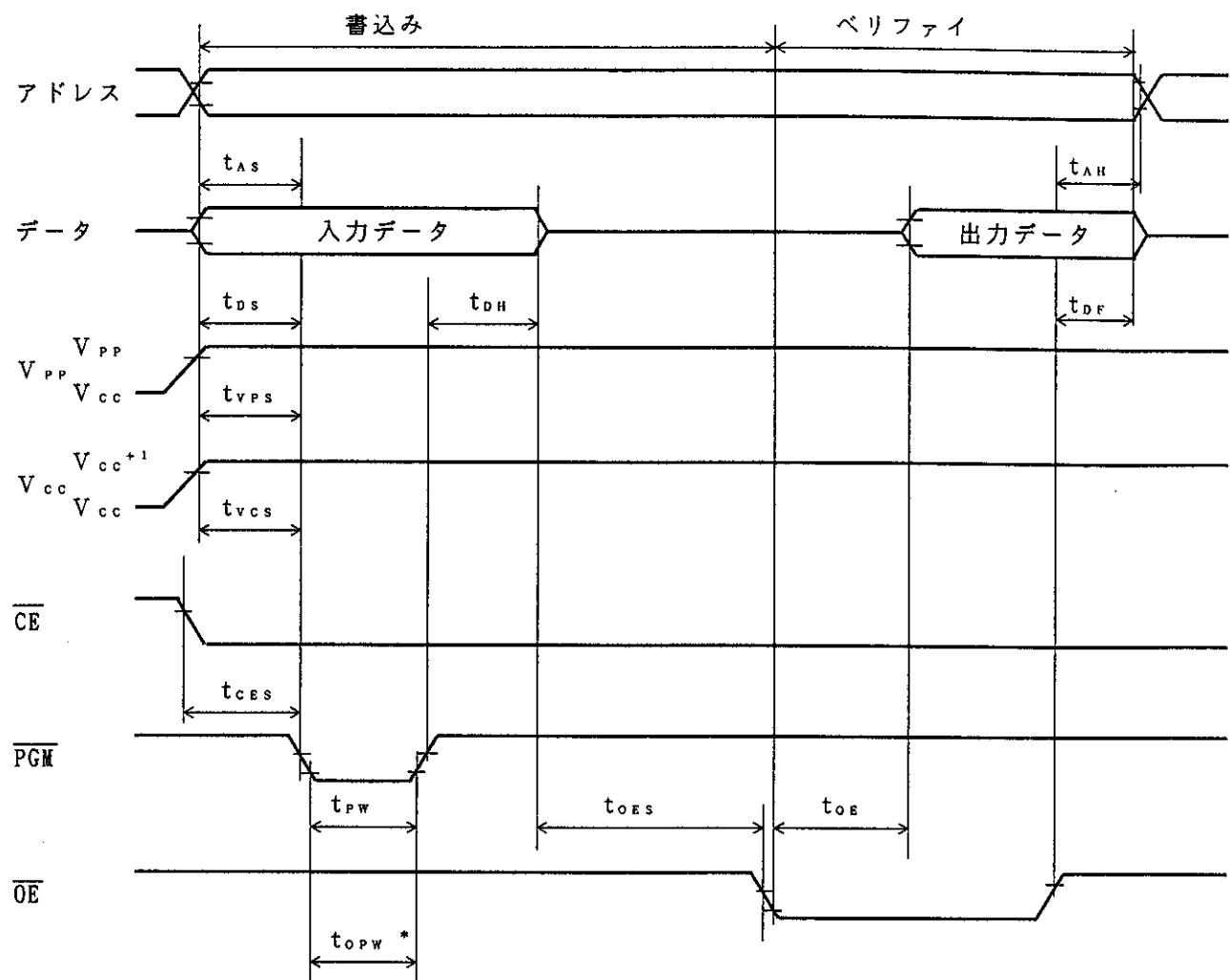

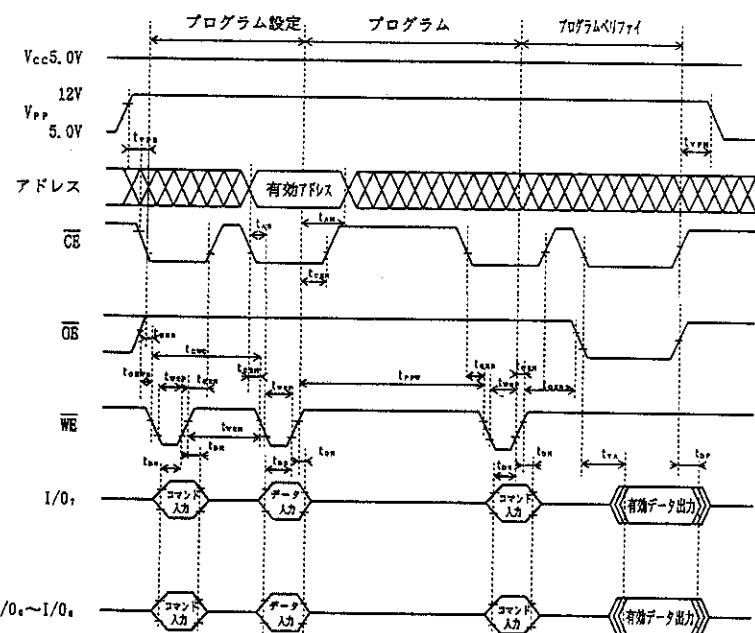

また、プログラミング時の電気的特性を表18.5、表18.6に、タイミングを図18.5に示します。

図18.4 高速プログラミングフローチャート

表18.5 DC特性

(条件:  $V_{cc} = 6.0 \text{ V} \pm 0.25 \text{ V}$ 、 $V_{pp} = 12.5 \text{ V} \pm 0.3 \text{ V}$ 、 $V_{ss} = 0 \text{ V}$ 、 $T_s = 25^\circ\text{C} \pm 5^\circ\text{C}$ )

| 項目                                                                                                 | 記号       | min  | typ | max            | 単位            | 測定条件                                    |

|----------------------------------------------------------------------------------------------------|----------|------|-----|----------------|---------------|-----------------------------------------|

| 入力"High"レベル電圧<br>EO <sub>1</sub> ~EO <sub>8</sub> 、EA <sub>1</sub> ~EA <sub>8</sub> 、<br>OE、CE、PGM | $V_{IH}$ | 2.4  | —   | $V_{cc} + 0.3$ | V             |                                         |

| 入力"Low"レベル電圧<br>EO <sub>1</sub> ~EO <sub>8</sub> 、EA <sub>1</sub> ~EA <sub>8</sub> 、<br>OE、CE、PGM  | $V_{IL}$ | -0.3 | —   | 0.8            | V             |                                         |

| 出力"High"レベル電圧<br>EO <sub>1</sub> ~EO <sub>8</sub>                                                  | $V_{OH}$ | 2.4  | —   | —              | V             | $I_{OH} = -200 \mu\text{A}$             |

| 出力"Low"レベル電圧<br>EO <sub>1</sub> ~EO <sub>8</sub>                                                   | $V_{OL}$ | —    | —   | 0.45           | V             | $I_{OL} = 1.6 \text{ mA}$               |

| 入力リード電流<br>EO <sub>1</sub> ~EO <sub>8</sub> 、EA <sub>1</sub> ~EA <sub>8</sub> 、<br>OE、CE、PGM       | $I_{L1}$ | —    | —   | 2              | $\mu\text{A}$ | $V_{in} = 5.25 \text{ V}/0.5 \text{ V}$ |

| $V_{cc}$ 電流                                                                                        | $I_{cc}$ | —    | —   | 40             | mA            |                                         |

| $V_{pp}$ 電流                                                                                        | $I_{pp}$ | —    | —   | 40             | mA            |                                         |

表18.6 AC特性

(条件:  $V_{cc} = 6.0 \text{ V} \pm 0.25 \text{ V}$ 、 $V_{pp} = 12.5 \text{ V} \pm 0.3 \text{ V}$ 、 $T_s = 25^\circ\text{C} \pm 5^\circ\text{C}$ )

| 項目                 | 記号             | min  | typ  | max  | 単位            | 測定条件     |

|--------------------|----------------|------|------|------|---------------|----------|

| アドレスセットアップ時間       | $t_{AS}$       | 2    | —    | —    | $\mu\text{s}$ | 図18.5 *1 |

| OEセットアップ時間         | $t_{OES}$      | 2    | —    | —    | $\mu\text{s}$ |          |

| データセットアップ時間        | $t_{DS}$       | 2    | —    | —    | $\mu\text{s}$ |          |

| アドレスホールド時間         | $t_{AH}$       | 0    | —    | —    | $\mu\text{s}$ |          |

| データホールド時間          | $t_{DH}$       | 2    | —    | —    | $\mu\text{s}$ |          |

| データ出力ディスエーブル時間     | $t_{DF}^{*2}$  | —    | —    | 130  | ns            |          |

| $V_{pp}$ セットアップ時間  | $t_{VPS}$      | 2    | —    | —    | $\mu\text{s}$ |          |

| プログラムパルス幅          | $t_{PW}$       | 0.19 | 0.20 | 0.21 | ns            |          |

| オーバープログラム時のPGMパルス幅 | $t_{OPW}^{*3}$ | 0.19 | —    | 5.25 | ns            |          |

| $V_{cc}$ セットアップ時間  | $t_{VCS}$      | 2    | —    | —    | $\mu\text{s}$ |          |

| CEセットアップ時間         | $t_{CES}$      | 2    | —    | —    | $\mu\text{s}$ |          |

| データ出力遅延時間          | $t_{OE}$       | 0    | —    | 150  | ns            |          |

【注】\*1 入力パルス・レベル: 0.8 ~ 2.2 V

入力立上がり/立下がり時間  $\leq 20 \text{ ns}$

タイミング参照レベル  $\left\{ \begin{array}{l} \text{入力: } 1.0 \text{ V}, 2.0 \text{ V} \\ \text{出力: } 0.8 \text{ V}, 2.0 \text{ V} \end{array} \right.$

\*2  $t_{DF}$ は出力が開放状態に達し、出力レベルを参照できなくなった場合で定義します。\*3  $t_{OPW}$ はフローチャートに記載した値で定義されます。

【注】\*  $t_{OTPW}$  はフローチャートに記載した値で定義します。

図18.5 PROM書き込み／ベリファイ・タイミング

### 18.3.2 書込み時の注意

- (1) 書込みは規定された電圧、タイミングで行ってください。

PROMモード時のプログラム電圧 ( $V_{PP}$ ) は12.5Vです。

定格以上の電圧を加えると、製品の永久破壊に至りますので、注意してください。特に PROMライタのオーバーシュートなどには十分注意してください。

PROMライタの HN27C101 の日立仕様にセットすると、 $V_{PP}$  は12.5Vになります。

- (2) PROMライタのソケット、ソケットアダプタおよび製品それぞれのインデックスが正しく一致していないと、過剰電流によって製品が破壊することがあります。書込み前に正しく PROMライタに装着されていることを必ず確認してください。

- (3) 書込み中はソケットアダプタおよび製品には触れないようにしてください。接触不良により書込み不良となる場合があります。

- (4) プログラミングモードは、ページプログラミング方式をサポートしていませんので、プログラミングモードの設定には注意してください。

- (5) H8/3048 の PROM の容量は128kバイトです。アドレスは必ず H'00000 ~ H'1FFFF に設定してください。

### 18.3.3 書込み後の信頼性

データ書込み後、データ保持特性を向上させるために、150°Cの高温放置をしてスクリーニングを行うと大変有効です。高温放置は、スクリーニングの1つであり、PROMメモリセルの初期のデータ保持不良を短時間で除くことができます。

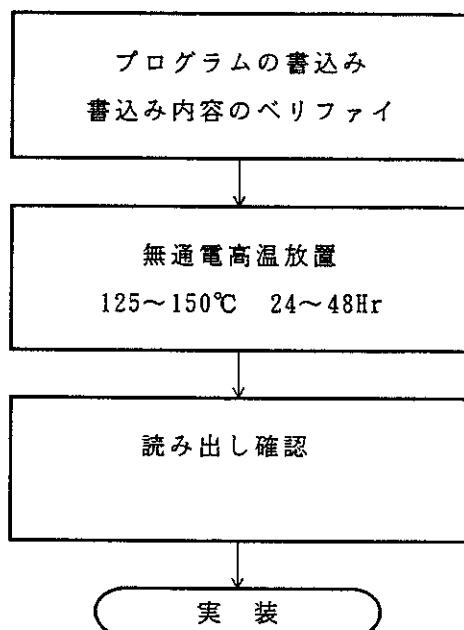

図18.6に推奨するスクリーニングフローを示します。

図18.6 推奨スクリーニングフロー

同じ、PROMライタでプログラミング中、書き込み不良が連続して発生した場合には書き込みを中止し、PROMライタ、ソケットアダプタなどに異常がないか確認してください。

書き込みあるいは高温放置後のプログラム確認において異常がありましたら、当社技術担当にご連絡ください。

## 18.4 フラッシュメモリの概要

### 18.4.1 フラッシュメモリの動作原理

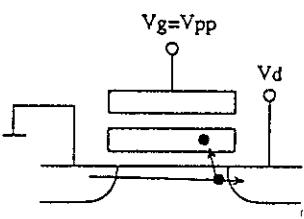

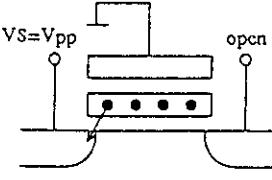

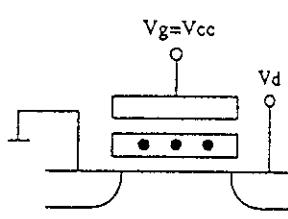

H8/3048Fに内蔵するフラッシュメモリの動作原理を表18.7に示します。

フラッシュメモリの書き込みは、EEPROMと同様、ゲートおよびドレインに高電圧をかけ、ドレン近傍で発生したホットエレクトロンをフローティングゲートに吸い上げることにより行われます。その結果、書き込み後のしきい値電圧は、消去時に比べ高くなります。消去は、ゲートを接地し、ソースに高電圧をかけ、トンネル効果によりフローティングゲートに蓄積した電子を引き抜くことにより行われます。消去後、しきい値電圧は低下します。読み出しが、EEPROMと同様にゲートに高レベルの電圧を加え、しきい値電圧の高低に応じたドレイン電流を検出することによって行われます。消去しすぎるとしきい値電圧が負になり、メモリセルが正常に動作しない場合があるので、消去時には注意が必要となります。

「18.7.6 消去のフローチャートとプログラム例」に消去制御に最適なフローチャートとプログラム例を示します。

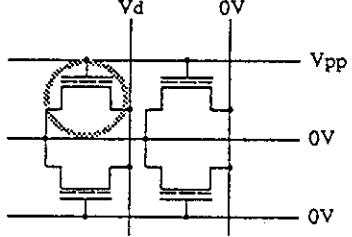

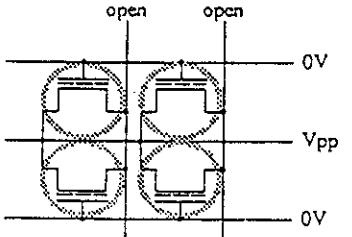

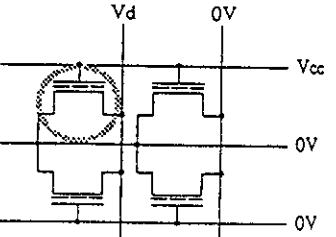

表18.7 メモリセル動作原理

|        | 書き込み                                                                                | 消去                                                                                   | 読み出し                                                                                  |

|--------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| メモリセル  |  |   |  |

| メモリアレイ |  |  |  |

#### 18.4.2 モード端子の設定とROM空間

H8/3048Fは、128kバイトのフラッシュメモリを内蔵しています。ROMはCPUと16ビットデータバスで接続されています。CPUは、命令サイズがバイト／ワードにかかわらず、フラッシュメモリを2ステートでアクセスします。

フラッシュメモリは、メモリマップ上のアドレスH'00000～H'1FFFに割り当てられています。この空間は、モード端子の設定で内蔵フラッシュメモリ空間と外部メモリ空間の切り換えができます。モード端子の設定とフラッシュメモリ空間の設定を表18.8に示します。

表18.8 モード端子の設定とROM空間

| モード名 | モード端子の設定        |                 |                 | ROM空間の設定     |

|------|-----------------|-----------------|-----------------|--------------|

|      | MD <sub>2</sub> | MD <sub>1</sub> | MD <sub>0</sub> |              |

| モード0 | 0               | 0               | 0               | 設定禁止         |

| モード1 | 0               | 0               | 1               | 外部メモリ空間      |

| モード2 | 0               | 1               | 0               | 外部メモリ空間      |

| モード3 | 0               | 1               | 1               | 外部メモリ空間      |

| モード4 | 1               | 0               | 0               | 外部メモリ空間      |

| モード5 | 1               | 0               | 1               | 内蔵フラッシュメモリ空間 |

| モード6 | 1               | 1               | 0               | 内蔵フラッシュメモリ空間 |

| モード7 | 1               | 1               | 1               | 内蔵フラッシュメモリ空間 |

フラッシュメモリの特長を以下に示します。

■ フラッシュメモリの5種類の動作状態

フラッシュメモリの動作状態として、プログラムモード、プログラムベリファイモード、イレースモード、イレースベリファイモード、プレライトベリファイモードがあります。

■ 消去ブロックの指定

フラッシュメモリ空間の消去対象とするブロックを、対応するビットの設定により指定できます。大ブロックエリア (12k ~ 16k バイト × 8 ブロック) と小ブロックエリア (512 バイト × 8 ブロック) があります。

■ 書込み、消去時間

フラッシュメモリの1バイトあたりの書込み時間は 50 $\mu$ s (typ)、全ブロック (128K バイト)、消去時間は 1 s (typ) です。

■ 書換え回数

フラッシュメモリの書換えは、100回まで可能です。

■ オンボードプログラミングモード

フラッシュメモリの書込み、消去、ベリファイを行うモードです。2種類の動作モード (ブートモード、ユーザプログラムモード) があります。

■ ビットレート自動合わせ込み

ブートモードのデータ転送時、ホストの転送ビットレートと H 8 / 3 0 4 8 F のビットレートの自動合わせ込みができます (9600bps, 4800bps, 2400bps)。

■ R A Mによるフラッシュメモリのエミュレーション

フラッシュメモリに R A Mの一部を重ね合わせることで、フラッシュメモリのリアルタイムな書換えをエミュレートします。

■ P R O Mモード

プログラムの書込み、消去可能なモードとして、オンボードプログラミングモード以外に P R O M モードがあり、汎用 P R O M ライタを用いてフラッシュメモリに自由にプログラムを書込むことができます。

■ プロテクトモード

ソフトウェアプロテクトとハードウェアプロテクトの2つのモードがあり、フラッシュメモリの書込み、消去、ベリファイのプロテクト状態を設定することができます。

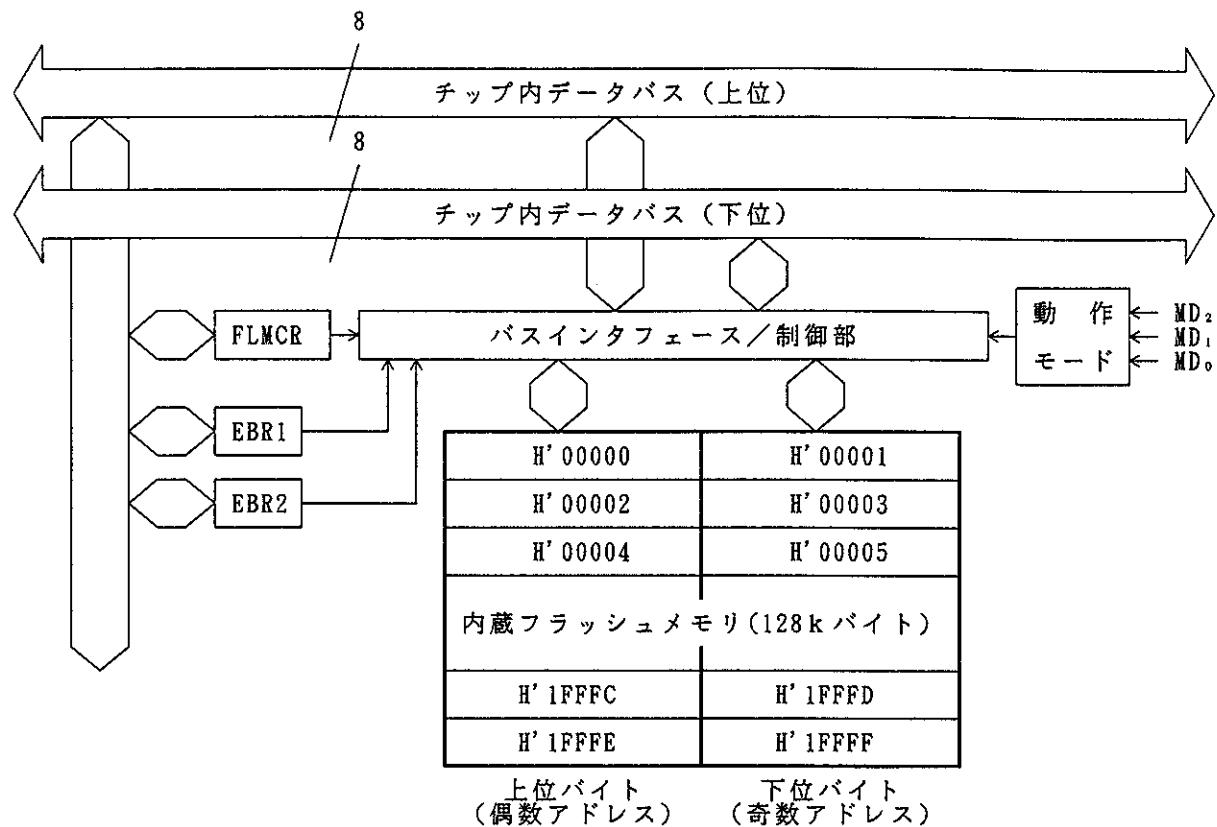

#### 18.4.4 ブロック図

フラッシュメモリのブロック図を図18.7に示します。

〈記号説明〉

FLMCR : フラッシュメモリコントロールレジスタ

EBR1 : 消去ブロック指定レジスタ1

EBR2 : 消去ブロック指定レジスタ2

図18.7 フラッシュメモリのブロック図

#### 18.4.5 端子構成

フラッシュメモリは表18.9に示す端子により制御されます。

表18.9 端子構成

| 端子名        | 略称               | 入出力 | 機能                   |

|------------|------------------|-----|----------------------|

| プログラム電源    | V <sub>PP</sub>  | 電源  | 12.0Vを印加             |

| モード2       | MD <sub>2</sub>  | 入力  | H 8 / 3048Fの動作モードを設定 |

| モード1       | MD <sub>1</sub>  | 入力  | H 8 / 3048Fの動作モードを設定 |

| モード0       | MD <sub>0</sub>  | 入力  | H 8 / 3048Fの動作モードを設定 |

| トランスマットデータ | TxD <sub>1</sub> | 出力  | シリアル送信データ出力          |

| レシーブデータ    | RxD <sub>1</sub> | 入力  | シリアル受信データ入力          |

トランスマットデータ端子とレシーブデータ端子はブートモード時に使用します。

#### 18.4.6 レジスタ構成

フラッシュメモリは表18.10に示すレジスタにより制御されます。

表18.10 レジスタ構成

| アドレス   | 名 称                | 略 称       | R / W               | 初期値                |

|--------|--------------------|-----------|---------------------|--------------------|

| H'FF40 | フラッシュメモリコントロールレジスタ | F L M C R | R / W <sup>*2</sup> | H'00 <sup>*1</sup> |

| H'FF42 | 消去ブロック指定レジスタ1      | E B R 1   | R / W <sup>*2</sup> | H'00 <sup>*1</sup> |

| H'FF43 | 消去ブロック指定レジスタ2      | E B R 2   | R / W <sup>*2</sup> | H'00 <sup>*1</sup> |

| H'FF48 | R A Mコントロールレジスタ    | R A M C R | R / W               | H'70               |

【注】<sup>\*1</sup> モード5、6、7（内蔵フラッシュメモリが有効）のとき初期値はH'00となります。

<sup>\*2</sup> モード1、2、3、4（内蔵フラッシュメモリが無効）のときは、リードすると常にH'FFが読み出され、ライトも無効となります。

## 18.5 フラッシュメモリの各レジスタの説明

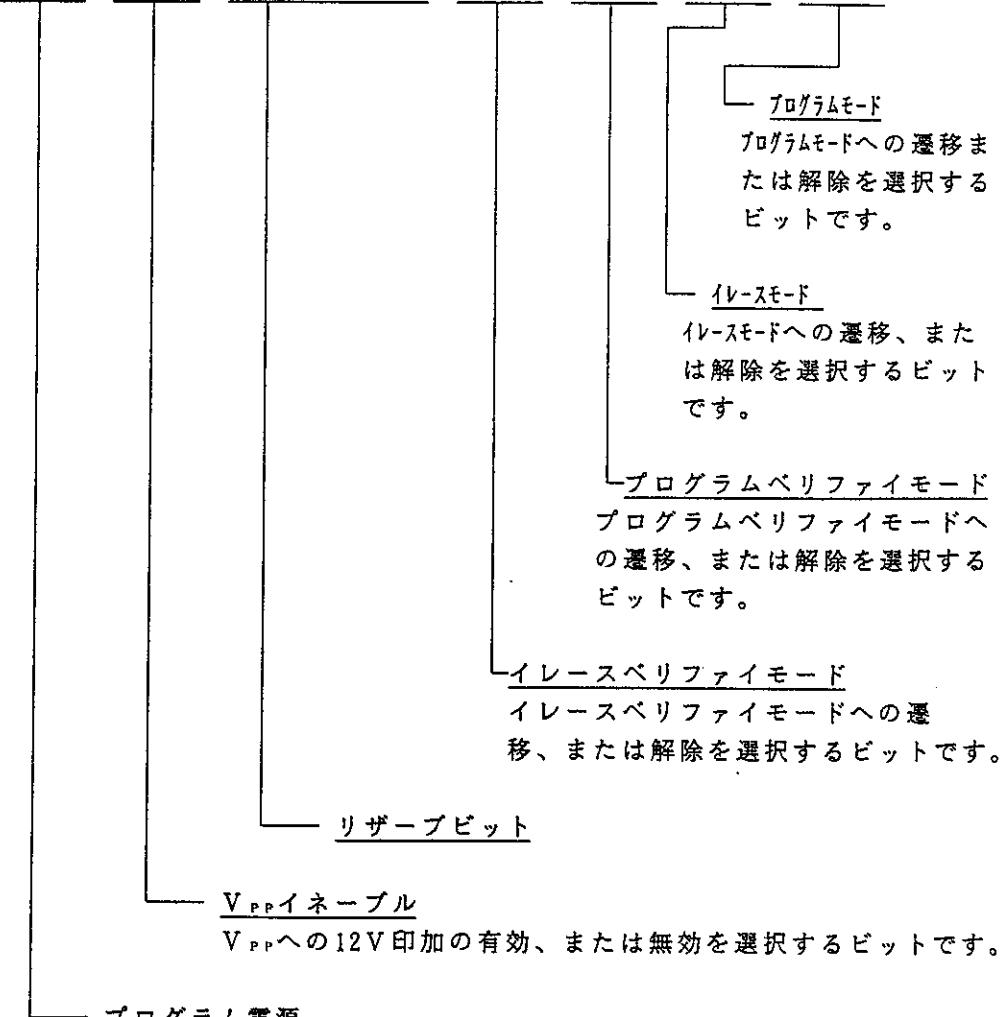

### 18.5.1 フラッシュメモリコントロールレジスタ (FLMCR)

フラッシュメモリコントロールレジスタ (FLMCR) は、フラッシュメモリの各動作モードを制御する8ビットのレジスタです。ビットをセットすることにより、プログラムモード、イレースモード、プログラムベリファイモード、イレースベリファイモードに遷移できます。FLMCRはリセット、またはスタンバイモード時、あるいは $V_{PP}$ に12V印加されていないとき、H'00にイニシャライズされます。ただし、 $V_{PP}$ に12Vが印加されているときのリセット、またはスタンバイモード時は、H'80になります。

| ビット: | 7        | 6         | 5 | 4 | 3  | 2  | 1 | 0 |

|------|----------|-----------|---|---|----|----|---|---|

|      | $V_{PP}$ | $V_{PP}E$ | — | — | EV | PV | E | P |

初期値\*: 0 0 0 0 0 0 0 0 0

R/W: R R/W — — R/W\* R/W\* R/W\* R/W\*

#### プログラム電源

$V_{PP}$ 端子に印加されている電圧レベルを示すフラグです。

【注】\*: モード5、6、7（内蔵フラッシュメモリが有効）のとき初期値はH'00となります。

モード1、2、3、4（内蔵フラッシュメモリが無効）のときは、リードすると常にH'FFが読み出され、ライトも無効となります。

### ビット7：プログラム電源（V<sub>PP</sub>）

プログラム電源ビット（V<sub>PP</sub>）は、V<sub>PP</sub>端子の電圧を検出し、そのレベルを1/0で表示するビットです。しきい値は、「21.3.1 DC特性」で指定する高電圧印加判定レベルV<sub>H</sub>です。V<sub>H</sub>値は、V<sub>CC</sub>+2V～11.4V間でばらつき、V<sub>H</sub>以上の電圧が印加されると“1”と表示し、V<sub>H</sub>以上の電圧が印加されていないと“0”と表示します。

本ビットは、フラッシュメモリに対する書き込み/消去動作時のハードウェアプロテクトの機能を制御します。ハードウェアプロテクトについては、18.7.8の②を参照してください。

なお、V<sub>PP</sub>使用時の注意は「18.10 フラッシュメモリの書き込み/消去時の注意(4)」を参照してください。

| ビット7<br>V <sub>PP</sub> | 説明                                                                                                                                       |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0                       | (クリア条件)<br>V <sub>PP</sub> 端子に高電圧印加判定レベルV <sub>H</sub> 以上の高電圧が印加されていないとき。<br>通常動作モードであり、フラッシュメモリへの書き込み/消去ができない（ハードウェアプロテクトされている）ことを示します。 |

| 1                       | (セット条件)<br>V <sub>PP</sub> 端子に高電圧印加判定レベルV <sub>H</sub> 以上の高電圧が印加されているとき。<br>フラッシュメモリへの書き込み/消去が可能なようにハードウェアプロテクト機能が解除されていることを示します。*       |

\*：正しい書き込み/消去のためにはV<sub>PP</sub>=12.0±0.6V(11.4～12.6V)に設定する必要があります。

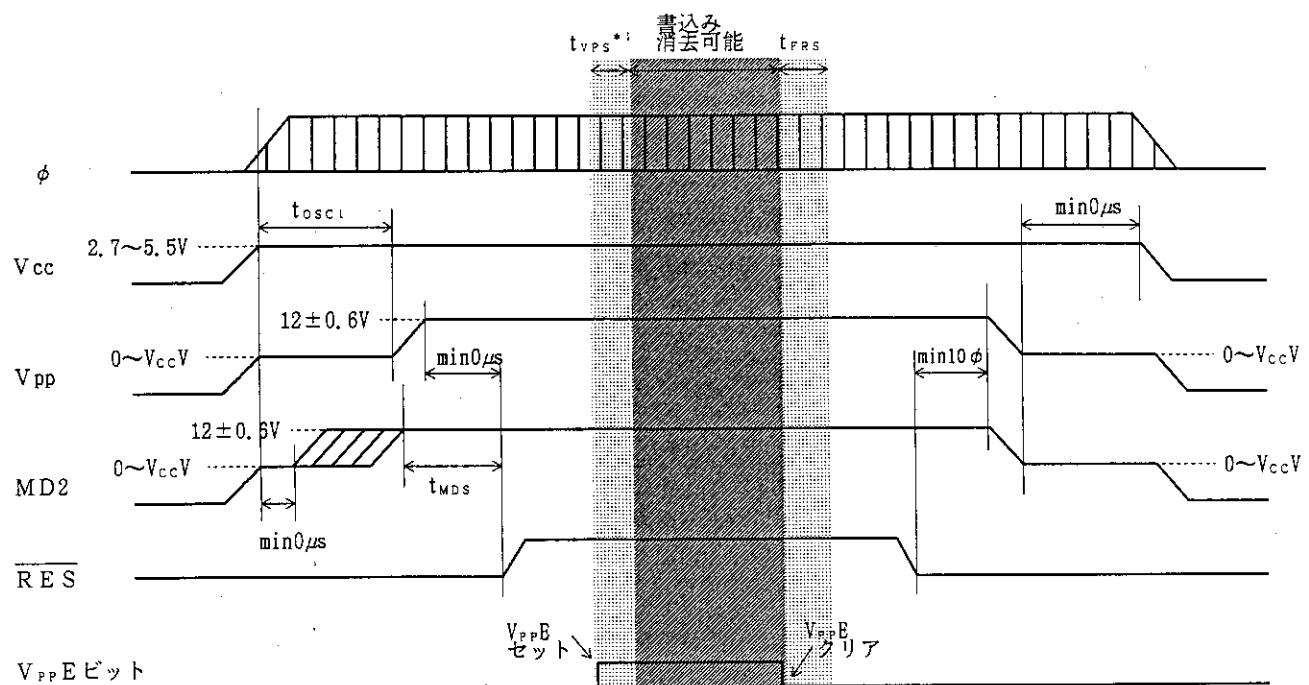

### ビット6：V<sub>PP</sub>イネーブルビット（V<sub>PP</sub>E）

V<sub>PP</sub>への12V印加の有効、または無効を選択するビットです。書き込みおよび消去する場合、このビットをセットしてから5μs以上の待ち時間が必要です。また、本ビットをクリア後、フラッシュメモリリードするには、フラッシュメモリリードセットアップ時間(t<sub>FRS</sub>)の待ち時間が必要です。

| ビット6<br>V <sub>PP</sub> E | 説明                         |

|---------------------------|----------------------------|

| 0                         | V <sub>PP</sub> 端子の12V電源無効 |

| 1                         | V <sub>PP</sub> 端子の12V電源有効 |

【注】 フラッシュメモリに使用する電源系は、V<sub>PP</sub>Eビットにより切替えられます。切替え後、電源系が安定する迄の期間の動作は保証されません。このため、V<sub>PP</sub>Eビットのセット/リセットの命令をフラッシュメモリからフェッチして実行することは禁止です。

#### ビット 5 ~ 4 : リザーブビット

リザーブビットです。リードすると常に 0 が読み出されます。ライトは無効です。

#### ビット 3 : イレースペリファイモード (E V) \*1

イレースペリファイモードへの遷移、または解除を選択するビットです。

| ビット 3 | 説               | 明     |

|-------|-----------------|-------|

| E V   |                 |       |

| 0     | イレースペリファイモードを解除 | (初期値) |

| 1     | イレースペリファイモードに遷移 |       |

#### ビット 2 : プログラムペリファイモード (P V) \*1

プログラムペリファイモードへの遷移、または解除を選択するビットです。

| ビット 2 | 説                | 明     |

|-------|------------------|-------|

| P V   |                  |       |

| 0     | プログラムペリファイモードを解除 | (初期値) |

| 1     | プログラムペリファイモードに遷移 |       |

#### ビット 1 : イレースモード (E) \*1 \*2

イレースモードへの遷移、または解除を選択するビットです。

| ビット 1 | 説          | 明     |

|-------|------------|-------|

| E     |            |       |

| 0     | イレースモードを解除 | (初期値) |

| 1     | イレースモードに遷移 |       |

#### ビット 0 : プログラムモード (P) \*1 \*2

プログラムモードへの遷移、または解除を選択するビットです。

| ビット 0 | 説           | 明     |

|-------|-------------|-------|

| P     |             |       |

| 0     | プログラムモードを解除 | (初期値) |

| 1     | プログラムモードに遷移 |       |

【注】 \*1 複数のビットを同時にセットしないでください。ビットをセットした状態で、V<sub>cc</sub>、V<sub>pp</sub>電源を切断しないでください。

\*2 各ビットのセットは、「18.7 フラッシュメモリの書き込み／消去」に示すアルゴリズムに従ってください。使用時の注意として「18.10 フラッシュメモリの書き込み／消去時の注意」を参照してください。E ビット、P ビットをセットした場合、プログラムの暴走に備えて、あらかじめウォッチドッグタイマの設定を行ってください。

### 18.5.2 消去ブロック指定レジスタ1 (E B R 1)

消去ブロック指定レジスタ (E B R 1) はフラッシュメモリの書き込みおよび消去する大ブロックを選択する8ビットのレジスタです。リセット、またはスタンバイモード時、V<sub>PP</sub>に12V印加されていてV<sub>PP</sub>Eビットが“0”的とき、あるいはV<sub>PP</sub>に12V印加されていないとき、H'00にイニシャライズされます。E B R 1のビットを“1”にセットすると対応するブロックが選択され、書き込みおよび消去対象ブロックになります。消去ブロックの分割を図18.8に示します。

| ビット: | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|------|

|      | LB7  | LB6  | LB5  | LB4  | LB3  | LB2  | LB1  | LB0  |

| 初期値: | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W: | R/W* |

【注】\* モード5、6、7（内蔵ROMが有効）のとき初期値はH'00となります。

モード1、2、3、4（内蔵ROMが無効）のときは、リードすると常にH'FFが読み出され、ライトも無効となります。

ビット7～0：ラージブロック7～0 (LB7～LB0)

ラージブロック7～0 (LB7～LB0) ブロックを書き込みおよび消去対象ブロックとして選択するビットです。

| ビット7～0 | LB7～LB0 | 説明                                 |

|--------|---------|------------------------------------|

| 0      | LB7～LB0 | ラージブロック7～0 ブロックを選択していないとき<br>(初期値) |

| 1      | LB7～LB0 | ラージブロック7～0 ブロックを選択しているとき           |

### 18.5.3 消去ブロック指定レジスタ2 (E B R 2)

消去ブロック指定レジスタ2 (E B R 2) は、フラッシュメモリの書き込みおよび消去する小ブロックを選択する8ビットのレジスタです。リセット、またはスタンバイモード時、V<sub>PP</sub>に12V印加されていてV<sub>PE</sub>ビットが“0”的とき、あるいはV<sub>PP</sub>に12V印加されていないとき、H'00に初期化されます。E B R 2のビットを“1”にセットすると対応するブロックが選択され、書き込みおよび消去対象ブロックになります。消去ブロックの分割を図18.8に示します。

| ビット: | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|-----|

|      | SB7 | SB6 | SB5 | SB4 | SB3 | SB2 | SB1 | SB0 |

初期値: 0 0 0 0 0 0 0 0 0

R/W: R/W\* R/W\* R/W\* R/W\* R/W\* R/W\* R/W\* R/W\* R/W\*

【注】\* モード5、6、7（内蔵ROMが有効）のとき初期値はH'00となります。

モード1、2、3、4（内蔵ROMが無効）のときは、リードすると常にH'FFが読み出され、ライトも無効となります。

ビット7～0: スモールブロック7～0 (S B 7～S B 0)

スモールブロック7～0 (S B 7～S B 0) ブロックを書き込みおよび消去対象ブロックとして選択するビットです。

| ビット7～0<br>S B 7～S B 0 | 説                          | 明     |

|-----------------------|----------------------------|-------|

| 0                     | S B 7～S B 0 ブロックを選択していないとき | (初期値) |

| 1                     | S B 7～S B 0 ブロックを選択しているとき  |       |

| 対応するビット | アドレス                |              |                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L B 0   | H' 00000 ~ H' 03FFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 1   | H' 04000 ~ H' 07FFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 2   | H' 08000 ~ H' 0BFFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 3   | H' 0C000 ~ H' 0FFFF | 大ブロック<br>エリア |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 4   | H' 10000 ~ H' 13FFF | (124K バイト)   |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 5   | H' 14000 ~ H' 17FFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 6   | H' 18000 ~ H' 1BFFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| L B 7   | H' 1C000 ~ H' 1EFFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 0   | H' 1F000 ~ H' 1F1FF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 1   | H' 1F200 ~ H' 1F3FF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 2   | H' 1F400 ~ H' 1F5FF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 3   | H' 1F600 ~ H' 1F7FF | 小ブロック<br>エリア |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 4   | H' 1F800 ~ H' 1F9FF | (4 K バイト)    |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 5   | H' 1FA00 ~ H' 1FBFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 6   | H' 1FC00 ~ H' 1FDFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

| S B 7   | H' 1FE00 ~ H' 1FFFF |              |                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                     |              | H' 00000<br>H' 03FFF<br>H' 04000<br>H' 07FFF<br>H' 08000<br>H' 0BFFF<br>H' 0C000<br>H' 0FFFF<br>H' 10000<br>H' 13FFF<br>H' 14000<br>H' 17FFF<br>H' 18000<br>H' 1BFFF<br>H' 1C000<br>H' 1EFFF<br>H' 1F000<br>H' 1F1FF<br>H' 1F200<br>H' 1F3FF<br>H' 1F400<br>H' 1F5FF<br>H' 1F600<br>H' 1F7FF<br>H' 1F800<br>H' 1F9FF<br>H' 1FA00<br>H' 1FBFF<br>H' 1FC00<br>H' 1FDFF<br>H' 1FE00<br>H' 1FFFF |

|         |                     |              | 16 k バイト<br>16 k バイト<br>12 k バイト<br>512 バイト                  |

図18.8 消去ブロックの分割

#### 18.5.4 RAMコントロールレジスタ (RAMCR)

RAMコントロールレジスタ (RAMCR) は、フラッシュメモリのリアルタイムな書き換えをエミュレートする際に使用するRAMエリアを選択するレジスタです。

| ビット: | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|------|---|---|---|---|------|------|------|------|

| FLER | — | — | — | — | RAMS | RAM2 | RAM1 | RAM0 |

初期値: 0 1 1 1 0 0 0 0

R/W: R — — — R/W R/W R/W R/W

##### ビット7: フラッシュメモリエラー (FLER)

ビット7は、フラッシュメモリへの書き込み、消去中に異常が発生し、エラーが生じたことを示すビットです。このビット7がセットされると、フラッシュメモリはエラープロテクトモード<sup>1</sup>に遷移します。

| ビット7 | 説明                                                                                                                                                                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FLER |                                                                                                                                                                                                                                                                                                                                |

| 0    | フラッシュメモリへの書き込み／消去プロテクト（エラープロテクト <sup>1</sup> ）が無効（クリア条件）<br>リセットまたはハードウェアスタンバイモードのとき<br>(初期値)                                                                                                                                                                                                                                  |

| 1    | フラッシュメモリへの書き込み、消去中にエラーが発生し、エラープロテクト <sup>1</sup> が有効となったことを示す<br>(セット条件)<br>(1) 書込み、消去中にフラッシュメモリをリード <sup>2</sup> したとき（ベクタリードおよび命令フェッチを含む。ただし、フラッシュメモリ空間とオーバラップしたRAMエリアのリードは除く）。<br>(2) 書込み、消去中の例外処理（ただし、リセット、トレース、不当命令、トランプ命令、ゼロ除算時の例外処理は除く）の実行直後。<br>(3) 書込み、消去中にSLEEP命令（ソフトウェアスタンバイモードを含む）を実行したとき。<br>(4) 書込み、消去中にバス開放したとき。 |

【注】<sup>1</sup> エラープロテクトの詳細は「18.7.8 プロテクトモード」を参照してください。

<sup>2</sup> このときリードした値は不定となります。

##### ビット6～4: リザーブビット

ビット6～4はリザーブビットです。ビット6～4をリードすると、常に1が読み出されます。ライトは無効です。

### ビット3: RAMセレクト (RAMS)

ビット2～0と共に使用し、RAMエリアを設定します（表18.11）。リセット、またはハードウェアスタンバイモード時にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

1ライト時は、フラッシュメモリ全ブロックの書き込み／消去プロテクト状態となります。

### ビット2～0: RAM2～0

ビット3と共に使用し、RAMエリアを設定します（表18.11）。リセット、またはハードウェアスタンバイモード時にイニシャライズされます。ソフトウェアスタンバイモード時にはイニシャライズされません。

表18.11 RAMエリアの設定方法

| RAMエリア            | ビット3 | ビット2 | ビット1 | ビット0 |

|-------------------|------|------|------|------|

|                   | RAMS | RAM2 | RAM1 | RAM0 |

| H'FFF000～H'FFF1FF | 0    | 0／1  | 0／1  | 0／1  |

| H'01F000～H'01F1FF | 1    | 0    | 0    | 0    |

| H'01F200～H'01F3FF | 1    | 0    | 0    | 1    |

| H'01F400～H'01F5FF | 1    | 0    | 1    | 0    |

| H'01F600～H'01F7FF | 1    | 0    | 1    | 1    |

| H'01F800～H'01F9FF | 1    | 1    | 0    | 0    |

| H'01FA00～H'01FBFF | 1    | 1    | 0    | 1    |

| H'01FC00～H'01FDFF | 1    | 1    | 1    | 0    |

| H'01FE00～H'01FFFF | 1    | 1    | 1    | 1    |

## 18.6 オンボードプログラミングモード

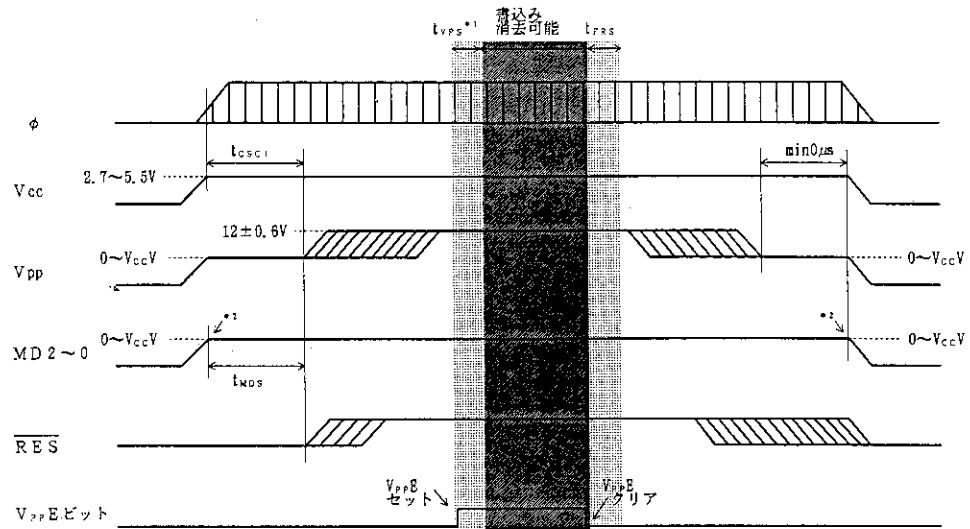

オンボードプログラミングモードに設定すると、内蔵フラッシュメモリのプログラム、消去、ベリファイを行うことができます。本モードには、2種類の動作モード（ブートモード、ユーザプログラムモード）があります。これらのモードは、モード端子（MD<sub>2</sub>～MD<sub>0</sub>）、V<sub>PP</sub>端子により設定します。表18.12にオンボードプログラミングモードの設定方法を示します。V<sub>PP</sub>の印加／切断時の注意については「18.10 フラッシュメモリの書き込み／消去時の注意」を参照してください。

表18.12 オンボードプログラミングモードの設定

| モード設定       |      | V <sub>PP</sub> | MD <sub>2</sub> | MD <sub>1</sub> | MD <sub>0</sub> | 備考                                         |

|-------------|------|-----------------|-----------------|-----------------|-----------------|--------------------------------------------|

| ブートモード      | モード5 | 12V             | 12V             | 0               | 1               | 0 : V <sub>IL</sub><br>1 : V <sub>IH</sub> |

|             | モード6 |                 | 12V             | 1               | 0               |                                            |

|             | モード7 |                 | 12V             | 1               | 1               |                                            |

| ユーザプログラムモード | モード5 | 1               | 1               | 0               | 1               |                                            |

|             | モード6 |                 | 1               | 1               | 0               |                                            |

|             | モード7 |                 | 1               | 1               | 1               |                                            |

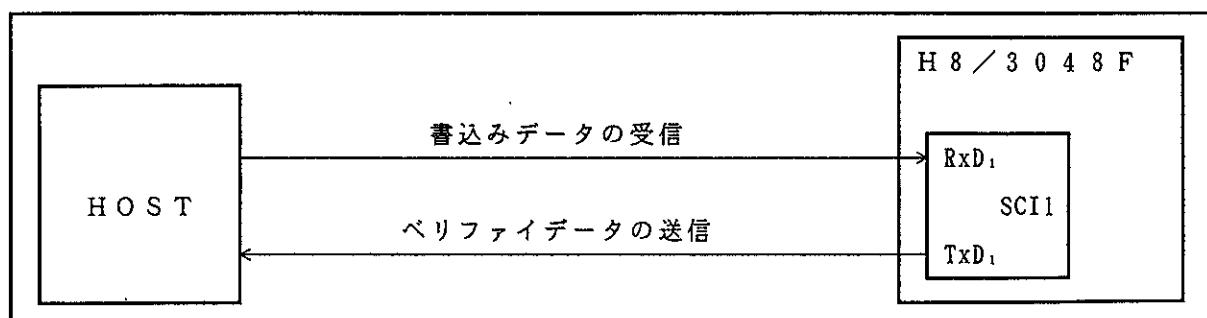

### 18.6.1 ブートモード

ブートモードを使用する場合には、あらかじめフラッシュメモリへの書き込み用のユーザプログラムをホスト側のパソコン等に準備しておく必要があります。また、使用するS C Iは、チャネル1の調歩同期式モードに設定されています。H'8048Fをブートモードに設定すると、リセット解除後、あらかじめ組み込まれているブートプログラムが起動され、ホストから送信されるデータの“Low”期間をまず測定し、ビットレートレジスタ（B R R）の値を決定します。次に、H'8048F内蔵のシリアルコミュニケーションインターフェース1（S C I 1）を用いて外部からのユーザプログラムの受信が可能となり、受信されたユーザプログラムは、R A Mに書き込まれます。

書き込み終了後、内蔵R A Mの先頭アドレス（モード5・7設定時H'FF300、モード6設定時H'FFF300）に分岐し、R A M上に書き込まれたプログラムを実行し、フラッシュメモリの書き込み、消去が可能となります。ブートモードの実行手順を図18.10に示します。

図18.9 ブートモードシステム構成図

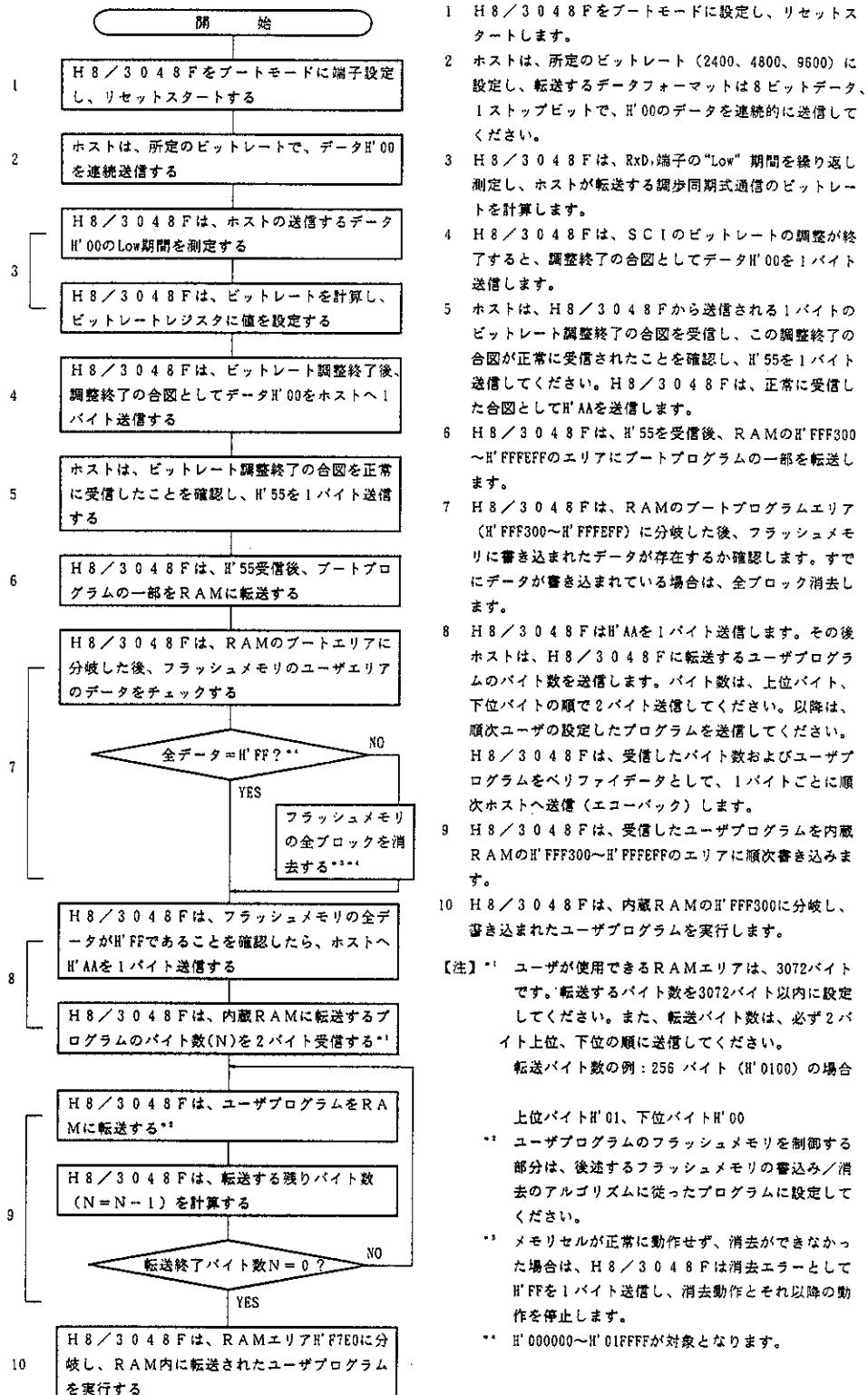

## ■ ブートモードの実行手順

ブートモードの実行手順を以下に示します。

図18.10 ブートモードの動作フロー チャート

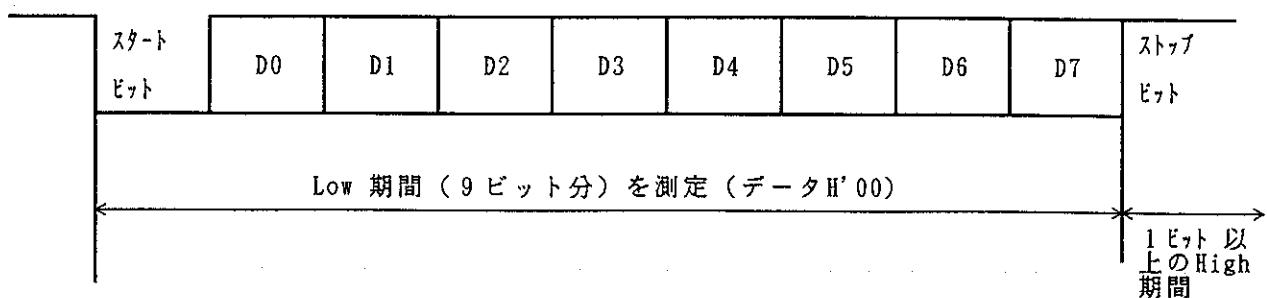

## ■ S C I ビットレートの自動合わせ込み動作

図18.11 ホスト送信データの“Low”期間の測定

ブートモードを起動すると、H 8／3048Fは、ホストより送信される調歩同期式S C I通信のデータの“Low”期間を測定します（図18.11）。このデータフォーマットは、8ビットデータ、1ストップビット、パリティなしのフォーマットです。H 8／3048Fは、測定した“Low”期間（9ビット）よりホストの送信するビットレートを計算します。H 8／3048Fは、ビットレートの調整が終わると、ビット調整終了合図としてホストへ1バイトのH'00データを送信します。ホストは、この調整終了合図を正常に受信したことを確認し、H 8／3048FへH'55を1バイト送信してください。受信が正常に行われない場合は、再度ブートモードでリセット起動し、“Low”期間の測定を実行してください。ホストが送信するビットレート、およびH 8／3048Fのシステムクロックの周波数によってホストとH 8／3048Fのビットレートに誤差が発生します。正常にS C I動作を行うために、ホストの転送ビットレートを2400、4800または9600 b p s<sup>\*1</sup>に設定してください。ホストの代表的な転送ビットレートとH 8／3048Fのビットレートの自動合わせ込みが可能なシステムクロックの周波数を表18.13に示します。このシステムクロックの範囲内でブートモードを実行してください。<sup>\*2</sup>

表18.13 H 8／3048Fのビットレートの自動合わせ込みが可能なシステムクロックの周波数

| ホストのビットレート<br>*1 | H 8／3048Fのビットレートの自動合わせ込みが可能な<br>システムクロックの周波数 |

|------------------|----------------------------------------------|

| 9600 b p s       | 8 MHz ~ 16MHz                                |

| 4800 b p s       | 4 MHz ~ 16MHz                                |

| 2400 b p s       | 2 MHz ~ 16MHz                                |

【注】\*1 ホストのビットレートは2400、4800、9600 b p sの設定のみで、それ以外の設定は使用しないでください。

\*2 H 8／3048Fは、表18.13に示すビットレートとシステムクロックの組合せ以外でも、自動合わせ込みを行う場合がありますが、ホストとH 8／3048Fのビットレートに誤差が生じ、その後の転送が正常に行われないことがあります。このため、ブートモードの実行は、表18.13に示す組合せの範囲内で必ず行ってください。

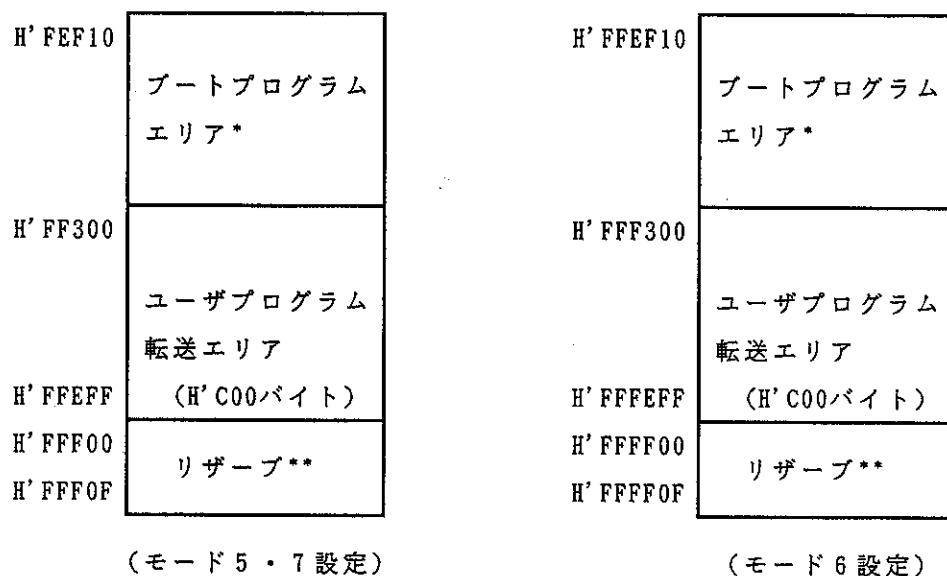

## ■ ブートモード時のRAMエリアの分割

ブートモードでは、モード5・7設定時:H' FEF10～H' FF2FF、モード6設定時:H' FFEF10～H' FFF2FF(H' 3F0バイト)は、図18.12に示すようにブートプログラムで使用するエリアとしてリザーブされています。ユーザのプログラムを転送するエリアはモード5・7設定時:H' FF300～H' FFEFF、モード6設定時:H' FFF300～H' FFFEFF(H' C00バイト)です。ブートプログラムのエリアは、RAM内に転送したユーザプログラムの実行状態に遷移すると使用できます。

図18.12 ブートモード時のRAMエリア

【注】\* RAM内に転送したユーザプログラム実行状態に遷移（モード5・7設定時:H' FF300、モード6設定時:H' FFF300に分岐）するまで本エリアを使用できません。なお、ユーザプログラムに分岐後もRAM内のブートプログラムエリア（モード5・7設定時:H' FEF10～H' FF2FF、モード6設定時:H' FFEF10～H' FFF2FF）にはブートプログラムがそのまま保持されていますので、注意してください。

\*\* リザーブ領域は使用しないでください。

## ■ ブートモード使用時の注意事項

- (1) H8/3048Fは、ブートモードでリセット解除すると、SCI1のRxD<sub>1</sub>端子の“Low”期間を測定します。RxD<sub>1</sub>端子が“High”的状態でリセット解除してください。リセット解除後、H8/3048FがRxD<sub>1</sub>端子へ入力させる“Low”期間を測定できるようになるまでは約100ステート必要です。

- (2) ブートモードは、フラッシュメモリに書き込まれているデータがある場合（全データがH'FFでないとき）、フラッシュメモリの全ブロックを消去します。本モードを実行する場合は、オンボード状態での初期の書き込み、あるいは、ユーザプログラムモードで起動するプログラムを誤って消去し、ユーザプログラムモードが実行できなくなった場合の強制復帰等に使用してください。

- (3) フラッシュメモリのプログラム中、あるいは消去中に割込みを使用することはできません。

- (4) RxD<sub>1</sub>端子およびTxD<sub>1</sub>端子は、ボード上でプルアップして使用してください。

- (5) H8/3048Fは、ユーザプログラム(RAMエリアのH'F300)に分岐するときに内蔵SCI(チャネル1)の送受信動作を終了（シリアルコントロールレジスタSCRのRE=0、TE=0）しますが、ビットレートレジスタBRR1には、合わせ込んだビットレートの値を保持しています。

また、このときトランスマットデータ端子TxD<sub>1</sub>は、“High”レベル出力状態（ポート9データディレクションレジスタのP91DDR=1、ポート9データレジスタのP91DR=1）となっています。

- さらにこのとき、CPU内蔵の汎用レジスタの値は不定です。このためユーザプログラムに分岐した直後に汎用レジスタのイニシャライズを必ず行ってください。特にスタックポインタ(SP)はサブルーチンコール時などに、暗黙的に使用されますので、ユーザプログラムで使用するスタックエリアを必ず指定してください。

- (6) ブートモードへの遷移は表18.12のモード設定条件に従って、MD<sub>2</sub>端子とV<sub>PP</sub>端子に12Vを印加後にリセットスタートすることにより可能です。

この時、H8/3048Fはリセット解除（Lowレベル→Highレベル立ち上がり）のタイミング<sup>\*1</sup>でモード端子の状態をマイコン内部にラッチし、ブートモード状態を保持します。

ブートモードを解除するためにはMD<sub>2</sub>端子とV<sub>PP</sub>端子への12V印加を解除した後にリセット解除<sup>\*2</sup>することにより可能ですが、以下のよう注意が必要です。

- (a) ブートモードから通常モード(V<sub>PP</sub>≠12V、MD<sub>2</sub>≠12V)へ遷移する場合は、モード遷移する前にマイコン内部のブートモード状態をRES端子によるリセット入力によって解除する必要があります。この時、V<sub>PP</sub>切断後からリセット解除して、リセットベクタをリードするまでの期間として、フラッシュメモリリードセットアップ時間(t<sub>FRS</sub>)が必要です<sup>\*3</sup>。

- (b) ブートモードの途中でMD<sub>2</sub>端子への12V印加を解除した場合は、RES端子によるリセット入力をしない限り、マイコン内部のブートモード状態は保持されており、ブートモードが継続されます。また、ブートモード状態でウォッチドッグタイマリセットが発生した場合、マイコン内部のモード状態は解除されず、モード端子の状態にかかわらず内蔵のブートプログラムが再起動されます。

- (c) ブートモードへの遷移時（リセット解除タイミング）及びブートモード動作中ではプログラム電圧V<sub>PP</sub>は12V±0.6Vの範囲を超えないようにしてください。これを超えると、ブートモードは正しく実行されません。また、ブートプログラム実行中やフラッシュメモリへの書き込み、消去中にV<sub>PP</sub>を切断しないでください\*<sup>2</sup>。

- (7) リセット中（RES端子にLowレベルを入力している期間）にMD<sub>2</sub>端子の入力レベルを0Vから12V、または12Vから0Vに変化させる場合、一瞬5V入力レベルに遷移することによりマイコン動作モードが切り替わります。このためアドレス兼用ポート及びバス制御出力信号（AS、RD、HWR、LWR）の状態が変化しますので、これらの端子はリセット中の出力信号として使用しないよう、マイコン外部で禁止する必要があります。

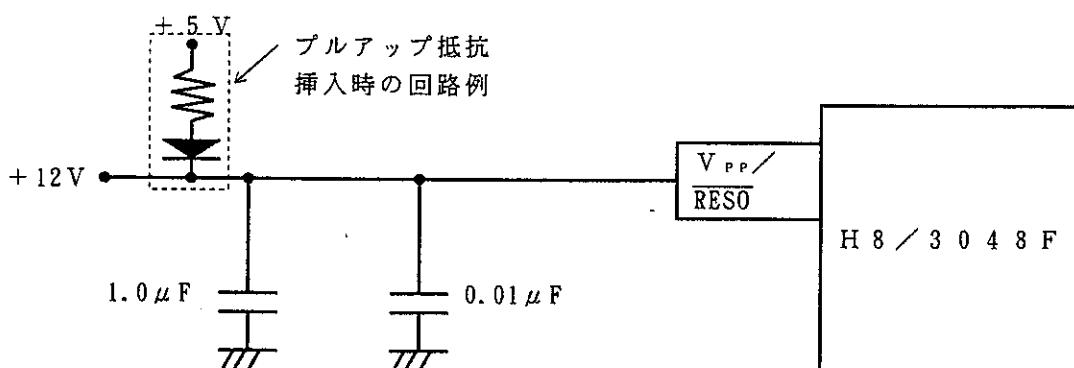

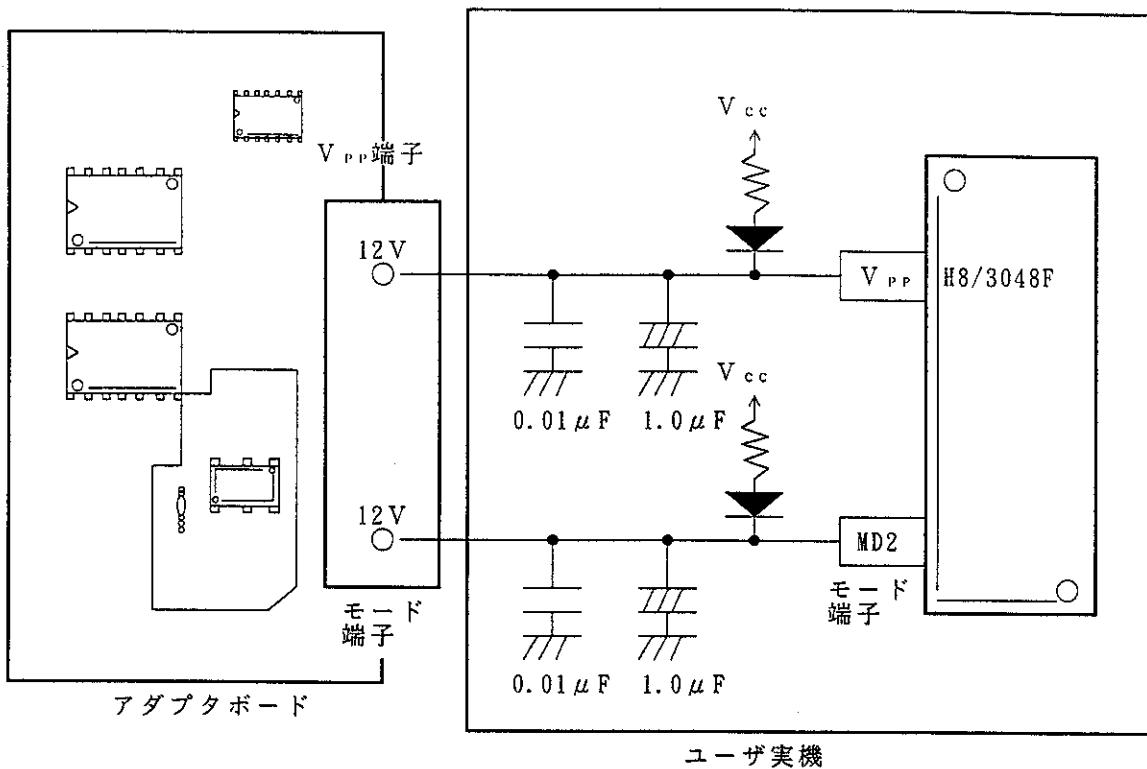

- (8) V<sub>PP</sub>およびMD<sub>2</sub>端子への12V印加は、オーバーシュートのピークが最大定格の13Vを超えないようにしてください。また、V<sub>PP</sub>およびMD<sub>2</sub>端子には、必ずバイパスコンデンサを接続してください。<sup>\*1</sup>

【注】<sup>\*1</sup> モード端子の入力は、リセット解除のタイミングに対し、モードプログラミングセットアップ時間（t<sub>MDS</sub>）を満足する必要があります。MD<sub>2</sub>端子への12V印加／切断時ではMD<sub>2</sub>端子に接続するプルアップ・プルダウン抵抗などの影響によって立下り・立上り波形に遅れが生じます。このためリセット解除のタイミングは、この遅れをボード上の実波形で確認してください。

<sup>\*2</sup> V<sub>PP</sub>の印加／切断の注意については「18.10 フラッシュメモリへの書き込み／消去時の注意」の(4)を参照してください。

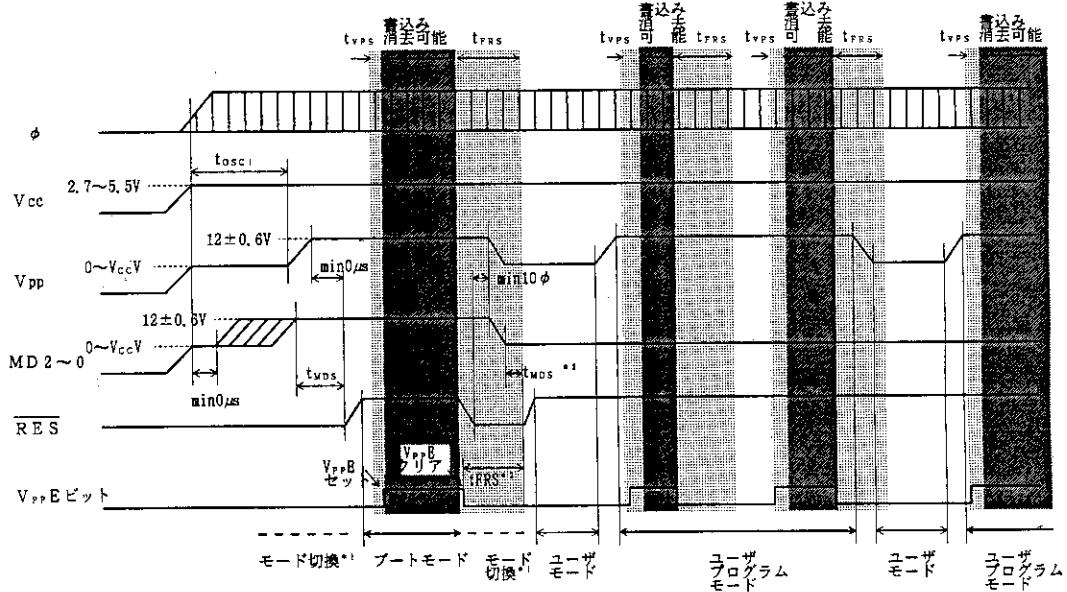

## 18.6.2 ユーザプログラムモード

H8／3048Fをユーザプログラムモードに設定すると、ユーザプログラムによるフラッシュメモリの消去、書き込みが可能になります。したがって、あらかじめ基板上にV<sub>PP</sub>供給手段、および書き換えデータ供給手段を設け、プログラムエリアの一部に書き換え用プログラムを内蔵させておくことにより、内蔵フラッシュメモリのオンボード書き換えを行うことができます。

本モードの設定は、内蔵ROMの有効なモード、モード5、6、7に設定しV<sub>PP</sub>端子に12V印加します。このモードの動作では、フラッシュメモリ以外の周辺機能は、モード5、6、7と同じ動作をします。

ただし、V<sub>PP</sub>端子に12V印加中は、WDTのオーバフロー時にリセット出力はできません。WDTのリセット出力イネーブル（RSTOE）を1にセットしないでください。

なお、書き込み、消去を行っている間、フラッシュメモリを読み出すことはできませんので、書き換えプログラムを外部メモリ上に置くか、または書き換えプログラムをいったんRAMエリアに転送し、RAM内で実行してください。

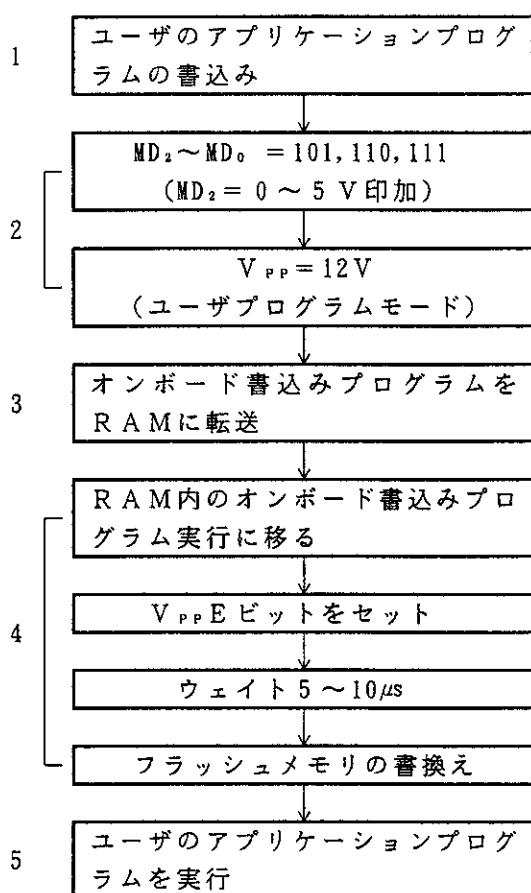

## ■ ユーザプログラムモード実行手順例

RAM内で実行する場合のユーザプログラムモード実行手順を以下に示します。

### 〈手順〉

- 1 ユーザは、あらかじめ以下に示す3～5の動作を実行するプログラムをフラッシュメモリに書き込みます。

- 2 端子をユーザプログラムモードに設定します。

- 3 リセットにより、CPUを起動し、オンボード書き込みプログラムをRAM内部に転送します。

- 4 RAM内のプログラムに分岐し、オンボード書き込みプログラムの実行に移ります。

フラッシュメモリの書き換えのため、FLMCRのVPEビットをセットします。

内部電源の安定化のため、5～10μs待ちます。

- 5 書換えプログラムを実行します。

書換え終了後、VPEビットをクリアし、書き込み終ったユーザのアプリケーションプログラムに分岐し、実行します。

VPEビットをクリア後、フラッシュメモリ内のプログラムを実行する前にフラッシュメモリリードセットアップ時間( $t_{PRS}$ )が必要です。

図18.13 ユーザプログラムモード動作例

【注】 プログラム暴走等による誤書き込み、誤消去を防止するため、VPPに12Vを印加するのはフラッシュメモリに書き込み、消去を行うときのみ（RAMによるフラッシュメモリのエミュレーション実行時も含む）とし、常時12Vを印加しないでください。また、書き込み／消去時（12V印加時）は、ウォッチドッグタイマを起動し、プログラムの暴走等に対応できるようにしてください。プログラム暴走等によって過剰書き込み、過剰消去になるとメモリセルが正常に動作しないことがあります。VPPの印加／切断時の注意については「18.10 フラッシュメモリの書き込み／消去時の注意」を参照してください。

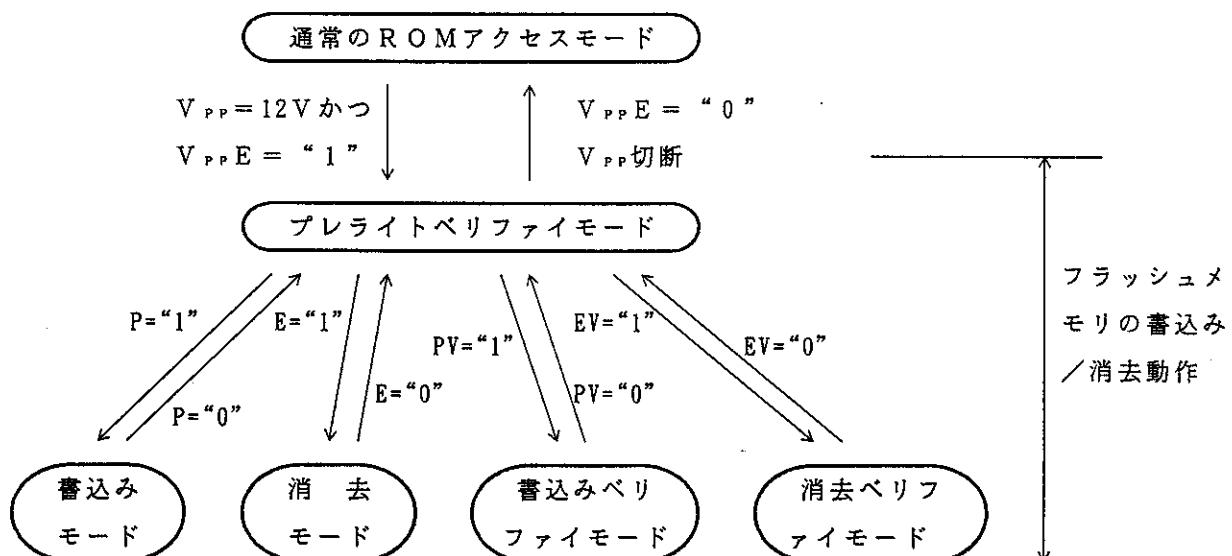

## 18.7 フラッシュメモリの書き込み／消去

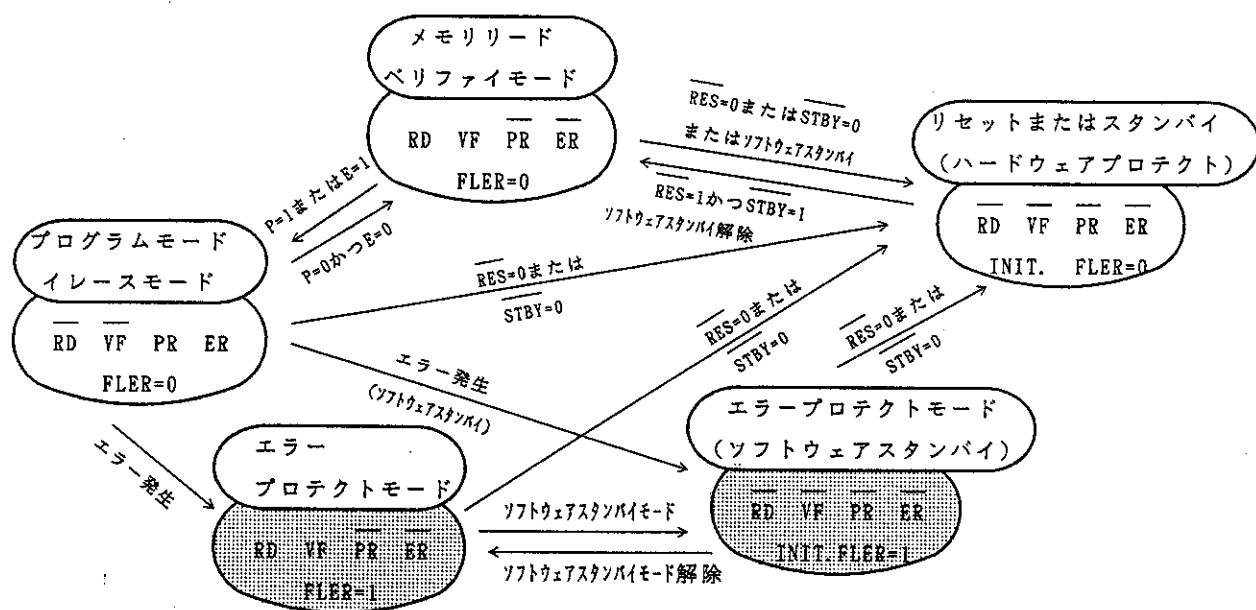

H8/3048Fに内蔵するフラッシュメモリは、CPUを用いてソフトウェアで書き込み、消去を行う方式を採用しています。フラッシュメモリの動作モードと状態遷移図を図18.14に示します。書き込み／消去モードには、書き込みモード、消去モード、書き込みベリファイモード、消去ベリファイモード、プレライトベリファイモードがあります。フラッシュメモリコントロールレジスタ（FLMCR）のPビット、Eビット、PVビット、EVビットのいずれかのビットをセットすることにより各動作モードに遷移することができます。また、FLMCRの全てのビットをクリアした状態でプレライトベリファイモードとなります。

フラッシュメモリは、書き込み、あるいは消去を行っている間読み出すことはできません。フラッシュメモリの書き込み、消去を制御するプログラムは、内蔵RAMあるいは外部メモリ上に置き、実行してください。以下に各動作モードの説明と、推奨する書き込みフロー、消去フローおよびプログラム例を示します。書き込み、消去のアルゴリズムは、各ステップごとに書き込み／消去の処理時間を2倍にする高信頼性アルゴリズムを採用しています。

書き込み、消去時の注意は「18.10 フラッシュメモリの書き込み／消去時の注意」を参照してください。

図18.14 フラッシュメモリ書き込み／消去動作モードの状態遷移図

【注】 P、E、PV、EVビットは、同時にセット／クリアを行わないでください。

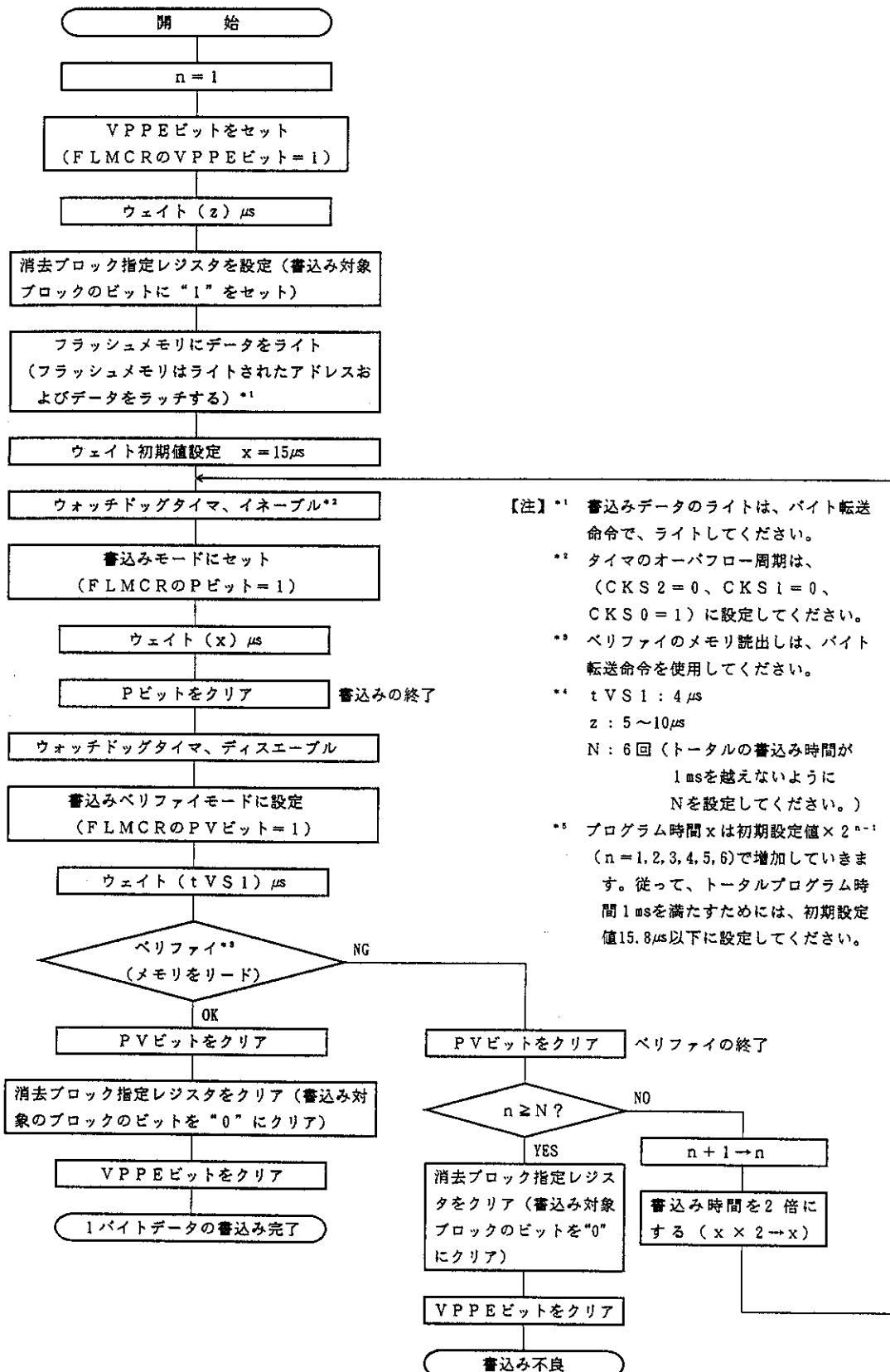

### 18.7.1 書込みモード

フラッシュメモリへのデータの書き込みは、図18.15に示す書き込みアルゴリズムに従ってください。この書き込みアルゴリズムは、デバイスへの電圧ストレスあるいはプログラムデータの信頼性を損なうことなく、書き込みを行うことができます。

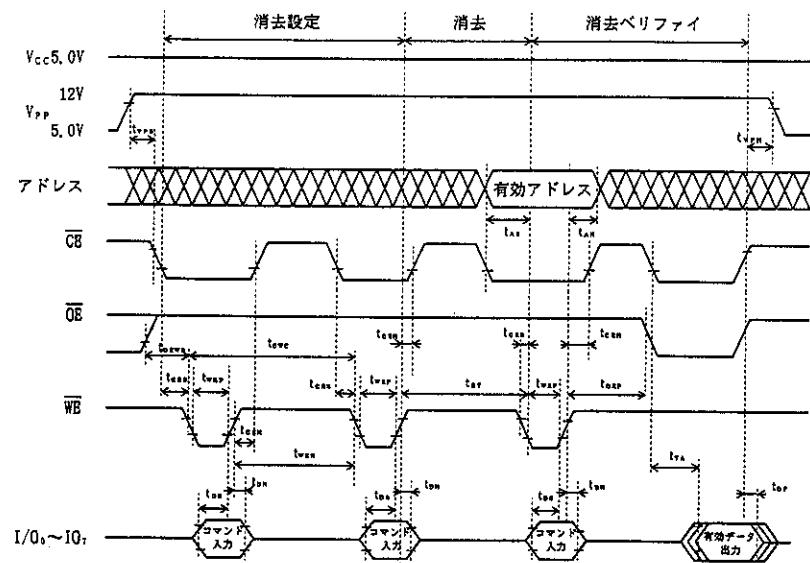

データの書き込みは、F L M C RのV<sub>PP</sub>Eビットをセットし、5～10μsの待機時間を経過した後、フラッシュメモリの書き込むエリアを消去ブロック指定レジスタ1、2（E B R 1、E B R 2）で設定し、書き込むアドレスにRAMと同様にデータをライトします。フラッシュメモリは、プログラムアドレスと、プログラムデータをアドレスラッチ、データラッチに各々ラッチします。F L M C RのPビットをセットし、動作モードをプログラムモードに設定します。Pビットをセットしている時間が書き込み時間になります。一回目の書き込み時間は、ソフトウェアタイマで、15.8μs以下になるように設定してください。また、プログラムの暴走等により、過剰時間書き込みをするとデバイスにダメージを与えます。プログラムモードに設定する前に、あらかじめウォッチドッグタイマを設定し、過剰に書き込みを起こすことのないようにしてください。

### 18.7.2 書込みペリファイモード

書き込みペリファイモードは、書き込みモードでデータを書き込んだあとそのデータを読み出し、正常に書き込まれているかを確認するモードです。

書き込み時間経過後、書き込みモードを解除（Pビット=0）し、書き込みペリファイモード（P Vビット=1）に設定してください。書き込みペリファイモードは、ラッチしたアドレスのメモリセルに書き込みペリファイ電圧を印加します。この状態で、フラッシュメモリをリードするとラッチしたアドレスのデータが読み出されます。リード動作は、書き込みペリファイモードに設定後、4μsの待機時間を置いて行ってください。書き込んだデータとペリファイデータを比較し、一致した場合、書き込みペリファイモードを解除し、次のアドレスの書き込みを行ってください。一致しなかった場合は、再度書き込みモードに設定し、同様に書き込み、書き込みペリファイシーケンスを繰り返します。ただし、同一ビットに対する書き込み、書き込みペリファイシーケンスの繰り返しは、6回を越えないでください（トータル書き込み時間が1msを越えないように回数を設定してください）。

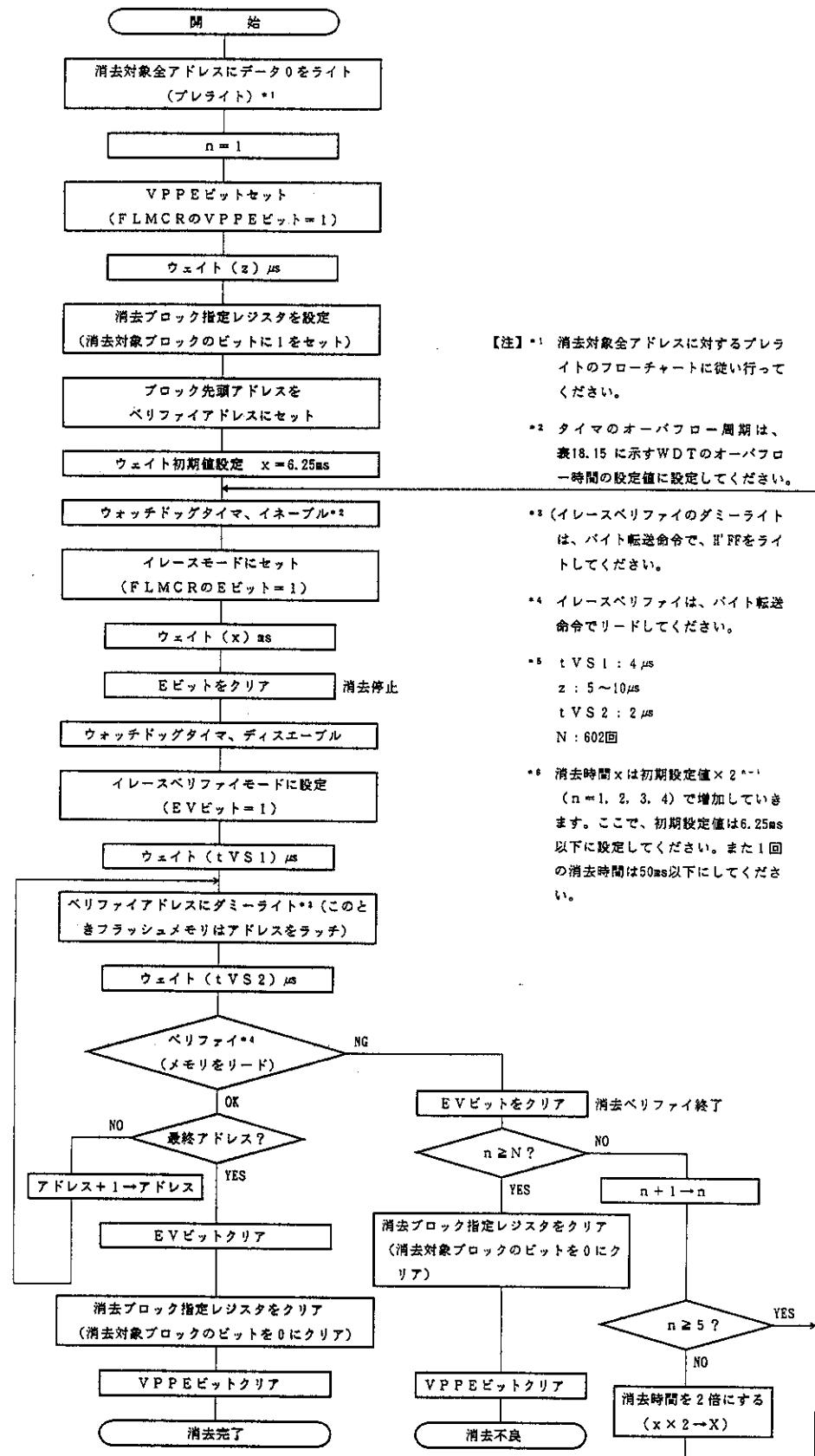

### 18.7.3 書込みのフローチャートとプログラム例

■ 1 バイト書込みのフローチャート

図18.15 書込みフローチャート

## ■ 1 バイト書込みのプログラム例

### 使用レジスタと使用方法

R 0 : プログラムベリファイのフェイルカウントに用います。

R 1 : プログラムベリファイのループカウンタ値の設定に用います。

E R 2 : プログラムアドレスをロングワードデータで格納します。アドレス設定はH'00000000～H'0001FFFFが有効です。

R 3 H : プログラムデータをバイトデータで格納します。

R 4 : T C S R 、 F L M C R の設定およびクリアに用います。

E 4 : プログラムループカウンタの初期値を格納します。

R 5 : F L M C R のクリアに用います。

E 5 : プログラムループカウンタの値を格納します。

E R 2 (プログラムアドレス) および R 3 H (プログラムデータ) の値を設定することにより、任意のデータを任意のアドレスに書込むことが可能です。

# a 、 # b および # g の値は動作周波数によって異なります。表18.14の計算方法によって算出してください。

```

FLMCR: .EQU      FFFF40

EBR1:  .EQU      FFFF42

EBR2:  .EQU      FFFF43

TCSR:  .EQU      FFFFA8

PRGM:  MOV.W #0001, R0      ; プログラムベリファイフェイルカウント

MOV.W #g,   R1      ; プログラムループカウンタの設定

MOV.W #4140, R4      ;

MOV.B  R4L,   @FLMCR:8 ; VPEビットセット

LOOP0: DEC.W #1,   R1      ;

BPL   LOOP0

MOV.B  #**,   R0H      ;

MOV.B  R0H,   @EBR*:8 ; EBR*セット

MOV.B  R3H,   @ER2      ; ダミーライト

MOV.W #a,   E4      ; プログラムループカウンタの初期値設定

PRGMS: MOV.W #A579, R4      ; WDTスタート

MOV.W R4,   @TCSR:16 ;

MOV.W E4,   E5      ; プログラムループカウンタ設定

MOV.W #4140, R4      ;

MOV.B  R4H,   @FLMCR:8 ; Pビットセット

LOOP1: DEC.W #1,   E5      ; プログラム

BPL   LOOP1

;

```

#### 18.7.4 消去モード

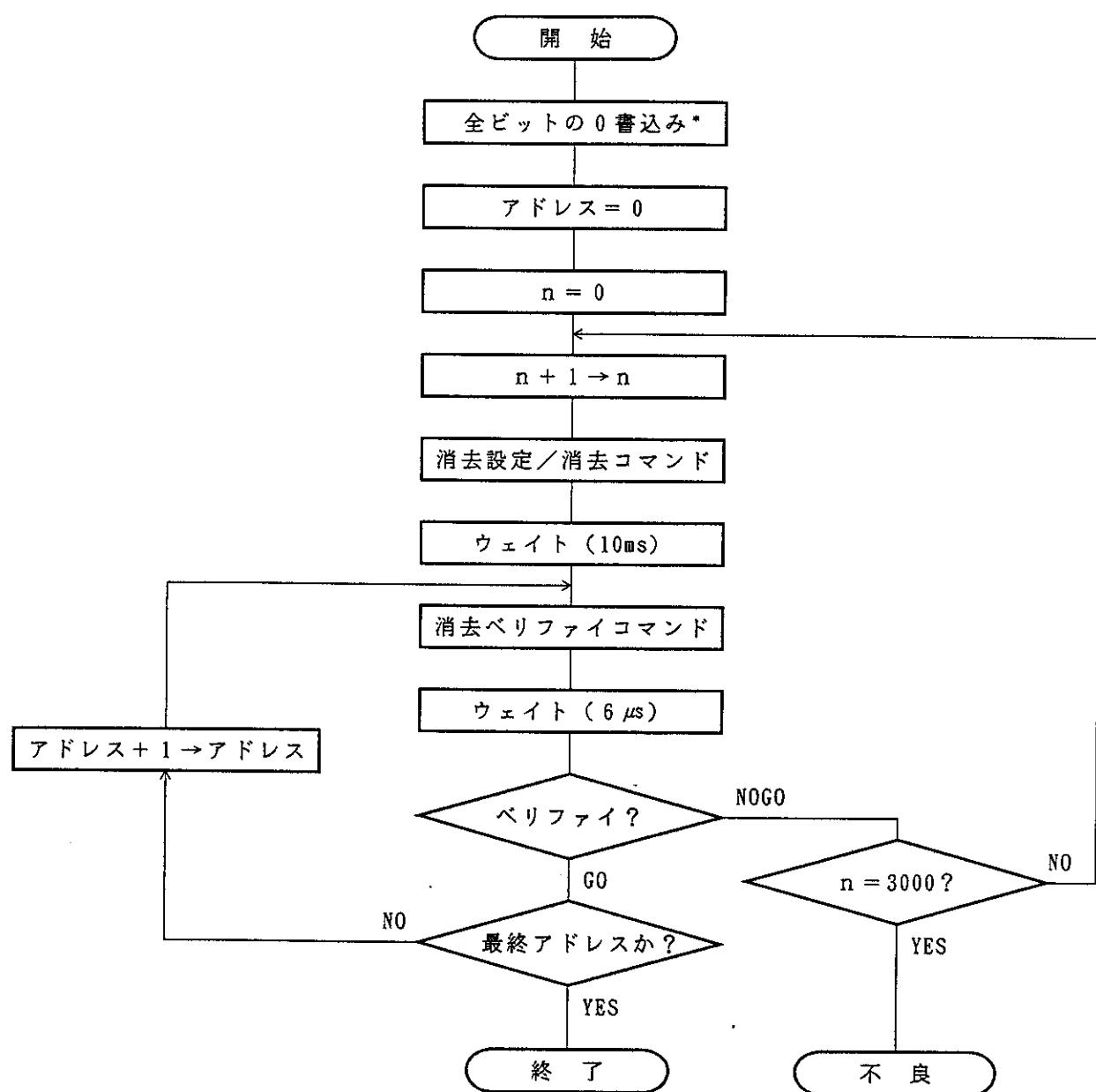

フラッシュメモリの消去は、図18.16に示す消去アルゴリズムに従い行ってください。この消去アルゴリズムは、デバイスへの電圧ストレス、あるいはプログラムデータの信頼性を損なうことなく、消去を行うことができます。

フラッシュメモリの消去では、消去を開始する前に消去するブロックの全メモリデータが書き込まれた状態（全メモリデータ：H'00）にしてください。全メモリデータが書き込まれた状態でない場合は、後述するシーケンスに従い全メモリデータに0を書き込んでください。フラッシュメモリの消去するエリアの指定は、FLMCRのV<sub>pp</sub>Eビットをセットし5～10μsの待機時間を経過した後、消去ブロック指定レジスタ1、2（EBR1、EBR2）で設定します。FLMCRのEビットをセットし、動作モードを消去モードに設定します。Eビットをセットしている時間が消去時間になります。消去は、過消去にならないよう、消去時間をソフトウェアタイマで分割して実行してください。プログラムの暴走等により、消去し過ぎるとしきい値電圧が負になりメモリセルが正常に動作しなくなりますので、消去モードに設定する前に、あらかじめウォッチドッグタイマを設定し、過消去を起こすことのないようにしてください。

#### 18.7.5 消去ベリファイモード

消去ベリファイモードは、消去した後データを読み出し、正常に消去されているかどうかを確認するモードです。消去時間経過後、消去モードを解除（Eビット=0）し、消去ベリファイモード（EVビット=1）に設定してください。設定した後、4μsの待機時間をとってください。消去ベリファイモードは、リードする前にリードするアドレスにデータH'FFをダミーライトしてください。このダミーライトにより、ラッチしたアドレスのメモリセルに消去ベリファイ電圧が印加されます。この状態でフラッシュメモリをリードするとラッチしたアドレスのデータが読み出されます。リード動作は、ダミーライト後、2μsの待機時間を経過した後行ってください。読み出したデータが消去されていた場合、次のアドレスをダミーライトし2μsの待機時間を経過した後消去ベリファイを行います。読み出したデータが未消去の場合は、再度消去モードに設定し、同様に消去、消去ベリファイシーケンスを最終アドレスまで繰り返します。ただし、この消去、消去ベリファイシーケンスの繰り返しは、602回を越えない範囲で全メモリデータが1になるまで行ってください。

### 18.7.6 消去のフローチャートとプログラム例

## ■ 1 ブロック消去のフロー チャート

図18.16 消去フローチャート

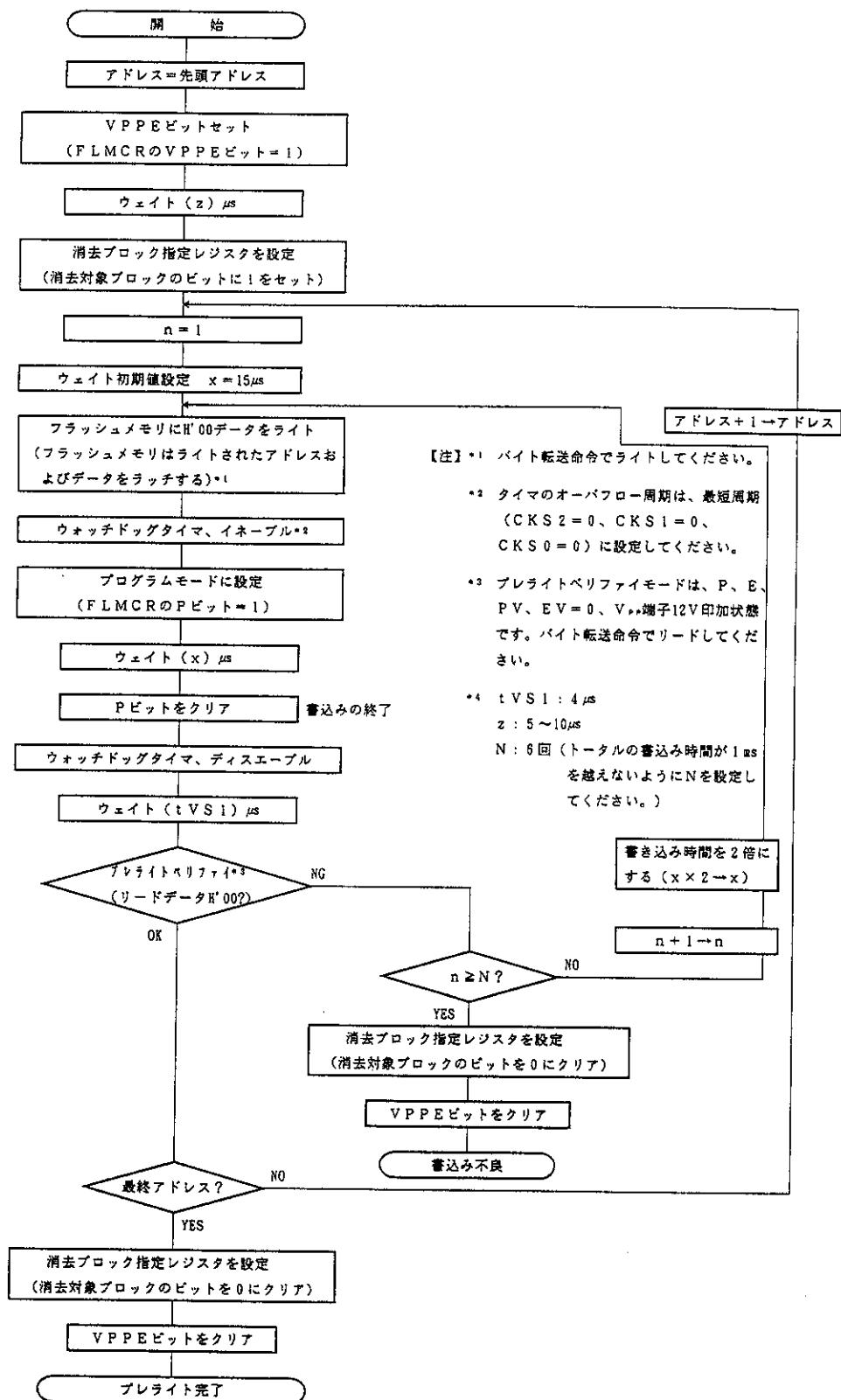

## ■ プレライトのフローチャート

図18.17 プレライトフローチャート

## ■ 1 ブロック消去のプログラム例

### 使用レジスタと使用方法

R 0 : プレライトベリファイおよびイレースベリファイのフェイルカウンタに用います。

ER 1 : プレライトに用いるアドレスを格納します。

ER 2 : プレライトおよびイレースベリファイに用いるアドレスを格納します。

ER 3 : イレースベリファイに用いるアドレスを格納します。

ER 3 : イレースベリファイに用いるアドレスを格納します。

ER 4 : ループカウンタ値の設定に用います。

R 5 : 各レジスタの設定に用います。

R 6 : 各レジスタの設定に用います。

プログラム中の # a、# c、# d、# e、# f、# g、# h の値は動作周波数によって異なります。

表18.14および表18.15の計算方法によって算出してください。

```

FLMCR: .EQU      FFFF40

EBR1:  .EQU      FFFF42

EBR2:  .EQU      FFFF43

TCSR:  .EQU      FFFFA8

```

```

; # BLKSTRは消去するブロックの先頭アドレスを設定してください。

; # BLKENDは消去するブロックの最終アドレスを設定してください。

MOV.L    #BLKSTR:32, ER1    ; ER1: 消去対象ブロックの先頭アドレス

MOV.L    #BLKEND:32, ER2    ; ER2: 消去対象ブロックの最終アドレス

```

### ； プレライト実行

```

PREWRT: MOV.W    #g,      R4      ; ウエイトカウタの設定

MOV.W    #4140,   R6      ;

MOV.B    R6L,     @FLMCR:8 ; VppEビットセット

LOOPRO: DEC.W    #1,      R4      ;

BPL     LOOPRO          ;

```

； 消去するブロックに対応するEBR1またはEBR2のビットをセットしてください。

```

MOV.B    #**,     R5H      ;

MOV.B    R5H      @EBR*    ; EBR*セット

PREWRN: SUB.B    R0H,     R0H      ; R0: プレライトベリファイフェイルカウント

MOV.W    # a ,    E4      ; プレライト ループカウンタの初期値設定

PREWRS: MOV.B    #00      R5H      ; データ#00をライト

MOV.B    R5H,     @ER1    ;

MOV.W    #A579,   R5      ; WDT スタート

```

```

MOV.W    R5,      @TCSR:16 ;

MOV.W    E4,      R4      ; プレライト ループカウント設定

MOV.W    #4140,   R6      ;

MOV.B    R6H,     @FLMCR:8 ; PEビットセット

LOOPR1: DEC.W   #1,      R4      ; プレライト

BPL     LOOPR1      ;

MOV.B    R6L,     @FLMCR:8 ; PEビットクリア

MOV.W    #A500,   R5      ; WDTストップ

MOV.W    R5,      @TCSR:16 ;

MOV.W    # c ,    R5      ; プレライトペリファイ ループカウントの設定

LOOPR2: DEC.W   #1,      R5      ; ウェイト

BPL     LOOPR2      ;

MOV.B    @ER1,    R5H     ; リードデータ=#00?

BEQ     PWVFOK      ; リードデータ=#00ならばPWVFOKに分岐

CMP.B    #05,    R0H     ; プレライトペリファイ 6 回実行?

BEQ     ABEND1      ; プレライトペリファイ 6 回実行ならばABEND1に分岐

SHLL.W   E4       ; プレライトループカウントを 2 倍

INC.B    R0H     ; プレライトペリファイ フェイルカウント+1 -> R0H

BRA     PREWRS      ; 再プレライト処理

PWVFOK: CMP.L   ER2,    ER1     ; 最終アドレス?

BEQ     ERASES      ;

INC.L    #1,      ER1     ; アドレス+1 -> R1

BRA     PREWRN      ; 最終アドレスでなければ次アドレスのプレライト

```

```

; イレース実行

ERASES: SUB.W   R0,      R0      ; R0:イレースペリファイ フェイルカウント

MOV.L    #BLKSTR:32,ER3   ; ER3:消去対象ブロックの先頭アドレス

MOV.W    # d ,    E4      ; イレースループカウント の初期値設定

ERASE: CMP.W    #025A,   R0      ; R0 = 025A? (イレースペリファイ フェイルカウント603回?)

BEQ     ABEND2      ; R0 = 025AならばABEND2に分岐

INC.W    #1,      R0      ; イレースペリファイフェイルカウント+1 -> R0

MOV.W    E4,      R4      ;

MOV.W    # f ,    R5      ; WDTスタート

MOV.W    R5,      @TCSR:16 ;

MOV.B    #42,    R5H     ; Eビット セット

MOV.B    R5H,     @FLMCR:8 ;

LOOPE: PUSH.L   ER5      ;

POP.L    ER5      ;

```

```

PUSH. L  ER5

POP. L  ER5

PUSH. L  ER5

POP. L  ER5

DEC. W  #1,    R4      ; イレース

BPL    LOOPE      ;

MOV. B  #40,    R5H      ;

MOV. B  R5H,    @FLMCR:8 ; EVビットクリア

MOV. W  #A500,  R5      ;

MOV. W  R5,    @TCSR:16 ; WDTストップ

```

; イレースペリファイ実行

```

MOV. B  #48,    R5H      ;

MOV. B  R5H,    @FLMCR:8 ; EVEットセット

MOV. W  # e ,   R4      ; R4: イレースペリファイループカウント

LOOPEV: DEC. W  #1,    R4      ;

BPL    LOOPEV      ; ウェイト

```

```

EVR2:  MOV. B  #FF,    R4H      ;

MOV. B  R4H,    @ER3      ; ダミーライト

MOV. W  # h ,   R4      ; R4: イレースペリファイループカウント

LOOPDW: DEC. W  #1,    R4      ;

BPL    LOOPDW      ; ウェイト

MOV. B  @ER3+,  R4H      ; リード

CMP. B  #FF,    R4H      ; リードデータ = #FF?

BNE    RERASE      ; リードデータ ≠ #FFならばRERASEに分岐

CMP. L  ER2,    ER3      ; ブロック最終アドレス?

BGT    EVR2      ; ブロック最終アドレスでなければ次アドレス イレースペリファイ

BRA    OKEND      ; OKENDに分岐

RERASE: MOV. W  #4000,  R5      ;

MOV. B  R5H,    @FLMCR:8 ; EVビットクリア

DEC. L  #1,    ER3      ; イレースペリファイアドレス-1 -> R3

CMP. W  #0004  R0      ;

BGE    KEEP      ; イレース4回目?

SHLL. W E4      ; イレースループカウントを2倍

KEEP:  BRA    ERASE      ; 再イレース

OKEND: MOV. W  #4000,  R5      ;

MOV. B  R5H,    @FLMCR:8 ; EVビットクリア

```

```

MOV.W #0000, R5      ;

MOV.W R5, @EBR1:16 ; EBR1とEBR2のクリア

MOV.B R5L, @FLMCR:8 ; VppEビットクリア

```

.....1ブロック消去完了

```

ABEND1: MOV.W    #0000,    R5      ;

MOV.W    R5,      @EBR1:16 ; EBR1とEBR2のクリア

MOV.B    R5L,     @FLMCR:8 ; VppEビットクリア

```

### 書き込み不良

```

ABEND2: MOV.W    #0000,  R5      ;

MOV.W    R5,    @EBR1:16 ; EBR1とEBR2のクリア

MOV.B    R5L,   @FLMCR:8 ; VppEビットクリア

```

## 消除不良

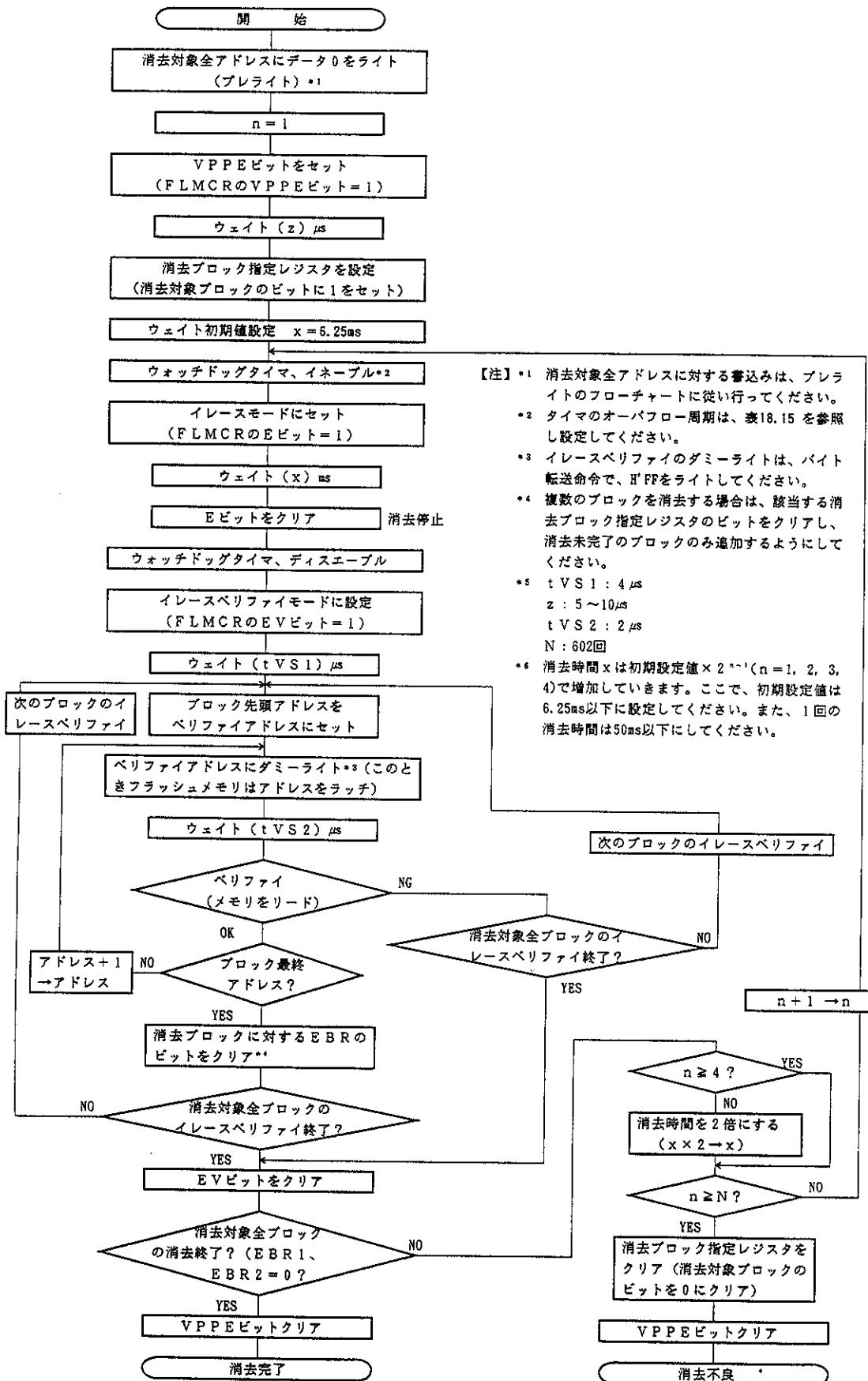

■ 複数ブロック消去のフローチャート

図18.18 複数ブロック消去フローチャート

## ■ 複数ブロック消去のプログラム例

### 使用レジスタと使用方法

R 0・R 6：イレースブロックの指定に用います。（後述の説明に従い設定してください。）

R 1 H：プレライトベリファイのフェイルカウントに用います。

R 1 L：R 0 の 0 ビットから 15 ビットをテストするのに使用します。

E R 2：プレライトおよびイレースベリファイ時に用いるアドレス格納番地を指定します。

E R 3：プレライトおよびイレースベリファイ時に用いるアドレスを格納します。

E R 4：プレライトおよびイレースベリファイ時に用いるアドレスを格納します。

E R 5：各種レジスタの設定に用います。

E 0・E 1：ループカウンタの設定に用います。

E 6：イレースベリファイのフェイルカウントに用います。

R 6 に設定する値により、任意のブロックを消去することが可能です。

R 6 の各ビットと、消去するブロックの対応とその具体例を以下に示します。

| ビット        | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R 6        | LB7 | LB6 | LB5 | LB4 | LB3 | LB2 | LB1 | LB0        | SB7 | SB6 | SB5 | SB4 | SB3 | SB2 | SB1 | SB0 |

| EBR1に対応します |     |     |     |     |     |     |     | EBR2に対応します |     |     |     |     |     |     |     |     |

### 【具体例】LB2、SB7、SB0を消去する場合

| ビット        | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8          | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R 6        | LB7 | LB6 | LB5 | LB4 | LB3 | LB2 | LB1 | LB0        | SB7 | SB6 | SB5 | SB4 | SB3 | SB2 | SB1 | SB0 |

| EBR1に対応します |     |     |     |     |     |     |     | EBR2に対応します |     |     |     |     |     |     |     |     |

設定値 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1

R 6 の設定は次のようになります。

MOV.W #0481, R6

MOV.W R6, @EBR1

プログラム中の # a、# c、# d、# e、# f、# g、# h の値は動作周波数によって異なります。表18.14および表18.15の計算方法によって算出してください。

プログラム中の #RAMSTR は、ROM内の本プログラムをRAMに転送する際のRAM先頭アドレスを入れてください。

```

FLMCR: .EQU FFFF40

EBR1: .EQU FFFF42

EBR2: .EQU FFFF43

TCSR: .EQU FFFFA8

```

; R0の値を設定してください。

```

START: MOV.W #FFFF, R6 ; 消去するブロックの選択 (R6:EBR1/EBR2)

```

```

MOV.W R6, R0 ; R0: EBR1/EBR2

SUB.W R1, R1 ; R1: R0のR1ビットテストを行うのに用いる

```

; #RAMSTRはプログラム転送先の先頭アドレス(RAM)を入れてください。(偶数に設定してください)

```

MOV.L #RAMSTR:32, ER2 ; 転送先の先頭アドレス (RAM)

ADD.L #ERVADR:32, ER2 ; #RAMSTR+#ERVADR→ER2

SUB.L #START:32, ER2 ; ER2: RAM内で用いるデータ領域のアドレス

```

```

PRETST: CMP.B #10, R1L ; R1L=#10 ?

BEQ ERASES ; R0の全ビットチェック終了ならERASESに分岐

```

```

CMP.B #08, R1L ;

BCC BC0 ;

BTST R1L, R0H ;

BNE PREWRT ;

BRA PWADD1 ;

BC0: BTST R1L, R0L ; R0のR1ビットをテスト

BNE PREWRT ; R0のR1ビットが1ならばPREWRTに分岐

```

```

PWADD1: INC.B R1L ; R1L+1→R1L

MOV.L @ER2+, ER3 ; ER2のデータインクリメント

BRA PRETST

```

; プレライト実行

```

PREWRT: MOV.L @ER2+, ER3 ; ER3: プレライトスタートアドレス

MOV.L @ER2, ER4 ; ER4: 次ブロックの先頭アドレス

MOV.W #g, E5 ; ウェイトカウント

MOV.W #4140, R5 ;

MOV.B R5L, @FLMCR:8 ; VppEビットセット

LOOPRO: DEC.W #1, E5 ;

BPL LOOPRO ;

MOV.W R6, @EBR1:16 ; EBRセット (R6:EBR1/EBR2)

```

```

PREW: MOV.B #01, R1H ; プレライトペリフェラルカウント

MOV.W #a, E0 ; プレライトループカウント 初期値設定

PREWRS: MOV.B #00, R5H ; データ#00をライト

MOV.B R5H, @ER3 ;

```

```

MOV.W  #A579, E5      ;

MOV.W  E5, @TCSR:16  ; WDT スタート

MOV.W  E0, E1      ; プログラム ループカウントの設定

MOV.W  #4140, R5

MOV.B  R5H, @FLMCR:8 ; Pビットセット

LOOPR1: DEC.W  #1, E1      ; プログラム

BPL   LOOPR1      ;

MOV.B  R5L, @FLMCR:8 ; Pビットクリア

MOV.W  #A500, R5

MOV.W  R5, @TCSR:16  ; WDT ストップ

MOV.W  # c, R5      ; プレライトペリファイル-ブカウント

LOOPR2: DEC.W  #1, R5

BPL   LOOPR2      ;

MOV.B  @ER3, R5H     ; リードデータ=#00 ?

BEQ   PWVFOK      ; リードデータ=#00ならばPWVFOKに分岐

PWVFNG: CMP.B  #06, R1H     ; プレライトペリファイ 6 回実行 ?

BEQ   ABEND1      ; プレライトペリファイ 6 回実行ならばABEND1に分岐

INC.B  R1H      ; プレライトペリファイ フェイルカウント+1→R1H

SHLL.W E0      ; プレライト-ブカウントを 2 倍

BRA   PREWRS      ; 再プレライト処理

PWVFOK: INC.L  #1, ER3      ; アドレス+1→ER3

CMP.L  ER4, ER3      ; 最終アドレス ?

BEQ   PWADD2      ;

BRA   PREW      ;

PWADD2: INC.B  R1L      ; R0のR1L+1ビットをテストするのに用いる

BRA   PRETST      ; PRETSTに分岐

; イレース実行

ERASES: MOV.W  R6, @EBR1:16 ; EBR1/EBR2の設定

SUB.W  E6, E6      ; E6: イレースペリファイ フェイルカウント

MOV.W  # d, E0      ; イレースループカウントの初期値設定

ERASE: MOV.W  # f, R5      ;

MOV.W  R5, @TCSR:16  ; WDT スタート

MOV.W  E0, E1      ; イレース ループカウントの設定

MOV.W  #4240, R5

MOV.B  R5H, @FLMCR:8 ; Eビットセット

LOOPE: PUSH.L ER5

POP.L  ER5

PUSH.L ER5

POP.L  ER5

PUSH.L ER5

POP.L  ER5

```

```

DEC. W      #1,      E1      ; イレース

BPL        LOOPE

MOV. B      R5L,     @FLMCR:8 ; Eビットクリア

MOV. W      #A500,   R5      ;

MOV. W      R5,      @TCSR:16 ; WDTストップ

; イレースペリファイ実行

EVR:   MOV. W      R6,      R0      ; R0: EBR1/EBR2

SUB. W      R1,      R1      ; R1: R0のR1ビットテストを行うのに用いる

; #RAMSTRは本プログラムの転送先であるRAMの先頭アドレスを入れてください

MOV. L      #RAMSTR:32, ER2      ; 転送先の先頭アドレス (RAM)

ADD. L      #ERVADR:32, ER2      ; #RAMSTR+#ERVADR→ER2

SUB. L      #START:32,  ER2      ; ER2: RAM内で用いるデータ領域のアドレス

MOV. B      #48,      R5H      ;

MOV. B      R5H,     @FLMCR:8 ; EVビットセット

MOV. W      # e ,     R5      ; R5: イレースペリファイル-ブカウントの設定

LOOPEV: DEC. W      #1,      R5      ; プログラム

BPL        LOOPEV      ; ウエイト

EBRTST: CMP. B      #10,     R1L      ; R1L=#10 ?

BEQ        HANTEI     ; R0の全ビットチェック終了ならHANTEIに分岐

CMP. B      #08,     R1L      ;

BCC        BC1

BTST       R1L,     R0H      ; R0H(EBR1)のR1ビットをテスト

BNE        ERSEVF     ;

BRA        ADD01      ;

BC1:   BTST       R1L,     R0L      ; R0L(EBR2)のR1ビットをテスト

BNE        ERSEVF     ; R0のR1ビットが1ならばERSEVFに分岐

ADD01: INC. B      R1L      ; R1L+1→R1L

MOV. L      @ER2+,   ER3      ; R2のダミーインクリメント

BRA        EBRTST

ERSEVF: MOV. L      @ER2+,   ER3      ; ER3: イレースペリファイするブロック先頭アドレス

MOV. L      @ER2,    ER4      ; ER4: 次ブロック先頭アドレス

EVR2:  MOV. B      #FF,      R5H      ;

MOV. B      R5H,     @ER3      ; ダミーライト

MOV. W      # h ,    R5      ; R5: イレースペリファイル-ブカウント

LOOPDW: DEC. W      #1,      R5      ;

BPL        LOOPDW      ; ウエイト

MOV. B      @ER3+,   R5L      ; リード

CMP. B      #FF,      R5L      ; リードデータ = #FF?

BNE        ADD02      ; リードデータ = #FFでなければADD02へ分岐

CMP. L      ER4,     ER3      ; ブロック最終アドレス?

BNE        EVR2       ; ブロック最終アドレスでなければEVR2へ分岐

```

--

```

CMP.B    #08,      R1L      ;

BCC      BC2      ;

BCLR     R1L,      R0H      ; R0H(EBR1)のR1Lビットをクリア

BRA     ADD02    ;

BC2:    BCLR     R1L,      R0L      ; R0L(EBR2)のR1Lビットをクリア

ADD02: INC.B     R1L      ;

BRA     EBRTST   ; 次の消去ブロックのイレースペリファイ

HANTEI: MOV.W    #4000,    R5       ;

MOV.B    R5H,      @FLMCR:8 ; EVビットクリア

MOV.W    R0,      @EBR1:16 ; イレースブロック完了のビットクリア

BEQ     EOWARI   ; EBR1/EBR2が全て0ならば消去正常終了

CMP.W    #025A,    E6       ; E6=025A? (イレースペリフェイルカウント602回?)

BEQ     ABEND2   ; E6=025AならばABEND2に分岐

INC.W    #1,       E6       ; イレースペリファイフェイルカウント+1→E6

CMP.W    #0004,    E6       ;

BGE     KEEP     ; イレース4回目?

SHLL.W   E0       ; イレースループカウントを2倍

KEEP:   BRA     ERASE   ; 再イレース

```

;-----< イレースペリファイ時のブロックアドレステーブル >-----

```

.ALIGN 2

ERVADR: .DATA.L 00000000 ; #0000 LB0

.DATA.L 00004000 ; #4000 LB1

.DATA.L 00008000 ; #8000 LB2

.DATA.L 0000C000 ; #C000 LB3

.DATA.L 00010000 ; #10000 LB4

.DATA.L 00014000 ; #14000 LB5

.DATA.L 00018000 ; #18000 LB6

.DATA.L 0001C000 ; #1C000 LB7

.DATA.L 0001F000 ; #1F000 SB0

.DATA.L 0001F200 ; #1F200 SB1

.DATA.L 0001F400 ; #1F400 SB2

.DATA.L 0001F600 ; #1F600 SB3

.DATA.L 0001F800 ; #1F800 SB4

.DATA.L 0001FA00 ; #1FA00 SB5

.DATA.L 0001FC00 ; #1FC00 SB6

.DATA.L 0001FE00 ; #1FE00 SB7

.DATA.L 00020000 ; #20000 FLASH AREA END ADDRESS

```

```

EOWARI: MOV.B    #00,      R5L      ;

MOV.B    R5L,      @FLMCR:8 ; VPEビットクリア

消去完了

ABEND1: MOV.W    #0000,    R5       ;

MOV.W    R5,      @EBR1:16 ; EBR1とEBR2のクリア

MOV.B    R5L,      @FLMCR:8 ; VPEビットクリア

書き込み不良

```

ABEND2: MOV.W #0000, R5 ;

MOV.W R5, @EBR1:16 ; EBR1とEBR2のクリア

MOV.B R5L, @FLMCR:8 ; VPE ビットクリア

消去不良

## ■ プログラム中のループカウンタ値およびWDTオーバフロー時間の設定

プログラム例中の a ~ h は動作周波数によって設定が変わります。

10MHzの場合を表18.14に示します。その他の動作周波数のときは、以下に示す計算式により算出してください。ただし、f に関しては表18.15に従って設定をしてください。

表18.14 プログラム中のループカウンタ値 (10MHz)

| 変 数                |       | a (f)   | b (f)   | c (f)   | d (f)   | e (f)   | g (f)   | h (f)   |

|--------------------|-------|---------|---------|---------|---------|---------|---------|---------|

| 動作周波数<br>f = 10MHz | 16進表示 | H' 0019 | H' 0007 | H' 0007 | H' 03B3 | H' 0007 | H' 0009 | H' 0004 |

|                    | 10進表示 | 25      | 7       | 7       | 947     | 7       | 9       | 4       |

(参) Program tVS1 tVS2 Erase tVS1 z tVS2

at write at pre-write at erase

### 【計算式】

$$a(f) \sim h(f) = \frac{\text{動作周波数 } f \text{ [MHz]}}{10} \times a(f=10) \sim h(f=10)$$

### 【計算例】 16MHzの場合

$$a(f) = \frac{16}{10} \times 25 = 40 \approx H' 0028$$

$$b(f) = \frac{16}{10} \times 7 = 11.2 \approx H' 000C$$

$$c(f) = \frac{16}{10} \times 7 = 11.2 \approx H' 000C$$

$$d(f) = \frac{16}{10} \times 947 = 1515.2 \approx H' 05EC$$

$$e(f) = \frac{16}{10} \times 7 = 11.2 \approx H' 000C$$

$$g(f) = \frac{16}{10} \times 9 = 14.4 \approx H' 000F$$

$$h(f) = \frac{16}{10} \times 4 = 6.4 \approx H' 0007$$

表18.15 WDTオーバフロー時間の設定

| 動作周波数 [MHz]     | 変 数 | f      |

|-----------------|-----|--------|

| 10MHz以上～16MHz以下 |     | H'A57F |

| 2MHz以上～10MHz未満  |     | H'A57E |

| 1MHz以上～2MHz未満   |     | H'A57D |

【注】ウォッチ・ドッグ・タイマ（WDT）の設定値は、WDTスタートからストップまでの間の書込み時間、消去時間を含んだ命令数で計算されています。このため、このプログラム例中のWDTスタートからストップまでの間に、さらに命令を追加しないでください。

#### 18.7.7 プレライトベリファイモード

プレライトベリファイモードは、消去前にしきい値電圧を揃えるため、全ビット“0”書込み後に使用するベリファイモードです。

全ビットの書込みは、図18.17に示すプレライトのアルゴリズムに従いH'00を書き込んでください。これにより、書込み後のフラッシュメモリの全データをH'00にしてください\*。所定の書込み時間経過後、書込みモードを解除（Pビット=0）し、プレライトベリファイモード（P、E、PV、EVビット=0）に設定してください。プレライトベリファイモードは、リードしたアドレスのメモリセルにプレライトベリファイ電圧を印加します。この状態でフラッシュメモリをリードすると、リードしたアドレスのデータが読み出されます。リード動作は、プレライトベリファイモードに設定後4μsの待機時間を置いて行ってください。

【注】プレライトのプログラム例は、消去フローのプログラム例を参照してください。

## 18.7.8 プロテクトモード

フラッシュメモリに対する書き込み／消去プロテクトは、ソフトウェアプロテクトとハードウェアプロテクトの二つのモードがあります。以下にこのプロテクトモードについて解説します。

### (1) ソフトウェアプロテクト

ソフトウェアプロテクトでは、フラッシュメモリコントロールレジスタ (FLMCR) のPビットおよびEビットをセットしても、プログラムモードまたはイレースモードへは遷移しません。このプロテクトの詳細を以下に示します。

| 項目            | 説明                                                                                                                        | 機能              |                 |                    |

|---------------|---------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------------|

|               |                                                                                                                           | 書き込み            | 消去              | ペリファイ <sup>1</sup> |

| ブロック指定プロテクト   | <p>消去ブロック指定レジスタ (EBR1、EBR2) によりブロック別に書き込み／消去プロテクトの設定が可能です。</p> <p>EBR1 および EBR2 をH'00に設定すると全ブロックが書き込み／消去プロテクト状態になります。</p> | 不可              | 不可              | 可                  |

| エミュレーションプロテクト | RAMコントロールレジスタ (RAMCR) のRAMSビットをセットすることにより、全ブロックの書き込み／消去プロテクト状態となります。                                                      | 不可 <sup>2</sup> | 不可 <sup>3</sup> | 可 <sup>2</sup>     |

【注】<sup>1</sup> プログラムペリファイ、イレースペリファイ、プレライトペリファイの3つのモードです。

<sup>2</sup> フラッシュメモリとオーバラップしたRAMエリアは除きます。

<sup>3</sup> 全ブロックが消去不可となり、ブロック別の指定はできません。

(2) ハードウェアプロテクト

ハードウェアプロテクトでは、フラッシュメモリに対する書込み、消去が強制的に禁止、中断された状態でフラッシュメモリコントロールレジスタ (FLMCR) および消去ブロック指定レジスタ (EBR1、EBR2) の設定はリセットされます。またエラープロテクトの場合はPビットおよびEビットをセット可能ですが、プログラムモードおよびイレースモードへは遷移しません。このハードウェアプロテクト状態の詳細を以下に示します。

| 項目                               | 説明                                                                                                                                                                                                                          | 機能   |                 |                    |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--------------------|

|                                  |                                                                                                                                                                                                                             | 書き込み | 消去              | ペリファイ <sup>1</sup> |

| プログラム電圧 (V <sub>PP</sub> ) プロテクト | V <sub>PP</sub> に12Vが印加されていないときには、FLMCR、EBR1、2はイニシャライズされ、書込み、消去が禁止された状態になります。このプロテクト状態にするためには、V <sub>PP</sub> 電圧が電源電圧V <sub>CC</sub> を越えないようしてください。 <sup>3</sup>                                                            | 不可   | 不可 <sup>2</sup> | 不可                 |

| リセット、スタンバイプロテクト                  | リセット (ウォッチドッグタイマリセットを含む) およびスタンバイ時はFLMCR、EBR1、2はイニシャライズされ、書込み、消去が禁止された状態になります。ただし、RES端子によるリセットでは、電源投入時は最低20ms (発振安定時間) の間、RES端子をLOWレベルに保持しないと確実にリセット状態になりません。また、動作中のリセットは最低10システムクロック (10φ) サイクルの間RES端子をLOWレベルに保持する必要があります。 | 不可   | 不可 <sup>2</sup> | 不可                 |

| エラープロテクト                         | フラッシュメモリへの書込み、消去中にマイコン動作中の異常を検出 (エラー発生 (FLER = 1)) した場合に、エラープロテクトが有効となります。このとき、FLMCR、EBR1、2の設定は保持しますが、エラーが発生した時点で書込み、消去を強制的に中断します。プロテクトの解除はリセットまたはハードウェアスタンバイのみです。詳細については、次頁のエラープロテクトを参照してください。                             | 不可   | 不可 <sup>2</sup> | 可                  |

【注】<sup>1</sup> プログラムペリファイ、イレースペリファイ、プレライトペリファイの3つのモード。

<sup>2</sup> 全ブロックが消去不可となり、ブロック別の指定はできません。

<sup>3</sup> 詳細については「18.10 フラッシュメモリの書込み／消去の注意」を参照してください。

## ■ エラープロテクト

フラッシュメモリへの書き込み、消去中（FLMCRのPビットまたはEビットがセットされた状態）に発生したマイコンの異常動作（書き込み／消去アルゴリズムに従っていない動作）がフラッシュメモリエラー（RAMCRのFLERビットがセット）として検出された場合に、フラッシュメモリはエラープロテクト状態へ遷移します（これはフラッシュメモリの動作状態を示すもので、これによりマイコンの動作が影響を受けることはありません）。

このとき、フラッシュメモリコントロールレジスタ（FLMCR）および消去ブロックレジスタ（EBR1、2）の設定は保持\*されていますが、エラーが発生した時点でプログラムモードまたはイレースモードを強制的に中断します。また、FLERビットがセットされた状態では、FLMCRのPビットまたはEビットの再設定を行ってもプログラムモードまたはイレースモードへ遷移することはできません。ただしFLMCRのPVビット、EVビットの設定は有効です。このため、エラープロテクト状態ではペリファイモードへの遷移は可能です。

このプロジェクト状態の解除はリセットまたはハードウェアスタンバイモードのみです。

【注】\* レジスタへのライトは可能です。ただし、ソフトウェアスタンバイモードに遷移した場合はレジスタはイニシャライズされます。

RD:メモリリード可

V F : ベリファイリード可

PR: プログラム可

ER : イレース可

RD: メモリリード不可

VF：ベリファイリード不可

PR：プログラム不可

### E.R. : イレース不可

INIT : レジスト (F1M)

C R E B R I

2) のイニシエータ

イニテッド

図18.19 フラッショメモリ状態遷移図

(モード5、6、7(内蔵ROMが有効)でプログラム電圧( $V_{pp}$ )印加時)

このエラーモードはフラッシュメモリへの書き込み、消去中にマイコンが暴走したり、書き込み／消去アルゴリズムに従っていない動作をした場合に発生する異常を検出することによって、過書きや過消去によるフラッシュメモリへのダメージを、極力防止することを目的とした機能です。

しかし、フラッシュメモリエラー（F L E R）ビットのセット条件以外の異常動作に対してはこの機能は無効です。また、このプロテクト状態に遷移するまでに相当な時間が経過している場合は、すでにフラッシュメモリにダメージを与えている可能性もあります。従って、この機能ではフラッシュメモリへのダメージを完全に防止することはできません。

このため、このような異常動作を防止するためには、プログラム電圧（V<sub>pp</sub>）が印加された状態では書き込み／消去アルゴリズムに従ってマイコンを正しく動作させることと、マイコンの異常をウォッチドックタイマ等でマイコン内部および外部で常に監視することが必要です。また、このプロテクトモードへ遷移した時点でのフラッシュメモリは誤書き込み、誤消去等により誤ったデータが書き込まれた状態であったり、強制停止によって書き込みや消去が不十分であるため、必ずブートモードによる強制復帰を行ってください。

ただし、メモリ内に過消去状態のメモリセルが存在すれば、ブートモードが正常に起動されない場合があります（H 8／3048Fの組み込みのブートプログラムは、フラッシュメモリエリアの一部にあり、メモリ内に過消去セルが存在するとブートプログラムも正常に読み出せなくなります）。

### 18.7.9 N M I 入力禁止条件

フラッシュメモリへの書き込み、消去中 (F L M C R の P ビットまたは E ビットがセット) 、およびブートモードのブートプログラム実行中 (ただし内蔵 R A M エリアに分岐するまでの期間<sup>\*1</sup>) は N M I 入力が禁止されます。

これは、以下のような動作状態を回避するためのものです。

- (1) 書込み、消去中に N M I 入力が発生することにより、書き込み／消去アルゴリズムに違反し、正常な動作が保証できなくなる。

- (2) 書込み／消去中の N M I 例外処理ではベクタリードが正常にできない<sup>\*2</sup>ため、結果としてマイコンが暴走してしまう。

- (3) ブートプログラム実行中に N M I 入力が発生すると正常なブートモードのシーケンスが実行できなくなる。

また、エラープログラム状態でフラッシュメモリコントロールレジスタ (F L M C R) の P ビットまたは E ビットが保持された状態でも N M I 入力は禁止状態となります。

しかし、V<sub>PP</sub>印加状態では N M I 入力が禁止されていないため、マイコンの外部で N M I 要求を制限する必要があります。

【注】<sup>\*1</sup> 内蔵 R A M のブートプログラムエリア (H' F F E F 10～H' F F F 2 F F 番地) に分岐するまでの期間を示します (この分岐はユーザプログラムの転送が完了した直後に発生します)。このため、R A M エリアに分岐した後は、書き込み消去以外の状態では N M I 入力が可能となります。

従って、ユーザプログラムによる初期書き込み (ベクタテーブルおよび N M I 処理プログラム等の書き込み) が完了するまでは、マイコン外部で N M I 要求を禁止する必要があります。

<sup>\*2</sup> この場合、以下の二つの理由によってベクタリードが正常に行われません。

- (1) 書込み、消去中 (F L M C R の P ビットまたは E ビットがセット) にフラッシュメモリのリードを行っても正しい値を読みだすことはできません (値は不定)。

- (2) N M I ベクタテーブルに値が書き込まれていない場合、N M I 例外処理が正しく実行されません。

## 18.8 RAMによるフラッシュメモリのエミュレーション

フラッシュメモリは、その消去や書き込みに時間がかかるため、パラメータ等のデータをリアルタイムに書き換えるながらチューニングを行うといった使い方が難しい場合があります。このような場合、フラッシュメモリのリアルタイムな書き換えをエミュレートするために、フラッシュメモリの小ブロックエリアにRAMの一部 (H'FFF000~H'FFF1FF) を重ね合わせて使うことができます。このRAMエリアの変更は、RAMコントロールレジスタ (RAMCR) のビット3~0によって行います。また、RAMエリアの変更後は、フラッシュメモリに重ね合わせたエリアと本来のRAMエリア (H'FFF000~H'FFF1FF) の2エリアからアクセスできます。表18.16にRAMエリアの設定方法を示します。

### RAMコントロールレジスタ (RAMCR)

| ビット:                | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0    |

|---------------------|---|---|---|---|------|------|------|------|

| FLER                | — | — | — | — | RAMS | RAM2 | RAM1 | RAM0 |

| 初期値 <sup>*1</sup> : | 0 | 1 | 1 | 1 | 0    | 0    | 0    | 0    |

| R/W:                | R | — | — | — | R/W  | R/W  | R/W  | R/W  |

【注】<sup>\*1</sup> ビット7およびビット3~0は、リセットまたはハードウェアスタンバイモード時にイニシャライズされます。ソフトウェアスタンバイモード時には、イニシャライズされません。

表18.16 RAMエリアの設定方法

| RAMエリア            | ビット3 | ビット2 | ビット1 | ビット0 |

|-------------------|------|------|------|------|

|                   | RAMS | RAM2 | RAM1 | RAM0 |

| H'FFF000~H'FFF1FF | 0    | 0/1  | 0/1  | 0/1  |

| H'01F000~H'01F1FF | 1    | 0    | 0    | 0    |

| H'01F200~H'01F3FF | 1    | 0    | 0    | 1    |

| H'01F400~H'01F5FF | 1    | 0    | 1    | 0    |

| H'01F600~H'01F7FF | 1    | 0    | 1    | 1    |

| H'01F800~H'01F9FF | 1    | 1    | 0    | 0    |

| H'01FA00~H'01FBFF | 1    | 1    | 0    | 1    |

| H'01FC00~H'01FDFF | 1    | 1    | 1    | 0    |

| H'01FE00~H'01FFFF | 1    | 1    | 1    | 1    |

■ フラッシュメモリのリアルタイムな書換えをエミュレートする例

図18.20 RAMのオーバラップ動作例

<手順>

- SYSCRのRAMEビットを“1”にセットして内蔵RAMを有効にします。

- リアルタイムな書換えを必要とするエリア(SB5)にRAMの一部(H'FFF000～H'FFF1FF)をオーバラップさせます。(RAMCRのビット3～0を“1”、“1”、“0”、“1”にセットします。)

- リアルタイムな書換えは、オーバラップさせたRAMを使って行います。

- 書換えデータ確定後、RAMのオーバラップを解除します(RAMSビットをクリア)。

- RAMのH'FFF000～H'FFF1FFに書き込まれたデータをフラッシュメモリ空間に書き込みます。

- 【注】

1. フラッシュメモリの小ブロックエリアにRAMの一部(H'FFF000～H'FFF1FF)を重ね合わせていた場合、この重ね合わせたフラッシュメモリのエリアは、アクセスできません。重ね合わせを解除することでアクセスできます。

2. RAMSビットを“1”にセットすると、RAM2～0ビットの値にかかわらず、フラッシュメモリの全ブロックに対して書き込み／消去プロテクトが有効となります。この状態ではフラッシュメモリコントロールレジスタ(FLMCR)のPビットまたはEビットをセットしてもプログラムまたはイレースモードに遷移しません。このため、フラッシュメモリエリアに実際に書き込み、消去を行う場合はRAMSビットを“0”にクリアしてください。

## 18.9 フラッシュメモリのPROMモード

### 18.9.1 PROMモードの設定

内蔵ROMがフラッシュメモリのH8/3048Fでは、フラッシュメモリのプログラム、消去可能なモードとして、オンボードプログラミングモード以外にPROMモードがあります。PROMモードでは、汎用PROMライタを用いて内蔵ROMに自由にプログラムを書き込むことができます。

表18.17にPROMモードの設定方法を示します。このPROMモードでは表18.18に示すソケットアダプタを必ず使用してください。

表18.17 PROMモードの設定方法

| 端子名                                                      | 設定          |

|----------------------------------------------------------|-------------|

| モード端子: MD <sub>2</sub> 、MD <sub>1</sub> 、MD <sub>0</sub> | Lowレベルを印加   |

| P8 <sub>0</sub> 端子、P8 <sub>1</sub> 端子、P9 <sub>2</sub> 端子 |             |

| STBY端子、HWR端子                                             | Highレベルを印加  |

| P5 <sub>0</sub> 端子、P5 <sub>1</sub> 端子、P8 <sub>2</sub> 端子 |             |

| RES端子                                                    | パワーオンリセット回路 |

| XTAL、EXTAL端子                                             | 発振回路        |

### 18.9.2 ソケットアダプタの端子対応とメモリマップ

プログラム書き込み/ベリファイは、汎用PROMライタに専用の100ピン-32ピン変換アダプタを取り付けて行います。表18.18にソケットアダプタの型名を示します。

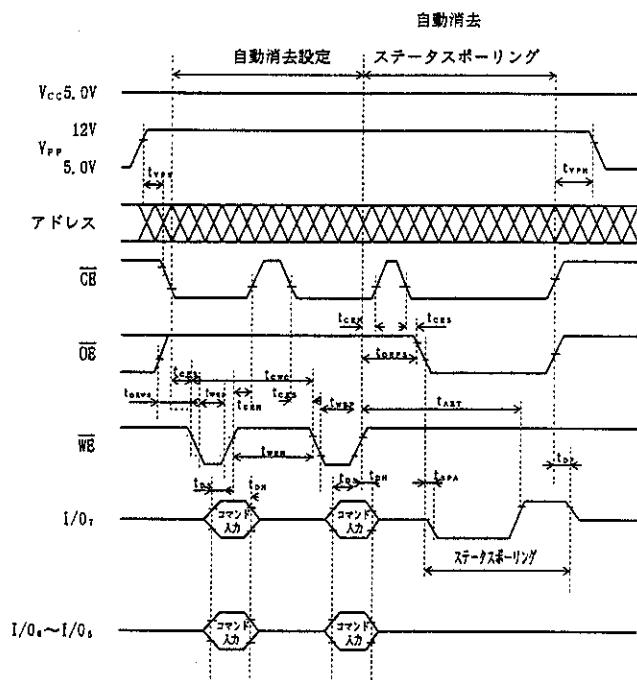

図18.21にPROMモードのメモリマップを示します。また、図18.22にソケットアダプタの端子対応図を示します。

表18.18 ソケットアダプタ型名

| 製品型名         | パッケージ名称                   | ソケットアダプタ型名   |

|--------------|---------------------------|--------------|

| HD64F3048F   |                           |              |

| HD64F3048VF  | 100ピンプラスチックQFP(FP-100B)   | HS3048ESHF1H |

| HD64F3048TF  |                           |              |

| HD64F3048VTF | 100ピンプラスチックTQFP(TFP-100B) | HS3048ESNF1H |

図18.21 PROMモード時のメモリマップ

\* FP-100B、TFP-100Bのピンピッチは、0.50mmと微細になっています。ICソケットからの抜き差しについては、適当な治具を用いて行うのが適切です。治具例を表18.19に示します。

表18.19 治具例

| メーカー     | 型番              |

|----------|-----------------|

| (株)エンプラス | HP-100(バキュームペン) |

| H 8 / 3 0 4 8 F      |                                                   | ソケットアダプタ        | HN28F101 (32ピン)  |      |

|----------------------|---------------------------------------------------|-----------------|------------------|------|

| ピン番号                 | 端子名                                               |                 | 端子名              | ピン番号 |

| FP-100B、<br>TFP-100B |                                                   |                 |                  |      |

| 10                   | RES0                                              |                 | V <sub>PP</sub>  | 1    |

| 64                   | NMI                                               |                 | A <sub>9</sub>   | 26   |

| 69                   | P6 <sub>s</sub>                                   |                 | A <sub>10</sub>  | 2    |

| 58                   | P6 <sub>o</sub>                                   |                 | A <sub>11</sub>  | 3    |

| 90                   | P8 <sub>s</sub>                                   |                 | WE               | 31   |

| 27                   | P3 <sub>o</sub>                                   |                 | I/O <sub>0</sub> | 13   |

| 28                   | P3 <sub>1</sub>                                   |                 | I/O <sub>1</sub> | 14   |

| 29                   | P3 <sub>2</sub>                                   |                 | I/O <sub>2</sub> | 15   |

| 30                   | P3 <sub>3</sub>                                   |                 | I/O <sub>3</sub> | 17   |

| 31                   | P3 <sub>4</sub>                                   |                 | I/O <sub>4</sub> | 18   |

| 32                   | P3 <sub>5</sub>                                   |                 | I/O <sub>5</sub> | 19   |