# 13. シリアルコミュニケーション インターフェース

## 第13章 目次

|                               |     |

|-------------------------------|-----|

| 13.1 概要                       | 485 |

| 13.1.1 特長                     | 485 |

| 13.1.2 ブロック図                  | 487 |

| 13.1.3 端子構成                   | 488 |

| 13.1.4 レジスタ構成                 | 488 |

| 13.2 各レジスタの説明                 | 489 |

| 13.2.1 レシーブシフトレジスタ (R S R)    | 489 |

| 13.2.2 レシーブデータレジスタ (R D R)    | 489 |

| 13.2.3 トランスマットシフトレジスタ (T S R) | 490 |

| 13.2.4 トランスマットデータレジスタ (T D R) | 490 |

| 13.2.5 シリアルモードレジスタ (S M R)    | 491 |

| 13.2.6 シリアルコントロールレジスタ (S C R) | 495 |

| 13.2.7 シリアルステータスレジスタ (S S R)  | 499 |

| 13.2.8 ビットレートレジスタ (B R R)     | 504 |

| 13.3 動作説明                     | 512 |

| 13.3.1 概要                     | 512 |

| 13.3.2 調歩同期式モード時の動作           | 514 |

| 13.3.3 マルチプロセッサ通信機能           | 523 |

| 13.3.4 クロック同期式モード時の動作         | 530 |

| 13.4 S C I 割込み                | 540 |

| 13.5 使用上の注意                   | 541 |

## 13.1 概要

H8/3048シリーズは、独立した2チャネルのシリアルコミュニケーションインターフェース(SCI : Serial Communication Interface)を備えています。2チャネルは、同一の機能を持っています。SCIは、調歩同期式通信とクロック同期式通信の2方式でシリアル通信ができます。また、複数のプロセッサ間のシリアル通信機能(マルチプロセッサ通信機能)を備えています。

消費電流低減のためSCIを使用しない場合には、SCI各チャネル単独に停止することができます。詳細は「20.6 モジュールスタンバイ機能」を参照してください。

また、SCI0については“ISO/IEC7816-3 (Identification Card)”に準拠したICカードインターフェース用シリアル通信機能としてスマートカードインターフェースをサポートしています。詳しくは「第14章 スマートカードインターフェース」を参照してください。

### 13.1.1 特長

SCIの特長を以下に示します。

■シリアル通信モードを調歩同期式モード／クロック同期式モードから選択可能

(a) 調歩同期式モード

キャラクタ単位で同期をとる調歩同期式方式でシリアルデータの通信を行います。Universal Asynchronous Receiver/Transmitter (UART) やAsynchronous Communication Interface Adapter (ACIA) など標準の調歩同期式通信用LSIとのシリアルデータ通信が可能です。また、複数のプロセッサとシリアルデータ通信ができるマルチプロセッサ間通信機能を備えています。

シリアルデータ通信フォーマットを12種類のフォーマットから選択できます。

- ・データ長：7ビット／8ビット

- ・ストップビット長：1ビット／2ビット

- ・parity：偶数parity／奇数parity／parityなし

- ・マルチプロセッサビット：“1”／“0”

- ・受信エラーの検出：parityエラー、オーバランエラー、フレーミングエラーを検出

- ・ブレークの検出：フレーミングエラー発生時にRXD端子のレベルを直接リードすることによりブレークを検出できます。

(b) クロック同期式モード

クロックに同期してシリアルデータ通信を行います。クロック同期式通信機能を持つ他のLSIとのシリアルデータ通信が可能です。

シリアルデータ通信フォーマットは1種類です。

- ・データ長：8ビット

- ・受信エラーの検出：オーバランエラーを検出

### ■全二重通信が可能

独立した送信部と受信部を備えているので、送信と受信を同時に行うことができます。

また、送信部、および受信部ともにダブルバッファ構造になっていますのでシリアルデータの連続送信、連続受信ができます。

### ■内蔵ボーレートジェネレータにより任意のビットレートを選択可能

### ■送受信クロックソースを、ボーレートジェネレータからの内部クロック、またはSCK端子からの外部クロックから選択可能

### ■4種類の割込み要因

送信データエンプティ、送信終了、受信データフル、受信エラーの4種類の割込み要因があり、それぞれ独立に要求することができます。また、SCI0については送信データエンプティ割込みと受信データフル割込みによりDMAコントローラ(DMAC)を起動させてデータの転送を行なうことができます。

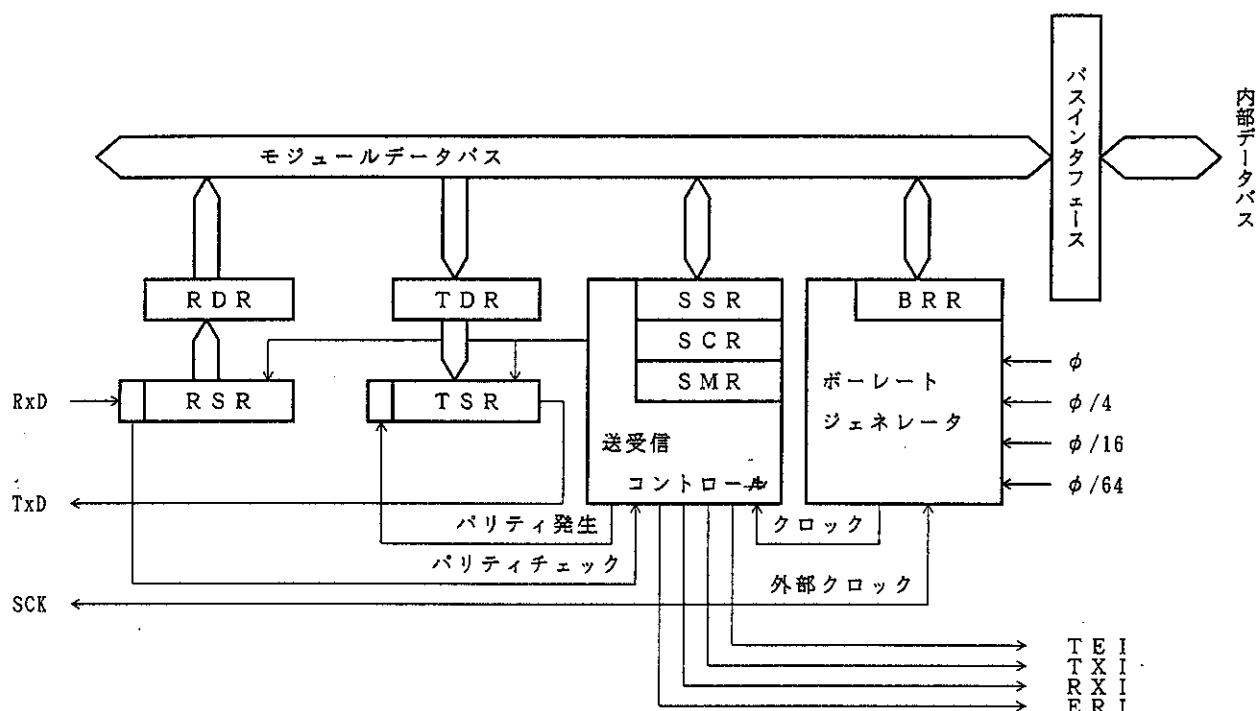

### 13.1.2 ブロック図

図13.1にS C Iのブロック図を示します。

#### 《記号説明》

- R S R : レシーブシフトレジスタ

- R D R : レシーブデータレジスタ

- T S R : トランスマットシフトレジスタ

- T D R : トランスマットデータレジスタ

- S M R : シリアルモードレジスタ

- S C R : シリアルコントロールレジスタ

- S S R : シリアルステータスレジスタ

- B R R : ビットレートレジスタ

図13.1 S C Iのブロック図

### 13.1.3 端子構成

SCIは、チャネルごとに表13.1に示すシリアル端子を持っています。

表13.1 端子構成

| チャネル | 名 称          | 略 称              | 入出力 | 機 能                       |

|------|--------------|------------------|-----|---------------------------|

| 0    | シリアルクロック端子   | SCK <sub>0</sub> | 入出力 | SCI <sub>0</sub> のクロック入出力 |

|      | レシーブデータ端子    | RxD <sub>0</sub> | 入力  | SCI <sub>0</sub> の受信データ入力 |

|      | トランスミットデータ端子 | TxD <sub>0</sub> | 出力  | SCI <sub>0</sub> の送信データ出力 |

| 1    | シリアルクロック端子   | SCK <sub>1</sub> | 入出力 | SCI <sub>1</sub> のクロック入出力 |

|      | レシーブデータ端子    | RxD <sub>1</sub> | 入力  | SCI <sub>1</sub> の受信データ入力 |

|      | トランスミットデータ端子 | TxD <sub>1</sub> | 出力  | SCI <sub>1</sub> の送信データ出力 |

### 13.1.4 レジスタ構成

SCIには、表13.2に示す内部レジスタがあります。これらのレジスタにより調歩同期式モード／クロック同期式モードの指定、データフォーマットの指定、ビットレートの指定、および送信部／受信部の制御を行うことができます。

表13.2 レジスタ構成

| チャネル | アドレス <sup>*1</sup> | 名 称            | 略 称  | R / W                 | 初期値  |

|------|--------------------|----------------|------|-----------------------|------|

| 0    | H'FFB0             | シリアルモードレジスタ    | S MR | R / W                 | H'00 |

|      | H'FFB1             | ビットレートレジスタ     | B RR | R / W                 | H'FF |

|      | H'FFB2             | シリアルコントロールレジスタ | S CR | R / W                 | H'00 |

|      | H'FFB3             | トランスミットデータレジスタ | T DR | R / W                 | H'FF |

|      | H'FFB4             | シリアルステータスレジスタ  | S SR | R / (W) <sup>*2</sup> | H'84 |

|      | H'FFB5             | レシーブデータレジスタ    | R DR | R                     | H'00 |

| 1    | H'FFB8             | シリアルモードレジスタ    | S MR | R / W                 | H'00 |

|      | H'FFB9             | ビットレートレジスタ     | B RR | R / W                 | H'FF |

|      | H'FFBA             | シリアルコントロールレジスタ | S CR | R / W                 | H'00 |

|      | H'FFBB             | トランスミットデータレジスタ | T DR | R / W                 | H'FF |

|      | H'FFBC             | シリアルステータスレジスタ  | S SR | R / (W) <sup>*2</sup> | H'84 |

|      | H'FFBD             | レシーブデータレジスタ    | R DR | R                     | H'00 |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> フラグをクリアするための“0”ライトのみ可能です。

## 13.2 各レジスタの説明

### 13.2.1 レシーブシフトレジスタ (R S R)

R S R は、シリアルデータを受信するためのレジスタです。

ビット :

R / W :

— — — — — — — —

S C I は、R S R にRxD端子から入力されたシリアルデータをL S B (ビット0) から受信した順にセットし、パラレルデータに変換します。1バイトのデータ受信を終了すると、データは自動的にR D Rへ転送されます。

C P U からR S R を直接リード／ライトすることはできません。

### 13.2.2 レシーブデータレジスタ (R D R)

R D R は、受信したシリアルデータを格納するレジスタです。

ビット :

初期値 :

0 0 0 0 0 0 0 0

R / W :

R R R R R R R R

S C I は、1バイトのシリアルデータの受信が終了すると、R S R からR D Rへ受信したシリアルデータを転送して格納し、受信動作を完了します。この後、R S R は受信可能になります。

このように、R S R とR D R はダブルバッファになっているため連続した受信動作が可能です。

R D R は、リード専用レジスタですのでC P U からライトすることはできません。

R D R は、リセット、またはスタンバイモード時にH'00にイニシャライズされます。

### 13.2.3 トランスマットシフトレジスタ (T S R)

T S Rは、シリアルデータを送信するためのレジスタです。

R/W : — — — — — — — —

S C Iは、T D Rから送信データを一旦T S Rに転送し、L S B（ビット0）から順にTxD端子に送り出すことでシリアルデータ送信を行います。

1バイトのデータ送信を終了すると自動的にT D RからT S Rへ次の送信データを転送し、送信を開始します。ただしL S S RのT D R Eビットが“1”にセットされている場合には、T D RからT S Rへのデータ転送は行いません。

C P Uから、直接T S Rをリード／ライトすることはできません。

### 13.2.4 トランスマットデータレジスタ (T D R)

T D Rは、シリアル送信するデータを格納する8ビットのレジスタです。

初期値 : 1 1 1 1 1 1 1 1

R/W : R/W R/W R/W R/W R/W R/W R/W R/W

S C Iは、T S Rの空を検出すると、T D Rにライトされた送信データをT S Rに転送してシリアル送信を開始します。T S Rのシリアルデータ送信中にT D Rに次の送信データをライトしておくと、連続シリアル送信ができます。

T D Rは、常にC P Uによるリード／ライトが可能です。

T D Rは、リセット、またはスタンバイモード時にH'FFにイニシャライズされます。

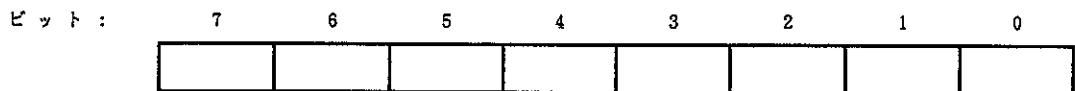

### 13.2.5 シリアルモードレジスタ (S M R)

S M R は、S C I のシリアル通信フォーマットの設定と、ボーレートジェネレータのクロックソースを選択するための 8 ビットのレジスタです。

ビット :

|  | 7   | 6   | 5  | 4   | 3    | 2  | 1    | 0    |

|--|-----|-----|----|-----|------|----|------|------|

|  | C/A | CHR | PE | 0/E | STOP | MP | CKS1 | CKS0 |

初期値 : 0 0 0 0 0 0 0 0 0

R/W : R/W R/W R/W R/W R/W R/W R/W R/W R/W

S M R は、常にC P U によるリード／ライトが可能です。

S M R は、リセット、またはスタンバイモード時にH'00にイニシャライズされます。

### ビット7：コミュニケーションモード（C/A）

S C I の動作モードを調歩同期式モード／クロック同期式モードのいずれかから選択します。

| ビット7 | 説明         |

|------|------------|

| C/A  |            |

| 0    | 調歩同期式モード   |

| 1    | クロック同期式モード |

### ビット6：キャラクタレンジス（C H R）

調歩同期式モードのデータ長を7ビット／8ビットデータのいずれかから選択します。クロック同期式モードではC H Rの設定にかかわらず、データ長は8ビットデータ固定です。

| ビット6  | 説明       |

|-------|----------|

| C H R |          |

| 0     | 8ビットデータ  |

| 1     | 7ビットデータ* |

【注】\* 7ビットデータを選択した場合、T D R のM S B（ビット7）は送信されません。

### ビット5：パリティイネーブル（P E）

調歩同期式モードでは、送信時にパリティビットの付加を、受信時にパリティビットのチェックを行うかどうかを選択します。クロック同期式モードでは、P Eビットの設定にかかわらずパリティビットの付加、およびチェックは行いません。

| ビット5 | 説明                     |

|------|------------------------|

| P E  |                        |

| 0    | パリティビットの付加、およびチェックを禁止  |

| 1    | パリティビットの付加、およびチェックを許可* |

【注】\* P Eビットに“1”をセットすると送信時には、O/Eビットで指定した偶数、または奇数パリティを送信データに付加して送信します。受信時には、受信したパリティビットがO/Eビットで指定した偶数、または奇数パリティになっているかどうかをチェックします。

#### ビット4：パリティモード（O／E）

・パリティの付加やチェックを偶数パリティ／奇数パリティのいずれで行うかを選択します。

O／Eビットの設定は、調歩同期式モードでP Eビットに“1”を設定しパリティビットの付加やチェックを許可したときのみ有効になります。クロック同期式モードや、調歩同期式モードでパリティの付加やチェックを禁止している場合には、O／Eビットの指定は無効です。

| ビット4 | 説明                   |

|------|----------------------|

| O／E  |                      |

| 0    | 偶数パリティ* <sup>1</sup> |

| 1    | 奇数パリティ* <sup>2</sup> |

【注】\*<sup>1</sup> 偶数パリティに設定すると送信時には、パリティビットと送信キャラクタをあわせて、その中の“1”的数の合計が偶数になるようにパリティビットを付加して送信します。

受信時には、パリティビットと受信キャラクタをあわせて、その中の“1”的数の合計が偶数であるかどうかをチェックします。

\*<sup>2</sup> 奇数パリティに設定すると送信時には、パリティビットと送信キャラクタをあわせて、その中の“1”的数の合計が奇数になるようにパリティビットを付加して送信します。

受信時には、パリティビットと受信キャラクタをあわせて、その中の“1”的数の合計が奇数であるかどうかをチェックします。

#### ビット3：ストップビットレンジス（S T O P）

調歩同期式モードでのストップビットの長さを1ビット／2ビットのいずれかから選択します。S T O Pビットの設定は調歩同期式モードでのみ有効になります。クロック同期式モードに設定した場合にはストップビットは付加されませんので、このビットの設定は無効です。

| ビット3    | 説明                     |

|---------|------------------------|

| S T O P |                        |

| 0       | 1ストップビット* <sup>1</sup> |

| 1       | 2ストップビット* <sup>2</sup> |

【注】\*<sup>1</sup> 送信時には、送信キャラクタの最後尾に1ビットの1（ストップビット）を付加して送信します。

\*<sup>2</sup> 送信時には、送信キャラクタの最後尾に2ビットの1（ストップビット）を付加して送信します。

なお、受信時にはS T O Pビットの設定にかかわらず、受信したストップビットの1ビットのみをチェックします。ストップビットの2ビット目が“1”的場合は、ストップビットとして扱いますが、“0”的場合は、次の送信キャラクタのスタートビットとして扱います。

## ビット2：マルチプロセッサモード(MP)

マルチプロセッサフォーマットを選択します。マルチプロセッサフォーマットを選択した場合、P Eビット、およびO/Eビットにおけるパリティの設定は無効になります。また、MPビットの設定は、調歩同期式モードのときのみ有効です。クロック同期式モードでは、MPビットの設定は無効です。

マルチプロセッサ通信機能については、「13.3.3 マルチプロセッサ通信機能」を参照してください。

| ビット2 | 説明                     |

|------|------------------------|

| M P  |                        |

| 0    | マルチプロセッサ機能の禁止<br>(初期値) |

| 1    | マルチプロセッサフォーマットを選択      |

## ビット1、0：クロックセレクト1、0 (CKS1、0)

内蔵ボーレートジェネレータのクロックソースを選択します。CKS1、0ビットの設定により $\phi$ 、 $\phi/4$ 、 $\phi/16$ 、 $\phi/64$ の4種類からクロックソースを選択できます。

クロックソースと、ビットレートレジスタの設定値、およびボーレートの関係については、「13.2.8 ビットレートレジスタ」を参照してください。

| ビット1 | ビット0 | 説明                   |

|------|------|----------------------|

| CKS1 | CKS0 |                      |

| 0    | 0    | $\phi$ クロック<br>(初期値) |

| 0    | 1    | $\phi/4$ クロック        |

| 1    | 0    | $\phi/16$ クロック       |

| 1    | 1    | $\phi/64$ クロック       |

### 13.2.6 シリアルコントロールレジスタ (SCR)

S C R は、S C I の送信／受信動作、調歩同期式モードでのシリアルクロック出力、割込み要求の許可／禁止、および送信／受信クロックソースの選択を行うレジスタです。

S C Rは、常にC P Uによるリード／ライトが可能です。

SCRは、リセット、またはスタンバイモード時にH'00にイニシャライズされます。

### ビット7：トランスマットインターフェース（TIE）

TDRからTSRへシリアル送信データが転送されSSRのTDRフラグが“1”にセットされたときに、送信データエンプティ割込み（TXI）要求の発生を許可／禁止します。

| ビット7 | 説明                       |       |

|------|--------------------------|-------|

| TIE  |                          |       |

| 0    | 送信データエンプティ割込み（TXI）要求の禁止* | （初期値） |

| 1    | 送信データエンプティ割込み（TXI）要求の許可  |       |

【注】\* TXI割込み要求の解除は、TDRフラグから“1”をリードした後、“0”にクリアするか、またはTIEビットを“0”にクリアすることで行うことができます。

### ビット6：レシーブインターフェース（RIE）

シリアル受信データがRSRからRDRへ転送されてSSRのRDRFフラグが“1”にセットされたとき、受信データフル割込み（RXI）要求、および受信エラー割込み（ERI）要求の発生を許可／禁止します。

| ビット6 | 説明                                       |       |

|------|------------------------------------------|-------|

| RIE  |                                          |       |

| 0    | 受信データフル割込み（RXI）要求、および受信エラー割込み（ERI）要求を禁止* | （初期値） |

| 1    | 受信データフル割込み（RXI）要求、および受信エラー割込み（ERI）要求を許可  |       |

【注】\* RXI、およびERI割込み要求の解除は、RDRF、またはFER、PER、ORERの各フラグから“1”をリードした後、“0”にクリアするか、RIEビットを“0”にクリアすることで行えます。

### ビット5：トランスマットインターフェース（TE）

SCIのシリアル送信動作の開始を許可／禁止します。

| ビット5 | 説明        |       |

|------|-----------|-------|

| TE   |           |       |

| 0    | 送信動作を禁止*  | （初期値） |

| 1    | 送信動作を許可** |       |

【注】\* SSRのTDRフラグは“1”に固定されます。

\*\* この状態で、TDRに送信データをライトして、SSRのTDRフラグを“0”にクリアするとシリアル送信を開始します。

なお、TEビットを“1”にセットする前に必ずSMRの設定を行い送信フォーマットを決定してください。

#### ビット4：レシーブイネーブル（R E）

S C I のシリアル受信動作の開始を許可／禁止します。

| ビット4 | 説明                    |

|------|-----------------------|

| R E  |                       |

| 0    | 受信動作を禁止 <sup>*1</sup> |

| 1    | 受信動作を許可 <sup>*2</sup> |

【注】<sup>\*1</sup> R E ビットを“0”にクリアしてもR D R F、F E R、P E R、O R E R の各フラグは影響を受けず、状態を保持しますので注意してください。

<sup>\*2</sup> この状態で調歩同期式モードの場合はスタートビットを、クロック同期式モードの場合は同期クロック入力をそれぞれ検出すると、シリアル受信を開始します。

なお、R E ビットを“1”にセットする前に必ずS M R の設定を行い、受信フォーマットを決定してください。

#### ビット3：マルチプロセッサインタラプトイネーブル（M P I E）

マルチプロセッサ割込みを許可／禁止します。M P I E ビットの設定は、調歩同期式モードで、かつ、S M R のM P ビットが“1”に設定されている受信時にのみ有効です。

クロック同期式モードのとき、あるいはM P ビットが“0”的きにはM P I E ビットの設定は無効です。

| ビット3    | 説明                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| M P I E |                                                                                                                                   |

| 0       | マルチプロセッサ割込み禁止状態（通常の受信動作をします）<br>〔クリア条件〕<br>(1) M P I E ビットを“0”にクリア<br>(2) M P B = “1”のデータを受信したとき                                  |

| 1       | マルチプロセッサ割込み許可状態*<br>マルチプロセッサビットが“1”的データを受け取るまで受信割込み(R X I )要求、受信エラー割込み(E R I )要求、およびS S R のR D R F、F E R、O R E R の各フラグのセットを禁止します。 |

【注】\* R S R からR D R への受信データの転送、および受信エラーの検出とS S R のR D R F、F E R、O R E R の各フラグのセットは行いません。M P B = “1”を含む受信データを受信すると、S S R のM P B ビットを“1”にセットし、M P I E ビットを自動的に“0”にクリアし、R X I 、E R I 割込み要求の発生(S C R のT I E 、R I E ビットが“1”にセットされている場合)とF E R 、O R E R フラグのセットが許可されます。

## ビット2：トランスマットエンドインタラプトイネーブル（T E I E）

送信キャラクタの最後尾ビットの送出時に有効な送信データがT D Rにないとき、送信終了割込み（T E I）要求の発生を許可／禁止します。

| ビット2<br>T E I E | 説明                   |       |

|-----------------|----------------------|-------|

|                 | 0                    | 1     |

| 0               | 送信終了割込み（T E I）要求を禁止* | （初期値） |

| 1               | 送信終了割込み（T E I）要求を許可* |       |

【注】\* T E I の解除は、S S R の T D R E フラグから“1”をリードした後、“0”にクリアしてT E N D フラグを“0”にクリアするか、T E I E ビットを“0”にクリアすることで行うことができます。

## ビット1、0：クロックイネーブル1、0（C K E 1、0）

S C I のクロックソースの選択、およびSCK端子からのクロック出力の許可／禁止を設定します。C K E 1 ビットとC K E 0 ビットの組み合わせによってSCK端子を入出力ポートにするか、シリアルクロック出力端子にするか、またはシリアルクロック入力端子にするかが決まります。

ただし、C K E 0 ビットの設定は調歩同期式モードで内部クロック動作（C K E 1 = “0”）時のみ有効です。クロック同期式モードのとき、および外部クロック動作（C K E = “1”）の場合はC K E 0 ビットの設定は無効です。また、S M R でS C I の動作モードを設定する前にC K E 1、C K E 0 ビットを設定してください。

S C I のクロックソースの選択についての詳細は「13.3 動作説明」の表13.9を参照してください。

| ビット1<br>C K E 1 | ビット0<br>C K E 0 | 説明         |                         |

|-----------------|-----------------|------------|-------------------------|

| 0               | 0               | 調歩同期式モード   | 内部クロック／SCK端子は入出力ポート*¹   |

|                 |                 | クロック同期式モード | 内部クロック／SCK端子は同期クロック出力*¹ |

| 0               | 1               | 調歩同期式モード   | 内部クロック／SCK端子はクロック出力*²   |

|                 |                 | クロック同期式モード | 内部クロック／SCK端子は同期クロック出力   |

| 1               | 0               | 調歩同期式モード   | 外部クロック／SCK端子はクロック入力*³   |

|                 |                 | クロック同期式モード | 外部クロック／SCK端子は同期クロック入力   |

| 1               | 1               | 調歩同期式モード   | 外部クロック／SCK端子はクロック入力*³   |

|                 |                 | クロック同期式モード | 外部クロック／SCK端子は同期クロック入力   |

【注】\*¹ 初期値

\*² ビットレートと同じ周波数のクロックを出力

\*³ ビットレートの16倍の周波数のクロックを入力

### 13.2.7 シリアルステータスレジスタ (S S R)

S C I の動作状態を示すステータスフラグと、マルチプロセッサビットを内蔵した 8 ビットのレジスタです。

| ビット : | 7    | 6    | 5    | 4   | 3   | 2    | 1   | 0    |

|-------|------|------|------|-----|-----|------|-----|------|

|       | TDRE | RDRF | ORER | FER | PER | TEND | MPB | MPBT |

初期値 : 1 0 0 0 0 1 0 0

R / W : R/(W)\* R/(W)\* R/(W)\* R/(W)\* R/(W)\* R R R R / W

マルチプロセッサ

ビットトランスファー

送信時のマルチプロセッサビットの値を設定するビットです。

マルチプロセッサビット

受信したマルチプロセッサビットを格納するビットです。

トランスマットエンド

送信終了を示すステータスフラグです。

パリティエラー

受信時にパリティエラーを検出したことを示すステータスフラグです。

フレーミングエラー

受信時にフレーミングエラーを検出したことを示すステータスフラグです。

オーバランエラー

受信時にオーバランエラーを検出したことを示すステータスフラグです。

レシーブデータレジスタフル

受信を完了し R D R にデータが格納されていることを示すステータスフラグです。

トランスマットデータレジスタエンプティ

T D R から T S R に送信データが転送され T D R にデータをライトすることが可能であることを示すステータスフラグです。

【注】\* フラグをクリアするための “0” ライトのみ可能です。

S S R は常に C P U からリード／ライトできます。ただし、T D R E、R D R F、O R E R、P E R、F E R の各フラグへ “1” をライトすることはできません。また、これらを “0” にクリアするためには、あらかじめ “1” をリードしておく必要があります。また、T E N D フラグ、および M P B フラグはリード専用であり、ライトすることはできません。

S S R は、リセット、またはスタンバイモード時に H'84 にイニシャライズされます。

#### ビット 7：トランスマットデータレジスタエンプティ (T D R E)

T D R から T S R にデータ転送が行われ T D R に次のシリアル送信データをライトすることが可能になったことを示します。

| ビット 7   | 説明                                                                                                                                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| T D R E |                                                                                                                                                     |

| 0       | T D R に有効な送信データがライトされていることを表示<br>【クリア条件】<br>(1) T D R E = “1” の状態をリードした後、“0” をライトしたとき<br>(2) D M A C で T D R へデータをライトしたとき                           |

| 1       | T D R に有効な送信データがないことを表示<br>【セット条件】<br>(1) リセット、またはスタンバイモード時<br>(2) S C R の T E ビットが “0” のとき<br>(3) T D R から T S R にデータ転送が行われ T D R にデータライトが可能になつたとき |

#### ビット 6：レシーブデータレジスタフル (R D R F)

受信したデータが R D R に格納されていることを示します。

| ビット 6   | 説明                                                                                                                                                       |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| R D R F |                                                                                                                                                          |

| 0       | R D R に受信データが格納されていないことを表示<br>(初期値)<br>【クリア条件】<br>(1) リセット、またはスタンバイモード時<br>(2) R D R F = “1” の状態をリードした後、“0” をライトしたとき<br>(3) D M A C で R D R のデータをリードしたとき |

| 1       | R D R に受信データが格納されていることを表示<br>【セット条件】<br>シリアル受信が正常終了し、R S R から R D R へ受信データが転送されたとき                                                                       |

【注】 受信時にエラーを検出したとき、および S C R の R E ビットを “0” にクリアしたときは R D R および R D R F フラグは影響を受けず以前の状態を保持します。

— R D R F フラグが “1” にセットされたまま次のデータを受信完了するとオーバランエラーを発生し、受信データが失われますので注意してください。

## ビット5：オーバランエラー（O R E R）

受信時にオーバランエラーが発生して異常終了したことを示します。

| ビット5<br>O R E R | 説明                                                                                                      |

|-----------------|---------------------------------------------------------------------------------------------------------|

| 0               | 受信中、または正常に受信を完了したことを表示<br>〔クリア条件〕<br>(1) リセット、またはスタンバイモード時<br>(2) O R E R = “1” の状態をリードした後、“0” をライトしたとき |

| 1               | 受信時にオーバランエラーが発生したことを表示* <sup>2</sup><br>〔セット条件〕<br>R D R F = “1” の状態で次のシリアル受信を完了したとき                    |

【注】\*<sup>1</sup> S C RのR E ビットを“0”にクリアしたときには、O R E R フラグは影響を受けず以前の状態を保持します。

\*<sup>2</sup> R D R ではオーバランエラーが発生する前の受信データを保持し、後から受信したデータが失われます。さらに、O R E R = “1” にセットされた状態で、以降のシリアル受信を続けることはできません。なお、クロック同期式モードでは、シリアル送信を続けることもできません。

## ビット4：フレーミングエラー（F E R）

調歩同期式モードで受信時にフレーミングエラーが発生して異常終了したことを示します。

| ビット4<br>F E R | 説明                                                                                                                    |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| 0             | 受信中、または正常に受信を完了したことを表示<br>〔クリア条件〕<br>(1) リセット、またはスタンバイモード時<br>(2) F E R = “1” の状態をリードした後、“0” をライトしたとき                 |

| 1             | 受信時にフレーミングエラーが発生したことを表示<br>〔セット条件〕<br>S C I が受信終了時に受信データの最後尾のストップビットが“1”であるかどうかをチェックし、ストップビットが“0”であったとき* <sup>2</sup> |

【注】\*<sup>1</sup> S C RのR E ビットを“0”にクリアしたときには、F E R フラグは影響を受けず以前の状態を保持します。

\*<sup>2</sup> 2ストップビットモードのときは、1ビット目のストップビットが“1”であるかどうかのみを判定し、2ビット目のストップビットはチェックをしません。なお、フレーミングエラーが発生したときの受信データはR D R に転送されますが、R D R F フラグはセットされません。さらに、F E R フラグが“1”にセットされた状態においては、以降のシリアル受信を続けることはできません。また、クロック同期式モードでは、シリアル送信も続けることができません。

### ビット3：パリティエラー（P E R）

調歩同期式モードで、パリティを付加した受信時にパリティエラーが発生して異常終了したこと示します。

| ビット3<br>P E R | 説明                                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 受信中、または正常に受信を完了したことを表示* <sup>1</sup><br>〔クリア条件〕<br>(1) リセット、またはスタンバイモード時<br>(2) P E R = “1” の状態をリードした後、“0” をライトしたとき                 |

| 1             | 受信時にパリティエラーが発生したことを表示* <sup>2</sup><br>〔セット条件〕<br>受信時の受信データとパリティビットをあわせた1の数が、S M RのO / $\bar{E}$ ビットで指定した偶数パリティ／奇数パリティの設定と一致しなかったとき |

【注】\*<sup>1</sup> S C RのR E ビットを“0”にクリアしたときには、P E R フラグは影響を受けず以前の状態を保持します。

\*<sup>2</sup> パリティエラーが発生したときの受信データはR D Rに転送されますが、R D R F フラグはセットされません。なお、P E R フラグが“1”にセットされた状態では、以降のシリアル受信を続けることはできません。さらに、クロック同期式モードでは、シリアル送信も続けることができません。

### ビット2：トランスマットエンド（T E N D）

送信キャラクタの最後尾ビットの送信時にT D Rに有効なデータがなく、送信を終了したことを示します。

T E N D フラグはリード専用ですので、ライトすることはできません。

| ビット2<br>T E N D | 説明                                                                                                                                  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 送信中であることを表示<br>〔クリア条件〕<br>(1) T D R E = “1” の状態をリードした後、T D R E フラグに“0”をライトしたとき<br>(2) D M A C でT D Rへデータをライトしたとき                    |

| 1               | 送信を終了したことを表示<br>〔セット条件〕<br>(1) リセット、またはスタンバイモード時<br>(2) S C RのT E ビットが“0”的とき<br>(3) 1バイトのシリアル送信キャラクタの最後尾ビットの送信時にT D R E = “1”であったとき |

#### ビット1：マルチプロセッサビット (M P B)

調歩同期式モードで受信をマルチプロセッサフォーマットで行うときに、受信データ中のマルチプロセッサビットを格納します。

M P B ビットは、リード専用であり、ライトすることはできません。

| ビット1  | 説明                                   |

|-------|--------------------------------------|

| M P B |                                      |

| 0     | マルチプロセッサビットが“0”のデータを受信したことを表示* (初期値) |

| 1     | マルチプロセッサビットが“1”のデータを受信したことを表示        |

【注】\* マルチプロセッサフォーマットでR E ビットを“0”にクリアしたときには、以前の状態を保持します。

#### ビット0：マルチプロセッサビットトランスファ (M P B T)

調歩同期式モードで送信をマルチプロセッサフォーマットで行うときに、送信データに付加するマルチプロセッサビットを格納します。

クロック同期式モードやマルチプロセッサフォーマットでないとき、あるいは送信でないときはM P B T ビットの設定は無効です。

| ビット0    | 説明                           |

|---------|------------------------------|

| M P B T |                              |

| 0       | マルチプロセッサビットが“0”のデータを送信 (初期値) |

| 1       | マルチプロセッサビットが“1”のデータを送信       |

### 13.2.8 ビットレートレジスタ (BRR)

BRRは、SMRのCKS1、CKS0ビットで選択されるボーレートジェネレータの動作クロックとあわせて、シリアル送信／受信のビットレートを設定する8ビットのレジスタです。

| ビット : | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|---|---|---|---|---|---|---|

|       |   |   |   |   |   |   |   |   |

初期値 : 1 1 1 1 1 1 1 1

R/W : R/W R/W R/W R/W R/W R/W R/W R/W

BRRは、常にCPUによるリード／ライトが可能です。

BRRは、リセット、またはスタンバイモード時にH'FFにイニシャライズされます。

なお、チャネルごとにボーレートジェネレータの制御が独立していますので、それぞれ異なる値を設定することができます。

表13.3に調歩同期式モードのBRRの設定例を表13.4にクロック同期式モードのBBRの設定例を示します。

表13.3 ピットレートに対するBRRの設定例【調歩同期式モード】(1)

| $\phi$<br>(MHz)<br>ビットレート<br>(bit/s) | 2 |     |           | 2.097152 |     |           | 2.4576 |     |           | 3 |     |           |

|--------------------------------------|---|-----|-----------|----------|-----|-----------|--------|-----|-----------|---|-----|-----------|

|                                      | n | N   | 誤差<br>(%) | n        | N   | 誤差<br>(%) | n      | N   | 誤差<br>(%) | n | N   | 誤差<br>(%) |

| 110                                  | 1 | 141 | 0.03      | 1        | 148 | -0.04     | 1      | 174 | -0.26     | 1 | 212 | 0.03      |

| 150                                  | 1 | 103 | 0.16      | 1        | 108 | 0.21      | 1      | 127 | 0.00      | 1 | 155 | 0.16      |

| 300                                  | 0 | 207 | 0.16      | 0        | 217 | 0.21      | 0      | 255 | 0.00      | 1 | 77  | 0.16      |

| 600                                  | 0 | 103 | 0.16      | 0        | 108 | 0.21      | 0      | 127 | 0.00      | 0 | 155 | 0.16      |

| 1200                                 | 0 | 51  | 0.16      | 0        | 54  | -0.70     | 0      | 63  | 0.00      | 0 | 77  | 0.16      |

| 2400                                 | 0 | 25  | 0.16      | 0        | 26  | 1.14      | 0      | 31  | 0.00      | 0 | 38  | 0.16      |

| 4800                                 | 0 | 12  | 0.16      | 0        | 13  | -2.48     | 0      | 15  | 0.00      | 0 | 19  | -2.34     |

| 9600                                 | 0 | 6   | -6.99     | 0        | 6   | -2.48     | 0      | 7   | 0.00      | 0 | 9   | -2.34     |

| 19200                                | 0 | 2   | 8.51      | 0        | 2   | 13.78     | 0      | 3   | 0.00      | 0 | 4   | -2.34     |

| 31250                                | 0 | 1   | 0.00      | 0        | 1   | 4.86      | 0      | 1   | 22.88     | 0 | 2   | 0.00      |

| 38400                                | 0 | 1   | -18.62    | 0        | 1   | -14.67    | 0      | 1   | 0.00      | - | -   | -         |

| $\phi$<br>(MHz)<br>ビットレート<br>(bit/s) | 3.6864 |     |           | 4 |     |           | 4.9152 |     |           | 5 |     |           |

|--------------------------------------|--------|-----|-----------|---|-----|-----------|--------|-----|-----------|---|-----|-----------|

|                                      | n      | N   | 誤差<br>(%) | n | N   | 誤差<br>(%) | n      | N   | 誤差<br>(%) | n | N   | 誤差<br>(%) |

| 110                                  | 2      | 64  | 0.70      | 2 | 70  | 0.03      | 2      | 86  | 0.31      | 2 | 88  | -0.25     |

| 150                                  | 1      | 191 | 0.00      | 1 | 207 | 0.16      | 1      | 255 | 0.00      | 2 | 64  | 0.16      |

| 300                                  | 1      | 95  | 0.00      | 1 | 103 | 0.16      | 1      | 127 | 0.00      | 1 | 129 | 0.16      |

| 600                                  | 0      | 191 | 0.00      | 0 | 207 | 0.16      | 0      | 255 | 0.00      | 1 | 64  | 0.16      |

| 1200                                 | 0      | 95  | 0.00      | 0 | 103 | 0.16      | 0      | 127 | 0.00      | 0 | 129 | 0.16      |

| 2400                                 | 0      | 47  | 0.00      | 0 | 51  | 0.16      | 0      | 63  | 0.00      | 0 | 64  | 0.16      |

| 4800                                 | 0      | 23  | 0.00      | 0 | 25  | 0.16      | 0      | 31  | 0.00      | 0 | 32  | -1.36     |

| 9600                                 | 0      | 11  | 0.00      | 0 | 12  | 0.16      | 0      | 15  | 0.00      | 0 | 15  | 1.73      |

| 19200                                | 0      | 5   | 0.00      | 0 | 6   | -6.99     | 0      | 7   | 0.00      | 0 | 7   | 1.73      |

| 31250                                | -      | -   | -         | 0 | 3   | 0.00      | 0      | 4   | -1.70     | 0 | 4   | 0.00      |

| 38400                                | 0      | 2   | 0.00      | 0 | 2   | 8.51      | 0      | 3   | 0.00      | 0 | 3   | 1.73      |

表13.3 ビットレートに対するBRRの設定例【調歩同期式モード】(2)

| $\phi$<br>(MHz)<br>ビットレート<br>(bit/s) | 6 |     |           | 6.144 |     |           | 7.3728 |     |           | 8 |     |           |

|--------------------------------------|---|-----|-----------|-------|-----|-----------|--------|-----|-----------|---|-----|-----------|

|                                      | n | N   | 誤差<br>(%) | n     | N   | 誤差<br>(%) | n      | N   | 誤差<br>(%) | n | N   | 誤差<br>(%) |

| 110                                  | 2 | 106 | -0.44     | 2     | 108 | 0.08      | 2      | 130 | -0.07     | 2 | 141 | 0.03      |

| 150                                  | 2 | 77  | 0.16      | 2     | 79  | 0.00      | 2      | 95  | 0.00      | 2 | 103 | 0.16      |

| 300                                  | 1 | 155 | 0.16      | 1     | 159 | 0.00      | 1      | 191 | 0.00      | 1 | 207 | 0.16      |

| 600                                  | 1 | 77  | 0.16      | 1     | 79  | 0.00      | 1      | 95  | 0.00      | 1 | 103 | 0.16      |

| 1200                                 | 0 | 155 | 0.16      | 0     | 159 | 0.00      | 0      | 191 | 0.00      | 0 | 207 | 0.16      |

| 2400                                 | 0 | 77  | 0.16      | 0     | 79  | 0.00      | 0      | 95  | 0.00      | 0 | 103 | 0.16      |

| 4800                                 | 0 | 38  | 0.16      | 0     | 39  | 0.00      | 0      | 47  | 0.00      | 0 | 51  | 0.16      |

| 9600                                 | 0 | 19  | -2.34     | 0     | 19  | 0.00      | 0      | 23  | 0.00      | 0 | 25  | 0.16      |

| 19200                                | 0 | 9   | -2.34     | 0     | 9   | 0.00      | 0      | 11  | 0.00      | 0 | 12  | 0.16      |

| 31250                                | 0 | 5   | 0.00      | 0     | 5   | 2.40      | 0      | 6   | 5.33      | 0 | 7   | 0.00      |

| 38400                                | 0 | 4   | -2.34     | 0     | 4   | 0.00      | 0      | 5   | 0.00      | 0 | 6   | -6.99     |

| $\phi$<br>(MHz)<br>ビットレート<br>(bit/s) | 9.8304 |     |           | 10 |     |           | 12 |     |           | 12.288 |     |           |

|--------------------------------------|--------|-----|-----------|----|-----|-----------|----|-----|-----------|--------|-----|-----------|

|                                      | n      | N   | 誤差<br>(%) | n  | N   | 誤差<br>(%) | n  | N   | 誤差<br>(%) | n      | N   | 誤差<br>(%) |

| 110                                  | 2      | 174 | -0.26     | 2  | 177 | -0.25     | 2  | 212 | 0.03      | 2      | 217 | 0.08      |

| 150                                  | 2      | 127 | 0.00      | 2  | 129 | 0.16      | 2  | 155 | 0.16      | 2      | 159 | 0.00      |

| 300                                  | 1      | 255 | 0.00      | 2  | 64  | 0.16      | 2  | 77  | 0.16      | 2      | 79  | 0.00      |

| 600                                  | 1      | 127 | 0.00      | 1  | 129 | 0.16      | 1  | 155 | 0.16      | 1      | 159 | 0.00      |

| 1200                                 | 0      | 255 | 0.00      | 1  | 64  | 0.16      | 1  | 77  | 0.16      | 1      | 79  | 0.00      |

| 2400                                 | 0      | 127 | 0.00      | 0  | 129 | 0.16      | 0  | 155 | 0.16      | 0      | 159 | 0.00      |

| 4800                                 | 0      | 63  | 0.00      | 0  | 64  | 0.16      | 0  | 77  | 0.16      | 0      | 79  | 0.00      |

| 9600                                 | 0      | 31  | 0.00      | 0  | 32  | -1.36     | 0  | 38  | 0.16      | 0      | 39  | 0.00      |

| 19200                                | 0      | 15  | 0.00      | 0  | 15  | 1.73      | 0  | 19  | -2.34     | 0      | 19  | 0.00      |

| 31250                                | 0      | 9   | -1.70     | 0  | 9   | 0.00      | 0  | 11  | 0.00      | 0      | 11  | 2.40      |

| 38400                                | 0      | 7   | 0.00      | 0  | 7   | 1.73      | 0  | 9   | -2.34     | 0      | 9   | 0.00      |

表13.3 ビットレートに対するBRRの設定例 [調歩同期式モード] (3)

| $\phi$<br>(MHz)<br>ビットレート<br>(bit/s) | 13 |     |           | 14 |     |           | 14.7456 |     |           | 16 |     |           | 18 |     |           |

|--------------------------------------|----|-----|-----------|----|-----|-----------|---------|-----|-----------|----|-----|-----------|----|-----|-----------|

|                                      | n  | N   | 誤差<br>(%) | n  | N   | 誤差<br>(%) | n       | N   | 誤差<br>(%) | n  | N   | 誤差<br>(%) | n  | N   | 誤差<br>(%) |

| 110                                  | 2  | 230 | -0.08     | 2  | 248 | -0.17     | 3       | 64  | 0.70      | 3  | 70  | 0.03      | 3  | 79  | -0.12     |

| 150                                  | 2  | 168 | 0.16      | 2  | 181 | 0.16      | 2       | 191 | 0.00      | 2  | 207 | 0.16      | 2  | 233 | 0.16      |

| 300                                  | 2  | 84  | -0.43     | 2  | 90  | 0.16      | 2       | 95  | 0.00      | 2  | 103 | 0.16      | 2  | 116 | 0.16      |

| 600                                  | 1  | 168 | 0.16      | 1  | 181 | 0.16      | 1       | 191 | 0.00      | 1  | 207 | 0.16      | 1  | 233 | 0.16      |

| 1200                                 | 1  | 84  | -0.43     | 1  | 90  | 0.16      | 1       | 95  | 0.00      | 1  | 103 | 0.16      | 1  | 116 | 0.16      |

| 2400                                 | 0  | 168 | 0.16      | 0  | 181 | 0.16      | 0       | 191 | 0.00      | 0  | 207 | 0.16      | 0  | 233 | 0.16      |

| 4800                                 | 0  | 84  | -0.43     | 0  | 90  | 0.16      | 0       | 95  | 0.00      | 0  | 103 | 0.16      | 0  | 116 | 0.16      |

| 9600                                 | 0  | 41  | 0.76      | 0  | 45  | -0.93     | 0       | 47  | 0.00      | 0  | 51  | 0.16      | 0  | 58  | -0.69     |

| 19200                                | 0  | 20  | 0.76      | 0  | 22  | -0.93     | 0       | 23  | 0.00      | 0  | 25  | 0.16      | 0  | 28  | 1.02      |

| 31250                                | 0  | 12  | 0.00      | 0  | 13  | 0.00      | 0       | 14  | -1.70     | 0  | 15  | 0.00      | 0  | 17  | 0.00      |

| 38400                                | 0  | 10  | -3.82     | 0  | 10  | 3.57      | 0       | 11  | 0.00      | 0  | 12  | 0.16      | 0  | 14  | -2.34     |

表13.4 ビットレートに対するBRRの設定例 [クロック同期式モード]

| $\phi$ (MHz)<br>ビットレート<br>(bit/s) | 2 |     | 4 |     | 8 |     | 10 |     | 13 |     | 16 |     | 18 |     |

|-----------------------------------|---|-----|---|-----|---|-----|----|-----|----|-----|----|-----|----|-----|

|                                   | n | N   | n | N   | n | N   | n  | N   | n  | N   | n  | N   | n  | N   |

| 110                               | 3 | 70  | — | —   | — | —   | —  | —   | —  | —   | —  | —   | —  | —   |

| 250                               | 2 | 124 | 2 | 249 | 3 | 124 | —  | —   | 3  | 202 | 3  | 249 | —  | —   |

| 500                               | 1 | 249 | 2 | 124 | 2 | 249 | —  | —   | 3  | 101 | 3  | 124 | 3  | 140 |

| 1k                                | 1 | 124 | 1 | 249 | 2 | 124 | —  | —   | 2  | 202 | 2  | 249 | 3  | 69  |

| 2.5k                              | 0 | 199 | 1 | 99  | 1 | 199 | 1  | 249 | 2  | 80  | 2  | 99  | 2  | 112 |

| 5k                                | 0 | 99  | 0 | 199 | 1 | 99  | 1  | 124 | 1  | 162 | 1  | 199 | 1  | 224 |

| 10k                               | 0 | 49  | 0 | 99  | 0 | 199 | 0  | 249 | 1  | 80  | 1  | 99  | 1  | 112 |

| 25k                               | 0 | 19  | 0 | 39  | 0 | 79  | 0  | 99  | 0  | 129 | 0  | 159 | 0  | 179 |

| 50k                               | 0 | 9   | 0 | 19  | 0 | 39  | 0  | 49  | 0  | 64  | 0  | 79  | 0  | 89  |

| 100k                              | 0 | 4   | 0 | 9   | 0 | 19  | 0  | 24  | —  | —   | 0  | 39  | 0  | 44  |

| 250k                              | 0 | 1   | 0 | 3   | 0 | 7   | 0  | —9  | 0  | 12  | 0  | 15  | 0  | 17  |

| 500k                              | 0 | 0*  | 0 | 1   | 0 | 3   | 0  | 4   | —  | —   | 0  | 7   | 0  | 8   |

| 1M                                |   |     | 0 | 0*  | 0 | 1   | —  | —   | —  | —   | 0  | 3   | 0  | 4   |

| 2M                                |   |     |   |     | 0 | 0*  | —  | —   | —  | —   | 0  | 1   | —  | —   |

| 2.5M                              |   |     |   |     | — | —   | 0  | 0*  | —  | —   | —  | —   | —  | —   |

| 4M                                |   |     |   |     |   |     |    |     |    |     | 0  | 0*  | —  | —   |

【注】 誤差は、なるべく1%以内になるように設定してください。

#### 《記号説明》

空欄：設定できません。

—：設定可能ですが誤差がでます。

\*：連続送信／受信はできません。

BRRの設定値は以下の計算式で求められます。

#### [調歩同期式モード]

$$N = \frac{\phi}{64 \times 2^{2n-1} \times B} \times 10^6 - 1$$

#### [クロック同期式モード]

$$N = \frac{\phi}{8 \times 2^{2n-1} \times B} \times 10^6 - 1$$

B : ビットレート (bit/s)

N : ポーレートジェネレータのBRRの設定値 ( $0 \leq N \leq 255$ )

$\phi$  : 動作周波数 (MHz)

n : ポーレートジェネレータ入力クロック (n = 0、1、2、3)

(nとクロックの関係は下表を参照してください。)

| n | クロック        | S M R の設定値 |         |

|---|-------------|------------|---------|

|   |             | C K S 1    | C K S 0 |

| 0 | $\phi$      | 0          | 0       |

| 1 | $\phi / 4$  | 0          | 1       |

| 2 | $\phi / 16$ | 1          | 0       |

| 3 | $\phi / 64$ | 1          | 1       |

調歩同期式モードのビットレート誤差は、以下の計算式で求められます。

$$\text{誤差 (\%)} = \left\{ \frac{\phi \times 10^6}{(N+1) \times B \times 64 \times 2^{2n-1}} - 1 \right\} \times 100$$

表13.5に調歩同期式モードの各周波数における最大ビットレートを示します。また、表13.6～表13.7に外部クロック入力時の最大ビットレートを示します。

表13.5 各周波数における最大ビットレート(調歩同期式モード)

| $\phi$ (MHz) | 最大ビットレート (bit/s) | 設定値 |   |

|--------------|------------------|-----|---|

|              |                  | n   | N |

| 2            | 62500            | 0   | 0 |

| 2.097152     | 65536            | 0   | 0 |

| 2.4576       | 76800            | 0   | 0 |

| 3            | 93750            | 0   | 0 |

| 3.6864       | 115200           | 0   | 0 |

| 4            | 125000           | 0   | 0 |

| 4.9152       | 153600           | 0   | 0 |

| 5            | 156250           | 0   | 0 |

| 6            | 187500           | 0   | 0 |

| 6.144        | 192000           | 0   | 0 |

| 7.3728       | 230400           | 0   | 0 |

| 8            | 250000           | 0   | 0 |

| 9.8304       | 307200           | 0   | 0 |

| 10           | 312500           | 0   | 0 |

| 12           | 375000           | 0   | 0 |

| 12.288       | 384000           | 0   | 0 |

| 14           | 437500           | 0   | 0 |

| 14.7456      | 460800           | 0   | 0 |

| 16           | 500000           | 0   | 0 |

| 17.2032      | 537600           | 0   | 0 |

| 18           | 562500           | 0   | 0 |

表13.6 外部クロック入力時の最大ビットレート（調歩同期式モード）

| $\phi$ (MHz) | 外部入力クロック (MHz) | 最大ビットレート (bit/s) |

|--------------|----------------|------------------|

| 2            | 0.5000         | 31250            |

| 2.097152     | 0.5243         | 32768            |

| 2.4576       | 0.6144         | 38400            |

| 3            | 0.7500         | 46875            |

| 3.6864       | 0.9216         | 57600            |

| 4            | 1.0000         | 62500            |

| 4.9152       | 1.2288         | 76800            |

| 5            | 1.2500         | 78125            |

| 6            | 1.5000         | 93750            |

| 6.144        | 1.5360         | 96000            |

| 7.3728       | 1.8432         | 115200           |

| 8            | 2.0000         | 125000           |

| 9.8304       | 2.4576         | 153600           |

| 10           | 2.5000         | 156250           |

| 12           | 3.0000         | 187500           |

| 12.288       | 3.0720         | 192000           |

| 14           | 3.5000         | 218750           |

| 14.7456      | 3.6864         | 230400           |

| 16           | 4.0000         | 250000           |

| 17.2032      | 4.3008         | 268800           |

| 18           | 4.5000         | 281250           |

表13.7 外部クロック入力時の最大ビットレート（クロック同期式モード）

| $\phi$ (MHz) | 外部入力クロック (MHz) | 最大ビットレート (bit/s) |

|--------------|----------------|------------------|

| 2            | 0.3333         | 333333.3         |

| 4            | 0.6667         | 666666.7         |

| 6            | 1.0000         | 1000000.0        |

| 8            | 1.3333         | 1333333.3        |

| 10           | 1.6667         | 1666666.7        |

| 12           | 2.0000         | 2000000.0        |

| 14           | 2.3333         | 2333333.3        |

| 16           | 2.6667         | 2666666.7        |

| 18           | 3.0000         | 3000000.0        |

### 13.3 動作説明

#### 13.3.1 概要

S C I は、キャラクタ単位で同期をとりながら通信する調歩同期式モードと、クロックパルスにより同期をとりながら通信するクロック同期式モードの 2 方式で、シリアル通信ができます。

調歩同期式モードと、クロック同期式モードの選択および送信フォーマットの選択は、S M R で行います。これを表13.8に示します。また、S C I のクロックソースは、S M R の C / A ビットおよび S C R の C K E 1 、 C K E 0 ビットの組合せでできます。これを表13.9に示します。

#### (1) 調歩同期式モード

- データ長： 7 ビット / 8 ビットから選択可能

- パリティの付加、マルチプロセッサビットの付加、および 1 ビット / 2 ビットのストップビットの付加を選択可能（これらの組合せにより送信／受信フォーマットおよび、キャラクタ長を決定）

- 受信時にフレーミングエラー、パリティエラー、オーバランエラー、およびブレークの検出が可能

- S C I のクロックソース：内部クロック／外部クロックから選択可能

- ・ 内部クロックを選択した場合：S C I はボーレートジェネレータのクロックで動作し、ビットレートと同じ周波数のクロックを出力することが可能

- ・ 外部クロックを選択した場合：ビットレートの 16 倍の周波数のクロックを入力することが必要（内蔵ボーレートジェネレータを使用しない）

#### (2) クロック同期式モード

- 送信／受信フォーマット： 8 ビットデータ固定

- 受信時にオーバランエラーの検出可能

- S C I のクロックソース：内部クロック／外部クロックから選択可能

- ・ 内部クロックを選択した場合：S C I はボーレートジェネレータのクロックで動作し、同期クロックを外部へ出力

- ・ 外部クロックを選択した場合：内部ボーレートジェネレータを使用せず、入力された同期クロックで動作

表13.8 SMRの設定値とシリアル送信／受信フォーマット

| SMRの設定値 |      |      |      |      | モード                                  | SCIの送信／受信フォーマット |                 |             |              |  |

|---------|------|------|------|------|--------------------------------------|-----------------|-----------------|-------------|--------------|--|

| ビット7    | ビット6 | ビット2 | ビット5 | ビット3 |                                      | データ長            | マルチプロセッサ<br>ビット | パリティ<br>ビット | ストップ<br>ビット長 |  |

| C/A     | CHR  | MP   | PE   | STOP |                                      |                 |                 |             |              |  |

| 0       | 0    | 0    | 0    | 0    | 調歩同期式<br>モード                         | 8ビットデータ         | なし              | なし          | 1ビット         |  |

|         |      |      | 1    | 1    |                                      |                 |                 | あり          | 2ビット         |  |

|         |      |      | 0    | 0    |                                      |                 |                 | なし          | 1ビット         |  |

|         |      |      | 1    | 1    |                                      |                 |                 | あり          | 2ビット         |  |

|         |      |      | 0    | 0    |                                      | 7ビットデータ         |                 | なし          | 1ビット         |  |

|         | 1    | 1    | 1    | 1    |                                      |                 |                 | あり          | 2ビット         |  |

|         |      |      | 0    | 0    |                                      |                 |                 | なし          | 1ビット         |  |

|         |      |      | 1    | 1    |                                      |                 |                 | あり          | 2ビット         |  |

|         |      |      | 0    | 0    | 調歩同期式<br>モード<br>(マルチプロセッサ<br>フォーマット) | 8ビットデータ         | あり              | なし          | 1ビット         |  |

|         |      |      | 1    | 1    |                                      |                 |                 | なし          | 2ビット         |  |

| 1       | -    | -    | -    | -    | クロック同<br>期式モード                       | 8ビットデータ         | なし              | なし          | なし           |  |

表13.9 SMR、SCRの設定とSCIのクロックソースの選択

| SMR | SCRの設定 |      |                        | モード | SCIの送信／受信クロック          |          |  |  |  |  |  |

|-----|--------|------|------------------------|-----|------------------------|----------|--|--|--|--|--|

|     | ビット7   | ビット1 | ビット0                   |     | SCK端子の機能               |          |  |  |  |  |  |

|     | C/A    | CKE1 | CKE0                   |     | クロック<br>ソース            | SCK端子の機能 |  |  |  |  |  |

| 0   | 0      | 0    | 調歩同期<br>式モード           | 内 部 | SCIは、SCK端子を使用しません      |          |  |  |  |  |  |

|     |        | 1    |                        |     | ビットレートと同じ周波数のクロックを出力   |          |  |  |  |  |  |

|     | 1      | 0    |                        | 外 部 | ビットレートの16倍の周波数のクロックを入力 |          |  |  |  |  |  |

|     |        | 1    |                        |     |                        |          |  |  |  |  |  |

| 1   | 0      | 0    | クロック<br>同 期 式<br>モ ー ド | 内 部 | 同期クロックを出力              |          |  |  |  |  |  |

|     |        | 1    |                        |     |                        |          |  |  |  |  |  |

|     | 1      | 0    |                        | 外 部 | 同期クロックを入力              |          |  |  |  |  |  |

|     |        | 1    |                        |     |                        |          |  |  |  |  |  |

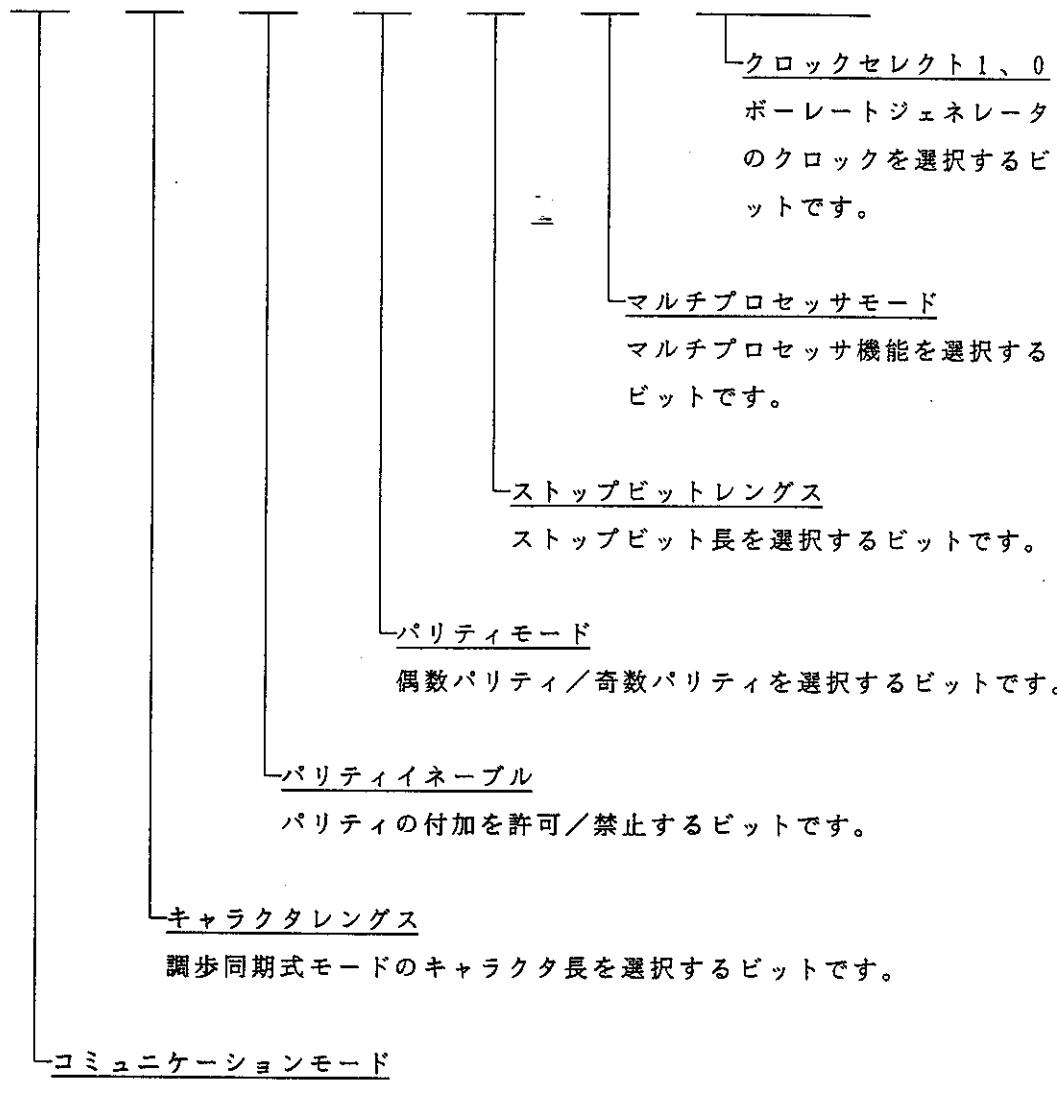

### 13.3.2 調歩同期式モード時の動作

調歩同期式モードは、通信開始を意味するスタートビットと通信終了を意味するストップビットとをデータに付加したキャラクタを送信／受信し、1キャラクタ単位で同期をとりながらシリアル通信を行うモードです。

S C I 内部では、送信部と受信部は独立していますので、全二重通信を行うことができます。また、送信部と受信部が共にダブルバッファ構造になっていますので、送信／受信中にデータのリード／ライトができるので、連続送信／受信が可能です。

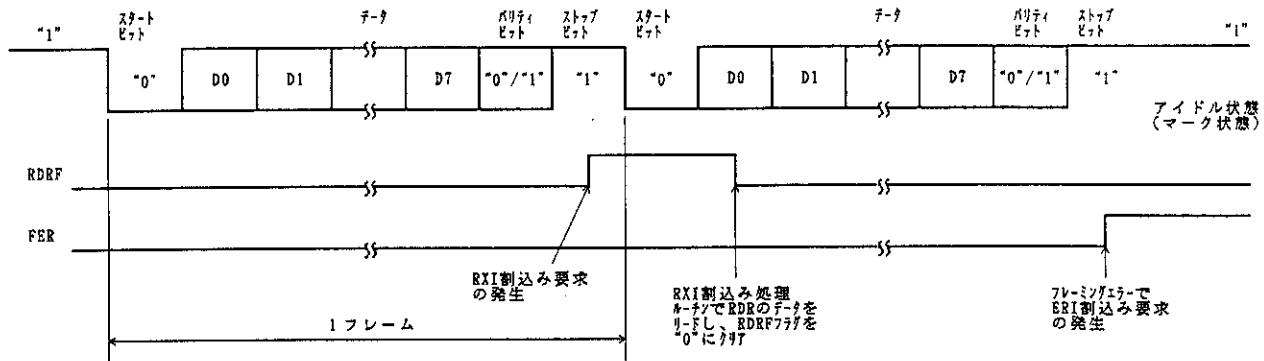

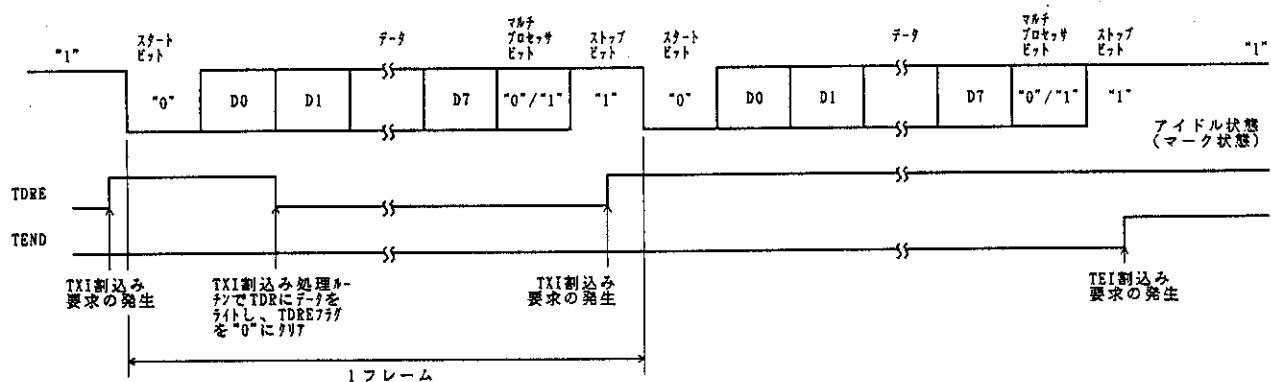

調歩同期式シリアル通信の一般的なフォーマットを図13.2に示します。

調歩同期式シリアル通信では、通信回線は通常、マーク状態（"High"レベル）に保たれています。S C I は通信回線を監視し、スペース（"Low"レベル）になったところをスタートビットとみなしてシリアル通信を開始します。

シリアル通信の1キャラクタは、スタートビット（"Low"レベル）から始まり、データ（L S B フースト：最下位ビットから）、パリティビット（"High"／"Low"レベル）、最後にストップビット（"High"レベル）の順で構成されています。

調歩同期式モードでは、S C I は受信時にスタートビットの立下がりエッジで同期化を行います。またS C I は、データを1ビット期間の16倍の周波数のクロックの8番目でサンプリングしますので、各ビットの中央で通信データが取り込まれます。

図13.2 調歩同式通信のデータフォーマット

(8ビットデータ／パリティあり／2ストップビットの例)

(1) 送信／受信フォーマット

調歩同期式モードで設定できる送信／受信フォーマットを、表13.10に示します。

送信／受信フォーマットは12種類あり、SMRの選定により選択できます。

表13.10 シリアル送信／受信フォーマット（調歩同期式モード）

| SMRの設定 |     |     |         | シリアル送信／受信フォーマットとフレーム長 |         |   |   |   |   |   |   |   |      |      |      |

|--------|-----|-----|---------|-----------------------|---------|---|---|---|---|---|---|---|------|------|------|

| CHR    | P E | M P | S T O P | 1                     | 2       | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10   | 11   | 12   |

| 0      | 0   | 0   | 0       | S                     | 8ビットデータ |   |   |   |   |   |   |   | STOP |      |      |

| 0      | 0   | 0   | 1       | S                     | 8ビットデータ |   |   |   |   |   |   |   | STOP | STOP |      |

| 0      | 1   | 0   | 0       | S                     | 8ビットデータ |   |   |   |   |   |   |   | P    | STOP |      |

| 0      | 1   | 0   | 1       | S                     | 8ビットデータ |   |   |   |   |   |   |   | P    | STOP | STOP |

| 1      | 0   | 0   | 0       | S                     | 7ビットデータ |   |   |   |   |   |   |   | STOP |      |      |

| 1      | 0   | 0   | 1       | S                     | 7ビットデータ |   |   |   |   |   |   |   | STOP | STOP |      |

| 1      | 1   | 0   | 0       | S                     | 7ビットデータ |   |   |   |   |   |   |   | P    | STOP |      |

| 1      | 1   | 0   | 1       | S                     | 7ビットデータ |   |   |   |   |   |   |   | P    | STOP | STOP |

| 0      | -   | 1   | 0       | S                     | 8ビットデータ |   |   |   |   |   |   |   | MPB  | STOP |      |

| 0      | -   | 1   | 1       | S                     | 8ビットデータ |   |   |   |   |   |   |   | MPB  | STOP | STOP |

| 1      | -   | 1   | 0       | S                     | 7ビットデータ |   |   |   |   |   |   |   | MPB  | STOP |      |

| 1      | -   | 1   | 1       | S                     | 7ビットデータ |   |   |   |   |   |   |   | MPB  | STOP | STOP |

《記号説明》

S : スタートビット

S T O P : ストップビット

P : パリティビット

M P B : マルチプロセッサビット

## (2) クロック

S C I の送受信クロックは、S M R の C / A ビットと S C R の C K E 1 、 C K E 0 ビットの設定により、内蔵ボーレートジェネレータの生成した内部クロックまたは、SCK端子から入力された外部クロックの2種類から選択できます。S C I のクロックソースの選択については表13.9を参照してください。

外部クロックをSCK端子に入力する場合には、使用するビットレートの16倍の周波数のクロックを入力してください。

内部クロックで動作させるとき、SCK端子からクロックを出力することができます。このとき出力されるクロックの周波数はビットレートと等しく、位相は図13.3に示すように送信データの中央にクロック立ち上がりエッジがくるようになります。

図13.3 出力クロックと通信データの位相関係（調歩同期式モード）

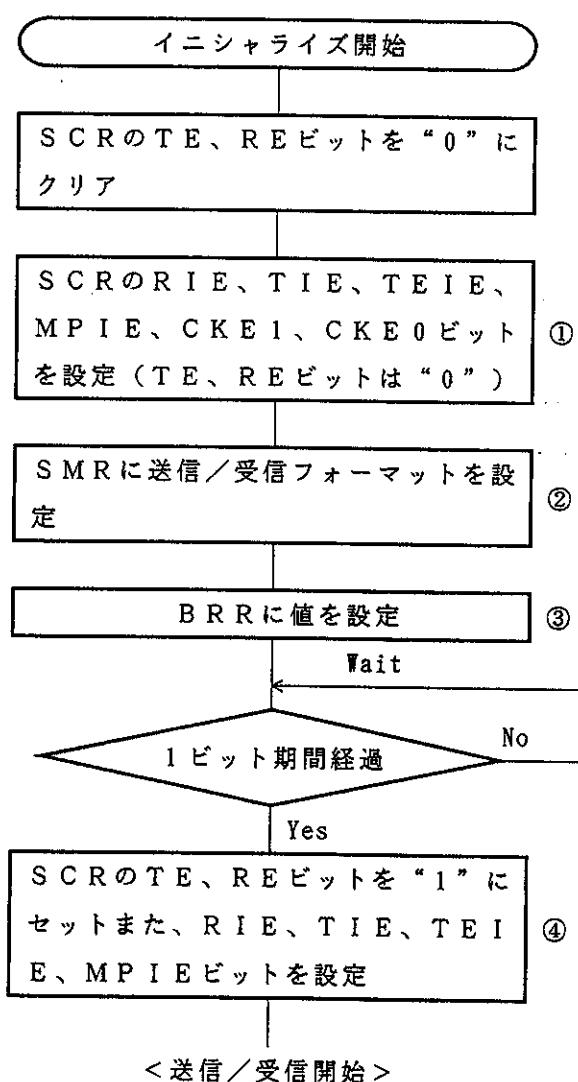

## (3) データの送信／受信動作

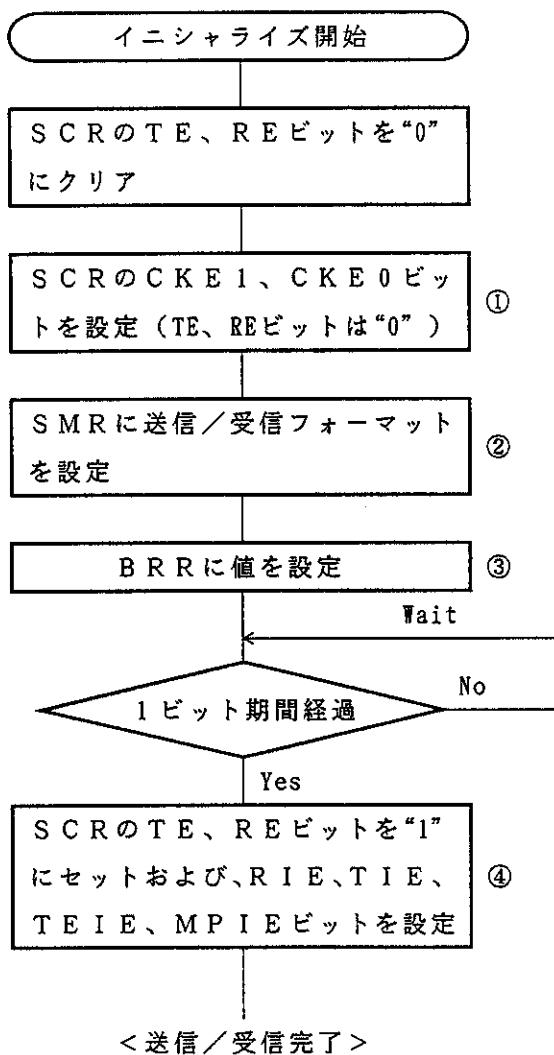

### ■ S C I のイニシャライズ（調歩同期式）

データの送信／受信前には、まずS C R の T E 、 R E ビットを“0”にクリアした後、以下の順でS C I をイニシャライズしてください。

動作モードの変更、通信フォーマットの変更などの場合には必ず、T E ビットおよびR E ビットを“0”にクリアしてから次の手順で変更を行ってください。T E ビットを“0”にクリアするとT D R E フラグは“1”にセットされ、T S R がイニシャライズされます。R E ビットを“0”にクリアしても、R D R F 、 P E R 、 F E R 、 O R E R の各フラグおよび、R D R の内容は保持されますので注意してください。

外部クロックを使用している場合には、動作が不確実になりますのでイニシャライズを含めた動作中にクロックを止めないでください。

図13.4にS C I のイニシャライズフローチャートの例を示します。

① S C R にクロックの選択を設定してください。

なお、R I E、T I E、T E I E、M P I E、およびT E、R E ビットは必ず“0”にクリアしてください。

調歩同期式モードでクロック出力を選択した場合には、S C R の設定後、ただちに出力されます。

② S M R に送信／受信フォーマットを設定します。

③ B R R にビットレートに対応する値をライドします。ただし、外部クロックを使用する場合には必要ありません。

④ 少なくとも1ビット期間待ってから、S C R のT E ビットまたはR E ビットを“1”にセットします。また、R I E、T I E、T E I E、M P I E ビットを設定してください。

T E、R E ビットを設定することによりTxD、RxD端子が使用可能となります。

図13.4 SCIのイニシャライズフローチャートの例

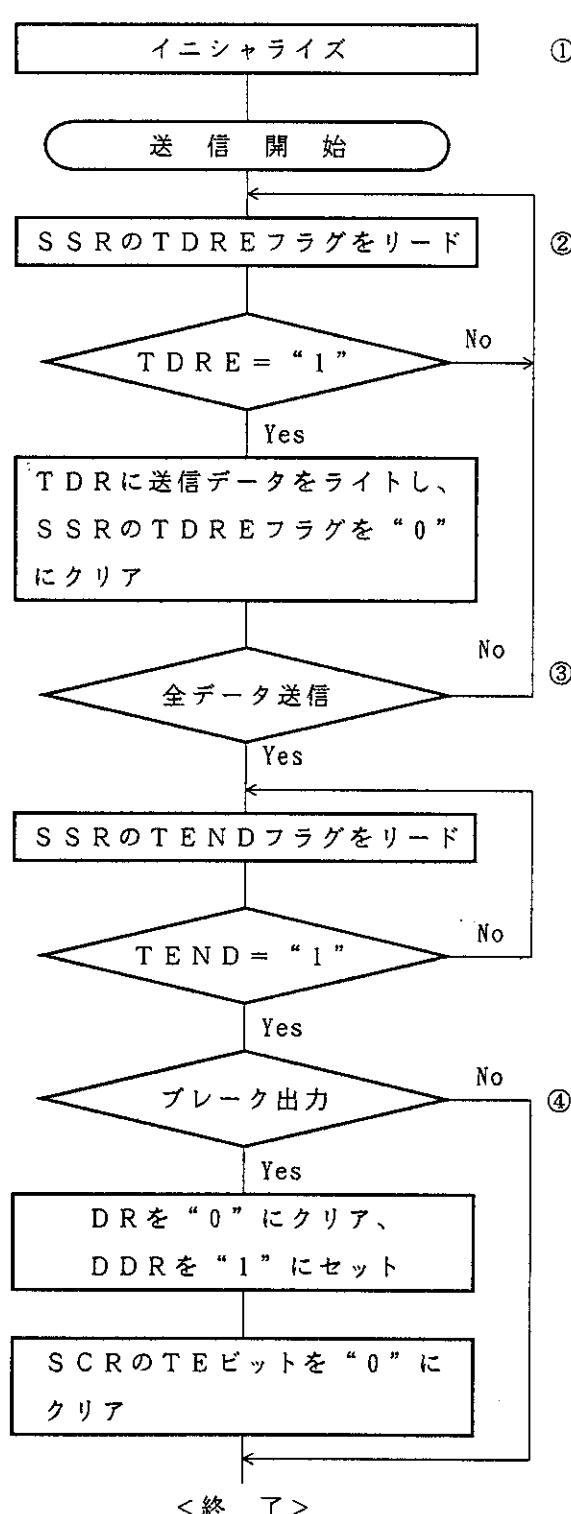

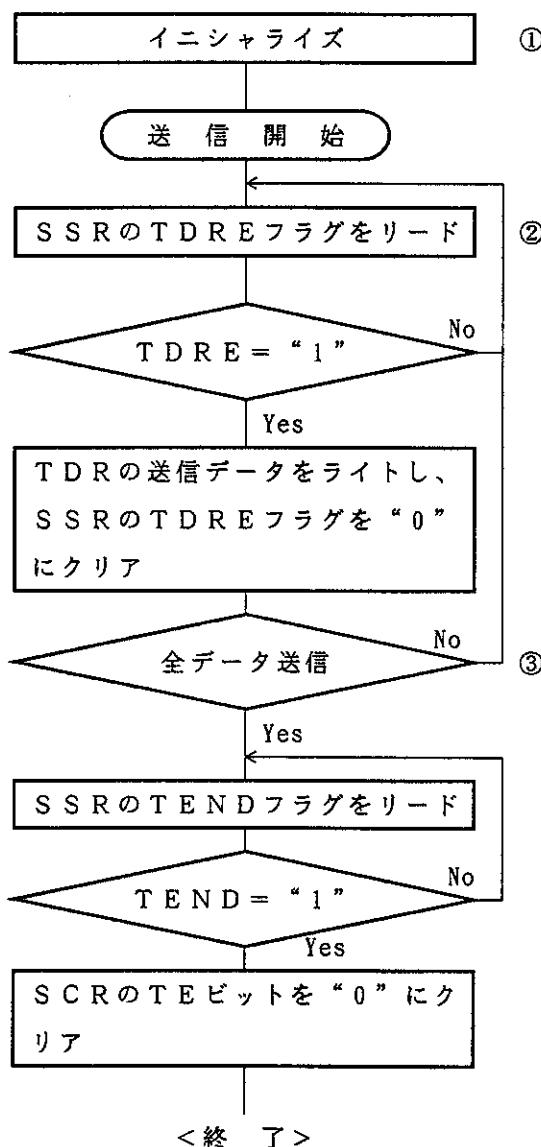

## ■シリアルデータ送信（調歩同期式）

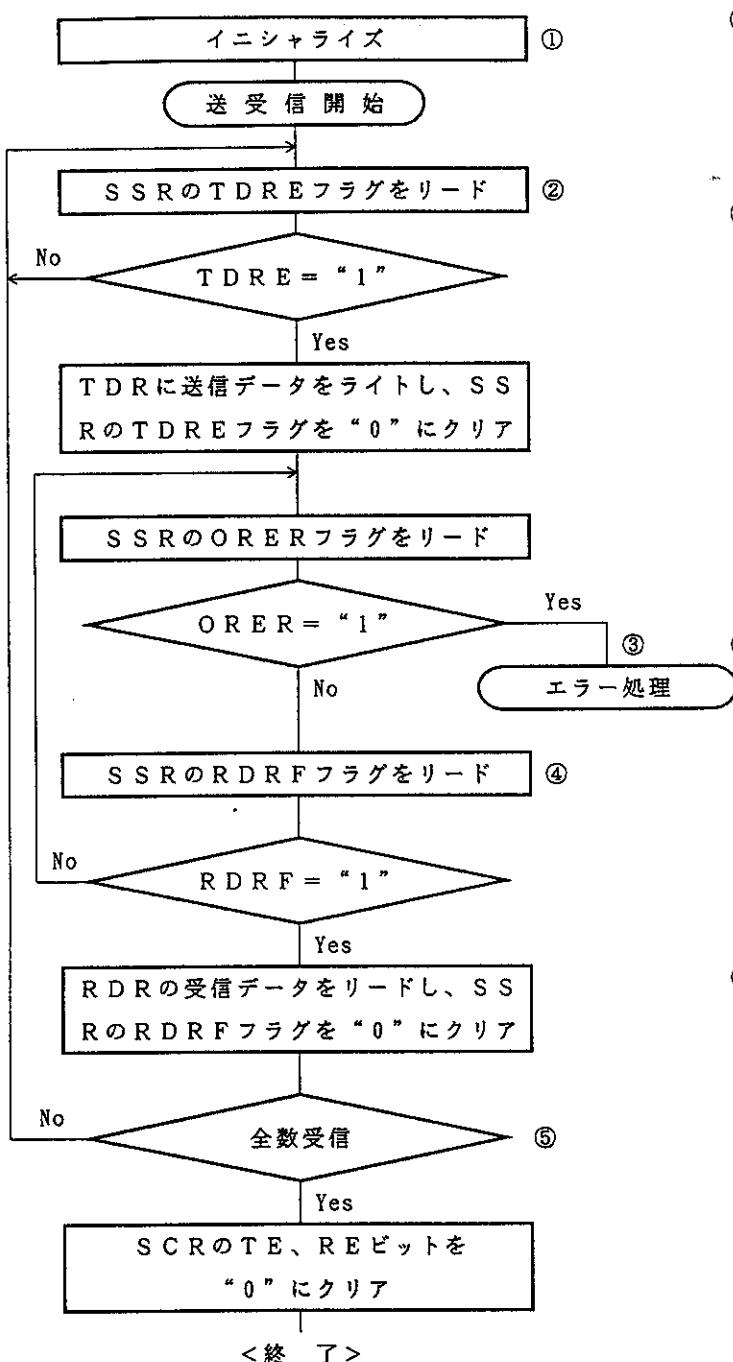

図13.5にシリアル送信のフローチャートの例を示します。

シリアルデータ送信は以下の手順に従い行ってください。

### ① SCIをイニシャライズ：

TxD端子は自動的に送信データ出力端子になります。

TEビットを1にセットした後、1フレーム分の1を出力して送信可能状態になります。

### ② SCIの状態を確認して、送信データをライト：

SSRをリードして、TDREフラグが“1”であることを確認した後、TDRに送信データをライトし、TDREフラグを“0”にクリアします。

### ③ シリアル送信の継続手順：

シリアル送信を続けるときには、TDREフラグの“1”をリードしてライト可能であることを確認した後にTDRにデータをライトし、続いてTDREフラグを“0”にクリアしてください。ただし、送信データエンブティ割込み(TXI)要求でDMACを起動し、TDRにデータをライトする場合にはTDREフラグのチェック、およびクリアは自動的に行われます。

### ④ シリアル送信の終了時にブレークを出力：

シリアル送信時にブレークを出力するときには、ポートのDDRを“1”にセット、DRを“0”にクリアした後にSCRのTEビットを“0”にクリアします。

図13.5 シリアル送信のフローチャートの例

S C I はシリアル送信時に以下のように動作します。

① S C I は、S S R の T D R E フラグを監視し、“0”であると T D R にデータがライトされたと認識し、T D R から T S R にデータを転送します。

② T D R から T S R へデータを転送した後に T D R E フラグを“1”にセットし、送信を開始します。

このとき、S C R の T I E ビットが“1”にセットされると送信データエンプティ割込み(T X I)要求を発生します。

シリアル送信データは、以下の順に TxD 端子から送り出されます。

(a) スタートビット：1ビットの“0”が出力されます。

(b) 送信データ：8ビット、または7ビットのデータがL S B から順に出力されます。

(c) パリティビットまたはマルチプロセッサビット：1ビットのパリティビット（偶数パリティ、または奇数パリティ）、または1ビットのマルチプロセッサビットが出力されます。

なお、パリティビット、またはマルチプロセッサビットを出力しないフォーマットも選択できます。

(d) ストップビット：1ビット／2ビットの“1”（ストップビット）が出力されます。

(e) マーク状態：次の送信を開始するスタートビットを送り出すまで“1”を出力し続けます。

③ S C I は、ストップビットを送出するタイミングで T D R E フラグをチェックします。

T D R E フラグが“0”であると T D R から T S R にデータを転送し、ストップビットを送り出した後、次フレームのシリアル送信を開始します。

T D R E フラグが“1”であると S S R の T E N D フラグに“1”をセットし、ストップビットを送り出した後、“1”を出力する“マーク状態”になります。このとき S C R の T E I E ビットが“1”にセットされると T E I 割込み要求を発生します。

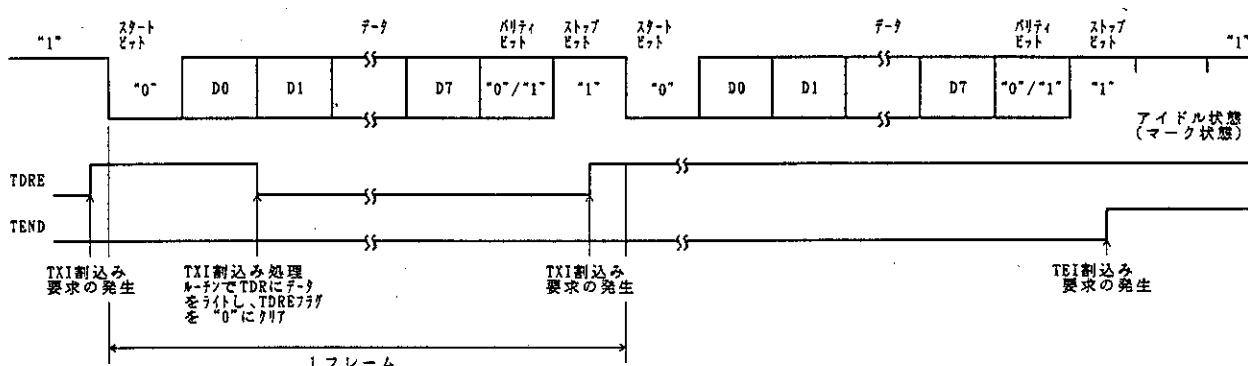

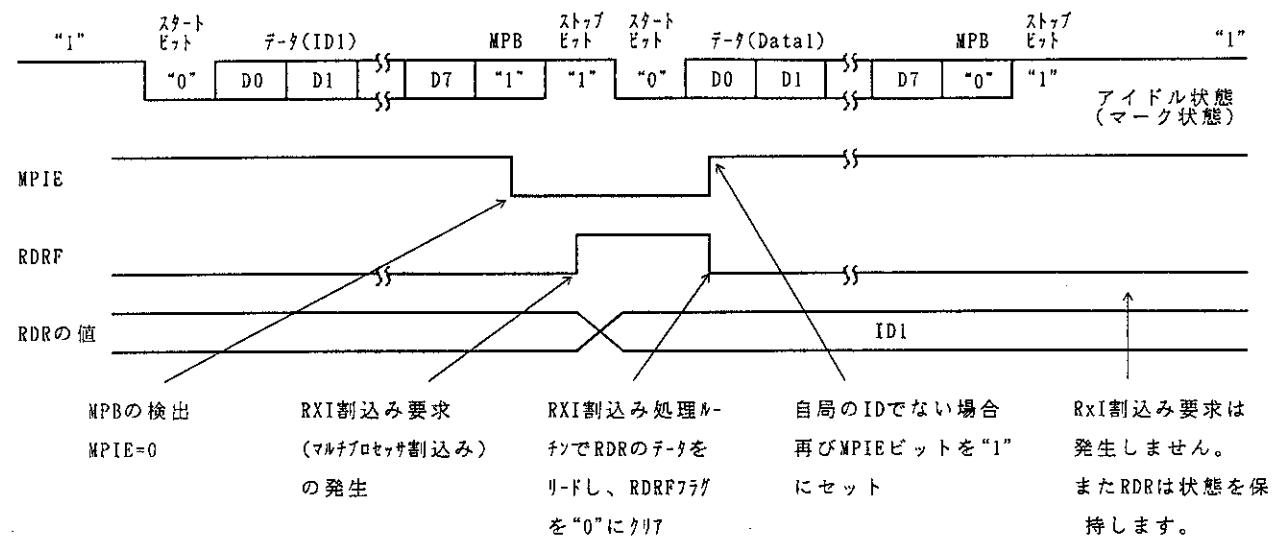

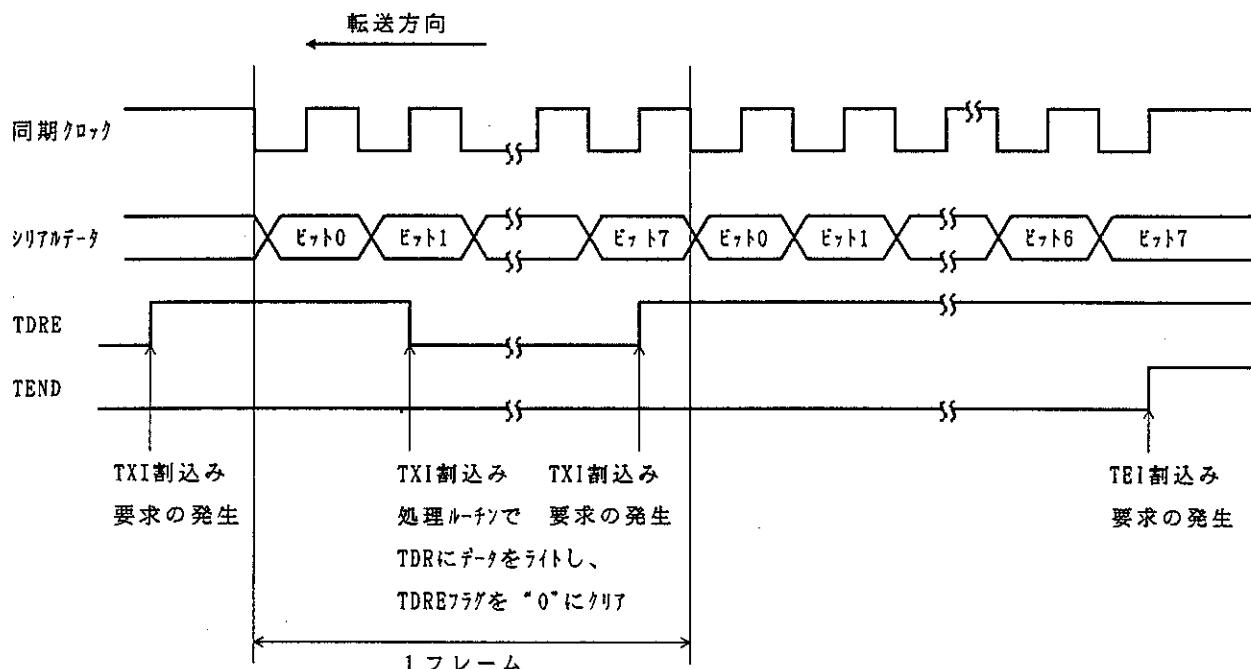

調歩同期式モードでの送信時の動作例を図13.6に示します。

図13.6 調歩同期式モードでの送信時の動作例

(8ビットデータ／パリティあり／1ストップビットの例)

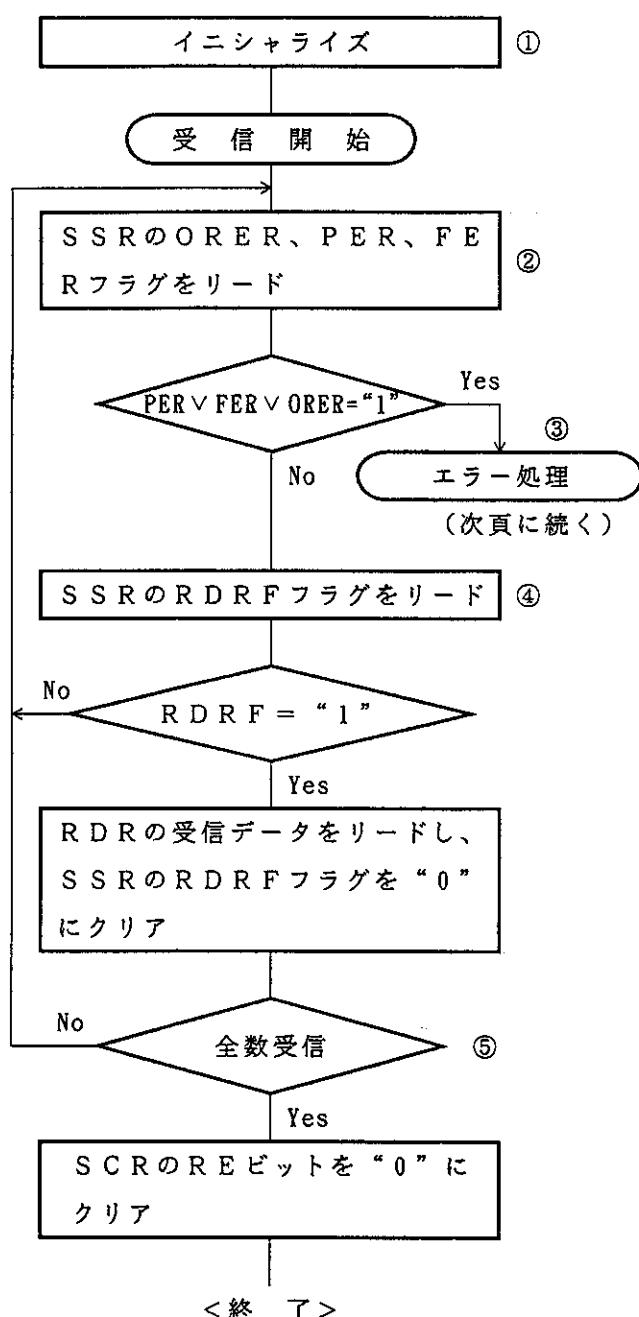

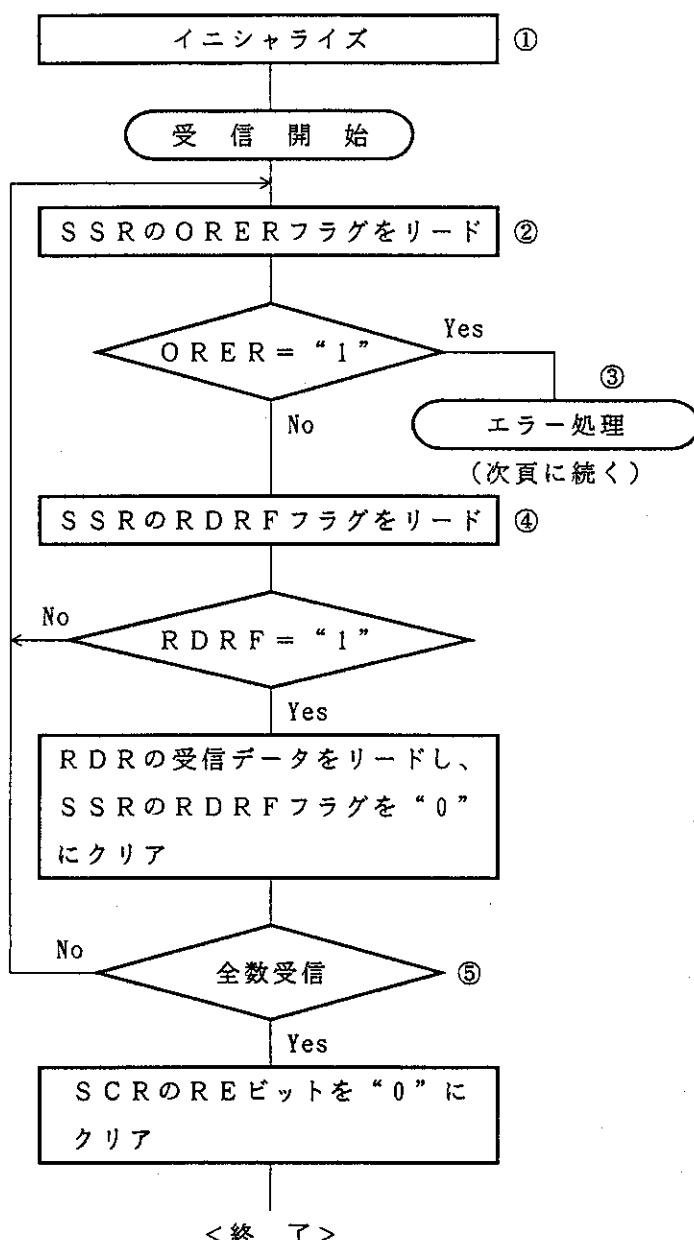

## ■シリアルデータ受信（調歩同期式）

図13.7にシリアル受信フローチャートの例を示します。

シリアルデータ受信は以下の手順に従い行ってください。

### ① SCIのイニシャライズ：

RxD端子は自動的に受信データ入力端子になります。

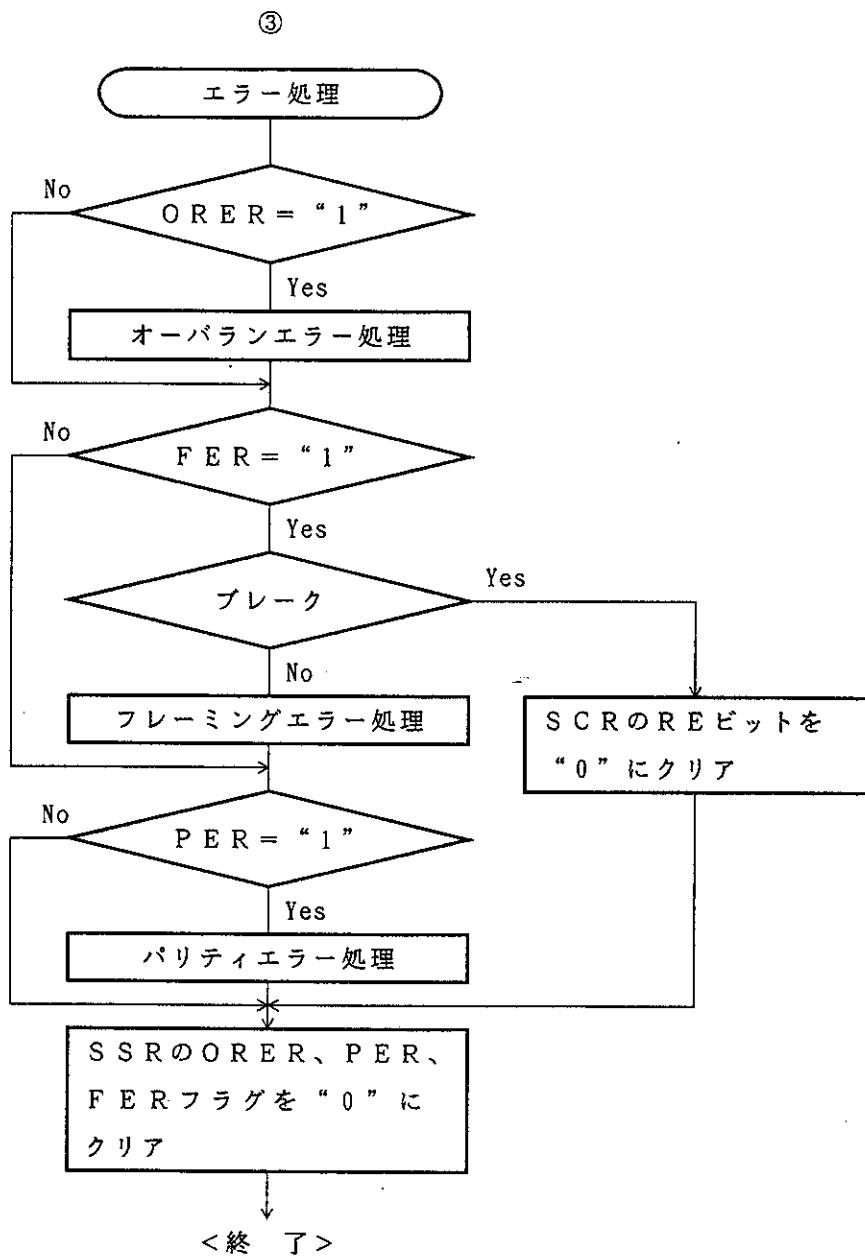

### ②③ 受信エラー処理とブレークの検出：

受信エラーが発生したときには、SSRのORER、PER、FERの各フラグをリードしてエラーを判定します。所定のエラー処理を行った後、必ず、ORER、PER、FERフラグをすべて“0”にクリアしてください。ORER、PER、FERフラグのいずれかが“1”にセットされた状態では受信を再開できません。また、フレーミングエラー時にRxD端子の値をリードすることでブレークの検出ができます。

### ④ SCIの状態を確認して受信データのリード：

SSRをリードして、RDREDF = “1”であることを確認した後、RDRの受信データをリードし、RDREDFフラグを“0”にクリアします。RDREDFフラグが“0”から“1”に変化したことは、RXI割込みによっても知ることができます。

### ⑤ シリアル受信の継続手順：

シリアル受信を続けるときには、現在のフレームのストップビットを受信する前に、RDREDFフラグのリード、RDRのリード、RDREDFフラグを“0”にクリアしておいてください。

ただし、RXI割込みでDMAを起動しRDRの値をリードする場合には、RDREDFフラグのクリアは自動的に行われます。

図13.7 シリアル受信データフローチャートの例(1)

図13.7 シリアル受信データフローチャートの例(2)

S C I は受信時に以下のように動作します。

- ① S C I は通信回線を監視し、スタートビットの“0”を検出すると内部を同期化し、受信を開始します。

- ② 受信したデータをR S R のL S B からM S B の順に格納します。

- ③ パリティビットおよび、ストップビットを受信します。

受信後、S C I は以下のチェックを行います。

- (a) パリティチェック：受信データの“1”的数をチェックし、これがS M R のO / E ビットで設定した偶数／奇数パリティになっているかをチェックします。

- (b) ストップビットチェック：ストップビットが“1”であるかをチェックします。

ただし、2ストップビットの場合、1ビット目のストップビットのみをチェックします。

- (c) ステータスチェック：R D R F フラグが“0”であり、受信データをR S R からR D R に転送できる状態であるかをチェックします。

以上のチェックがすべてパスしたとき、R D R F フラグが“1”にセットされ、R D R に受信データが格納されます。

エラーチェックで受信エラー\*を発生すると表13.11のように動作します。

【注】\* 受信エラーが発生した状態では、以後の受信動作ができません。

また、受信時にR D R F フラグが“1”にセットされませんので、必ずエラーフラグを“0”にクリアしてください。

- ④ R D R F フラグが“1”になったとき、S C R のR I E ビットが“1”にセットされていると受信データフル割込み（R X I ）要求を発生します。

また、O R E R 、P E R 、F E R フラグのいずれかが“1”になったとき、S C R のR I E ビットが“1”にセットされていると受信エラー割込み（E R I ）要求を発生します。

表13.11 受信エラーと発生条件

| 受信エラー名    | 略称      | 発生条件                                          | データ転送                         |

|-----------|---------|-----------------------------------------------|-------------------------------|

| オーバランエラー  | O R E R | S S R のR D R F フラグが“1”にセットされたまま次のデータ受信を完了したとき | R S R からR D R に受信データは転送されません。 |

| フレーミングエラー | F E R   | ストップビットが“0”的とき                                | R S R からR D R に受信データは転送されます。  |

| パリティエラー   | P E R   | S M R で設定した偶数／奇数パリティの設定と受信したデータが異なるとき         | R S R からR D R に受信データが転送されます。  |

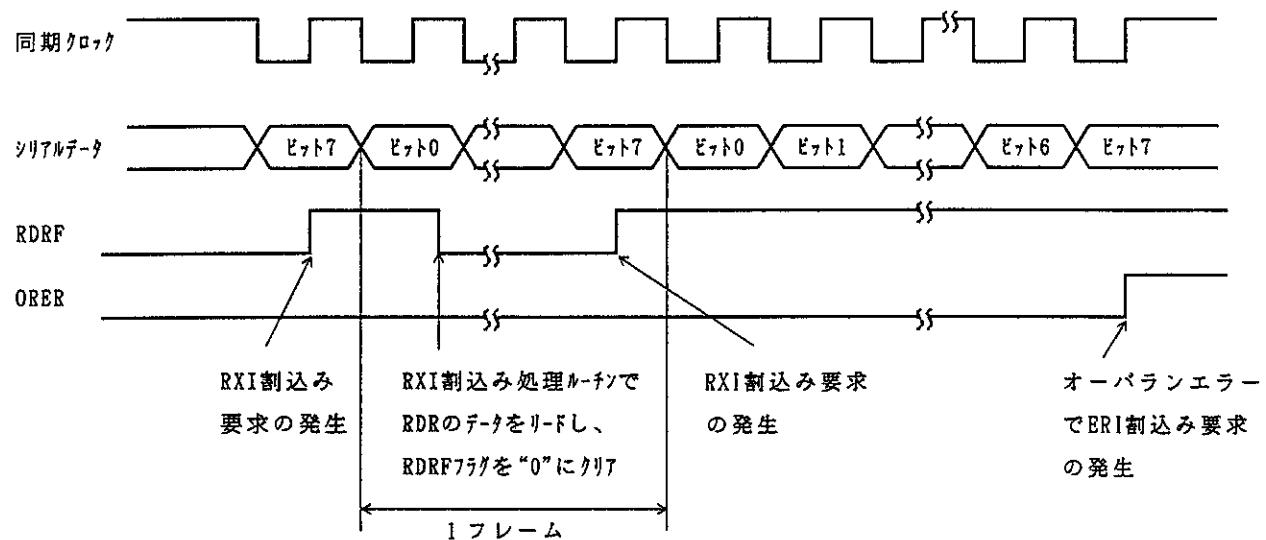

調歩同期式モード受信時の動作例を図13.8に示します。

図13.8 SCIの受信時の動作例 (8ビットデータ/パリティあり/1ストップビットの例)

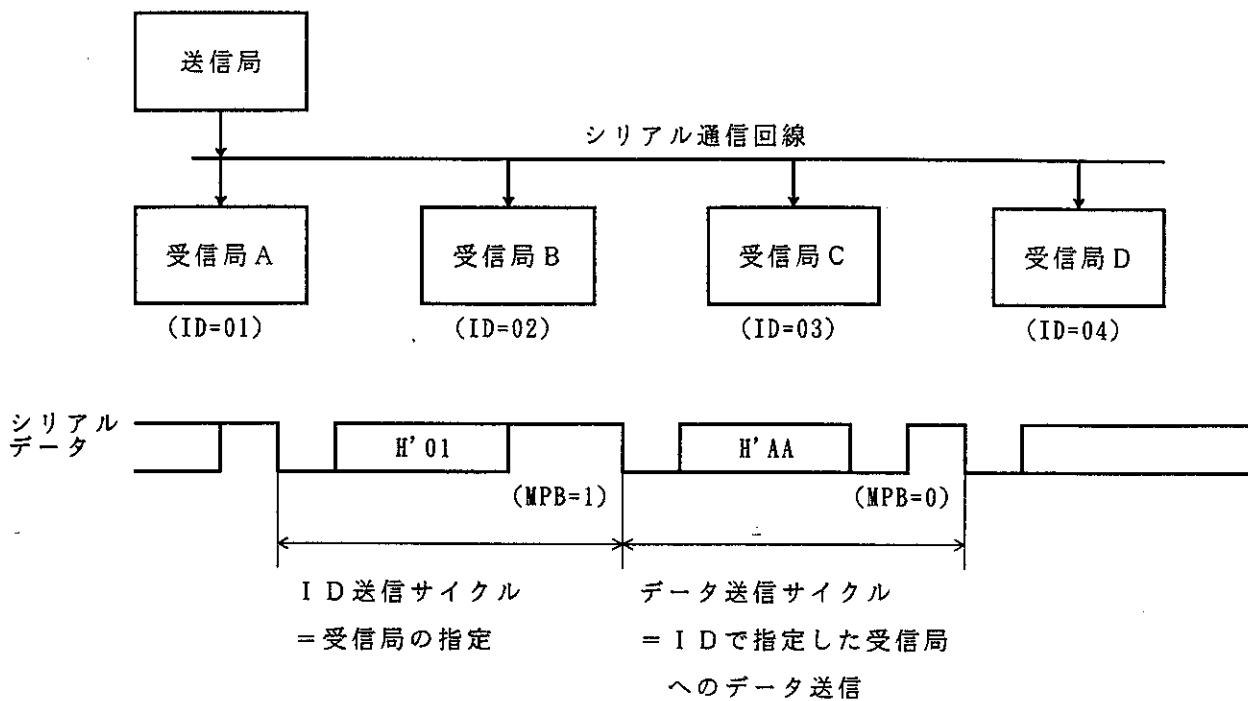

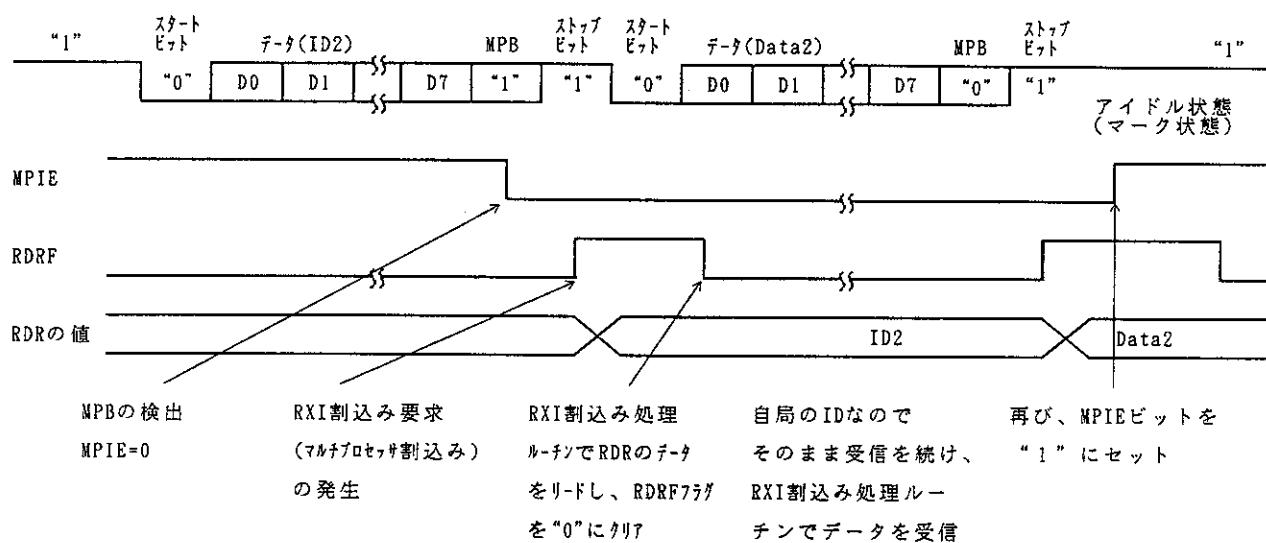

### 13.3.3 マルチプロセッサ通信機能

マルチプロセッサ通信機能とは、調歩同期式モードでマルチプロセッサビットを付加したフォーマット（マルチプロセッサフォーマット）でシリアル通信をする機能です。この機能を使用すると、複数のプロセッサ間でシリアル通信回線を共有したデータの送受信ができます。

マルチプロセッサ通信を行うとき、受信局は各々固有のIDコードでアドレッシングされています。

シリアル通信サイクルは、受信局を指定するID送信サイクルとデータ送信サイクルの2つから構成されます。このID送信サイクルとデータ送信サイクルの区別は、マルチプロセッサビットで行います。

送信局は、まず、シリアル通信を行いたい受信局のIDを、マルチプロセッサビット“1”を付加したデータにして送信します。続いて、送信データを、マルチプロセッサビット“0”を付加したデータにして送信します。

受信局は、マルチプロセッサビット“1”的データが送信されるまでは、データを読み飛ばします。

マルチプロセッサビット“1”的データを受信したとき、受信局は自局のIDと比較します。そして、一致した局は続いて送信されるデータを受信します。一方一致しなかった局は、再びマルチプロセッサビット“1”的データが送信されるまでは、データを読み飛ばします。このようにして複数のプロセッサ間のデータ送受信が行われます。

図13.9にマルチプロセッサフォーマットを使用したプロセッサ間通信の例を示します。

#### (1) 送信／受信フォーマット

送信／受信フォーマットは4種類です。

マルチプロセッサフォーマットを指定した場合は、パリティビットの指定は無効です。

詳細は表13.10を参照してください。

(2) クロック

調歩同期式モードの項を参照してください。

《記号説明》

MPB : マルチプロセッサビット

図13.9 マルチプロセッサフォーマットを使用したプロセッサ間通信の例

(受信局 Aへのデータ H' AA の送信の例)

### (3) データの送信／受信動作

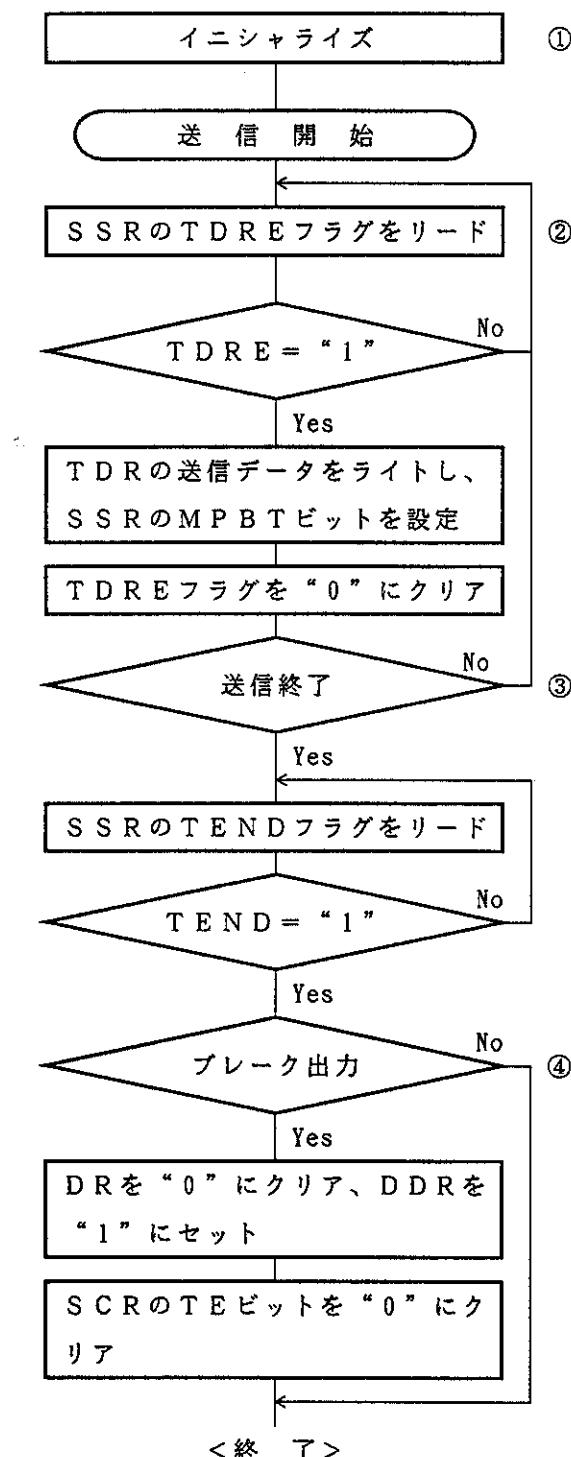

#### ■マルチプロセッサシリアルデータ送信

図13.10にマルチプロセッサシリアル送信のフローチャートの例を示します。

マルチプロセッサシリアルデータ送信は、以下の手順に従い行ってください。

①

#### ① SCIのイニシャライズ：

TxD端子は自動的に送信データ出力端子になります。

②

#### ② SCIの状態を確認して、送信データをライト：

SSRをリードして、TDRフラグが“1”であることを確認した後、TDRに送信データをライトします。

また、SSRのMPBTビットを“0”、または“1”に設定します。

最後にTDREフラグを“0”にクリアしてください。

③

#### ③ シリアル送信の継続手順：

シリアル送信を続けるときには、必ずTDRフラグの“1”をリードしてライト可能であることを確認した後にTDRにデータをライトし、続いてTDREフラグを“0”にクリアしてください。

ただし、送信データエンティティ割込み(TXI)要求でDMAを起動しTDRにデータをライトする場合にはTDREフラグのチェック、およびクリアは自動的に行われます。

④

#### ④ シリアル送信の終了時にブレークを出力：

シリアル送信時にブレークを出力するときには、ポートのDDRを“1”にセットし、DRを“0”にクリアした後にSCRのTEビットを“0”にクリアします。

図13.10 マルチプロセッサシリアル送信のフローチャートの例

S C I は、シリアル送信時に以下のように動作します。

(1) S C I は、S S R の T D R E フラグを監視し、“0”であると T D R にデータがライトされたと認識し、T D R から T S R にデータを転送します。

(2) T D R から T S R へデータを転送した後に T D R E フラグを “1” にセットし、送信を開始します。

このとき、S C R の T I E ビットが “1” にセットされていると送信データエンプティ割込み (T X I ) 要求を発生します。

シリアル送信データは、以下の順に TxD 端子から送りだされます。

(a) スタートビット：1 ビットの “0” が出力されます。

(b) 送信データ：8 ビット／7 ビットのデータが L S B から順に出力されます。

(c) マルチプロセッサビット：1 ビットのマルチプロセッサビット (M P B T の値) が出力されます。

(d) ストップビット：1 ビット／2 ビットの “1” (ストップビット) が出力されます。

(e) マーク状態：次の送信を開始するスタートビットを送り出すまで “1” を出力し続けます。

(3) S C I は、ストップビットを送り出すタイミングで T D R E フラグをチェックします。

T D R E フラグが “0” であると T D R から T S R にデータを転送し、ストップビットを送り出した後、次のフレームのシリアル送信を開始します。

T D R E フラグが “1” であると S S R の T E N D フラグを “1” にセットし、ストップビットを送り出した後、“1” を出力するマーク状態になります。このとき S C R の T E I E ビットが “1” にセットされていると送信終了割込み (T E I ) 要求を発生します。

図 13.11 にマルチプロセッサフォーマットの S C I の送信時の動作例を示します。

図 13.11 S C I の送信時の動作例

(8 ビットデータ／マルチプロセッサビットあり／1 ストップビットの例)

## ■マルチプロセッサシリアルデータ受信

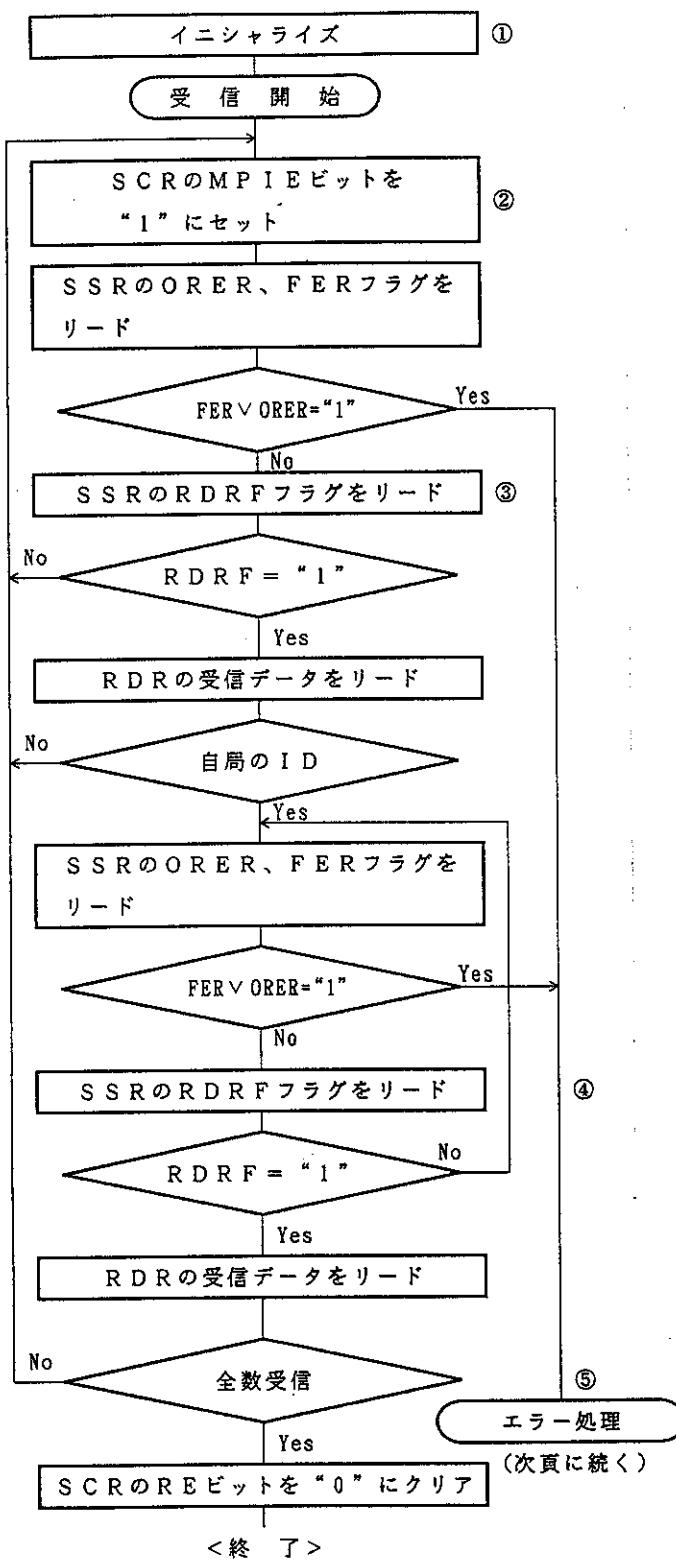

図13.12にマルチプロセッサシリアル受信のフローチャートの例を示します。

マルチプロセッサシリアルデータ受信は、以下の手順に従い行ってください。

① SCIのイニシャライズ：

RxD端子は自動的に受信データ入力端子になります。

② ID受信サイクル：

SCRのMPIEビットを“1”にセットしておきます。

③ SCIの状態を確認して、IDの受信と比較：

SSRをリードして、RDRFフラグが“1”であることを確認した後、RDRのデータをリードし、自局のIDと比較します。

自局のIDでないときには、再びMPIEビットを“1”にセットし、RDRFフラグを“0”にクリアします。

自局のIDのときには、RDRFフラグを“0”にクリアします。

④ SCIの状態を確認してデータの受信：

SSRをリードして、RDRFフラグが“1”であることを確認した後、RDRのデータをリードします。

⑤ 受信エラー処理とブレークの検出：

受信エラーが発生したときには、SSRのORER、FERフラグをリードしてエラーを判定します。所定のエラー処理を行った後、必ずORER、FERフラグをすべて“0”にクリアしてください。

ORER、FERフラグのいずれかが“1”にセットされた状態では受信を再開できません。

また、フレーミングエラー時にRxD端子の値をリードすることでブレークの検出ができます。

図13.12 マルチプロセッサシリアル受信のフローチャートの例(1)

図13.12 マルチプロセッサシリアル受信のフローチャートの例(2)

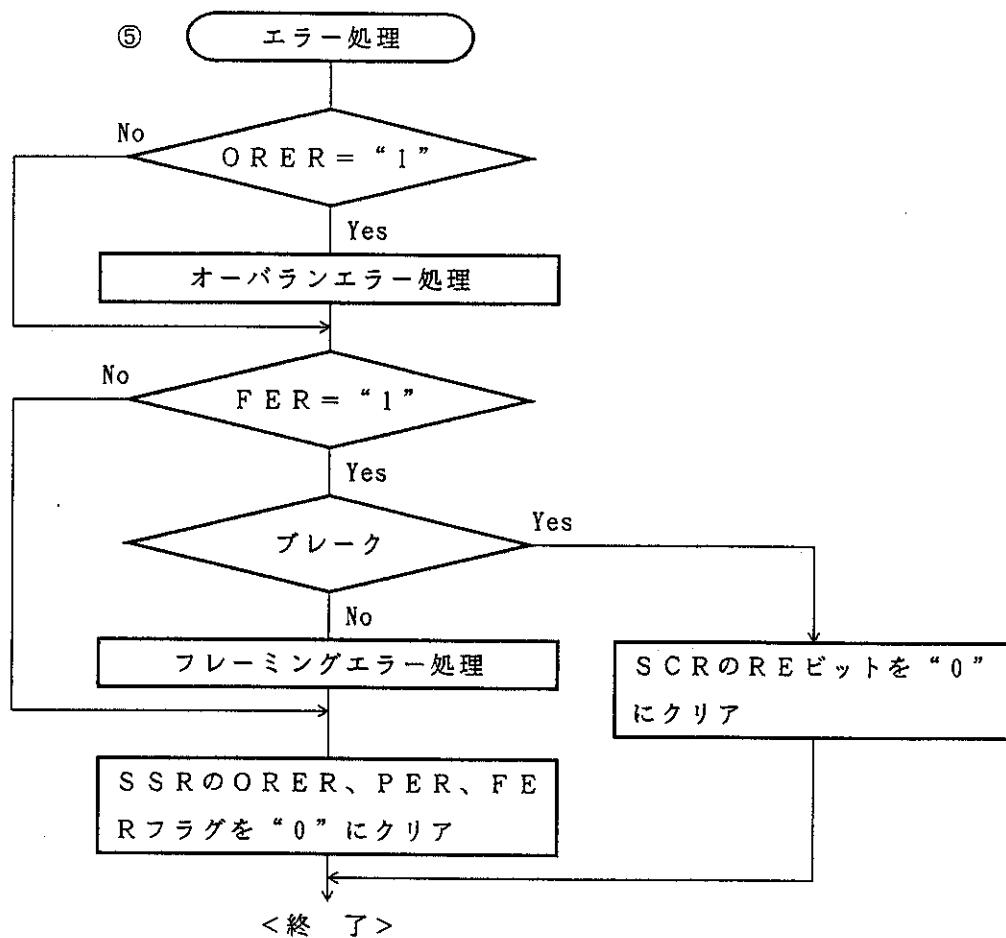

図13.13にマルチプロセッサフォーマットのSCIの受信時の動作例を示します。

(a) 自局の ID と一致しないとき

(b) 自局の I.D と一致したとき

図 13.13 SCI の受信時の動作例

(8ビットデータ/マルチプロセッサビットあり/1ストップビットの例)

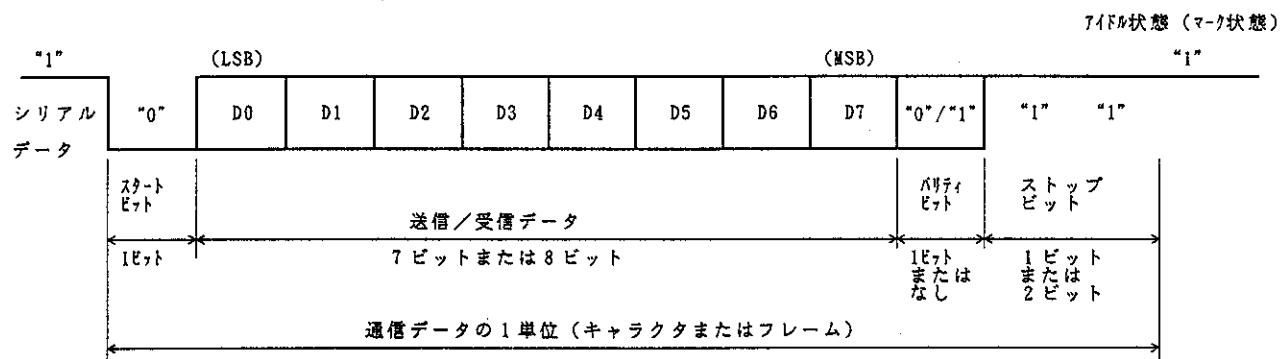

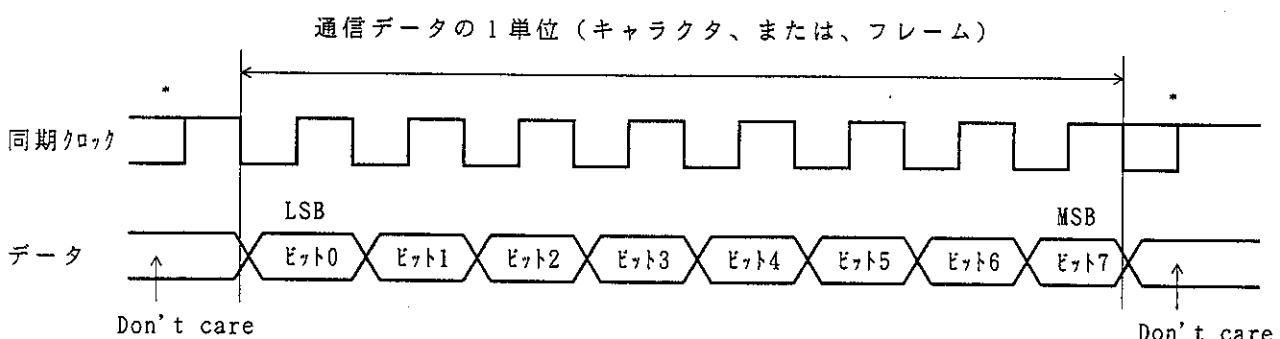

### 13.3.4 クロック同期式モード時の動作

クロック同期式モードは、クロックパルスに同期してデータを送信／受信するモードで、高速シリアル通信に適しています。

S C I 内部では、送信部と受信部は独立していますので、クロックを共有することで全二重通信ができます。

また、送信部と受信部が共にダブルバッファ構造になっていますので送信／受信中にデータのリード／ライトができ、連続送信／受信が可能です。

クロック同期式シリアル通信の一般的なフォーマットを図13.14に示します。

【注】\* 連続送信／受信のとき以外は“High”レベル

図13.14 クロック同期式通信のデータフォーマット

クロック同期式シリアル通信では、通信回線のデータは同期クロックの立上がりから次の立上がりまで出力されます。また、同期クロックの立上がりでデータの確定が保証されます。

シリアル通信の1キャラクタは、データのL S Bから始まり最後にM S Bが出力されます。M S B出力後の通信回線の状態はM S Bの状態を保ちます。

クロック同期式モードでは、S C Iは同期クロックの立上がりに同期してデータを受信します。

#### (1) 送信／受信フォーマット

8ビットデータ固定です。

パリティビットやマルチプロセッサビットの付加はできません。

#### (2) クロック

S M RのC/AビットとS C RのCKE1、CKE0ビットの設定により内蔵ボーレートジェネレータの生成した内部クロック、または、SCK端子から入力された外部同期クロックの2種類から選択できます。S C Iのクロックソースの選択については表13.9を参照してください。

内部クロックで動作させるとき、SCK端子からは同期クロックが出力されます。

同期クロックは1キャラクタの送受信で8パルス出力され、送信／受信を行わないときには“High”レベルに固定されます。ただし、受信のみの動作のときは、オーバランエラーが発生するか、R Eビットを0にクリアするまで同期クロックは出力されます。1キャラクタ単位の受信動作を行いたいときは、クロックソースは外部クロックを選択してください。

### (3) データの送信／受信動作

#### ■ S C I のイニシャライズ（クロック同期式）

データの送信／受信前には、S C RのT E、R Eビットを“0”にクリアした後、以下の手順に従いS C Iをイニシャライズしてください。

モードの変更、通信フォーマットの変更などの場合には必ず、T E、R Eビットを“0”にクリアしてから下記手順で変更してください。T Eビットを“0”にクリアするとT D R Eフラグは“1”にセットされ、T S Rがイニシャライズされます。

R Eビットを“0”にクリアしてもR D R F、P E R、F E R、O R Eの各フラグ、およびR D Rの内容は保持されますので注意してください。

図13.15にS C Iのイニシャライズフローチャートの例を示します。

① S C Rにクロックの選択を設定してください。なお、R I E、T I E、T E I E、M P I E、T E、R Eビットは必ず“0”に設定してください。

② S M Rに送信／受信フォーマットを設定します。

③ B R Rにビットレートに対応する値をライドします。ただし、外部クロックを使用する場合にはこの作業は必要ありません。

④ 少なくとも1ビット期間待ってから、S C RのT Eまたは、R Eビットを“1”にセットします。

また、R I E、T I E、T E I E、M P I Eビットを設定してください。T E、R Eビットの設定でTxD、RxD端子が使用可能になります。

図13.15 S C Iのイニシャライズフローチャートの例

■シリアルデータ送信（クロック同期式）

図13.16にシリアル送信のフローチャートの例を示します。

シリアルデータ送信は以下の手順に従い行ってください。

①

① SCIのイニシャライズ：

TxD端子は自動的に送信データ出力端子になります。

②

② SCIの状態を確認して、送信データをライト：

SSRをリードして、TDRフラグが“1”であることを確認した後、TDRに送信データをライトし、TDRフラグを“0”にクリアします。

③

③ シリアル送信の継続手順：

シリアル送信を続けるときには、必ずTDRフラグの“1”をリードしてライト可能であることを確認した後にTDRにデータをライトし、続いてTDRフラグを“0”にクリアしてください。

ただし、送信データエンティティ割込み(TXI)要求でDMAを起動しTDRにデータをライトする場合にはTDRフラグのチェック、およびクリアは自動的に行われます。

図13.16 シリアル送信のフローチャートの例

S C I はシリアル送信時に以下のように動作します。

(1) S C I は、S S R の T D R E フラグを監視し、“0”であると T D R にデータがライトされたと認識し、T D R から T S R にデータを転送します。

(2) T D R から T S R へデータを転送した後に T D R E フラグを“1”にセットし、送信を開始します。

このとき、S C R の T I E ビットが“1”にセットされていると送信データエンブティ割込み（T X I）要求を発生します。

クロック出力モードに設定したときには、S C I は同期クロックを8パルス出力します。

外部クロックに設定したときには、入力クロックに同期してデータを出力します。

シリアル送信データは、L S B (ビット0)～M S B (ビット7)の順にTxD端子から送り出されます。

(3) S C I は、M S B (ビット7)を送り出すタイミングで T D R E フラグをチェックします。

T D R E フラグが“0”であると T D R から T S R にデータを転送し、次フレームのシリアル送信を開始します。

T D R E フラグが“1”であると S S R の T E N D フラグを“1”にセットし、M S B (ビット7)を送り出した後、TxD端子は状態を保持します。

このとき S C R の T E I E ビットが“1”にセットされていると送信終了割込み（T E I）要求を発生します。

(4) シリアル送信終了後は、SCK端子は固定になります。

図13.17にS C Iの送信時の動作例を示します。

図13.17 S C I の送信時の動作例

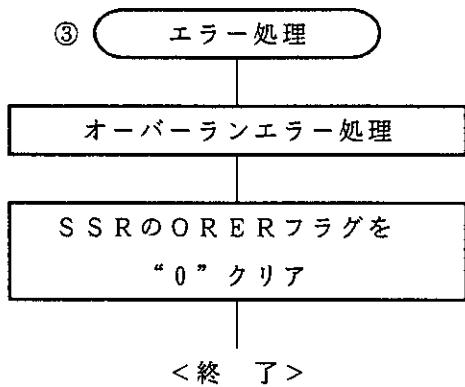

## ■シリアルデータ受信（クロック同期式）

図13.18にシリアル受信フローチャートの例を示します。

シリアルデータ受信は以下の手順に従い行ってください。

動作モードを調歩同期式モードからクロック同期式モードに切り換える際には、必ず、ORER、PER、FERの各フラグが“0”にクリアされていることを確認してください。

FER、PERフラグが“1”にセットされているとRDRFフラグがセットされません。また、送信／受信動作が行えません。

### ① SCIのイニシャライズ：

RxD端子は自動的に受信データ入力端子になります。

### ②③ 受信エラー処理：

受信エラーが発生したときには、SSRのORERフラグをリードしてから、所定のエラー処理を行った後、ORERフラグを“0”にクリアしてください。

ORERフラグ=“1”的状態では、送信／受信を再開できません。

### ④ SCIの状態を確認して受信データのリード：

SSRをリードして、RDRFフラグが“1”であることを確認した後、RDRの受信データをリードし、RDRFフラグを“0”にクリアします。RDRFフラグが“0”から“1”に変化したことは、RXI割込みによっても知ることができます。

### ⑤ シリアル受信の継続手順：

シリアル受信を続けるときには、現在のフレームのMSB(ビット7)を受信する前に、RDRFフラグのリード、RDRのリード、RDRFフラグの“0”クリアを終了しておいてください。ただし、受信データフル割込み(RXI)要求でDMACを起動し、RDRの値をリードする場合にはRDRFフラグのクリアは自動的に行われます。

図13.18 シリアルデータ受信フローチャートの例(1)

図13.18 シリアルデータ受信フローチャートの例(2)

SCIは受信時に以下のように動作します。

- ① SCIは同期クロックの入力または出力に同期して内部を初期化します。

- ② 受信したデータをRSRのLSBからMSBの順に格納します。

受信後、SCIは、RDRFフラグが“0”であり、受信データをRSRからRDRに転送できる状態であるかをチェックします。

このチェックがパスしたときRDRFフラグが“1”にセットされ、RDRに受信データが格納されます。エラーチェックで受信エラーを発生すると、表13.11のように動作します。

エラーチェックで受信エラーを発生した状態では以後の送信、受信動作ができません。

- ③ RDRFフラグが“1”になったとき、SCRのRIEビットが“1”にセットされていると受信データフル割込み(RXI)要求を発生します。

また、ORERフラグが“1”になったとき、SCRのRIEビットが“1”にセットされていると受信エラー割込み(ERI)要求を発生します。

図13.19にS C Iの受信時の動作例を示します。

図13.19 S C I の受信時の動作例

## ■シリアルデータ送受信同時動作（クロック同期式）

図13.20にシリアル送受信同時動作のフローチャートの例を示します。

シリアルデータ送受信同時動作は、以下の手順に従い行ってください。

### ① イニシャライズ：

TxD端子は送信データ出力端子に、RxD端子は受信データ入力端子になり送受信同時動作可能状態になります。

### ② SCIの状態確認と送信データのライ

ト：

SSRをリードしてTDRフラグが“1”であることを確認した後、TDRに送信データをライトし、TDRフラグを“0”にクリアします。

TDRフラグが“0”から“1”に変化したことは、TXI割込みによっても知ることができます。

### ③ 受信エラー処理：

受信エラーが発生したときには、SSRのORERフラグをリードしてから、所定のエラー処理を行った後、ORERフラグを“0”にクリアしてください。ORERフラグが“1”にセットされた状態では送信／受信を再開できません。

### ④ SCIの状態を確認して受信データのリード：

SSRをリードして、RDRFフラグが“1”であることを確認した後、RDRの受信データをリードし、RDRFフラグを“0”にクリアします。

RDRFフラグが“0”から“1”に変化したことは、RXI割込みによっても知ることができます。

図13.20 シリアル送受信同時動作のフローチャートの例(1)

⑤ シリアル送受信の継続手順：

シリアル送受信を続けるときには、現在のフレームの M S B (ビット 7) を受信する前に、R D R F フラグのリード、R D R のリード、R D R F フラグの “0”クリアを終了しておいてください。また、現在のフレームの M S B (ビット 7) を送信する前に T D R E フラグの “1” をリードしてライト可能であることを確認してください。さらに T D R にデータをライトし、T D R E フラグを “0” にクリアしておいてください。

ただし、送信データエンプティ割込み (T X I) 要求で D M A C を起動し T D R にデータをライトする場合には、T D R E フラグのチェック、およびクリアは自動的に行われます。また、受信データフル割込み (R X I) 要求で D M A C を起動し R D R の値をリードする場合には R D R F フラグのクリアは自動的に行われます。

【注】 送信、または受信動作から同時送受信に切り換えるときには、T E ビットとR E ビットを“0”にクリアしてからT E ビットとR E ビットを“1”にセットしてください。

図13.20 シリアル送受信同時動作のフローチャートの例(2)

## 13.4 SCI 割込み

SCIには、送信終了割込み(TEI)要求、受信エラー割込み(ERI)要求、受信データフル割込み(RXI)要求、送信データエンプティ割込み(TXI)要求の4種類の割込み要因があります。表13.12に各割込み要因と優先順位を示します。各割込み要因は、SCRのTIEビット、RIEビットおよびTEIEビットで許可／禁止できます。また、各割込み要求はそれぞれ独立に割込みコントローラに送られます。

SSRのTDRFフラグが“1”にセットされると、TXI割込み要求が発生します。また、SRのTENDフラグが“1”にセットされると、TEI割込み要求が発生します。TXI割込み要求によりDMACを起動してデータ転送を行うことができます。TDRFフラグはDMACによるデータ転送時に自動的に“0”にクリアされます。なお、TEI割込み要求でDMACの起動はできません。

SSRのRDRFフラグが“1”にセットされるとRXI割込み要求が発生します。SSRのOERR、PER、FERフラグのいずれかが“1”にセットされるとERI割込み要求が発生します。RXI割込み要求でDMACを起動してデータ転送を行うことができます。RDRFフラグはDMACによるデータ転送時に自動的に“0”にクリアされます。なお、ERI割込み要求でDMACの起動はできません。

SCIチャネル0の割込みによりDMACの起動が可能です。

表13.12 SCI割込み要因

| 割込み要因 | O S O S                   | 優先順位             |

|-------|---------------------------|------------------|

| ERI   | 受信エラー(OERR、FER、PER)による割込み | 高<br>↑<br>↓<br>低 |

| RXI   | 受信データフル(RDRF)による割込み       |                  |

| TXI   | 送信データエンプティ(TDRF)による割込み    |                  |

| TEI   | 送信終了(TEND)による割込み          |                  |

## 13.5 使用上の注意

SCIを使用する際は、以下のことに注意してください。

### (1) TDRへのライトとTDR.Eフラグの関係について

SSRのTDR.EフラグはTDRからTSRに送信データの転送が行われたことを示すステータスフラグです。SCIがTDRからTSRにデータを転送すると、TDR.Eフラグが“1”にセットされます。

TDRへのデータのライトは、TDR.Eフラグの状態にかかわらず行うことができます。しかし、TDR.Eフラグが“0”的状態で新しいデータをTDRにライトすると、TDRに格納されていたデータは、まだTSRに転送されていないため失われてしまいます。したがってTDRへの送信データのライトは、必ずTDR.Eフラグが“1”にセットされていることを確認してから行ってください。

### (2) 複数の受信エラーが同時に発生した場合の動作について

複数の受信エラーが同時に発生した場合、SSRの各ステータスフラグの状態は、表13.13のようになります。また、オーバランエラーが発生した場合にはRSRからRDRへのデータ転送は行われず、受信データは失われます。

表13.13 SSRのステータスフラグの状態と受信データの転送

| SSRのステータスフラグ |         |       |       | 受信データ転送<br>RSR→RDR | 受信エラーの状態                   |

|--------------|---------|-------|-------|--------------------|----------------------------|

| RDR.F        | O.R.E.R | F.E.R | P.E.R |                    |                            |

| 1            | 1       | 0     | 0     | ×                  | オーバランエラー                   |

| 0            | 0       | 1     | 0     | ○                  | フレーミングエラー                  |

| 0            | 0       | 0     | 1     | ○                  | パリティエラー                    |

| 1            | 1       | 1     | 0     | ×                  | オーバランエラー+フレーミングエラー         |

| 1            | 1       | 0     | 1     | ×                  | オーバランエラー+パリティエラー           |

| 0            | 0       | 1     | 1     | ○                  | フレーミングエラー+パリティエラー          |

| 1            | 1       | 1     | 1     | ×                  | オーバランエラー+フレーミングエラー+パリティエラー |

【注】 ○：RSR→RDRに受信データを転送します。

×：RSR→RDRに受信データを転送しません。

### (3) ブレークの検出と処理について

フレーミングエラー（F E R）検出時にRxD端子の値を直接リードすることで、ブレークを検出できます。ブレークでは、RxD端子からの入力がすべて“0”になりますのでF E Rフラグがセットされ、またパリティエラー（P E R）もセットされる場合があります。

S C Iは、ブレークを受信した後も受信動作を続けますので、F E Rフラグを“0”にクリアしても再び“1”にセットされますので、注意してください。

### (4) ブレークの送り出し

TxD端子は、D RとD D Rにより入出力方向とレベルが決まるI / Oポートと兼用になっています。これをを利用してブレークの送り出しができます。

シリアル送信のイニシャライズからT Eビットを“1”にセットするまでは、マーク状態をD Rの値で代替します（T Eビットを1にセットするまで、TxD端子として機能しません）。このため、最初はD D RとD Rを“1”に設定しておきます。

シリアル送信時にブレークを送り出したいときはD Rを“0”にクリアした後、T Eビットを“0”にクリアします。

T Eビットを“0”にクリアすると現在の送信状態とは無関係に送信部は初期化され、TxD端子はI / Oポートになり、TxD端子から“0”が出力されます。

### (5) 受信エラーフラグと送信動作について（クロック同期式モードのみ）

受信エラーフラグ（O R E R、P E R、F E R）が“1”にセットされた状態では、T D R Eフラグを“0”にクリアしても送信を開始できません。必ず送信開始時には、受信エラーフラグを“0”にクリアしておいてください。

また、R Eビットを“0”にクリアしても受信エラーフラグは“0”にクリアできませんので注意してください。

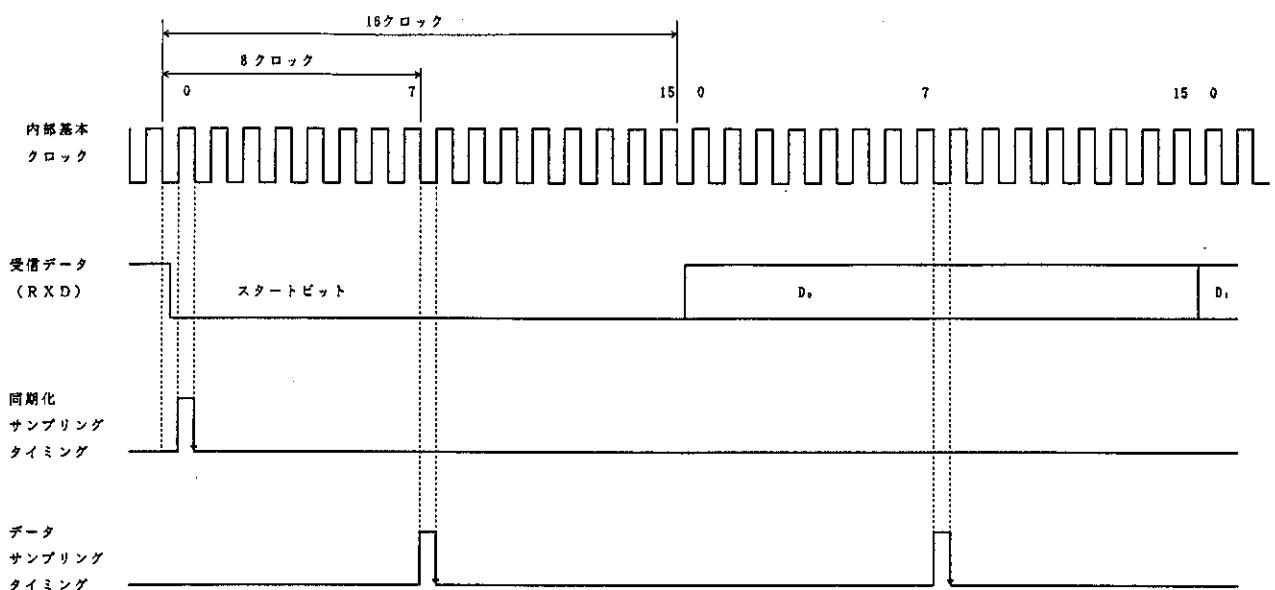

### (6) 調歩同期式モードの受信データサンプリングタイミングと受信マージン

調歩同期式モードでは、S C Iは転送レートの16倍の周波数の基本クロックで動作しています。

受信時にS C Iは、スタートビットの立下がりを基本クロックでサンプリングして、内部を同期化します。また、受信データを基本クロックの8クロック目の立上がりエッジで内部に取り込みます。これを図13.21に示します。

図13.21 調歩同期式モードの受信データサンプリングタイミング

したがって、調歩同期式モードでの受信マージンは式(1)のように表すことができます。

$$M = \left| \left( 0.5 - \frac{1}{2N} \right) - (L - 0.5)F - \frac{|D - 0.5|}{N} \right| \times 100\% \quad \cdots \cdots \text{式(1)}$$

M : 受信マージン (%)

N : クロックに対するビットレートの比 ( $N = 16$ )

D : クロックデューティ ( $D = 0 \sim 1.0$ )

L : フレーム長 ( $L = 9 \sim 12$ )

F : クロック周波数の偏差の絶対値

式(1)で、 $F = 0$ 、 $D = 0.5$ とすると、受信マージンは式(2)より 46.875% となります。

$D = 0.5$ 、 $F = 0$  のとき、

$$\begin{aligned} M &= \left( 0.5 - \frac{1}{2 \times 16} \right) \times 100\% \\ &= 46.875\% \end{aligned} \quad \cdots \cdots \text{式(2)}$$

ただし、この値はあくまでも計算上の値ですので、システム設計の際には20~30%の余裕を持たせてください。

(7) DMA C 使用上の制約事項

DMA Cにより、RDRのリードを行うときは必ずDTCRのDTS2～0ビットで起動要因を当該SCIの受信完了割込み(RXI)に設定してください。

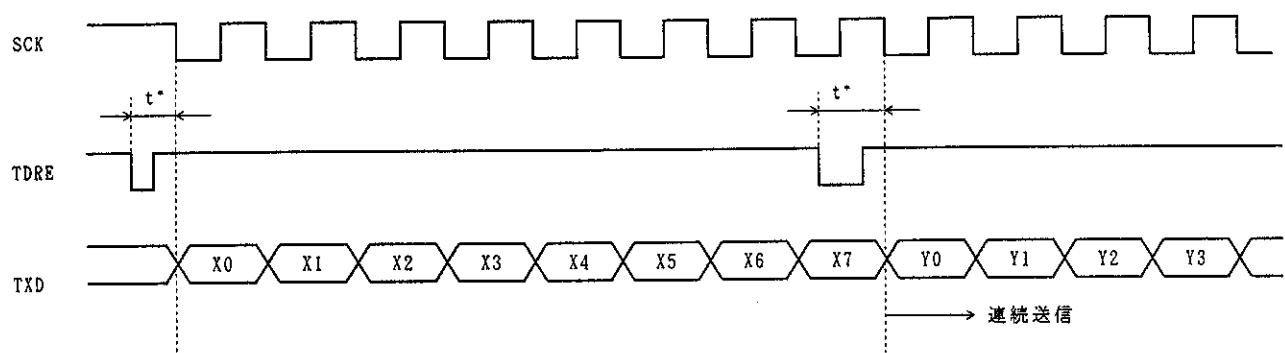

(8) クロック同期式使用上の制約事項

同期クロックに外部クロックソースを使用しデータ送信を行う場合、SSRのTDRのクリアから各フレームに対応する送信クロックの先頭(立ち上がりエッジ)までの間隔は、5ステート以上確保してください(図13.22参照)。本条件は連続送信を行う際にも必要です。

本条件が満たされない場合、誤動作することがあります。

\* :  $t \geq 5$  ステートとしてください。

図13.22 クロック同期式送信時の例