# 10. 16ビットインテグレーテッド タイマユニット(ITU)

## 第10章 目次

|                                    |     |

|------------------------------------|-----|

| 10.1 概要                            | 327 |

| 10.1.1 特長                          | 327 |

| 10.1.2 ブロック図                       | 330 |

| 10.1.3 端子構成                        | 335 |

| 10.1.4 レジスタ構成                      | 337 |

| 10.2 各レジスタの説明                      | 339 |

| 10.2.1 タイマスタートレジスタ(TSTR)           | 339 |

| 10.2.2 タイマシンクロレジスタ(TSNC)           | 341 |

| 10.2.3 タイマモードレジスタ(TMDR)            | 343 |

| 10.2.4 タイマファンクションコントロールレジスタ(TFCR)  | 347 |

| 10.2.5 タイマアウトプットマスティネーブルレジスタ(TOER) | 350 |

| 10.2.6 タイマアウトプットコントロールレジスタ(TOCR)   | 353 |

| 10.2.7 タイマカウンタ(TCNT)               | 355 |

| 10.2.8 ジェネラルレジスタA、B(GRA、GRB)       | 356 |

| 10.2.9 バッファレジスタA、B(BRA、BRB)        | 357 |

| 10.2.10 タイマコントロールレジスタ(TCR)         | 358 |

| 10.2.11 タイマI/Oコントロールレジスタ(TIOR)     | 361 |

| 10.2.12 タイマステータスレジスタ(TSR)          | 364 |

| 10.2.13 タイマインタラプトイネーブルレジスタ(TIER)   | 367 |

| 10.3 CPUとのインターフェース                 | 369 |

| 10.3.1 16ビットアクセス可能なレジスタ            | 369 |

| 10.3.2 8ビットアクセスのレジスタ               | 371 |

|        |                    |     |

|--------|--------------------|-----|

| 10.4   | 動作説明               | 372 |

| 10.4.1 | 概要                 | 372 |

| 10.4.2 | 基本機能               | 374 |

| 10.4.3 | 同期動作               | 383 |

| 10.4.4 | PWMモード             | 385 |

| 10.4.5 | リセット同期PWMモード       | 389 |

| 10.4.6 | 相補PWMモード           | 392 |

| 10.4.7 | 位相計数モード            | 401 |

| 10.4.8 | バッファ動作             | 403 |

| 10.4.9 | ITU出力タイミング         | 410 |

| 10.5   | 割込み                | 413 |

| 10.5.1 | ステータスフラグのセットタイミング  | 413 |

| 10.5.2 | ステータスフラグのクリアタイミング  | 415 |

| 10.5.3 | 割込み要因とDMAコントローラの起動 | 416 |

| 10.6   | 使用上の注意             | 417 |

---

## 10.1 概要

H8/3048シリーズは、5チャネルの16ビットタイマにより構成される16ビットインテグレーテッドタイマユニット（ITU）を内蔵しています。

消費電流低減のためITUを使用しない場合には、ITUを単独に停止することができます。詳細は「20.6 モジュールスタンバイ機能」を参照してください。

### 10.1.1 特長

ITUの特長を以下に示します。

- 最大12種類のパルス出力、または最大10種類のパルス入力処理が可能

- 各チャネル2本、合計10本のジェネラルレジスタ（GR）を持ち、各レジスタ独立にアウトプットコンペア／インプットキャプチャの機能設定が可能

- 各チャネルとも8種類のカウンタ入力クロックを選択可能

- 内部クロック： $\phi$ 、 $\phi/2$ 、 $\phi/4$ 、 $\phi/8$

- 外部クロック：TCLKA、TCLKB、TCLKC、TCLKD

- 各チャネルとも次の動作モードを設定可能

- ・コンペアマッチによる波形出力：0出力／1出力／トグル出力が選択可能（チャネル2は0出力／1出力が可能）

- ・インプットキャプチャ機能：立上がりエッジ／立下がりエッジ／両エッジ検出が選択可能

- ・カウンタクリア機能：コンペアマッチ／インプットキャプチャによるカウンタクリアが可能

- ・同期動作：複数のタイマカウンタ（TCNT）への同時書き込みが可能

コンペアマッチ／インプットキャプチャによる同時クリアが可能

カウンタの同期動作による各レジスタの同期入出力が可能

- ・PWMモード：任意デューティのPWM出力が可能

同期動作と組み合わせることにより、最大5相のPWM出力が可能

- チャネル2は位相計数モードを設定可能

- 2相エンコーダのカウント数の自動計測が可能

- チャネル3、4は次の動作モードを設定可能

- ・リセット同期PWMモード：チャネル3、4を組み合わせることにより、正相・逆相のPWM波形を3相出力可能

- ・相補PWMモード：チャネル3、4を組み合わせることにより、正相・逆相がノンオーバラップの関係にあるPWM波形を3相出力可能

- ・バッファ動作：インプットキャプチャレジスタのダブルバッファ構成が可能

アウトプットコンペアレジスタの自動書き換えが可能

■内部16ビットバスによる高速アクセス

T C N T、G R、およびバッファレジスタ（B R）の16ビットレジスタに対して、16ビットバスによる高速アクセスが可能

■15種類の割込み要因

各チャネルともコンペアマッチ／インプットキャプチャ兼用割込み×2要因、オーバフロー割込み×1要因があり、それぞれ独立に要求可能

■D M Aコントローラ（D M A C）の起動が可能

チャネル0～3のコンペアマッチ／インプットキャプチャ兼用割込み（1本×4チャネル）により、D M A Cの起動が可能

■プログラマブルパターンコントローラ（T P C）の出力トリガを生成可能

チャネル0～3のコンペアマッチ／インプットキャプチャ信号をT P Cの出力トリガとして使用可能

I T U の機能一覧を表10.1に示します。

表10.1 I T U の機能一覧

| 項目                                             | チャネル0                                                                                       | チャネル1                                                                               | チャネル2                                                                                | チャネル3                                                                                 | チャネル4                                                                                 |

|------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| カウントクロック                                       | 内部クロック: $\phi$ 、 $\phi/2$ 、 $\phi/4$ 、 $\phi/8$<br>外部クロック: TCLKA、TCLKB、TCLKC、TCLKDから独立に選択可能 |                                                                                     |                                                                                      |                                                                                       |                                                                                       |

| ジエネラルレジスタ<br>(アウトプットコンペア/インプットキャプチャ<br>兼用レジスタ) | G RA 0、<br>G RB 0                                                                           | G RA 1、<br>G RB 1                                                                   | G RA 2、<br>G RB 2                                                                    | G RA 3、<br>G RB 3                                                                     | G RA 4、<br>G RB 4                                                                     |

| バッファレジスタ                                       | —                                                                                           | —                                                                                   | —                                                                                    | B RA 3、<br>B RB 3                                                                     | B RA 4、<br>B RB 4                                                                     |

| 入出力端子                                          | TIOCA0、<br>TIOCB0                                                                           | TIOCA1、<br>TIOCB1                                                                   | TIOCA2、<br>TIOCB2                                                                    | TIOCA3、<br>TIOCB3                                                                     | TIOCA4、<br>TIOCB4                                                                     |

| 出力端子                                           | —                                                                                           | —                                                                                   | —                                                                                    | —                                                                                     | TOCXA4、<br>TOCXB4                                                                     |

| カウンタクリア機能                                      | G RA0/G RB0<br>のコンペアマッチ<br>または<br>インプットキャプチャ                                                | G RA1/G RB1<br>のコンペアマッチ<br>または<br>インプットキャプチャ                                        | G RA2/G RB2<br>のコンペアマッチ<br>または<br>インプットキャプチャ                                         | G RA3/G RB3<br>のコンペアマッチ<br>または<br>インプットキャプチャ                                          | G RA4/G RB4<br>のコンペアマッチ<br>または<br>インプットキャプチャ                                          |

| コンペア<br>マッチ                                    | 0出力                                                                                         | ○                                                                                   | ○                                                                                    | ○                                                                                     | ○                                                                                     |

|                                                | 1出力                                                                                         | ○                                                                                   | ○                                                                                    | ○                                                                                     | ○                                                                                     |

| 出力                                             | トグル出力                                                                                       | ○                                                                                   | ○                                                                                    | —                                                                                     | ○                                                                                     |

| インプットキャプチャ機能                                   | ○                                                                                           | ○                                                                                   | ○                                                                                    | ○                                                                                     | ○                                                                                     |

| 同期動作                                           | ○                                                                                           | ○                                                                                   | ○                                                                                    | ○                                                                                     | ○                                                                                     |

| P W M モード                                      | ○                                                                                           | ○                                                                                   | ○                                                                                    | ○                                                                                     | ○                                                                                     |

| リセット同期 P W M モード                               | —                                                                                           | —                                                                                   | —                                                                                    | —                                                                                     | ○                                                                                     |

| 相補 P W M モード                                   | —                                                                                           | —                                                                                   | —                                                                                    | —                                                                                     | ○                                                                                     |

| 位相計数モード                                        | —                                                                                           | —                                                                                   | ○                                                                                    | —                                                                                     | —                                                                                     |

| バッファ動作                                         | —                                                                                           | —                                                                                   | —                                                                                    | ○                                                                                     | ○                                                                                     |

| D M A C の起動                                    | G RA 0 の<br>コンペアマッチ<br>または<br>インプットキャプチャ                                                    | G RA 1 の<br>コンペアマッチ<br>または<br>インプットキャプチャ                                            | G RA 2 の<br>コンペアマッチ<br>または<br>インプットキャプチャ                                             | G RA 3 の<br>コンペアマッチ<br>または<br>インプットキャプチャ                                              | —                                                                                     |

| 割込み要因                                          | 3要因<br>• コンペアマッチ/<br>インプットキャプ<br>チャA0<br>• コンペアマッチ/<br>インプットキャプ<br>チャB0<br>• オーバフロー         | 3要因<br>• コンペアマッチ/<br>インプットキャプ<br>チャA1<br>• コンペアマッチ/<br>インプットキャプ<br>チャB1<br>• オーバフロー | 3要因<br>• コンペアマッチ/<br>インプットキャプ<br>チャA2<br>• コンペアマッチ/<br>インプットキャップ<br>チャB2<br>• オーバフロー | 3要因<br>• コンペアマッチ/<br>インプットキャップ<br>チャA3<br>• コンペアマッチ/<br>インプットキャップ<br>チャB3<br>• オーバフロー | 3要因<br>• コンペアマッチ/<br>インプットキャップ<br>チャA4<br>• コンペアマッチ/<br>インプットキャップ<br>チャB4<br>• オーバフロー |

《記号説明》

○: 可能

—: 不可

### 10.1.2 ブロック図

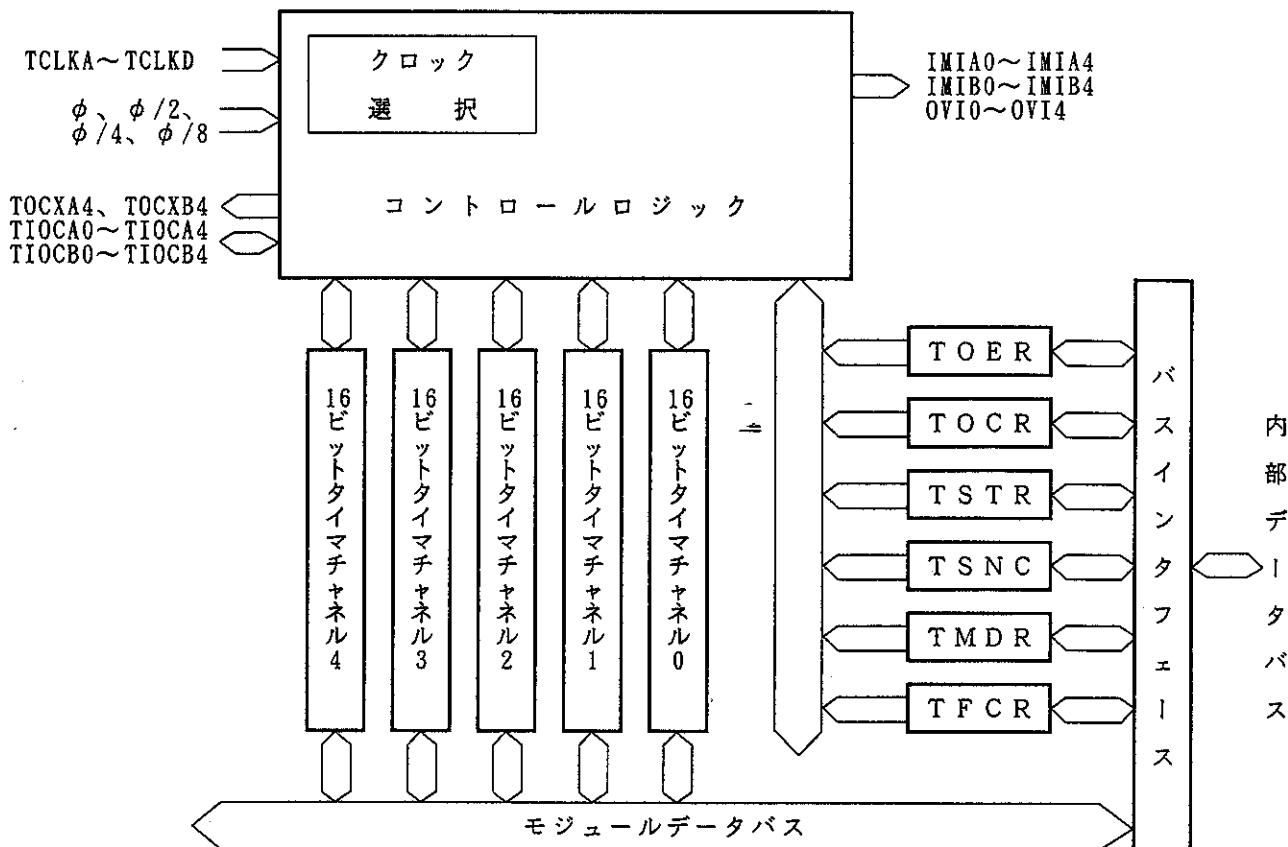

#### (1) ITUのブロック図（全体図）

ITUのブロック図（全体図）を図10.1に示します。

#### 《記号説明》

- TOER : タイマアウトプットマスタインペブルレジスタ (8ビット)

- TOCR : タイマアウトプットコントロールレジスタ (8ビット)

- TSTR : タイマスタートレジスタ (8ビット)

- TSNC : タイマシンクロレジスタ (8ビット)

- TMDR : タイマモードレジスタ (8ビット)

- TFCR : タイマファンクションコントロールレジスタ (8ビット)

図10.1 ITUのブロック図（全体図）

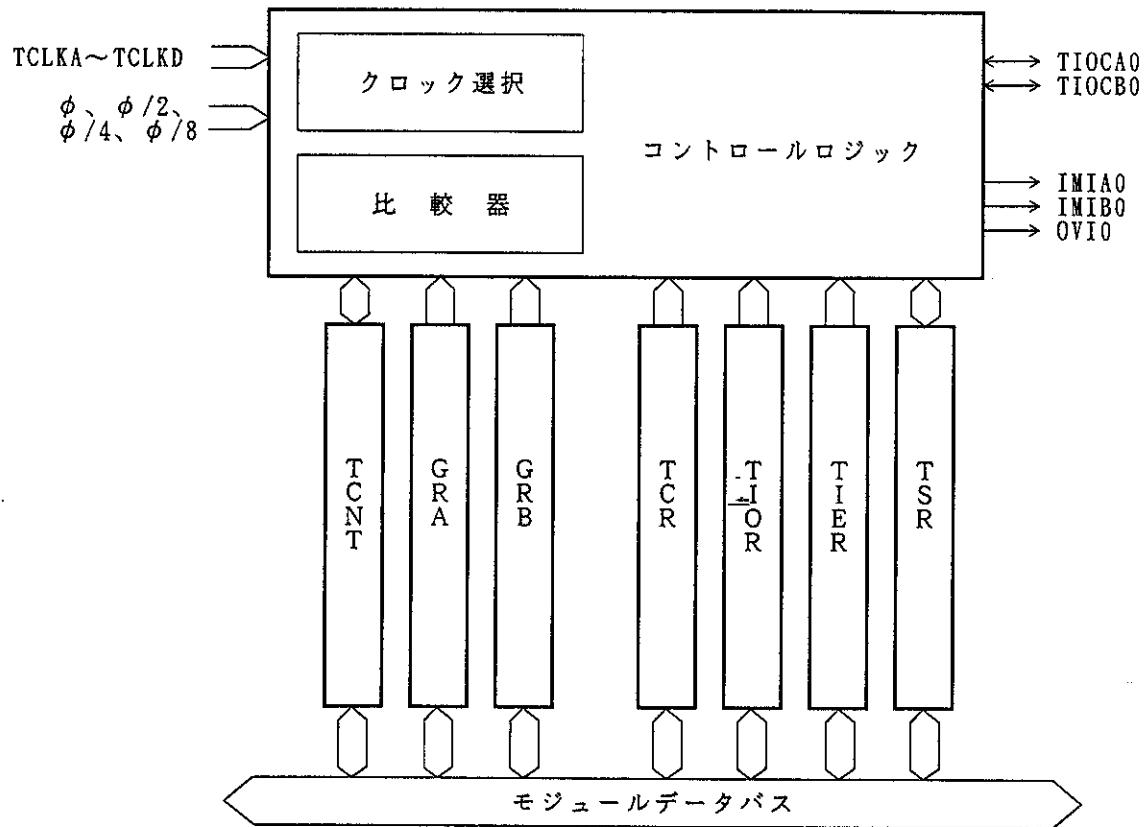

(2) チャネル0、1のブロック図

ITUのチャネル0、1は同一の機能をもっています。チャネル0、1のブロック図を図10.2に示します。

《記号説明》

- T C N T : タイマカウンタ (16ビット)

- G R A、B : ジェネラルレジスタ A、B (インプットキャプチャ／アウトプットコンペア兼用レジスタ) (16ビット×2)

- T C R : タイマコントロールレジスタ (8ビット)

- T I O R : タイマI/Oコントロールレジスタ (8ビット)

- T I E R : タイマインタラプトイネーブルレジスタ (8ビット)

- T S R : タイマステータスレジスタ (8ビット)

図10.2 チャネル0、1のブロック図 (チャネル0の場合)

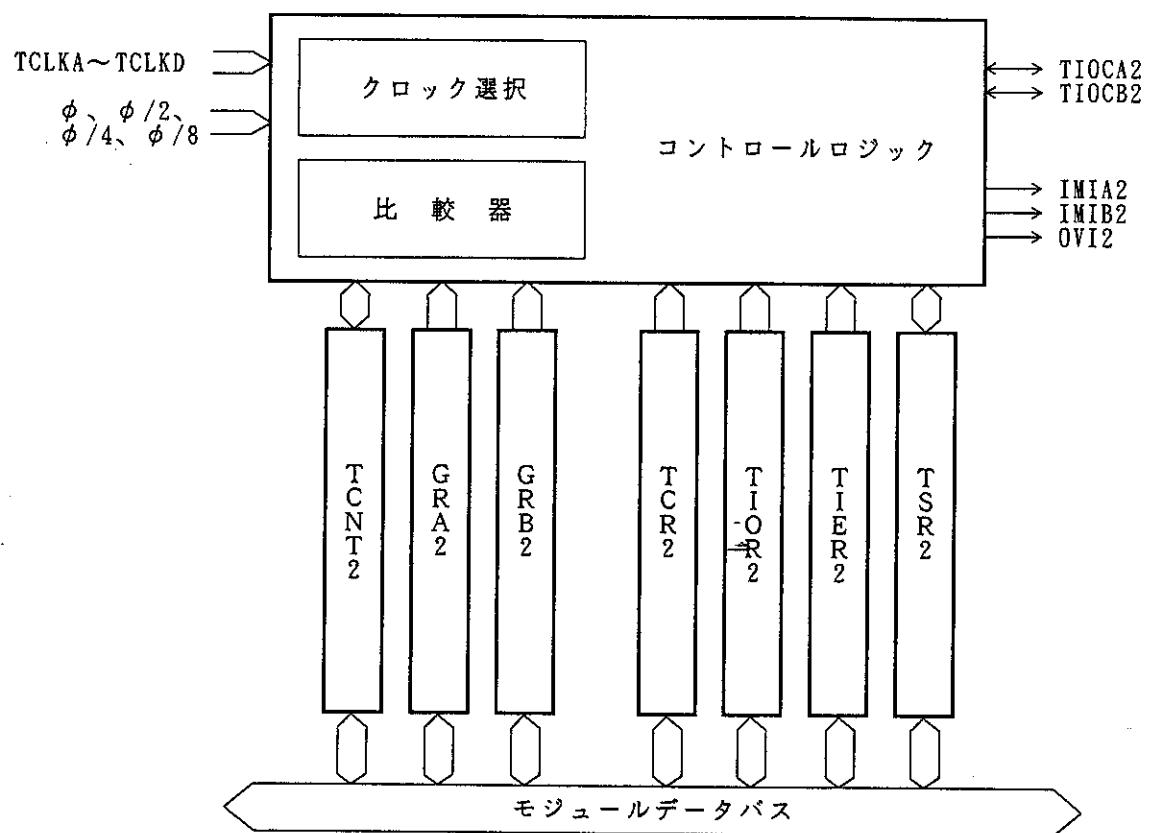

### (3) チャネル2のブロック図

チャネル2のブロック図を図10.3に示します。チャネル2は0出力、1出力のみ可能です。

#### 《記号説明》

- $TCNT_2$  : タイマカウンタ2 (16ビット)

- $GRA_2, B_2$  : ジェネラルレジスタA2, B2 (インプットキャプチャ／アウトプットコンペア兼用レジスタ) (16ビット×2)

- $TCR_2$  : タイマコントロールレジスタ2 (8ビット)

- $TIOR_2$  : タイマI/Oコントロールレジスタ2 (8ビット)

- $TIER_2$  : タイマインタラプトイネーブルレジスタ2 (8ビット)

- $TSR_2$  : タイマステータスレジスタ2 (8ビット)

図10.3 チャネル2のブロック図

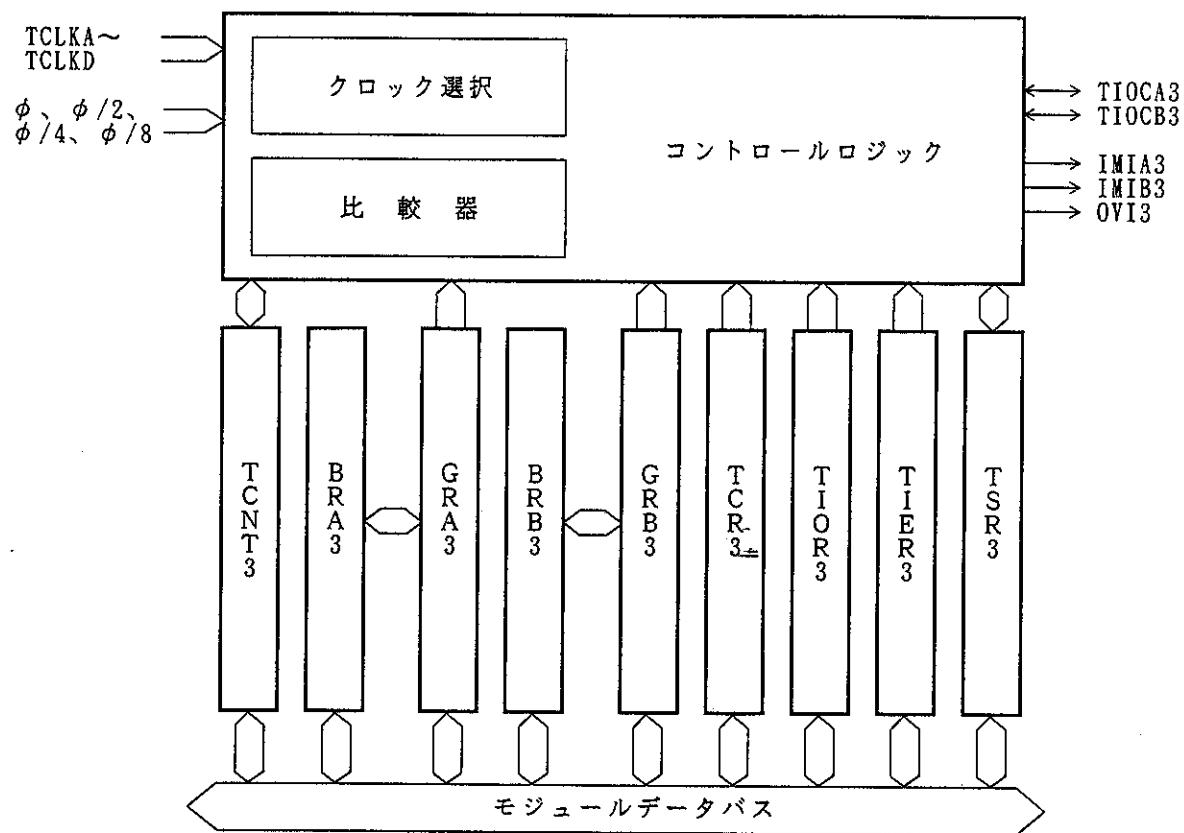

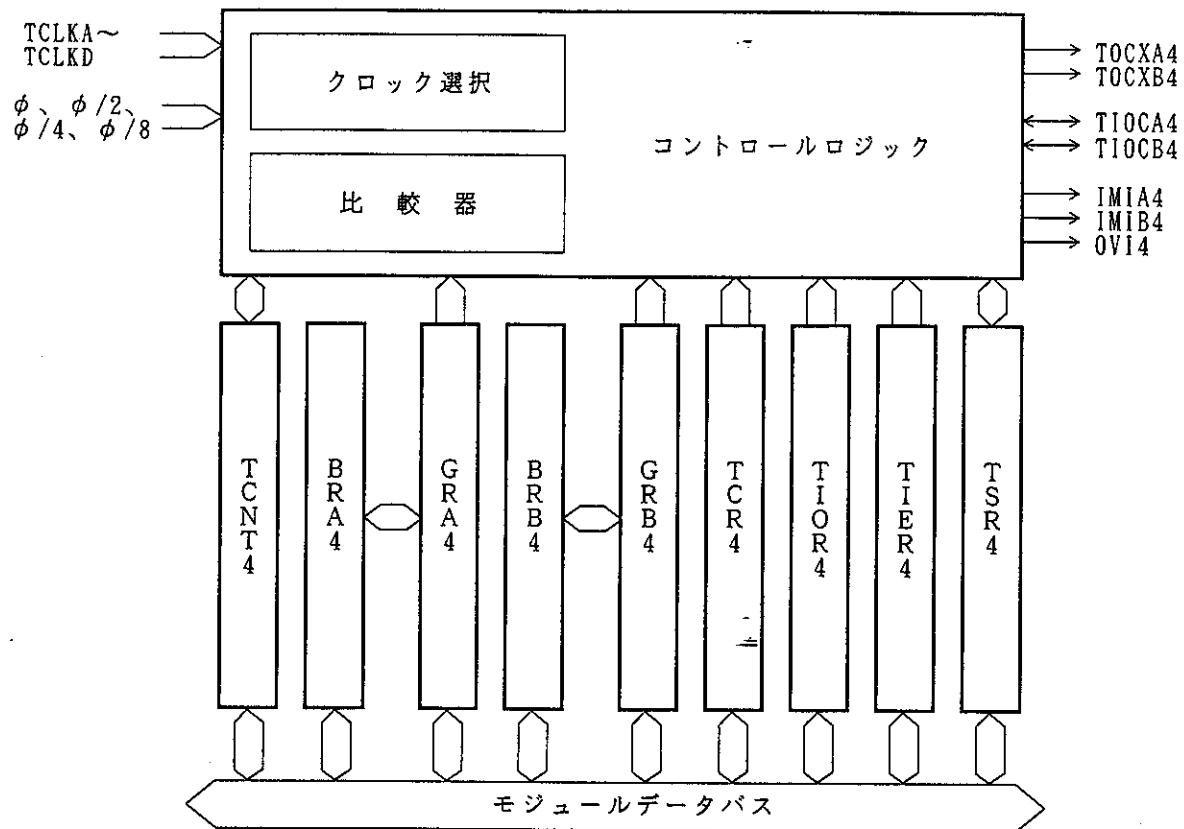

(4) チャネル3、4のブロック図

チャネル3のブロック図を図10.4、チャネル4のブロック図を図10.5に示します。

《記号説明》

- T C N T 3 : タイマカウンタ3 (16ビット)

- G R A 3、B 3 : ジェネラルレジスタA 3、B 3 (インプットキャプチャ／アウトプットコンペア兼用レジスタ) (16ビット×2)

- B R A 3、B 3 : バッファレジスタA 3、B 3 (インプットキャプチャ／アウトプットコンペア兼用バッファレジスタ) (16ビット×2)

- T C R 3 : タイマコントロールレジスタ3 (8ビット)

- T I O R 3 : タイマI/Oコントロールレジスタ3 (8ビット)

- T I E R 3 : タイマインタラプトイネーブルレジスタ3 (8ビット)

- T S R 3 : タイマステータスレジスタ3 (8ビット)

図10.4 チャネル3のブロック図

#### 《記号説明》

- T C N T 4 : タイマカウンタ4 (16ビット)

- G R A 4、B 4 : ジェネラルレジスタA 4、B 4 (インプットキャプチャ／アウトプットコンペア兼用レジスタ) (16ビット×2)

- B R A 4、B 4 : バッファレジスタA 4、B 4 (インプットキャプチャ／アウトプットコンペア兼用バッファレジスタ) (16ビット×2)

- T C R 4 : タイマコントロールレジスタ4 (8ビット)

- T I O R 4 : タイマI/Oコントロールレジスタ4 (8ビット)

- T I E R 4 : タイマインターブトイネーブルレジスタ4 (8ビット)

- T S R 4 : タイマステータスレジスタ4 (8ビット)

図10.5 チャネル4のブロック図

### 10.1.3 端子構成

I T Uの端子構成を表10.2に示します。

表10.2 端子構成(1)

| チャネル   | 名 称                          | 略 称    | 入出力 | 機 能                                                                                              |

|--------|------------------------------|--------|-----|--------------------------------------------------------------------------------------------------|

| 共<br>通 | クロック入力A                      | TCLKA  | 入 力 | 外部クロックA入力端子<br>(位相計数モード時A相入力端子)                                                                  |

|        | クロック入力B                      | TCLKB  | 入 力 | 外部クロックB入力端子<br>(位相計数モード時B相入力端子)                                                                  |

|        | クロック入力C                      | TCLKC  | 入 力 | 外部クロックC入力端子                                                                                      |

|        | クロック入力D                      | TCLKD  | 入 力 | 外部クロックD入力端子                                                                                      |

| 0      | インプットキャプチャ/<br>アウトプットコンペアA 0 | TIOCA0 | 入出力 | G R A 0 アウトプットコンペア出力/<br>G R A 0 インプットキャプチャ入力/<br>PWM出力端子(PWMモード時)                               |

|        | インプットキャプチャ/<br>アウトプットコンペアB 0 | TIOCB0 | 入出力 | G R B 0 アウトプットコンペア出力/<br>G R B 0 インプットキャプチャ入力端子                                                  |

| 1      | インプットキャプチャ/<br>アウトプットコンペアA 1 | TIOCA1 | 入出力 | G R A 1 アウトプットコンペア出力/<br>G R A 1 インプットキャプチャ入力/<br>PWM出力端子(PWMモード時)                               |

|        | インプットキャプチャ/<br>アウトプットコンペアB 1 | TIOCB1 | 入出力 | G R B 1 アウトプットコンペア出力/<br>G R B 1 インプットキャプチャ入力端子                                                  |

| 2      | インプットキャプチャ/<br>アウトプットコンペアA 2 | TIOCA2 | 入出力 | G R A 2 アウトプットコンペア出力/<br>G R A 2 インプットキャプチャ入力/<br>PWM出力端子(PWMモード時)                               |

|        | インプットキャプチャ/<br>アウトプットコンペアB 2 | TIOCB2 | 入出力 | G R B 2 アウトプットコンペア出力/<br>G R B 2 インプットキャプチャ入力端子                                                  |

| 3      | インプットキャプチャ/<br>アウトプットコンペアA 3 | TIOCA3 | 入出力 | G R A 3 アウトプットコンペア出力/<br>G R A 3 インプットキャプチャ入力/<br>PWM出力端子(PWMモード/<br>相補PWMモード/リセット同期PWM<br>モード時) |

|        | インプットキャプチャ/<br>アウトプットコンペアB 3 | TIOCB3 | 入出力 | G R B 3 アウトプットコンペア出力/<br>G R B 3 インプットキャプチャ入力/<br>PWM出力端子(相補PWMモード/<br>リセット同期PWMモード時)            |

表10.2 端子構成(2)

| チャネル | 名 称                           | 略 称    | 入出力 | 機 能                                                                                                              |

|------|-------------------------------|--------|-----|------------------------------------------------------------------------------------------------------------------|

| 4    | インプットキャプチャ/<br>アウトプットコンペア A 4 | TIOCA4 | 入出力 | G R A 4 アウトプットコンペア出力/<br>G R A 4 インプットキャプチャ入力/<br>P W M 出力端子 (P W M モード/<br>相補 P W M モード / リセット同期 P W M<br>モード時) |

|      | インプットキャプチャ/<br>アウトプットコンペア B 4 | TIOCB4 | 入出力 | G R B 4 アウトプットコンペア出力/<br>G R B 4 インプットキャプチャ入力/<br>P W M 出力端子 (相補 P W M モード/<br>リセット同期 P W M モード時)                |

|      | アウトプットコンペア<br>X A 4           | TOCXA4 | 出 力 | P W M 出力端子 (相補 P W M モード/<br>リセット同期 P W M モード時)                                                                  |

|      | アウトプットコンペア<br>X B 4           | TOCXB4 | 出 力 | P W M 出力端子 (相補 P W M モード/<br>リセット同期 P W M モード時)                                                                  |

#### 10.1.4 レジスタ構成

I T U のレジスタ構成を表10.3に示します。

表10.3 レジスタ構成(1)

| チャネル   | アドレス <sup>*1</sup> | 名 称                    | 略 称         | R / W                 | 初期値  |

|--------|--------------------|------------------------|-------------|-----------------------|------|

| 共<br>通 | H'FF60             | タイマスタートレジスタ            | T S T R     | R / W                 | H'E0 |

|        | H'FF61             | タイマシンクロレジスタ            | T S N C     | R / W                 | H'E0 |

|        | H'FF62             | タイマモードレジスタ             | T M D R     | R / W                 | H'80 |

|        | H'FF63             | タイマファンクションコントロールレジスタ   | T F C R     | R / W                 | H'C0 |

|        | H'FF90             | タイマアウトプットマスティネーブルレジスタ  | T O E R     | R / W                 | H'FF |

|        | H'FF91             | タイマアウトプットコントロールレジスタ    | T O C R     | R / W                 | H'FF |

| 0      | H'FF64             | タイマコントロールレジスタ 0        | T C R 0     | R / W                 | H'80 |

|        | H'FF65             | タイマ I / O コントロールレジスタ 0 | T I O R 0   | R / W                 | H'88 |

|        | H'FF66             | タイマインタラブトイネーブルレジスタ 0   | T I E R 0   | R / W                 | H'F8 |

|        | H'FF67             | タイマステータスレジスタ 0         | T S R 0     | R / (W) <sup>*2</sup> | H'F8 |

|        | H'FF68             | タイマカウンタ 0 H            | T C N T 0 H | R / W                 | H'00 |

|        | H'FF69             | タイマカウンタ 0 L            | T C N T 0 L | R / W                 | H'00 |

|        | H'FF6A             | ジェネラルレジスタ A 0 H        | G R A 0 H   | R / W                 | H'FF |

|        | H'FF6B             | ジェネラルレジスタ A 0 L        | G R A 0 L   | R / W                 | H'FF |

|        | H'FF6C             | ジェネラルレジスタ B 0 H        | G R B 0 H   | R / W                 | H'FF |

|        | H'FF6D             | ジェネラルレジスタ B 0 L        | G R B 0 L   | R / W                 | H'FF |

| 1      | H'FF6E             | タイマコントロールレジスタ 1        | T C R 1     | R / W                 | H'80 |

|        | H'FF6F             | タイマ I / O コントロールレジスタ 1 | T I O R 1   | R / W                 | H'88 |

|        | H'FF70             | タイマインタラブトイネーブルレジスタ 1   | T I E R 1   | R / W                 | H'F8 |

|        | H'FF71             | タイマステータスレジスタ 1         | T S R 1     | R / (W) <sup>*2</sup> | H'F8 |

|        | H'FF72             | タイマカウンタ 1 H            | T C N T 1 H | R / W                 | H'00 |

|        | H'FF73             | タイマカウンタ 1 L            | T C N T 1 L | R / W                 | H'00 |

|        | H'FF74             | ジェネラルレジスタ A 1 H        | G R A 1 H   | R / W                 | H'FF |

|        | H'FF75             | ジェネラルレジスタ A 1 L        | G R A 1 L   | R / W                 | H'FF |

|        | H'FF76             | ジェネラルレジスタ B 1 H        | G R B 1 H   | R / W                 | H'FF |

|        | H'FF77             | ジェネラルレジスタ B 1 L        | G R B 1 L   | R / W                 | H'FF |

| 2      | H'FF78             | タイマコントロールレジスタ 2        | T C R 2     | R / W                 | H'80 |

|        | H'FF79             | タイマ I / O コントロールレジスタ 2 | T I O R 2   | R / W                 | H'88 |

|        | H'FF7A             | タイマインタラブトイネーブルレジスタ 2   | T I E R 2   | R / W                 | H'F8 |

|        | H'FF7B             | タイマステータスレジスタ 2         | T S R 2     | R / (W) <sup>*2</sup> | H'F8 |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。

<sup>\*2</sup> フラグをクリアするための“0”ライトのみ可能です。

表10.3 レジスタ構成(2)

| チャネル | アドレス <sup>*1</sup> | 名 称                | 略 称    | R/W                 | 初期値  |

|------|--------------------|--------------------|--------|---------------------|------|

| 2    | H'FF7C             | タイマカウンタ2H          | TCNT2H | R/W                 | H'00 |

|      | H'FF7D             | タイマカウンタ2L          | TCNT2L | R/W                 | H'00 |

|      | H'FF7E             | ジェネラルレジスタA2H       | GRA2H  | R/W                 | H'FF |

|      | H'FF7F             | ジェネラルレジスタA2L       | GRA2L  | R/W                 | H'FF |

|      | H'FF80             | ジェネラルレジスタB2H       | GRB2H  | R/W                 | H'FF |

|      | H'FF81             | ジェネラルレジスタB2L       | GRB2L  | R/W                 | H'FF |

| 3    | H'FF82             | タイマコントロールレジスタ3     | TCR3   | R/W                 | H'80 |

|      | H'FF83             | タイマI/Oコントロールレジスタ3  | TIOR3  | R/W                 | H'88 |

|      | H'FF84             | タイマイソラブトイネ-ブルレジスタ3 | TIER3  | R/W                 | H'F8 |

|      | H'FF85             | タイマステータスレジスタ3      | TSR3   | R/(W) <sup>*2</sup> | H'F8 |

|      | H'FF86             | タイマカウンタ3H          | TCNT3H | R/W                 | H'00 |

|      | H'FF87             | タイマカウンタ3L          | TCNT3L | R/W                 | H'00 |

|      | H'FF88             | ジェネラルレジスタA3H       | GRA3H  | R/W                 | H'FF |

|      | H'FF89             | ジェネラルレジスタA3L       | GRA3L  | R/W                 | H'FF |

|      | H'FF8A             | ジェネラルレジスタB3H       | GRB3H  | R/W                 | H'FF |

|      | H'FF8B             | ジェネラルレジスタB3L       | GRB3L  | R/W                 | H'FF |

|      | H'FF8C             | バッファレジスタA3H        | BRA3H  | R/W                 | H'FF |

|      | H'FF8D             | バッファレジスタA3L        | BRA3L  | R/W                 | H'FF |

|      | H'FF8E             | バッファレジスタB3H        | BRB3H  | R/W                 | H'FF |

|      | H'FF8F             | バッファレジスタB3L        | BRB3L  | R/W                 | H'FF |

| 4    | H'FF92             | タイマコントロールレジスタ4     | TCR4   | R/W                 | H'80 |

|      | H'FF93             | タイマI/Oコントロールレジスタ4  | TIOR4  | R/W                 | H'88 |

|      | H'FF94             | タイマイソラブトイネ-ブルレジスタ4 | TIER4  | R/W                 | H'F8 |

|      | H'FF95             | タイマステータスレジスタ4      | TSR4   | R/(W) <sup>*2</sup> | H'F8 |

|      | H'FF96             | タイマカウンタ4H          | TCNT4H | R/W                 | H'00 |

|      | H'FF97             | タイマカウンタ4L          | TCNT4L | R/W                 | H'00 |

|      | H'FF98             | ジェネラルレジスタA4H       | GRA4H  | R/W                 | H'FF |

|      | H'FF99             | ジェネラルレジスタA4L       | GRA4L  | R/W                 | H'FF |

|      | H'FF9A             | ジェネラルレジスタB4H       | GRB4H  | R/W                 | H'FF |

|      | H'FF9B             | ジェネラルレジスタB4L       | GRB4L  | R/W                 | H'FF |

|      | H'FF9C             | バッファレジスタA4H        | BRA4H  | R/W                 | H'FF |

|      | H'FF9D             | バッファレジスタA4L        | BRA4L  | R/W                 | H'FF |

|      | H'FF9E             | バッファレジスタB4H        | BRB4H  | R/W                 | H'FF |

|      | H'FF9F             | バッファレジスタB4L        | BRB4L  | R/W                 | H'FF |

【注】<sup>\*1</sup> アドレスの下位16ビットを示しています。<sup>\*2</sup> フラグをクリアするための“0”ライトのみ可能です。

## 10.2 各レジスタの説明

#### 10.2.1 タイマスタートレジスタ (T S T R)

T S T R は 8 ビットのリード／ライト可能なレジスタで、チャネル 0～4 の T C N T の動作／停止を選択します。

| ビット: | 7 | 6 | 5 | 4    | 3    | 2    | 1    | 0    |

|------|---|---|---|------|------|------|------|------|

|      | — | — | — | STR4 | STR3 | STR2 | STR1 | STR0 |

| 初期値: | 1 | 1 | 1 | 0    | 0    | 0    | 0    | 0    |

| R/W: | — | — | — | R/W  | R/W  | R/W  | R/W  | R/W  |

リザーブビット                            カウンタスタート 4 ~ 0

T C N T 4 ~ T C N T 0 の動作／停止を選択するビットです。

T S T Rはリセット、またはスタンバイモード時に、H'EOにイニシャライズされます。

ビット7～5：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット4：カウンタスタート4（STB4）

タイマカウンタ4（T C N T 4）の動作／停止を選擇します。

| ビット4    |                      | 説明    |

|---------|----------------------|-------|

| S T R 4 |                      |       |

| 0       | T C N T 4 のカウント動作は停止 | (初期値) |

| 1       | T C N T 4 はカウント動作    |       |

ビット3：カウンタスタート3（STR3）

タイマカウンタ3（T C N T 3）の動作／停止を選択します。

| ビット3    | 説明                   |       |

|---------|----------------------|-------|

| S T R 3 |                      |       |

| 0       | T C N T 3 のカウント動作は停止 | (初期値) |

| 1       | T C N T 3 はカウント動作    |       |

**ビット2：カウンタスタート2（S T R 2）**

タイマカウンタ2（T C N T 2）の動作／停止を選択します。

| ビット2    | 説                    | 明     |

|---------|----------------------|-------|

| S T R 2 |                      |       |

| 0       | T C N T 2 のカウント動作は停止 | (初期値) |

| 1       | T C N T 2 はカウント動作    |       |

**ビット1：カウンタスタート1（S T R 1）**

タイマカウンタ1（T C N T 1）の動作／停止を選択します。

| ビット1    | 説                    | 明     |

|---------|----------------------|-------|

| S T R 1 |                      |       |

| 0       | T C N T 1 のカウント動作は停止 | (初期値) |

| 1       | T C N T 1 はカウント動作    |       |

**ビット0：カウンタスタート0（S T R 0）**

タイマカウンタ0（T C N T 0）の動作／停止を選択します。

| ビット0    | 説                    | 明     |

|---------|----------------------|-------|

| S T R 0 |                      |       |

| 0       | T C N T 0 のカウント動作は停止 | (初期値) |

| 1       | T C N T 0 はカウント動作    |       |

### 10.2.2 タイマシンクロレジスタ (T S N C)

T SNC は 8 ビットのリード／ライト可能なレジスタで、チャネル 0 ~ 4 の独立動作／同期動作を選択します。対応するビットを “1” にセットしたチャネルが同期動作を行います。

| ビット: | 7 | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

|------|---|---|---|-------|-------|-------|-------|-------|

| 初期値: | — | — | — | SYNC4 | SYNC3 | SYNC2 | SYNC1 | SYNC0 |

| R/W: | 1 | 1 | 1 | 0     | 0     | 0     | 0     | 0     |

|      | — | — | — | R/W   | R/W   | R/W   | R/W   | R/W   |

リザーブビット

タイマ同期 4 ~ 0

チャネル 4 ~ 0 の同期動作を

設定するビットです。

T S N C はリセット、またはスタンバイモード時に、H'-E0にイニシャライズされます。

ビット7～5：リザーブビット

リザーブピットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット4：タイマ同期4（SYN C4）

チャンネル4の独立動作／同期動作を選択します。

| ビット4      | 説明                                                                    |

|-----------|-----------------------------------------------------------------------|

| S Y N C 4 |                                                                       |

| 0         | チャネル4のタイマカウンタ（T C N T 4）は独立動作（T C N T 4のプリセット／クリアは他チャネルと無関係）<br>（初期値） |

| I         | チャネル4は同期動作<br>T C N T 4の同期プリセット／同期クリアが可能                              |

### ビット3：タイマ同期3 (SYNC3)

チャネル3の独立動作／同期動作を選択します。

| ビット3  | 説明                                                               |

|-------|------------------------------------------------------------------|

| SYNC3 |                                                                  |

| 0     | チャネル3のタイマカウンタ (TCNT3) は独立動作 (TCNT3のプリセット／クリアは他チャネルと無関係)<br>(初期値) |

| 1     | チャネル3は同期動作<br>TCNT3の同期プリセット／同期クリアが可能                             |

### ビット2：タイマ同期2 (SYNC2)

チャネル2の独立動作／同期動作を選択します。

| ビット2  | 説明                                                               |

|-------|------------------------------------------------------------------|

| SYNC2 |                                                                  |

| 0     | チャネル2のタイマカウンタ (TCNT2) は独立動作 (TCNT2のプリセット／クリアは他チャネルと無関係)<br>(初期値) |

| 1     | チャネル2は同期動作<br>TCNT2の同期プリセット／同期クリアが可能                             |

### ビット1：タイマ同期1 (SYNC1)

チャネル1の独立動作／同期動作を選択します。

| ビット1  | 説明                                                               |

|-------|------------------------------------------------------------------|

| SYNC1 |                                                                  |

| 0     | チャネル1のタイマカウンタ (TCNT1) は独立動作 (TCNT1のプリセット／クリアは他チャネルと無関係)<br>(初期値) |

| 1     | チャネル1は同期動作<br>TCNT1の同期プリセット／同期クリアが可能                             |

### ビット0：タイマ同期0 (SYNC0)

チャネル0の独立動作／同期動作を選択します。

| ビット0  | 説明                                                               |

|-------|------------------------------------------------------------------|

| SYNC0 |                                                                  |

| 0     | チャネル0のタイマカウンタ (TCNT0) は独立動作 (TCNT0のプリセット／クリアは他チャネルと無関係)<br>(初期値) |

| 1     | チャネル0は同期動作<br>TCNT0の同期プリセット／同期クリアが可能                             |

### 10.2.3 タイマモードレジスタ (TMDR)

TMDRは8ビットのリード／ライト可能なレジスタで、チャネル0～4のPWMモードの設定、チャネル2の位相計数モードの設定およびオーバフローフラグ(OVF)のセット条件の設定を行います。

| ビット: | 7 | 6   | 5    | 4    | 3    | 2    | 1    | 0                           |

|------|---|-----|------|------|------|------|------|-----------------------------|

|      | — | MDF | FDIR | PWM4 | PWM3 | PWM2 | PWM1 | PWM0                        |

| 初期値: | 1 | 0   | 0    | 0    | 0    | 0    | 0    | 0                           |

| R/W: | — | R/W | R/W  | R/W  | R/W  | R/W  | R/W  | R/W                         |

|      |   |     |      |      |      |      |      | <u>PWMモード4～0</u>            |

|      |   |     |      |      |      |      |      | チャネル4～0をPWMモードに設定するビットです。   |

|      |   |     |      |      |      |      |      | <u>フラグディレクション</u>           |

|      |   |     |      |      |      |      |      | TSR2のOVFフラグセット条件を設定するビットです。 |

|      |   |     |      |      |      |      |      | <u>位相計数モード</u>              |

|      |   |     |      |      |      |      |      | チャネル2を位相計数モードに設定するビットです。    |

|      |   |     |      |      |      |      |      | <u>リザーブビット</u>              |

TMDRはリセット、またはスタンバイモード時に、H'80にイニシャライズされます。

#### ビット7: リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット6: 位相計数モード(MDF)

チャネル2を通常動作させるか、位相計数モードで動作させるかを選択します。

| ビット6 | 説明            |

|------|---------------|

| MDF  |               |

| 0    | チャネル2は通常動作    |

| 1    | チャネル2は位相計数モード |

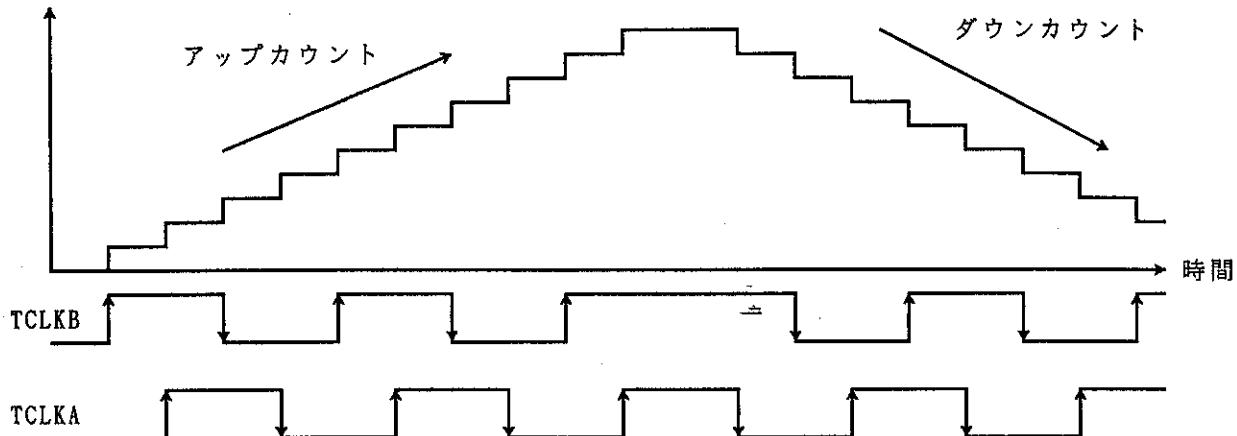

MDFビットを“1”にセットして位相計数モードにすると、TCNT2はアップ／ダウンカウント、TCLKA、TCLKB端子がカウントクロック入力端子となります。TCNT2はTCLKA、TCLKB端子の立上がり(↑)／立下がり(↓)の両エッジでカウントされ、カウントアップ／ダウン方向は次のようになります。

| カウント方向  | カウントダウン |        |        |       | カウントアップ |       |       |        |

|---------|---------|--------|--------|-------|---------|-------|-------|--------|

| TCLKA端子 | ↑       | “High” | ↓      | “Low” | ↑       | “Low” | ↓     | “High” |

| TCLKB端子 | “Low”   | ↑      | “High” | ↓     | “High”  | ↑     | “Low” | ↓      |

位相計数モードでは、TCR2のCKEG1、CKEG0ビットによる外部クロックエッジの選択、およびTPSC2～TPSC0ビットによるカウンタクロックの選択は無効となり、上記の位相計数モードの動作が優先されます。

ただし、TCR2のCCLR1、CCLR0ビットによるカウンタクリア条件の設定、TIOR2、TIER2、TSR2のコンペアマッチ／インプットキャプチャ機能と割込みの設定は位相計数モードでも有効です。

#### ビット5：フラグディレクション(FDIR)

TSR2のOVFフラグのセット条件を設定します。本ビットの設定は、チャネル2がいずれのモードで動作していても有効となります。

| ビット5<br>FDIR | 説                                              | 明     |

|--------------|------------------------------------------------|-------|

| 0            | TSR2のOVFフラグは、TCNT2がオーバフローまたはアンダフローしたときに“1”にセット | (初期値) |

| 1            | TSR2のOVFフラグは、TCNT2がオーバフローしたときに“1”にセット          |       |

#### ビット4：PWMモード4(PWM4)

チャネル4を通常動作させるか、PWMモードで動作させるかを選択します。

| ビット4<br>PWM4 | 説            | 明     |

|--------------|--------------|-------|

| 0            | チャネル4は通常動作   | (初期値) |

| 1            | チャネル4はPWMモード |       |

PWM4を“1”にセットしてPWMモードにすると、TIOCA4端子はPWM出力端子となり、GRA4のコンペアマッチで1出力、GRB4のコンペアマッチで0出力となります。

TFCRのCMD1、CMD0ビットにより相補PWMモードまたはリセット同期PWMモードが設定されているとき、本ビットの設定は無効となり、CMD1、CMD0ビットの設定が優先されます。

### ビット3：PWMモード3（PWM3）

チャネル3を通常動作させるか、PWMモードで動作させるかを選択します。

| ビット3 | 説明           |

|------|--------------|

| PWM3 |              |

| 0    | チャネル3は通常動作   |

| 1    | チャネル3はPWMモード |

PWM3を“1”にセットしてPWMモードにすると、TIOCA3端子はPWM出力端子となり、GRA3のコンペアマッチで1出力、GRB3のコンペアマッチで0出力となります。

TFCRのCMD1、CMD0ビットにより相補PWMモードまたはリセット同期PWMモードが設定されているとき、本ビットの設定は無効となり、CMD1、CMD0ビットの設定が優先されます。

### ビット2：PWMモード2（PWM2）

チャネル2を通常動作させるか、PWMモードで動作させるかを選択します。

| ビット2 | 説明           |

|------|--------------|

| PWM2 |              |

| 0    | チャネル2は通常動作   |

| 1    | チャネル2はPWMモード |

PWM2を“1”にセットしてPWMモードにすると、TIOCA2端子はPWM出力端子となり、GRA2のコンペアマッチで1出力、GRB2のコンペアマッチで0出力となります。

### ビット1：PWMモード1（PWM1）

チャネル1を通常動作させるか、PWMモードで動作させるかを選択します。

| ビット1 | 説明           |

|------|--------------|

| PWM1 |              |

| 0    | チャネル1は通常動作   |

| 1    | チャネル1はPWMモード |

PWM1を“1”にセットしてPWMモードに設定すると、TIOCA1端子はPWM出力端子となり、GRA1のコンペアマッチ1で出力、GRB1のコンペアマッチで0出力となります。

### ビット0：PWMモード0（PWM0）

チャネル0を通常動作させるか、PWMモードで動作させるかを選択します。

| ビット0 | 説明           |

|------|--------------|

| PWM0 |              |

| 0    | チャネル0は通常動作   |

| 1    | チャネル0はPWMモード |

PWM0を“1”にセットしてPWMモードに設定すると、TIOCA0端子はPWM出力端子となり、GRA0のコンペアマッチで1出力、GRB0のコンペアマッチで0出力となります。

#### 10.2.4 タイマファンクションコントロールレジスタ (TFCR)

TFCRは8ビットのリード／ライト可能なレジスタで、チャネル3、4の相補PWMモード／リセット同期PWMモードの設定、およびバッファ動作の設定を行います。

TFCRはリセット、またはスタンバイモード時に、H'COにイニシャライズされます。

#### ビット7, 6: リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット5、4：コンビネーションモード1、0（CMD1、CMD0）

チャネル3、4を通常動作させるか、相補PWMモードまたはリセット同期PWMモードで動作させるかを選択します。

| ビット5 | ビット4 | 説                             | 明     |

|------|------|-------------------------------|-------|

| CMD1 | CMD0 |                               |       |

| 0    | 0    | チャネル3、4は通常動作                  | (初期値) |

|      | 1    |                               |       |

| 1    | 0    | チャネル3、4を組み合わせ、相補PWMモードで動作     |       |

|      | 1    | チャネル3、4を組み合わせ、リセット同期PWMモードで動作 |       |

相補PWMモード、およびリセット同期PWMモードの設定は、使用するTCNTを停止させた状態で行ってください。

本ビットにより、相補PWMモードまたはリセット同期PWMモードに設定した場合、TMDRのPWM4、PWM3ビットによるPWMモードの設定より優先されます。なお、相補PWMモード、リセット同期PWMモードの設定とTSNCのSYNC4、SYNC3ビットによる同期動作の設定は同時に有効となりますが、相補PWMモードを設定したときは、チャネル3とチャネル4を同期動作に設定（TSNCのSYNC4ビットとSYNC3ビットをともに“1”にセット）しないでください。

#### ビット3：バッファ動作B4（BFB4）

チャネル4のGRB4を通常動作とするか、GRB4とBRB4を組み合わせてバッファ動作とするかを設定します。

| ビット3 | 説                | 明     |

|------|------------------|-------|

| BFB4 |                  |       |

| 0    | GRB4は通常動作        | (初期値) |

| 1    | GRB4とBRB4はバッファ動作 |       |

#### ビット2：バッファ動作A4（BFA4）

チャネル4のGRA4を通常動作とするか、GRA4とBRA4を組み合わせてバッファ動作とするかを設定します。

| ビット2 | 説                | 明     |

|------|------------------|-------|

| BFA4 |                  |       |

| 0    | GRA4は通常動作        | (初期値) |

| 1    | GRA4とBRA4はバッファ動作 |       |

**ビット1：バッファ動作B3 (BFB3)**

チャネル3のGRB3を通常動作とするか、GRB3とBRB3を組み合わせてバッファ動作とするかを設定します。

| ビット1 | 説                | 明     |

|------|------------------|-------|

| BFB3 |                  |       |

| 0    | GRB3は通常動作        | (初期値) |

| 1    | GRB3とBRB3はバッファ動作 |       |

**ビット0：バッファ動作A3 (BFA3)**

チャネル3のGRA3を通常動作とするか、GRA3とBRA3を組み合わせてバッファ動作とするかを設定します。

| ビット0 | 説                | 明     |

|------|------------------|-------|

| BFA3 |                  |       |

| 0    | GRA3は通常動作        | (初期値) |

| 1    | GRA3とBRA3はバッファ動作 |       |

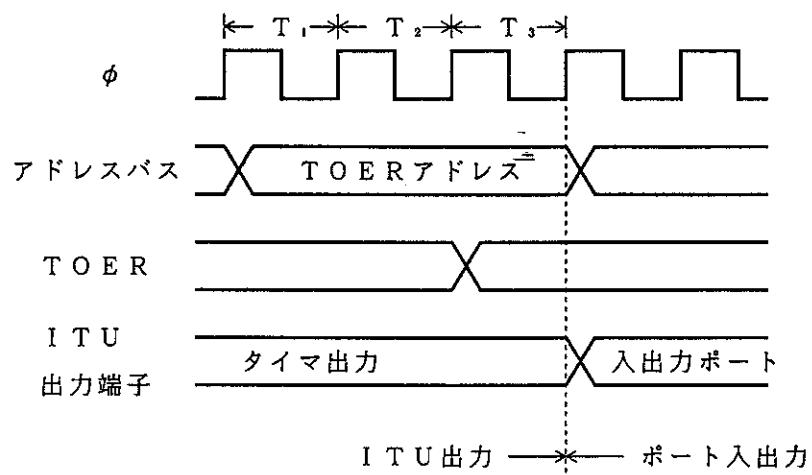

### 10.2.5 タイマアウトプットマスティネーブルレジスタ (T O E R)

T O E R は、8ビットのリード／ライト可能なレジスタで、チャネル3、4の出力設定を許可／禁止します。

| ビット:                                                                                                                                                                                                  | 7 | 6 | 5    | 4    | 3   | 2   | 1   | 0   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------|------|-----|-----|-----|-----|

| 初期値:                                                                                                                                                                                                  | — | — | EXB4 | EXA4 | EB3 | EB4 | EA4 | EA3 |

| R/W:                                                                                                                                                                                                  | — | — | R/W  | R/W  | R/W | R/W | R/W | R/W |

| マスティネーブル TIOCA <sub>3</sub> 、TIOCB <sub>3</sub> 、TIOCA <sub>4</sub> 、TIOCB <sub>4</sub> 、<br>TIOCA <sub>5</sub> 、TIOCB <sub>5</sub> 、TIOCA <sub>6</sub> 、TIOCB <sub>6</sub> 端子の出力設定を<br>許可／禁止するビットです。 |   |   |      |      |     |     |     |     |

| マスティネーブル TOCXA <sub>4</sub> 、TOCXB <sub>4</sub> 、<br>TOCXA <sub>5</sub> 、TOCXB <sub>5</sub> 端子の出力設定を許可／禁止するビットです。                                                                                     |   |   |      |      |     |     |     |     |

| <u>リザーブビット</u>                                                                                                                                                                                        |   |   |      |      |     |     |     |     |

T O E R はリセット、またはスタンバイモード時にH'FFにイニシャライズされます。

#### ビット7、6：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット5：マスティネーブル T O C X B 4 (E X B 4)

TOCXB<sub>4</sub>端子のITU出力を許可／禁止します。

| ビット5    | 説明                                                                                                                                   |

|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| E X B 4 |                                                                                                                                      |

| 0       | T F C R の設定にかかわらずTOCXB <sub>4</sub> 端子の出力は禁止 (TOCXB <sub>4</sub> 端子は入出力ポートとして動作)<br>XTGD=“0”的状態で、チャネル1のインプットキャプチャAが発生したとき<br>“0”にクリア |

| 1       | T F C R の設定に従いTOCXB <sub>4</sub> 端子の出力は許可<br>(初期値)                                                                                   |

ビット4：マスタイネーブルTOCXA4(ExA4)

TOCXA<sub>4</sub>端子のITU出力を許可／禁止します。

| ビット4<br>ExA4 | 説明                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

| 0            | TFCRの設定にかかわらずTOCXA <sub>4</sub> 端子の出力は禁止(TOCXA <sub>4</sub> 端子は入出力ポートとして動作)<br>XTGD=“0”の状態で、チャネル1のインプットキャプチャAが発生したとき“0”にクリア |

| 1            | TFCRの設定に従いTOCXA <sub>4</sub> 端子の出力は許可<br>(初期値)                                                                              |

ビット3：マスタイネーブルTIOCB3(EB3)

TIOCB<sub>3</sub>端子のITU出力を許可／禁止します。

| ビット3<br>EB3 | 説明                                                                                                                               |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| 0           | TIOR3、TFCRの設定にかかわらずTIOCB <sub>3</sub> 端子の出力は禁止(TIOCB <sub>3</sub> 端子は出力ポートとして動作)<br>XTGD=“0”の状態で、チャネル1のインプットキャプチャAが発生したとき“0”にクリア |

| 1           | TIOR3、TFCRの設定に従いTIOCB <sub>3</sub> 端子の出力は許可<br>(初期値)                                                                             |

ビット2：マスタイネーブルTIOCB4(EB4)

TIOCB<sub>4</sub>端子のITU出力を許可／禁止します。

| ビット2<br>EB4 | 説明                                                                                                                                |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0           | TIOR4、TFCRの設定にかかわらずTIOCB <sub>4</sub> 端子の出力は禁止(TIOCB <sub>4</sub> 端子は入出力ポートとして動作)<br>XTGD=“0”の状態で、チャネル1のインプットキャプチャAが発生したとき“0”にクリア |

| 1           | TIOR4、TFCRの設定に従いTIOCB <sub>4</sub> 端子の出力は許可<br>(初期値)                                                                              |

ビット1：マスタイネーブルTIOCA4 (EA4)

TIOCA<sub>4</sub>端子のITU出力を許可／禁止します。

| ビット1<br>EA4 | 説明                                                                                                                                             |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | TIOR4、TMDR、TFCRの設定にかかわらずTIOCA <sub>4</sub> 端子の出力は禁止<br>(TIOCA <sub>4</sub> 端子は入出力ポートとして動作)<br>XTGD=“0”の状態で、チャネル1のインプットキャプチャAが発生したとき<br>“0”にクリア |

| 1           | TIOR4、TMDR、TFCRの設定に従いTIOCA <sub>4</sub> 端子の出力は許可<br>(初期値)                                                                                      |

ビット0：マスタイネーブルTIOCA3 (EA3)

TIOCA<sub>3</sub>端子のITU出力を許可／禁止します。

| ビット0<br>EA3 | 説明                                                                                                                                             |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | TIOR3、TMDR、TFCRの設定にかかわらずTIOCA <sub>3</sub> 端子の出力は禁止<br>(TIOCA <sub>3</sub> 端子は入出力ポートとして動作)<br>XTGD=“0”の状態で、チャネル1のインプットキャプチャAが発生したとき<br>“0”にクリア |

| 1           | TIOR3、TMDR、TFCRの設定に従いTIOCA <sub>3</sub> 端子の出力は許可<br>(初期値)                                                                                      |

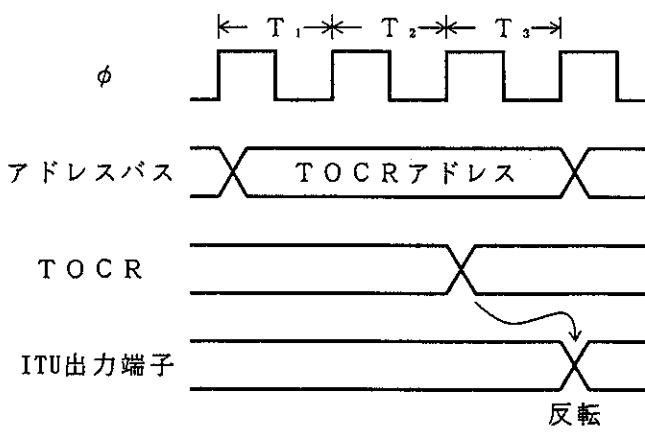

### 10.2.6 タイマアウトプットコントロールレジスタ (TOCR)

TOCRは、8ビットのリード／ライト可能なレジスタで、相補PWMモード／リセット同期PWMモード出力の外部トリガによる禁止または出力レベル反転を行います。

ビット : 7 6 5 4 3 2 1 0

|   |   |   |         |   |   |         |         |

|---|---|---|---------|---|---|---------|---------|

| — | — | — | X T G D | — | — | O L S 4 | O L S 3 |

|---|---|---|---------|---|---|---------|---------|

初期値 : 1 1 1 1 1 1 1 1

R / W : — — — R / W — — R / W R / W

リザーブビット

出力レベルセレクト3、4

相補PWMモード／リセット同期

PWMモードの出力レベルを選択

するビットです。

リザーブセット

外部トリガディスエーブル

相補PWMモード／リセット同期PWMモード出力の

外部からのトリガによる出力禁止を設定するビットです。

X T G D、O L S 4 および O L S 3 ビットの設定は、リセット同期PWMモードまたは相補PWMモードを設定しているときのみ有効となります。他の出力状態では、これらのビットの設定は無効です。

TOCRはリセット、またはスタンバイモード時にH'FFにイニシャライズされます。

ビット7～5：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

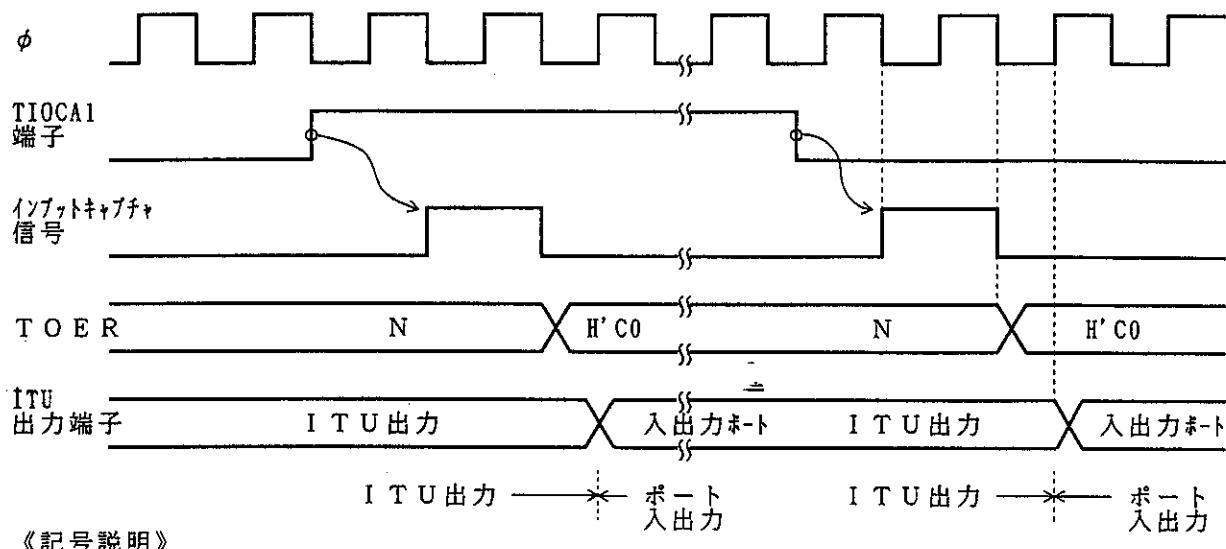

#### ビット4：外部トリガディスエーブル（X T G D）

リセット同期PWMモード／相補PWMモード時のITU出力の外部トリガによる禁止を設定します。

| ビット4    | 説明                                                                                                |

|---------|---------------------------------------------------------------------------------------------------|

| X T G D |                                                                                                   |

| 0       | リセット同期PWMモード／相補PWMモード時、チャネル1のインプットキヤプチャA信号を外部トリガとして使用<br>外部トリガの発生時、TOERのビット5～0が“0”にクリアされ、ITU出力は禁止 |

| 1       | 外部トリガを禁止<br>(初期値)                                                                                 |

#### ビット3、2：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

#### ビット1：出力レベルセレクト4（O L S 4）

リセット同期PWMモード／相補PWMモード出力のレベルを選択します。

| ビット1    | 説明                                                                        |

|---------|---------------------------------------------------------------------------|

| O L S 4 |                                                                           |

| 0       | TIOCA <sub>3</sub> 、TIOCA <sub>4</sub> 、TIOCB <sub>4</sub> は反転出力          |

| 1       | TIOCA <sub>3</sub> 、TIOCA <sub>4</sub> 、TIOCB <sub>4</sub> は直接出力<br>(初期値) |

#### ビット0：出力レベルセレクト3（O L S 3）

リセット同期PWMモード／相補PWMモード出力のレベルを選択します。

| ビット0    | 説明                                                                        |

|---------|---------------------------------------------------------------------------|

| O L S 3 |                                                                           |

| 0       | TOCXB <sub>3</sub> 、TOCXA <sub>4</sub> 、TOCXB <sub>4</sub> は反転出力          |

| 1       | TOCXB <sub>3</sub> 、TOCXA <sub>4</sub> 、TOCXB <sub>4</sub> は直接出力<br>(初期値) |

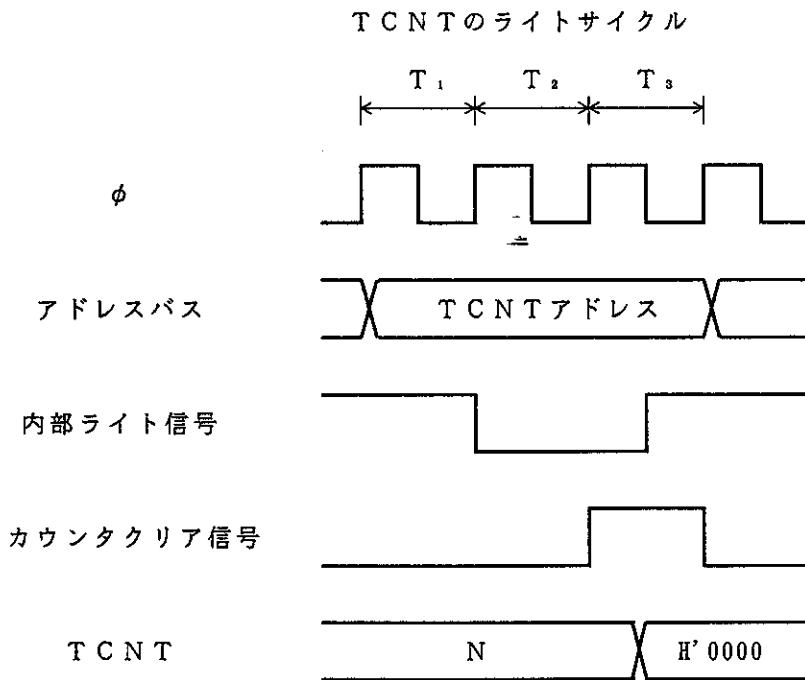

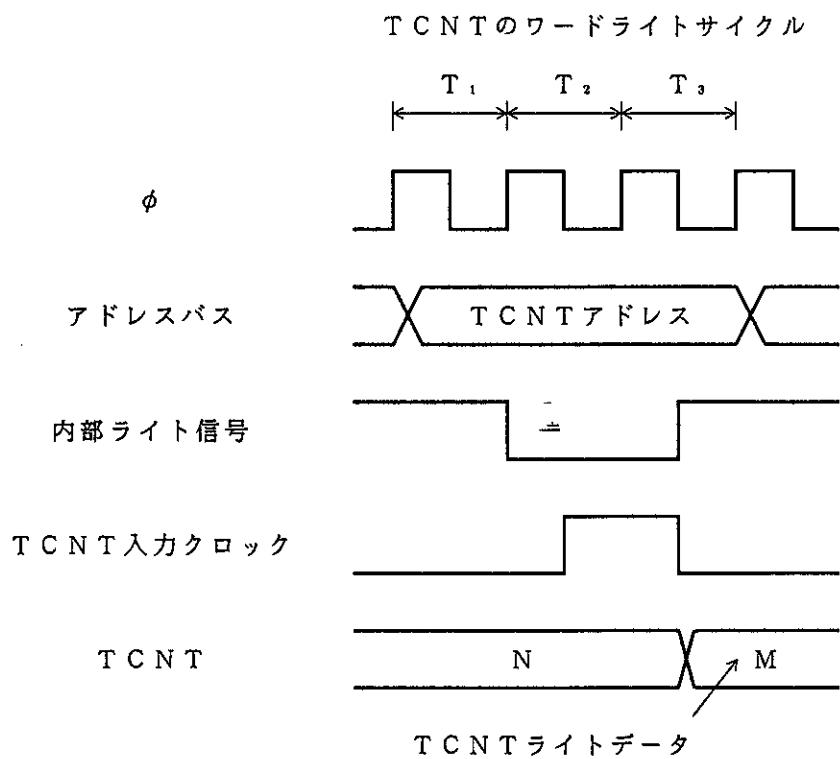

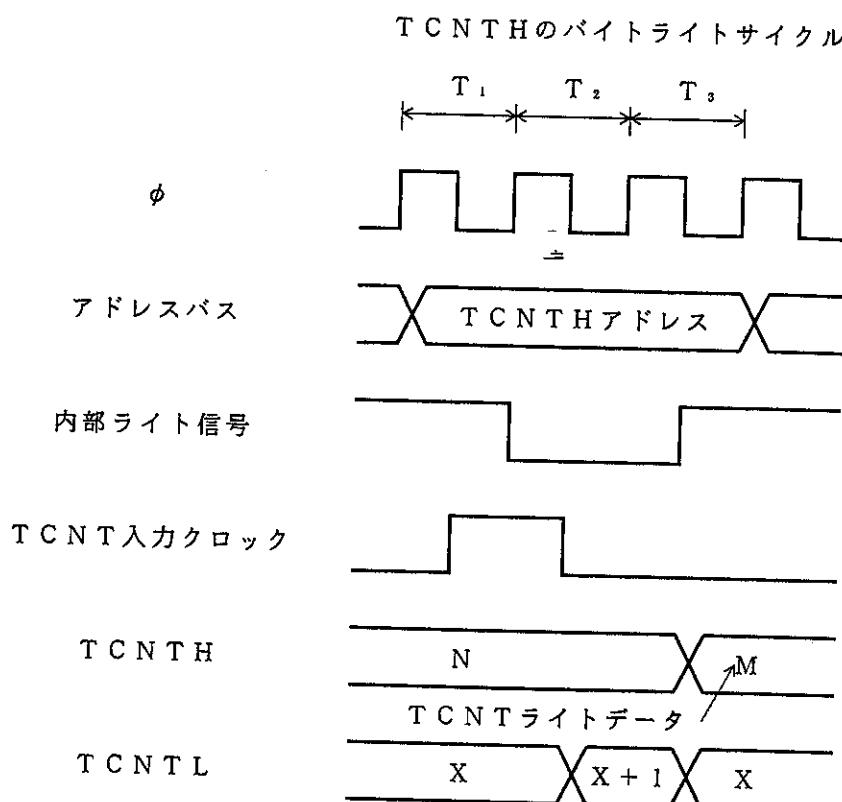

### 10.2.7 タイマカウンタ (T C N T)

T C N T は16ビットのカウンタです。I T Uには、各チャネル1本、計5本のT C N Tがあります。

| チャネル | 略 称       | 機 能                                     |

|------|-----------|-----------------------------------------|

| 0    | T C N T 0 | アップカウンタ                                 |

| 1    | T C N T 1 |                                         |

| 2    | T C N T 2 | 位相計数モード : アップ／ダウンカウンタ<br>上記以外 : アップカウンタ |

| 3    | T C N T 3 | 相補 PWMモード : アップ／ダウンカウンタ                 |

| 4    | T C N T 4 | 上記以外 : アップカウンタ                          |

ビット : 15 14 13 12 11 10 9 8 7 6 5\_ 4 3 2 1 0

初期値 : 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

R/W : R/W R/W

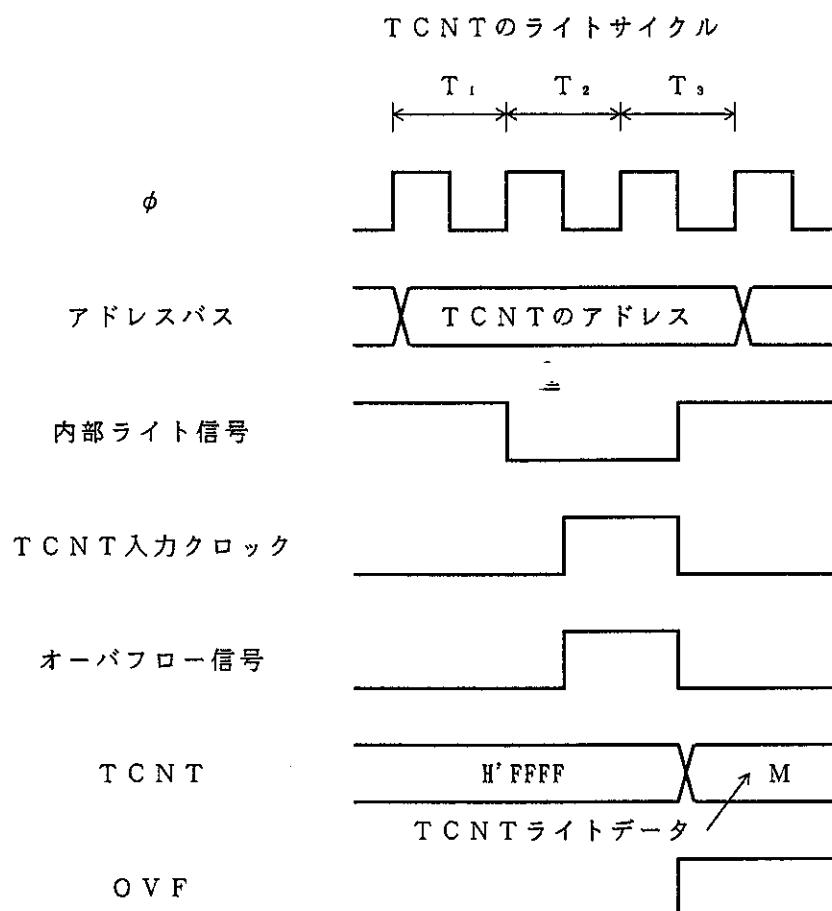

T C N T は16ビットのリード／ライト可能なレジスタで、入力したクロックによりカウント動作を行います。入力するクロックは、T C RのT P S C 2～T P S C 0ビットにより選択します。

T C N T 0、T C N T 1はアップカウント動作を行います。T C N T 2は位相計数モード時、またT C N T 3、T C N T 4は相補PWMモード時、アップ／ダウンカウント動作を行い、それ以外の場合はアップカウント動作します。

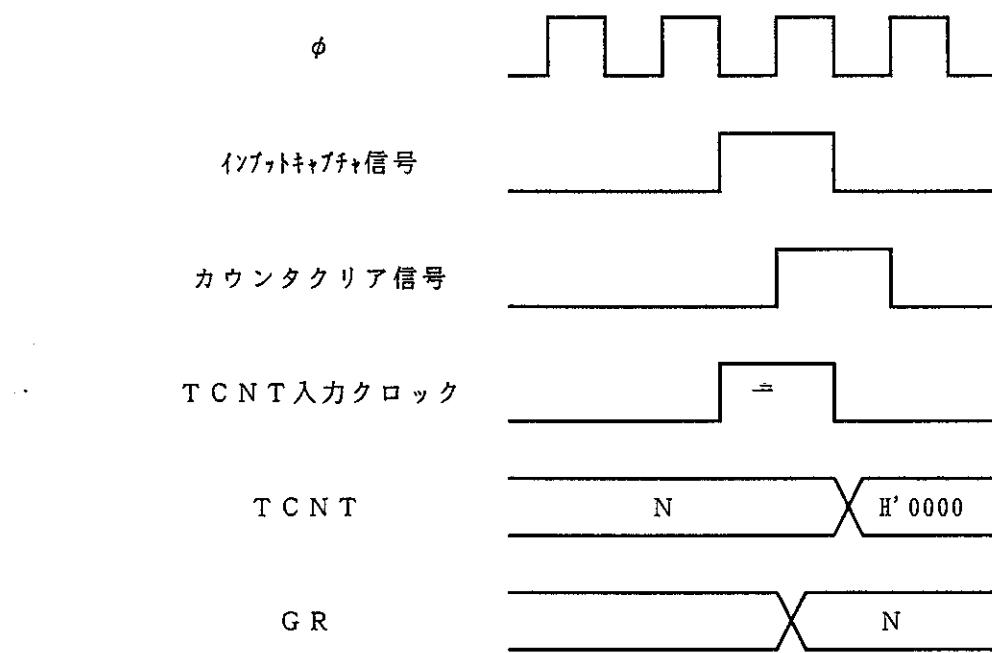

T C N T は、対応するG R A、G R Bとのコンペアマッチ、またはG R A、G R BへのインプットキャプチャによりH'0000にクリアすることができます（カウンタクリア機能）。

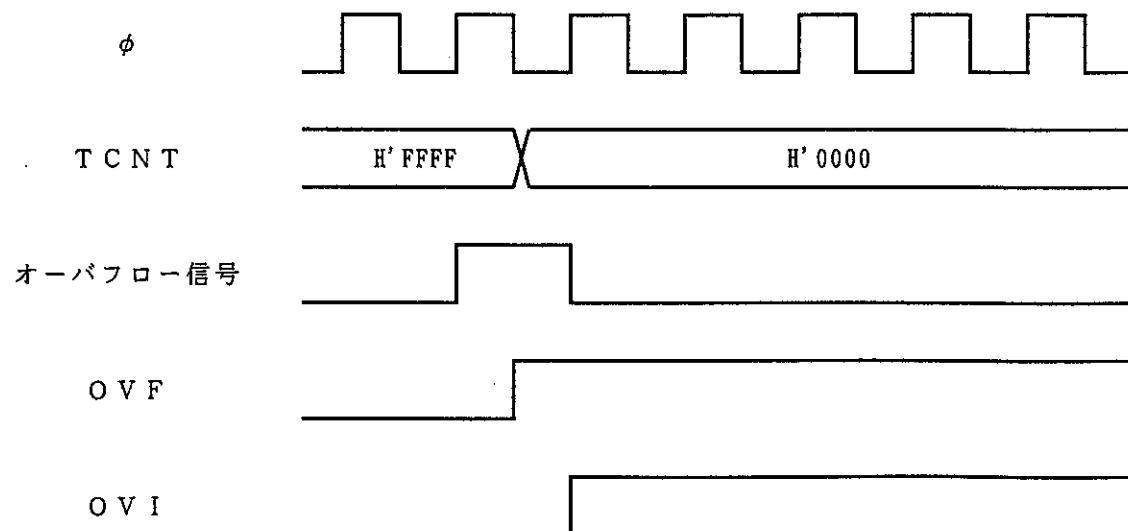

T C N T がオーバフロー (H'FFFF→H'0000) すると、対応するチャネルのT S RのO V F フラグが“1”にセットされます。

T C N T がアンダフロー (H'0000→H'FFFF) すると、対応するチャネルのT S RのO V F フラグが“1”にセットされます。

T C N T はC P Uと内部16ビットバスで接続されており、ワード／バイト単位のリード／ライトが可能です。

T C N T はリセット、またはスタンバイモード時にH'0000にイニシャライズされます。

### 10.2.8 ジェネラルレジスタA、B (G R A、G R B)

G Rは、16ビットのレジスタです。I T Uには、各チャネル2本、計10本のジェネラルレジスタがあります。

| チャネル | 略 称             | 機 能                                            |

|------|-----------------|------------------------------------------------|

| 0    | G R A 0、G R B 0 | アウトプットコンペア／インプットキャプチャ兼用レジスタ                    |

| 1    | G R A 1、G R B 1 |                                                |

| 2    | G R A 2、G R B 2 |                                                |

| 3    | G R A 3、G R B 3 | アウトプットコンペア／インプットキャプチャ兼用レジスタ。                   |

| 4    | G R A 4、G R B 4 | バッファレジスタ (B R A、B R B) と組み合わせることにより、バッファ動作設定可能 |

ビット : 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

初期値 : 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

R / W : R/W R/W

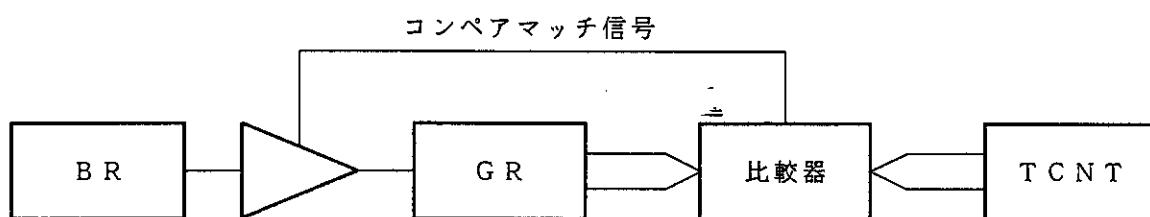

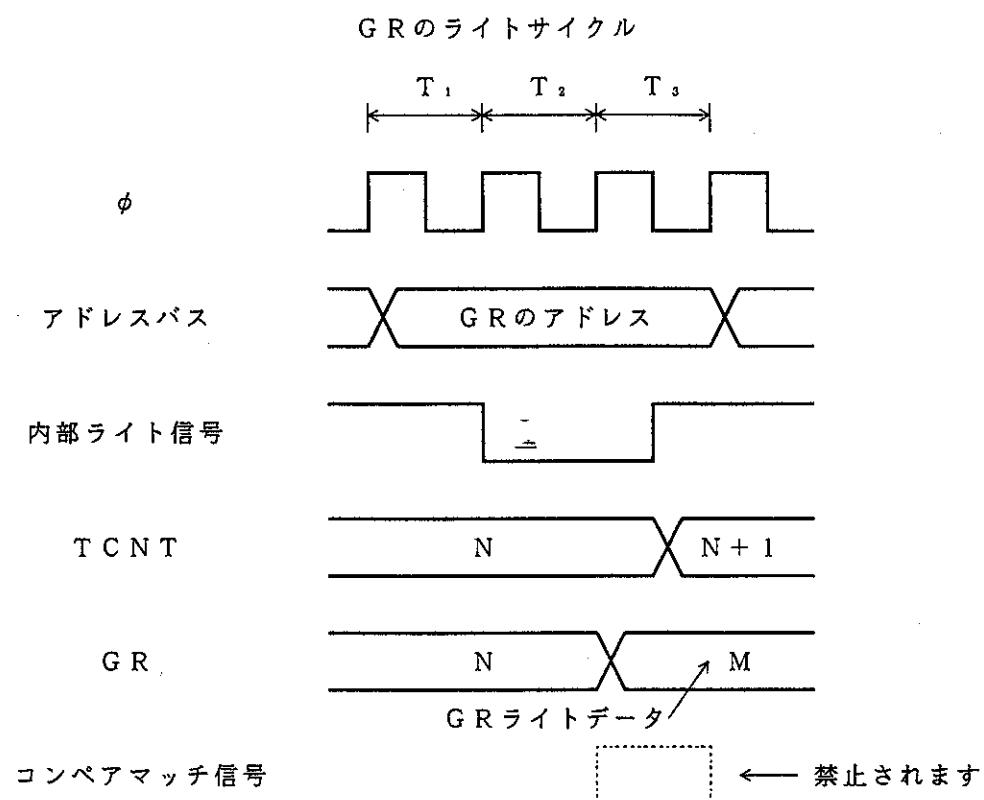

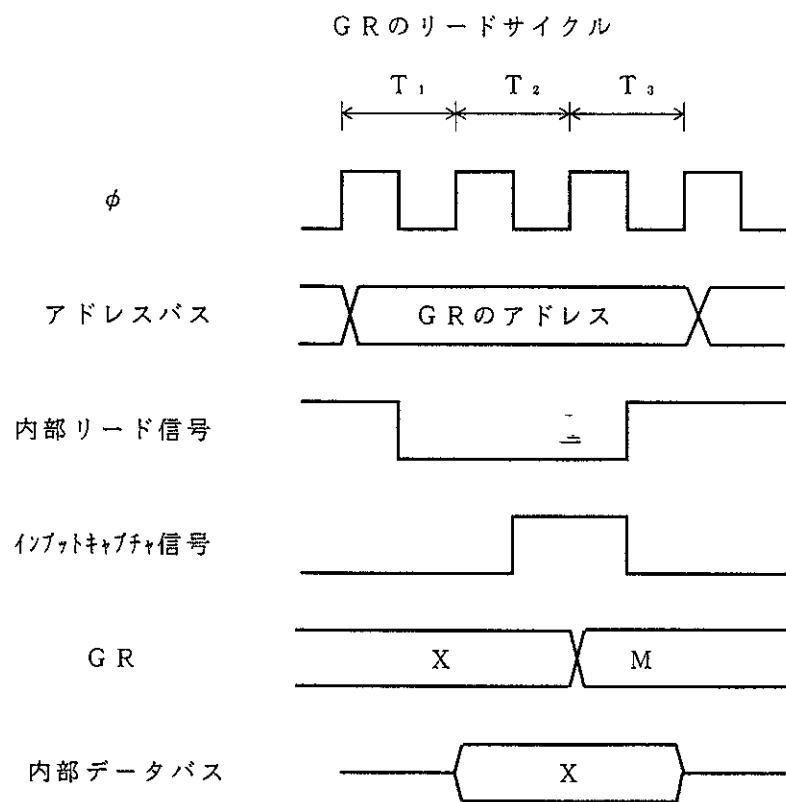

G Rは16ビットのリード／ライト可能なレジスタで、アウトプットコンペアレジスタとインプットキャプチャレジスタの両方の機能をもっています。機能の切換えは、T I O Rにより行います。

アウトプットコンペアレジスタとして使用しているときは、G R A/G R Bの値とT C N Tの値は常に比較されています。両者の値が一致（コンペアマッチ）すると、T S RのI M F A/I M F Bフラグが“1”にセットされます。T I O Rによりコンペアマッチ出力を設定することができます。

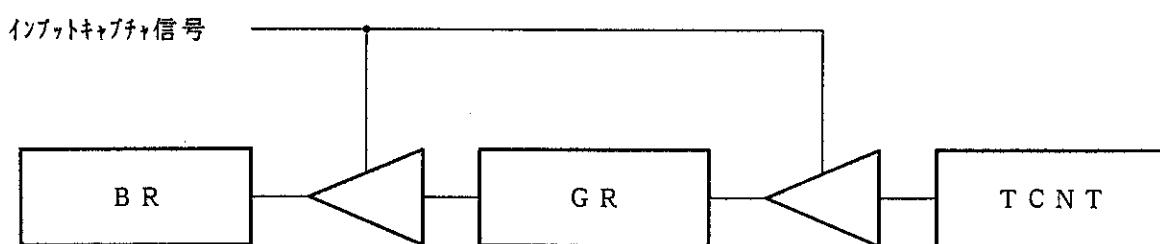

インプットキャプチャレジスタとして使用しているときは、外部からのインプットキャプチャ信号を検出して、T C N Tの値を格納します。このとき対応するT S RのI M F A/I M F Bフラグが“1”にセットされます。インプットキャプチャ信号の検出エッジはT I O Rにより行います。

P W Mモード、相補P W Mモード、またはリセット同期P W Mモードに設定されている場合には、T I O Rの設定は無視されます。

G RはC P Uと内部16ビットバスで接続されており、ワード／バイト単位のリード／ライトが可能です。

G Rはリセット、またはスタンバイモード時にアウトプットコンペアレジスタ(端子出力なし)に設定され、H' FFFFにイニシャライズされます。

### 10.2.9 バッファレジスタA、B (BRA、BRB)

B Rは、16ビットのレジスタです。I T Uには、チャネル3、4に各2本、計4本のバッファレジスタがあります。

| チャネル | 略 称       | 機 能                                                                                                          |

|------|-----------|--------------------------------------------------------------------------------------------------------------|

| 3    | BRA3、BRB3 | バッファ動作時に使用<br>• 対応するG RA、G RBがアウトプットコンペアレジスタのときアウトプットコンペアバッファレジスタとして機能し、コンペアマッチによりBRA、BRBの値をG RA、G RBに自動転送可能 |

| 4    | BRA4、BRB4 | • 対応するG RA、G RBがインプットキャプチャレジスタのときインプットキャプチャバッファレジスタとして機能し、インプットキャプチャ時それまで格納されていたG RA、G RBの値をBRA、BRBに自動転送可能   |

ビット : 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

初期値 : 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

R/W : R/W R/W

B Rは、16ビットのリード／ライト可能なレジスタで、バッファ動作設定時に使用されます。バッファ動作の設定はT F C RのBFB4、BFA4、BFB3、およびBFA3ビットにより独立に行うことができます。

B RはG Rと対になって機能し、G Rがアウトプットコンペアレジスタに設定されているときはアウトプットコンペアバッファレジスタとして、またG Rがインプットキャプチャレジスタとして設定されているときはインプットキャプチャバッファレジスタとして機能します。

B RはC P Uと内部16ビットバスで接続されており、ワード／バイト単位のリード／ライトが可能です。

B Rは、リセット、またはスタンバイモード時にH'FFFFにイニシャライズされます。

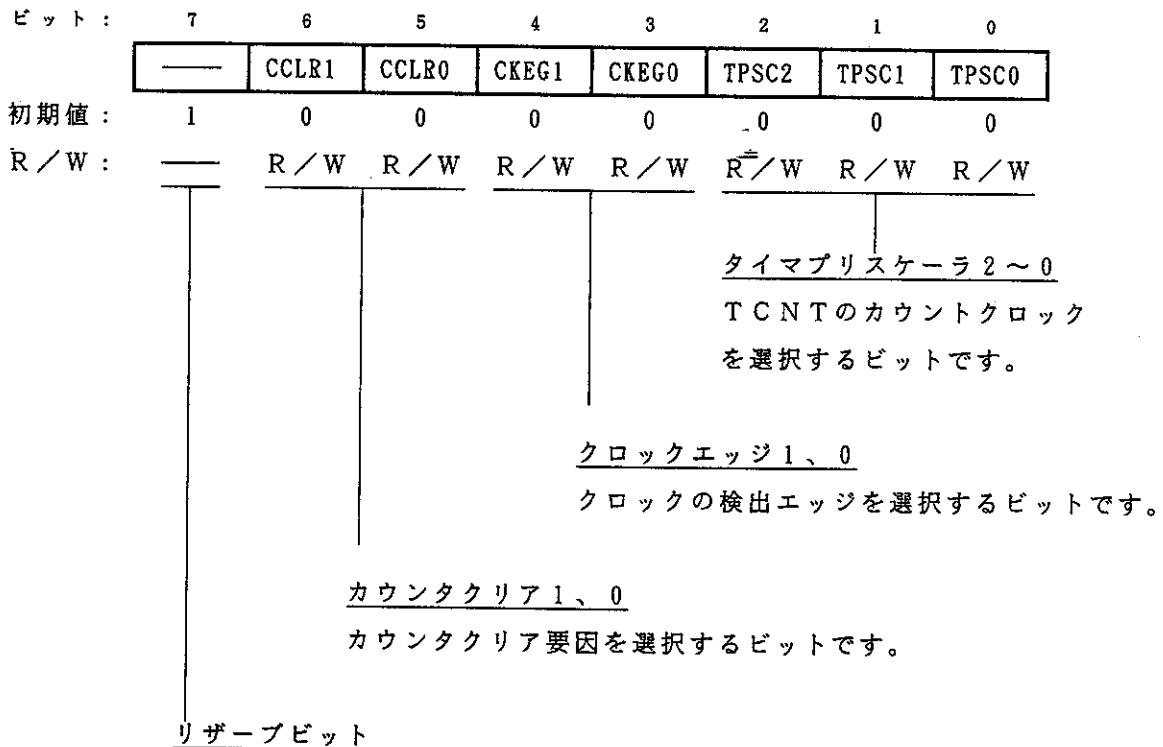

## 10.2.10 タイマコントロールレジスタ (T C R)

T C R は 8 ビットのレジスタです。I T U には、各チャネル 1 本、計 5 本の T C R があります。

| チャネル | 略 称     | 機 能                                                                                                 |

|------|---------|-----------------------------------------------------------------------------------------------------|

| 0    | T C R 0 | T C R は T C N T の制御を行います。                                                                           |

| 1    | T C R 1 | 各チャネルの T C R は同一の機能をもっています。                                                                         |

| 2    | T C R 2 | チャネル 2 を位相計数モードに設定したとき、T C R 2 の C K E G 1 、 C K E G 0 ビットおよび T P S C 2 ~ T P S C 0 ビットの設定は無効となります。 |

| 3    | T C R 3 |                                                                                                     |

| 4    | T C R 4 |                                                                                                     |

T C R は 8 ビットのリード／ライト可能なレジスタで、T C N T のカウンタクロックの選択、外部クロック選択時のエッジの選択、およびカウンタクリア要因の選択を行います。

T C R はリセット、またはスタンバイモード時に、H'80 にイニシャライズされます。

ビット 7 : リザーブビット

リザーブビットです。リードすると常に “1” が読み出されます。ライトは無効です。

ビット6、5：カウンタクリア1、0 (CCLR1、CCLR0)

T C N T のカウンタクリア要因を選択します。

| ビット6<br>CCLR1 | ビット5<br>CCLR0 | 説明                                                           |

|---------------|---------------|--------------------------------------------------------------|

| 0             | 0             | T C N T のクリア禁止<br>(初期値)                                      |

|               | 1             | G R A のコンペアマッチ／インプットキャプチャ <sup>*1</sup> でT C N T をクリア        |

| 1             | 0             | G R B のコンペアマッチ／インプットキャプチャ <sup>*1</sup> でT C N T をクリア        |

|               | 1             | 同期クリア。同期動作 <sup>*2</sup> をしている他のタイマのカウンタクリアに同期してT C N T をクリア |

【注】<sup>\*1</sup> G R がアウトプットコンペアレジスタとして機能しているとき、コンペアマッチにより、クリアされます。G R がインプットキャプチャレジスタとして機能しているとき、インプットキャプチャによりクリアされます。

<sup>\*2</sup> 同期動作の設定はT S N C により行います。

ビット4、3：クロックエッジ1、0 (CKEG1、CKEG0)

外部クロック選択時に、外部クロックの入力エッジを選択します。

| ビット4<br>CKEG1 | ビット3<br>CKEG0 | 説明                    |

|---------------|---------------|-----------------------|

| 0             | 0             | 立上がりエッジでカウント<br>(初期値) |

|               | 1             | 立下がりエッジでカウント          |

| 1             | —             | 立上がり／立下がりの両エッジでカウント   |

チャネル2が位相計数モードに設定されているとき、T C R 2 の C K E G 1 、 C K E G 0 ビットの設定は無効になり、位相計数モードの動作が優先されます。

ビット2～0：タイマプリスケーラ2～0（TPSC2～TPSC0）

TCNTのカウントクロックを選択します。

| ビット2  | ビット1  | ビット0  | 説明                            |

|-------|-------|-------|-------------------------------|

| TPSC2 | TPSC1 | TPSC0 |                               |

| 0     | 0     | 0     | 内部クロック： $\phi$ でカウント<br>(初期値) |

|       |       | 1     | 内部クロック： $\phi/2$ でカウント        |

|       | 1     | 0     | 内部クロック： $\phi/4$ でカウント        |

|       |       | 1     | 内部クロック： $\phi/8$ でカウント        |

| 1     | 0     | 0     | 外部クロックA：TCLKA端子入力でカウント        |

|       |       | 1     | 外部クロックB：TCLKB端子入力でカウント        |

|       | 1     | 0     | 外部クロックC：TCLKC端子入力でカウント        |

|       |       | 1     | 外部クロックD：TCLKD端子入力でカウント        |

TPSC2ビットを“0”にクリアして内部クロックを選択した場合、クロックの立下がりエッジでカウントされます。また、TPSC2ビットを“1”にセットして外部クロックを選択した場合、カウントエッジはCKEG1、CKEG0ビットの設定に従います。

チャネル2が位相計数モードに設定されているとき（TMDRのMDFビット＝“1”）、TCR2のTPSC2～TPSC0ビットの設定は無効となり、位相計数モードの動作が優先されます。

### 10.2.11 タイマI/Oコントロールレジスタ (TIOR)

TIORは8ビットのレジスタです。ITUには、各チャネル1本、計5本のTIORがあります。

| チャネル | 略称    | 機能                                                           |

|------|-------|--------------------------------------------------------------|

| 0    | TIOR0 | TIORはGRの制御を行います。                                             |

| 1    | TIOR1 | PWMモード時、一部機能が異なります。                                          |

| 2    | TIOR2 | チャネル3、4を相補PWMモード／リセット同期PWMモードに設定したとき、TIOR3、TIOR4の設定は無効となります。 |

| 3    | TIOR3 |                                                              |

| 4    | TIOR4 |                                                              |

ビット : 7 6 5 4 3 2 1 0

— IOB2 IOB1 IOB0 — I0A2 I0A1 I0A0

初期値 : 1 0 0 0 1 0 0 0

R/W : — R/W R/W R/W — R/W R/W R/W

I/OコントロールA 2～0

GRAの機能を選択するビットです。

リザーブビット

I/OコントロールB 2～0

GRBの機能を選択するビットです。

リザーブビット

TIORは8ビットのリード／ライト可能なレジスタで、GRA、GRBをアウトプットコンペアレジスタとして使用するか、インプットキャプチャレジスタとして使用するかを選択します。またTIOCA、TIOCMB端子の機能を選択します。アウトプットコンペアレジスタを選択した場合は出力設定を選択し、インプットキャプチャレジスタを選択した場合はインプットキャプチャ信号の入力エッジを選択します。

TIORはリセット、またはスタンバイモード時に、H'88にイニシャライズされます。

ビット7：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット6～4：I/OコントロールB2～0（I O B 2～I O B 0）

G R B の機能を選択します。

| ビット6<br>I O B 2 | ビット5<br>I O B 1 | ビット4<br>I O B 0 | 説明                            |                                                                     |

|-----------------|-----------------|-----------------|-------------------------------|---------------------------------------------------------------------|

| 0               | 0               | 0               | G R B はアウト<br>プットコンペア<br>レジスタ | コンペアマッチによる端子出力禁止<br>(初期値)                                           |

|                 |                 | 1               |                               | G R B のコンペアマッチで0出力* <sup>1</sup>                                    |

|                 | 1               | 0               |                               | G R B のコンペアマッチで1出力* <sup>1</sup>                                    |

|                 |                 | 1               |                               | G R B のコンペアマッチでトグル出力<br>(チャネル2のみ1出力) * <sup>1</sup> 、* <sup>2</sup> |

| 1               | 0               | 0               | G R B はインプ<br>ットキャプチャ<br>レジスタ | 立上がりエッジでG R Bへインプットキャ<br>プチャ                                        |

|                 |                 | 1               |                               | 立下がりエッジでG R Bへインプットキャ<br>プチャ                                        |

|                 | 1               | 0               |                               | 立上がり／立下がりの両エッジでインプッ<br>トキャプチャ                                       |

【注】\*<sup>1</sup> リセット後、最初のコンペアマッチが発生するまでの出力値は0です。

\*<sup>2</sup> チャネル2はコンペアマッチによるトグル出力機能がありません。この設定にすると自動的に1出力が選択されます。

ビット3：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット2～0：I/OコントロールA2～0 (IOA2～IOA0)

GRAの機能を選択します。

| ビット2<br>IOA2 | ビット1<br>IOA1 | ビット0<br>IOA0 | 説明                         |                                        |

|--------------|--------------|--------------|----------------------------|----------------------------------------|

| 0            | 0            | 0            | GRAはアウト<br>プットコンペア<br>レジスタ | コンペアマッチによる端子出力禁止<br>(初期値)              |

|              |              | 1            |                            | GRAのコンペアマッチで0出力*1                      |

|              | 1            | 0            |                            | GRAのコンペアマッチで1出力*1                      |

|              |              | 1            |                            | GRAのコンペアマッチでトグル出力<br>(チャネル2のみ1出力) *1*2 |

| 1            | 0            | 0            | GRAはインプ<br>ットキャプチャ<br>レジスタ | 立上がりエッジでGRAへインプットキャ<br>プチャ             |

|              |              | 1            |                            | 立下がりエッジでGRAへインプットキャ<br>プチャ             |

|              | 1            | 0            |                            | 立上がり／立下がりの両エッジでインプッ<br>トキャプチャ          |

|              |              | 1            |                            |                                        |

【注】\*1 リセット後、最初のコンペアマッチが発生するまでの出力値は0です。

\*2 チャネル2はコンペアマッチによるトグル出力機能がありません。この設定にすると自動的に1出力が選択されます。

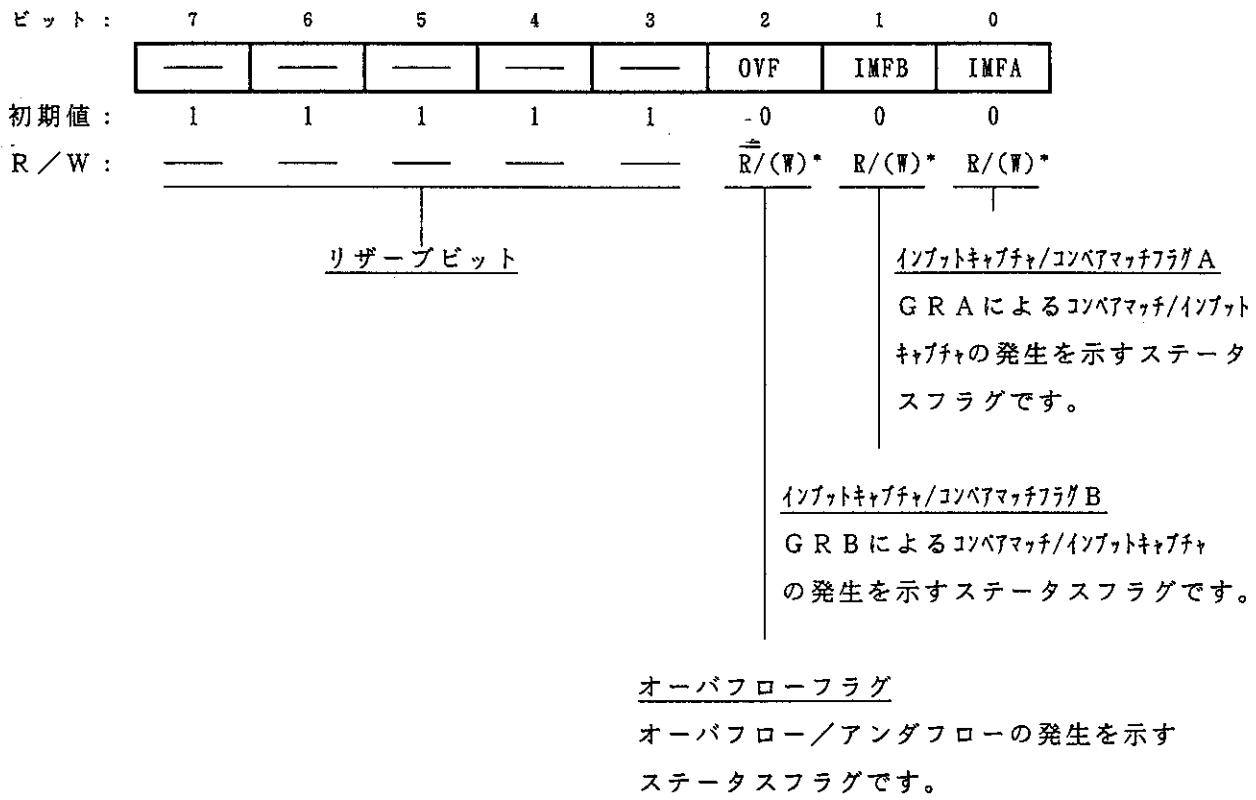

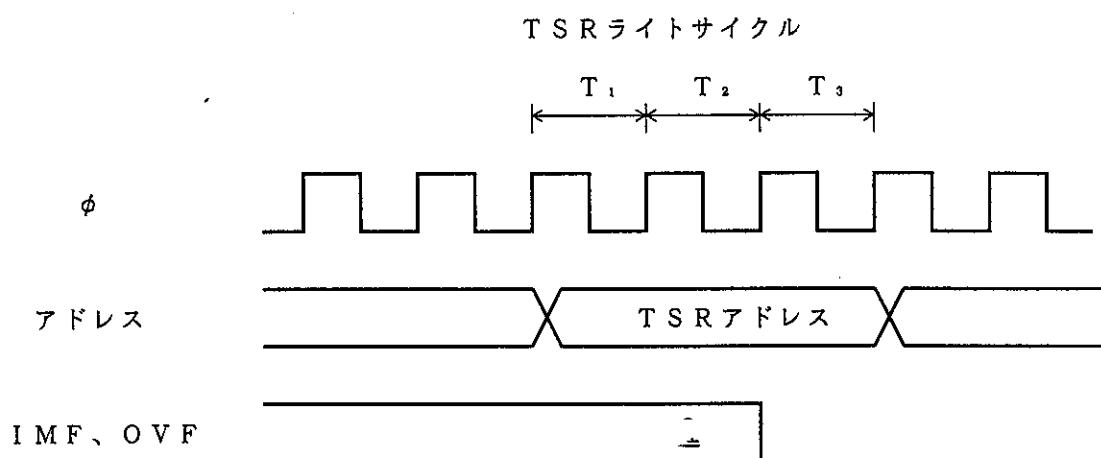

## 10.2.12 タイマステータスレジスタ (T S R)

T S R は 8 ビットのレジスタです。I T U には、各チャネル 1 本、計 5 本の T S R があります。

| チャネル | 略 称     | 機 能                                   |

|------|---------|---------------------------------------|

| 0    | T S R 0 | インプットキャプチャ／コンペアマッチやオーバフローのステータスを示します。 |

| 1    | T S R 1 |                                       |

| 2    | T S R 2 |                                       |

| 3    | T S R 3 |                                       |

| 4    | T S R 4 |                                       |

【注】\* フラグをクリアするための “0” ライトのみ可能です。

T S R は 8 ビットのリード／ライト可能なレジスタで、T C N T のオーバフロー／アンダフローの発生、および G R A、G R B のコンペアマッチ／インプットキャプチャの発生を示します。

これらのフラグは割込み要因であり、T I E R の対応するビットにより割込みが許可されていれば、C P U に割込みを要求します。

T S R はリセット、またはスタンバイモード時に、H'F8 にイニシャライズされます。

### ビット7～3：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

### ビット2：オーバフローフラグ(OVF)

T C N Tのオーバフロー／アンダフローの発生を示すステータスフラグです。

| ビット2  | 説明                                                                                                                  |

|-------|---------------------------------------------------------------------------------------------------------------------|

| O V F |                                                                                                                     |

| 0     | [クリア条件]<br>O V F = “1”の状態で、O V F フラグをリードした後、O V F フラグに“0”をライトしたとき<br>(初期値)                                          |

| 1     | [セット条件]<br>T C N Tの値がオーバフロー ( $H' FFFF \rightarrow H' 0000$ ) または<br>アンダフロー ( $H' 0000 \rightarrow H' FFFF$ ) したとき* |

【注】\* T C N Tのアンダーフローは、T C N Tがアップ／ダウンカウンタとして機能している場合に発生します。したがって、次の場合のみアンダフローが発生することがあります。

- (1)チャネル2が位相計数モードに設定されているとき(T M D RのM D F = “1”)

- (2)チャネル3、4が相補P W Mモードに設定されているとき(T F C RのC M D 1 = “1”、C M D 0 = “0”)

### ビット1：インプットキャプチャ／コンペアマッチフラグB(IMFB)

G R Bのコンペアマッチまたはインプットキャプチャの発生を示すステータスフラグです。

| ビット1    | 説明                                                                                                                                                   |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| I M F B |                                                                                                                                                      |

| 0       | [クリア条件]<br>I M F B = “1”の状態で、I M F B フラグをリードした後、I M F B フラグに“0”をライトしたとき<br>(初期値)                                                                     |

| 1       | [セット条件]<br>(1)G R Bがアウトプットコンペアレジスタとして機能している場合、<br>T C N T = G R Bになったとき<br>(2)G R Bがインプットキャプチャレジスタとして機能している場合、インプットキャプチャ信号によりT C N Tの値がG R Bに転送されたとき |

ビット0：インプットキャプチャ／コンペアマッチフラグA（IMFA）

GRAのコンペアマッチまたはインプットキャプチャの発生を示すステータスフラグです。

| ビット0<br>IMFA | 説明                                                                                                                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | [クリア条件]<br>(1) IMFA = "1" の状態で、IMFAフラグをリードした後、IMFAフラグに "0" をライトしたとき<br>(2) IMIA割込みにより DMA Cが起動されたとき（チャネル0～3のみ）                           |

| 1            | [セット条件]<br>(1) GRAがアウトプットコンペアレジスタとして機能している場合、TCNT = GRAになったとき<br>(2) GRAがインプットキャプチャレジスタとして機能している場合、インプットキャプチャ信号により TCNT の値が GRA に転送されたとき |

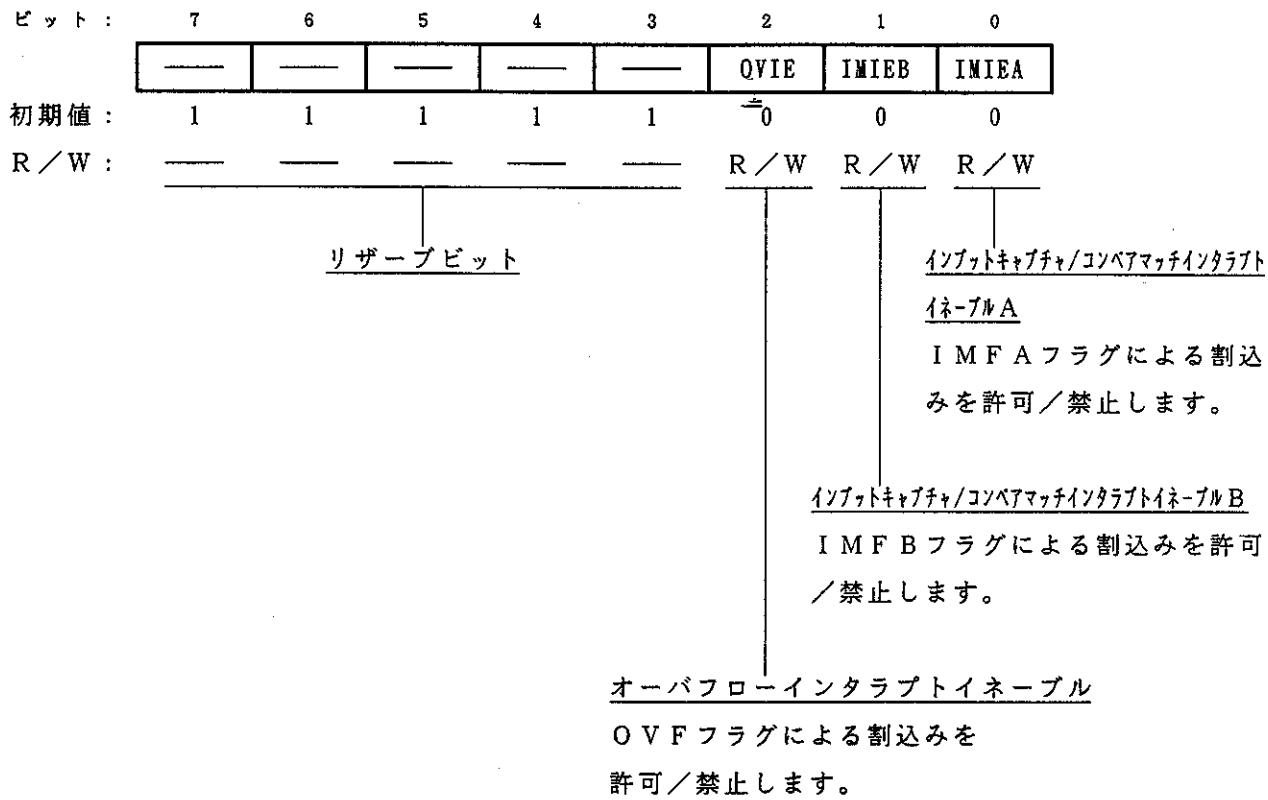

### 10.2.13 タイマインタラプトイネーブルレジスタ (TIER)

TIERは8ビットのレジスタです。ITUには、各チャネル1本、計5本のTIERがあります。

| チャネル | 略 称    | 機 能                |

|------|--------|--------------------|

| 0    | TIER 0 | 割込み要求の許可／禁止を制御します。 |

| 1    | TIER 1 |                    |

| 2    | TIER 2 |                    |

| 3    | TIER 3 |                    |

| 4    | TIER 4 |                    |

TIERは8ビットのリード／ライト可能なレジスタで、オーバフロー割込み要求、GRのコンペアマッチ／インプットキャプチャ割込み要求の許可／禁止を制御します。

TIERはリセット、またはスタンバイモード時に、H'F8にイニシャライズされます。

ビット7～3：リザーブビット

リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

## ビット2：オーバフローインタラプトイネーブル(OVIE)

TSRのOVFフラグが“1”にセットされたとき、OVFフラグによる割込み要求を許可／禁止します。

| ビット2 | 説明                     |       |

|------|------------------------|-------|

| OVIE |                        |       |

| 0    | OVFフラグによる割込み(OVI)要求を禁止 | (初期値) |

| 1    | OVFフラグによる割込み(OVI)要求を許可 |       |

## ビット1：インプットキャプチャ／コンペアマッチインタラプトイネーブルB(IMIEB)

TSRのIMFBフラグが“1”にセットされたとき、IMFBによる割込み要求を許可／禁止します。

| ビット1  | 説明                       |       |

|-------|--------------------------|-------|

| IMIEB |                          |       |

| 0     | IMFBフラグによる割込み(IMIB)要求を禁止 | (初期値) |

| 1     | IMFBフラグによる割込み(IMIB)要求を許可 |       |

## ビット0：インプットキャプチャ／コンペアマッチインタラプトイネーブルA(IMIEA)

TSRのIMFAフラグが“1”にセットされたとき、IMFAによる割込み要求を許可／禁止します。

| ビット0  | 説明                       |       |

|-------|--------------------------|-------|

| IMIEA |                          |       |

| 0     | IMFAフラグによる割込み(IMIA)要求を禁止 | (初期値) |

| 1     | IMFAフラグによる割込み(IMIA)要求を許可 |       |

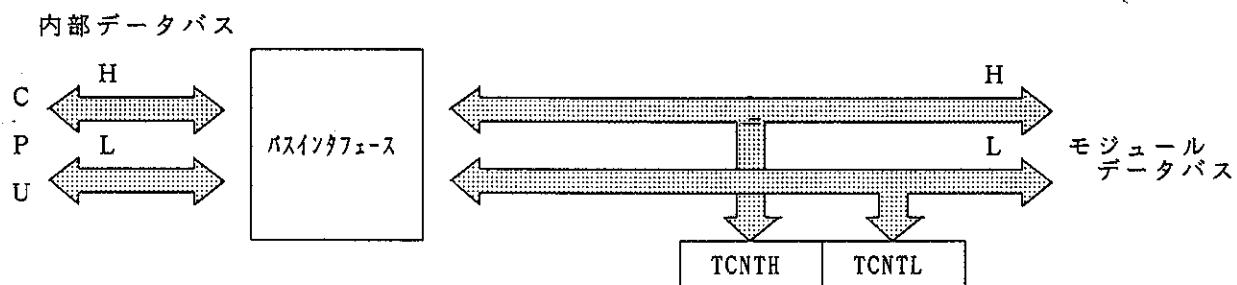

## 10.3 CPUとのインターフェース

### 10.3.1 16ビットアクセス可能なレジスタ

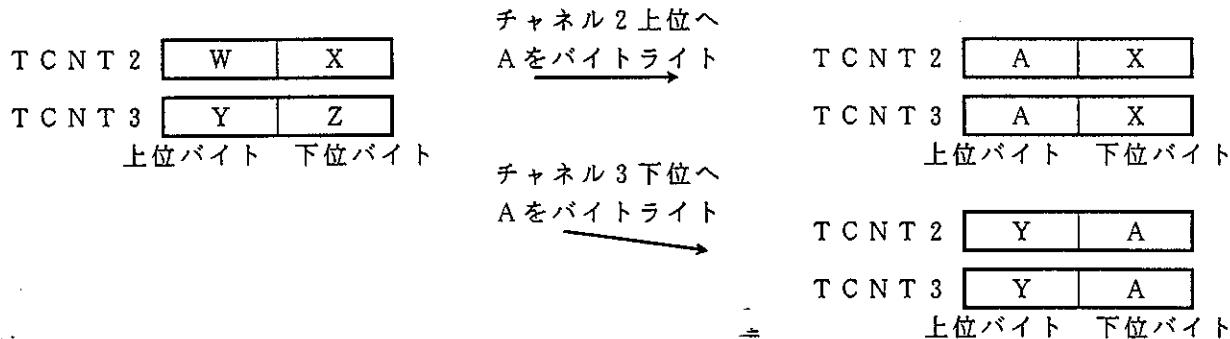

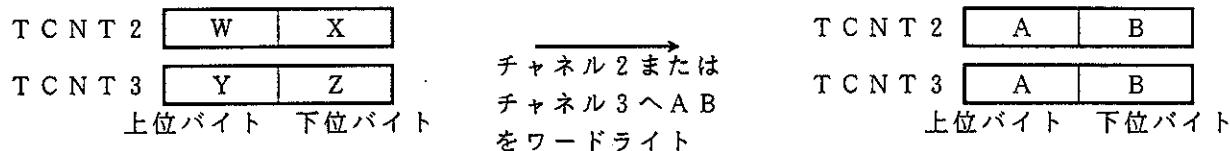

TCNT、GRA、GRB、およびBRA、BRB、BRは16ビットのレジスタです。これらのレジスタは、CPUと内部16ビットデータバスで接続されており、ワード単位のリード／ライトが可能です。また、バイト単位のリード／ライトもできます。

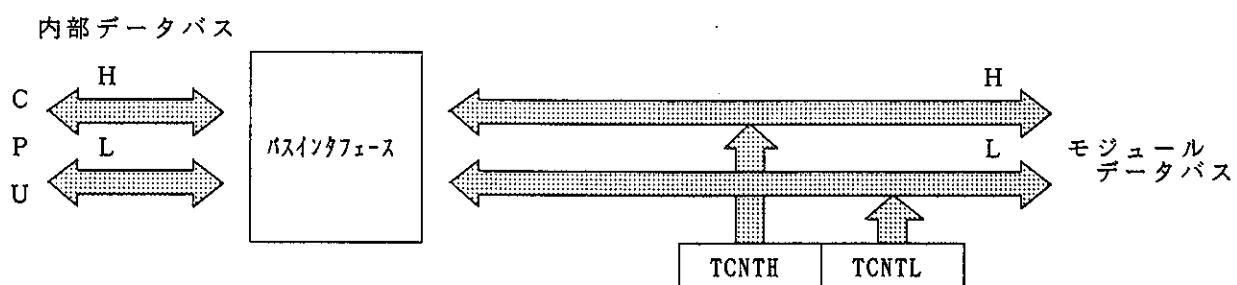

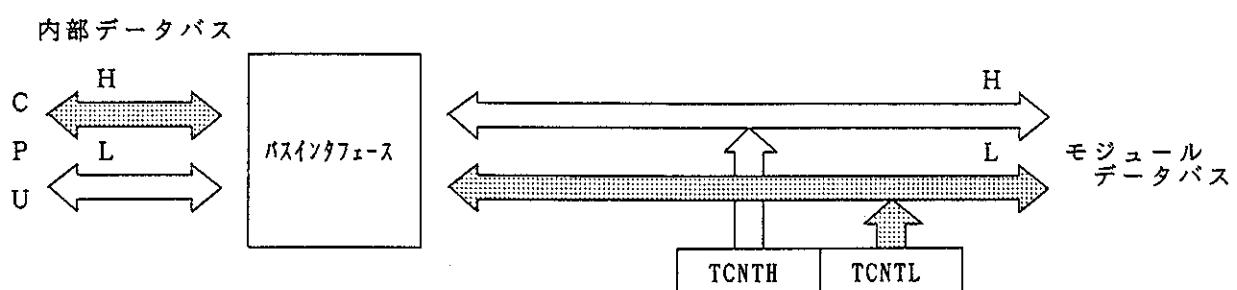

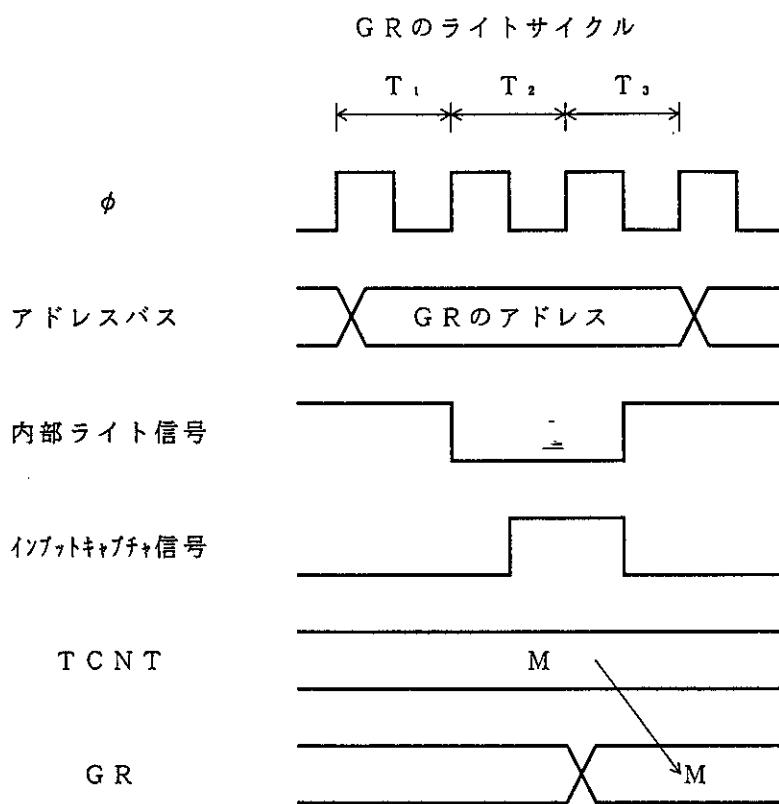

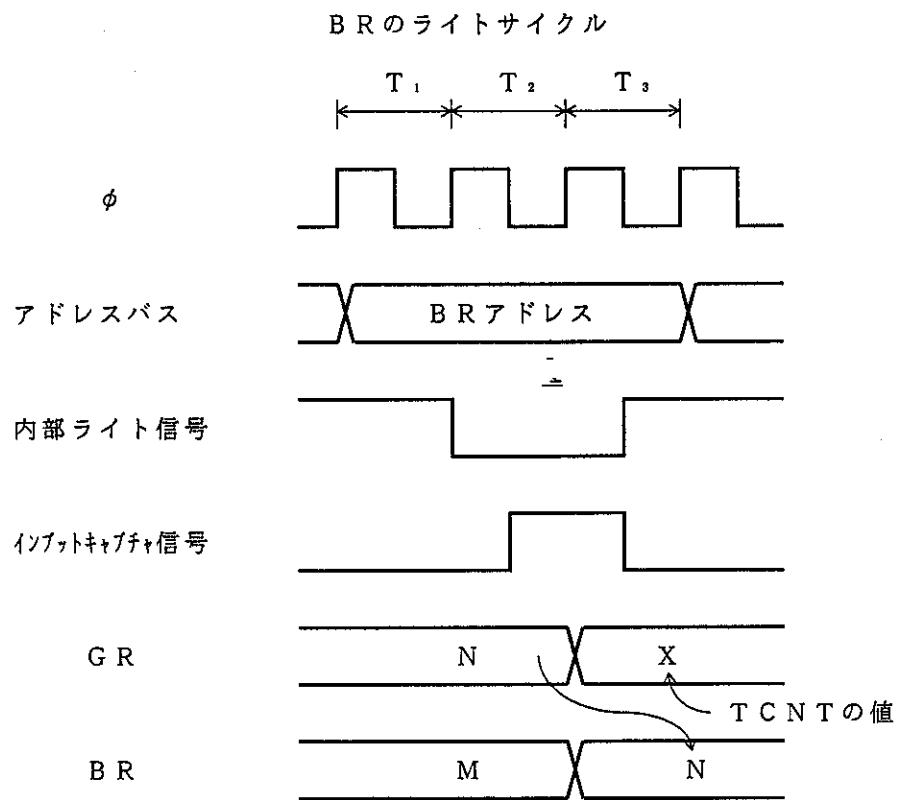

TCNTに対してワード単位のリード／ライトを行った場合の動作を図10.6、図10.7に示します。

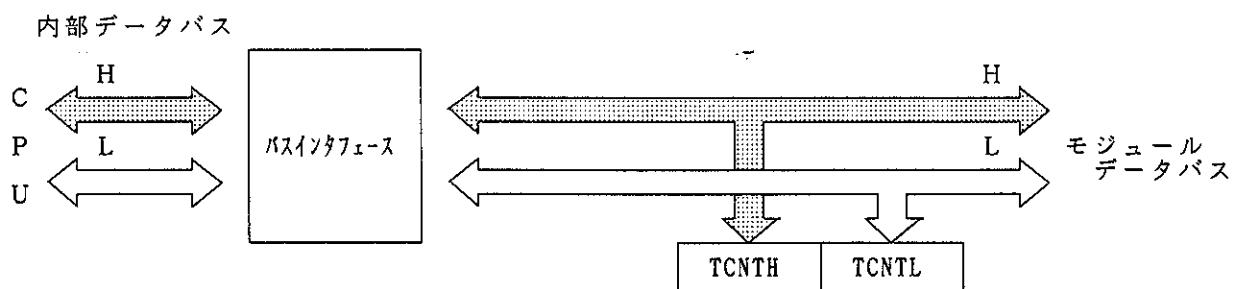

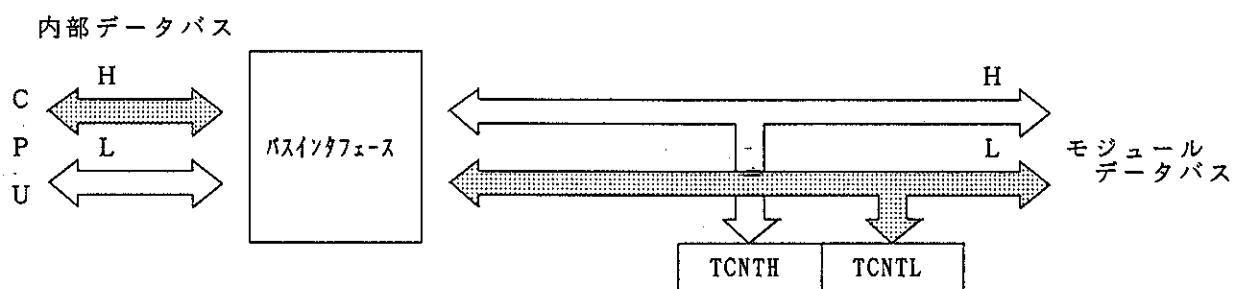

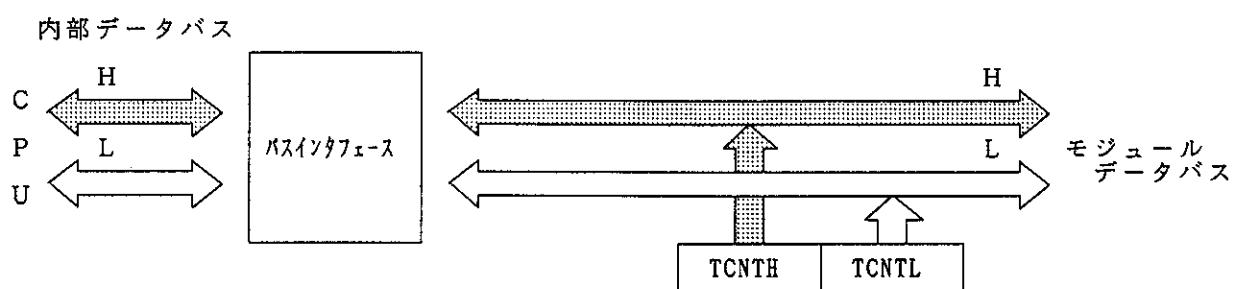

また、TCNTH、TCNTLに対してバイト単位のリード／ライトを行った場合の動作を図10.8、図10.9、図10.10、図10.11に示します。

図10.6 TCNTのアクセス動作 [CPU→TCNT (ワード)]

図10.7 TCNTのアクセス動作 [TCNT→CPU (ワード)]

図10.8 TCNTのアクセス動作 [CPU→TCNT (上位バイト)]

図10.9 TCNTのアクセス動作 [CPU→TCNT (下位バイト)]

図10.10 TCNTのアクセス動作 [TCNT→CPU (上位バイト)]

図10.11 TCNTのアクセス動作 [TCNT→CPU (下位バイト)]

### 10.3.2 8ビットアクセスのレジスタ

T C N T、G R、B R以外のレジスタは8ビットレジスタです。これらのレジスタはC P Uと内部8ビットデータバスで接続されています。

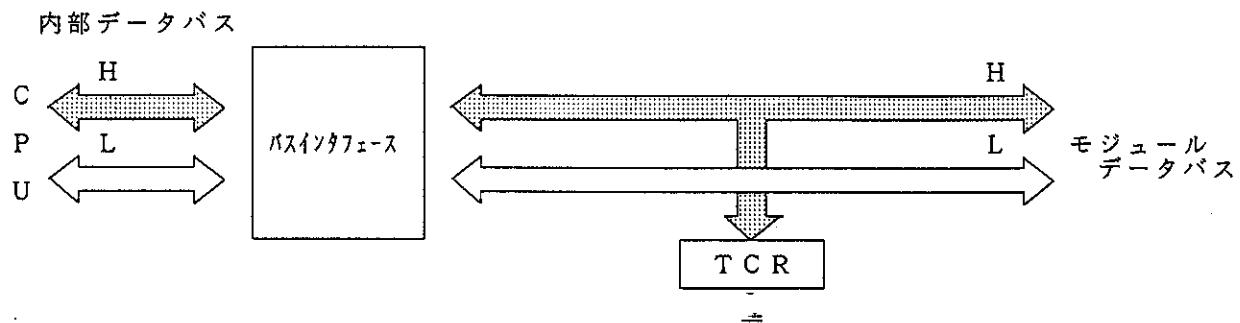

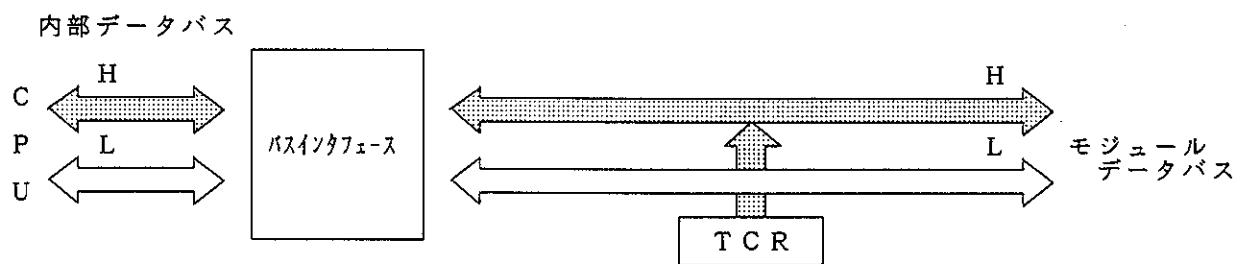

T C Rに対してバイト単位のリード／ライトを行った場合の動作を図10.12、図10.13に示します。なお、ワードサイズの転送命令を実行するとバイト単位2回の転送が行われます。

図10.12 T C Rのアクセス動作 [C P U→T C R]

図10.13 T C Rのアクセス動作 [T C R→C P U]

## 10.4 動作説明

### 10.4.1 概要

以下に各モードの動作概要を示します。

#### (1) 通常動作

各チャネルには、T C N TとG Rがあります。T C N Tは、アップカウント動作を行い、フリーランニング動作、周期カウント動作、または外部イベントカウント動作が可能です。

G R A、G R Bは、それぞれインプットキャプチャレジスタまたはアウトプットコンペアレジスタとして使用することができます。

#### (2) 同期動作

同期動作を設定したチャネルのT C N Tは、同期プリセット動作を行います。すなわち、同期動作に設定されたチャネルのうち任意のT C N Tを書き換えると他のチャネルのT C N Tも同時に書き換えられます。また、同期動作に設定された複数のチャネルのT C RのC C L R 1、C C L R 0ビットの設定により、T C N Tの同期クリアが可能です。

#### (3) P W Mモード

T I O C A端子からP W M波形を出力するモードです。コンペアマッチAにより1出力、コンペアマッチBにより0出力となります。G R A、G R Bの設定により、デューティ0～100%のP W M波形を出力できます。P W Mモードに設定すると当該チャネルのG R A、G R Bは自動的にアウトプットコンペアレジスタとして機能します。

#### (4) リセット同期P W Mモード

チャネル3、4を組み合わせて、正相と逆相のP W M波形を3相出力します（3相のP W M波形は一方の変化点が共通となる関係になります）。リセット同期P W Mモードに設定するとG R A 3、G R B 3、G R A 4、G R B 4は自動的にアウトプットコンペアレジスタとして機能します。また、T I O C A 3、T I O C B 3、T I O C A 4、T O C X A 4、T I O C B 4、T O C X B 4端子は自動的にP W M出力端子となり、T C N T 3はアップカウント動作を行います。T C N T 4は独立に動作します（ただし、G R A 4、G R B 4はT C N T 4とは切り離されています）。

#### (5) 相補P W Mモード

チャネル3、4を組み合わせて、正相と逆相がノンオーバラップの関係にあるP W M波形を3相出力します。相補P W Mモードに設定するとG R A 3、G R B 3、G R A 4、G R B 4は自動的にアウトプットコンペアレジスタとして機能します。また、T I O C A 3、T I O C B 3、T I O C A 4、T O C X A 4、T I O C B 4、T O C X B 4端子は自動的にP W M出力端子となり、T C N T 3、T C N T 4はアップ／ダウンカウント動作を行います。

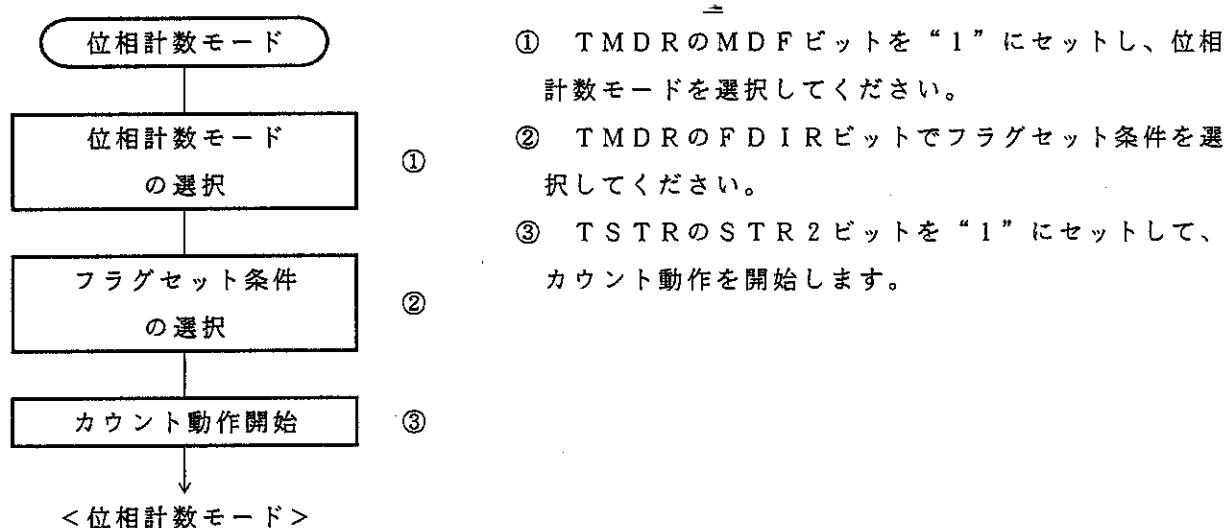

#### (6) 位相計数モード

TCLKA、TCLKB端子から入力される2つのクロックの位相差を検出して、T C N T 2をアップ／ダウンカウント動作させるモードです。位相計数モードに設定するとTCLKA、TCLKB端子はクロック入力となり、またT C N T 2はアップ／ダウンカウント動作を行います。

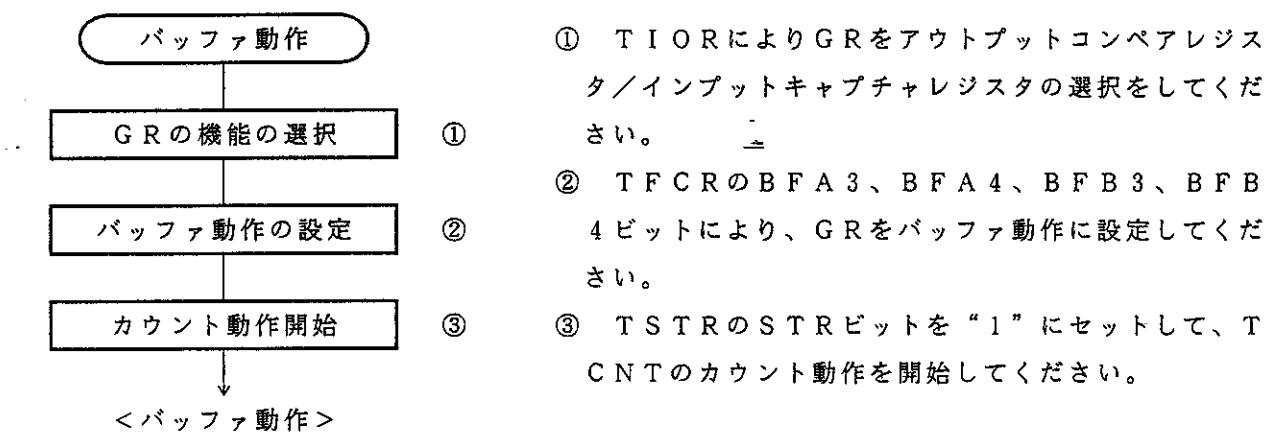

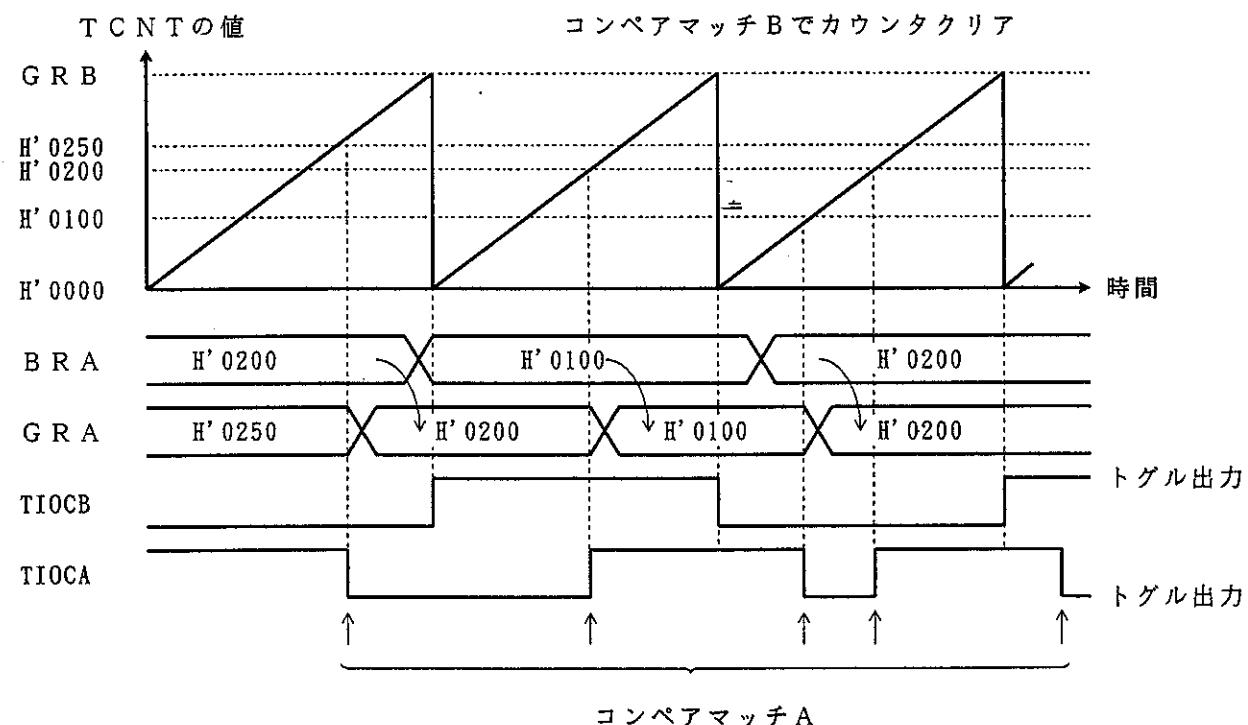

#### (7) バッファ動作

##### ① G Rがアウトプットコンペアレジスタの場合

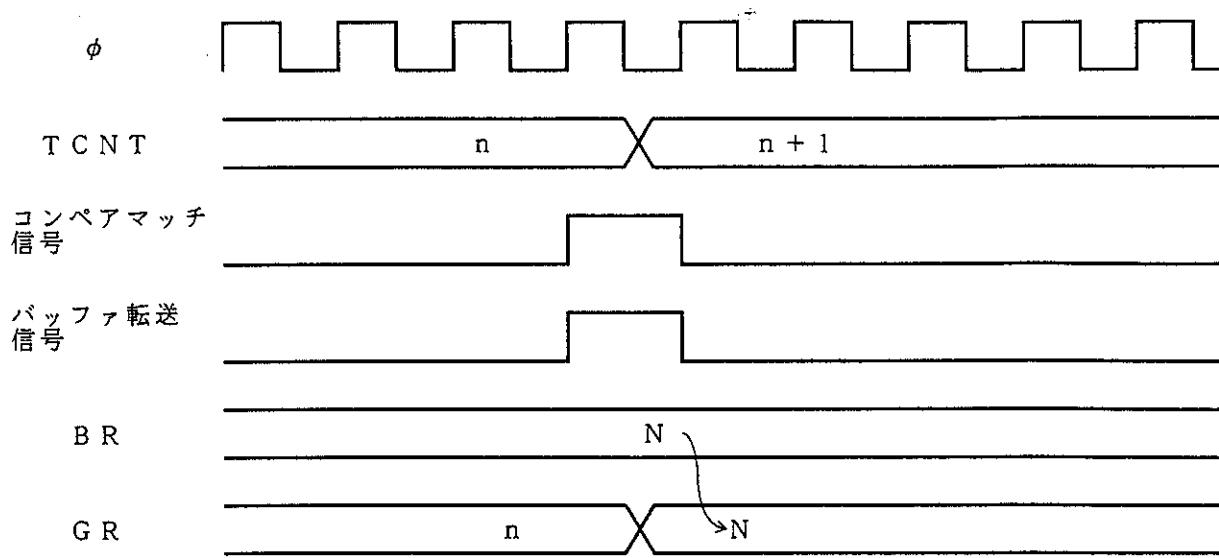

コンペアマッチが発生すると当該チャネルのB Rの値が、G Rに転送されます。

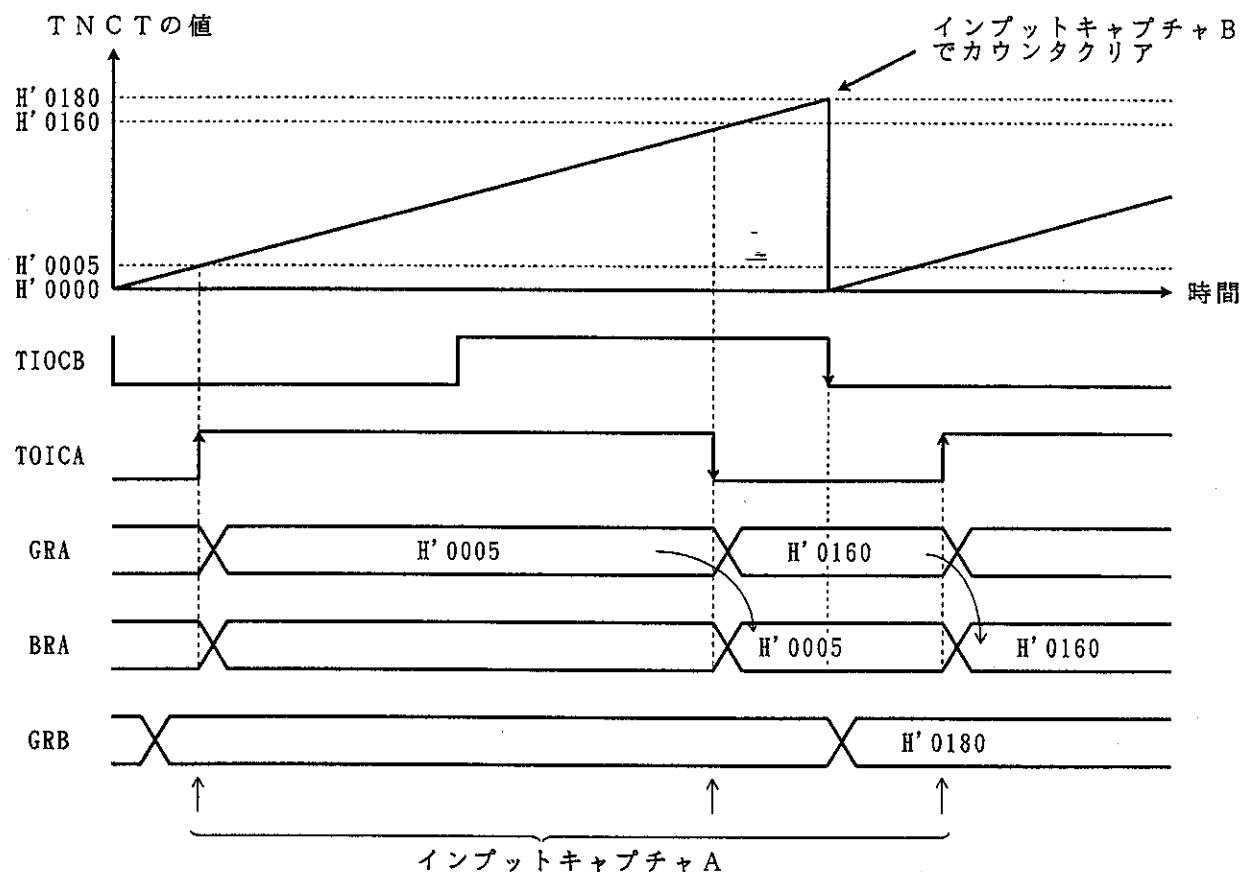

##### ② G Rがインプットキャプチャレジスタの場合

インプットキャプチャが発生するとT C N Tの値をG Rに転送すると同時に、それまで格納されていたG Rの値をB Rに転送します。

##### ③ 相補P W Mモードの場合

T C N T 3、T C N T 4のカウント方向が変化するとB Rの値が、G Rに転送されます。

##### ④ リセット同期P W Mモードの場合

G R A 3のコンペアマッチによりB Rの値が、G Rに転送されます。

#### 10.4.2 基本機能

##### (1) カウンタの動作

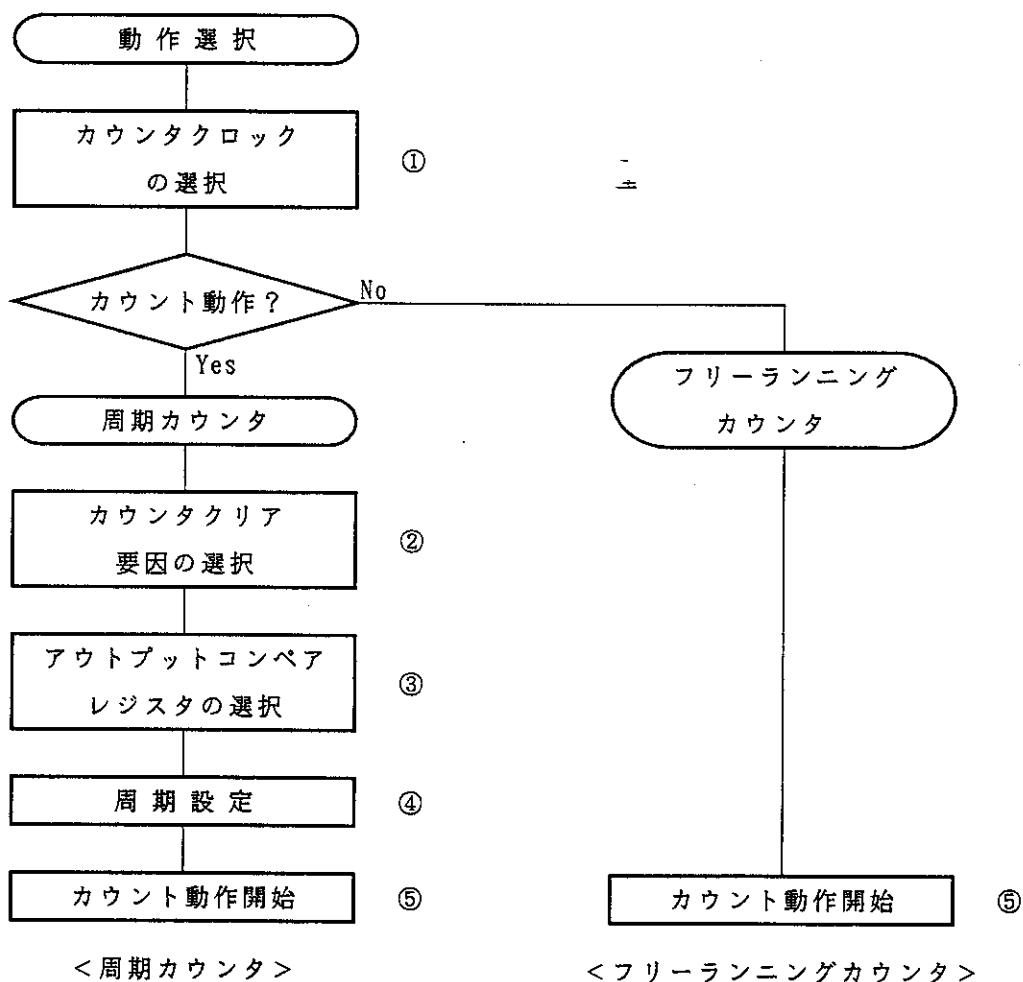

タイマスタートレジスタ（TSTR）のSTR0～STR4ビットを“1”にセットすると、対応するチャネルのTCNTはカウント動作を開始します。フリーランニングカウンタ動作、周期カウンタ動作などが可能です。

##### (a) カウント動作の設定手順例

カウント動作の設定手順例を図10.14に示します。

図10.14 カウント動作設定手順例

- ① TCRのTPSC2～TPSC0ビットでカウンタクロックを選択してください。外部クロックを選択した場合は、TCRのCKEG1、CKEG0ビットで外部クロックのエッジを選択してください。

- ② 周期カウント動作の場合TCRのCCLR1、CCLR0ビットでTCNTをGRAのコンペアマッチでクリアするか、GRBのコンペアマッチでクリアするかを選択してください。

- ③ ②で選択したGRAまたはGRBを、TIORによりアウトプットコンペアレジスタに設定してください。

- ④ ②で選択したGRAまたはGRBに周期カウンタの周期を設定してください。

- ⑤ TSTRのSTRビットを“1”にセットしてカウント動作を開始してください。

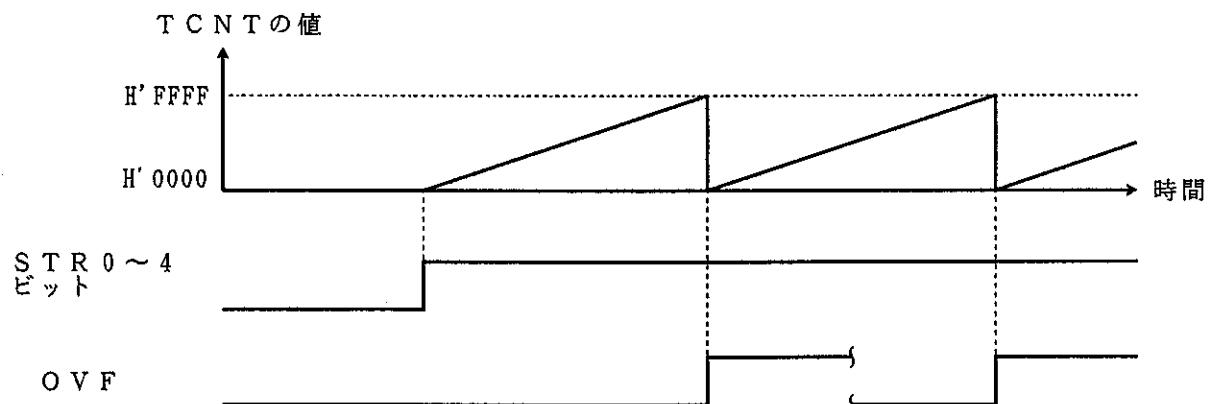

(b) フリーランニングカウント動作と周期カウント動作

ITUチャネル0～4のカウンタ(TCNT)はリセット直後は、すべてフリーランニングカウンタの設定となっており、TSTRの対応するビットを“1”にセットするとフリーランニングカウンタとしてアップカウント動作を開始します。TCNTがオーバフロー( $H' FFFF \rightarrow H' 0000$ )するとTSRのOVFフラグが“1”にセットされます。このとき、対応するTIERのOVIEビットが“1”ならば、CPUに割込みを要求します。TCNTはオーバフロー後、H' 0000から再びアップカウント動作を継続します。

フリーランニングカウンタの動作を図10.15に示します。

図10.15 フリーランニングカウンタの動作

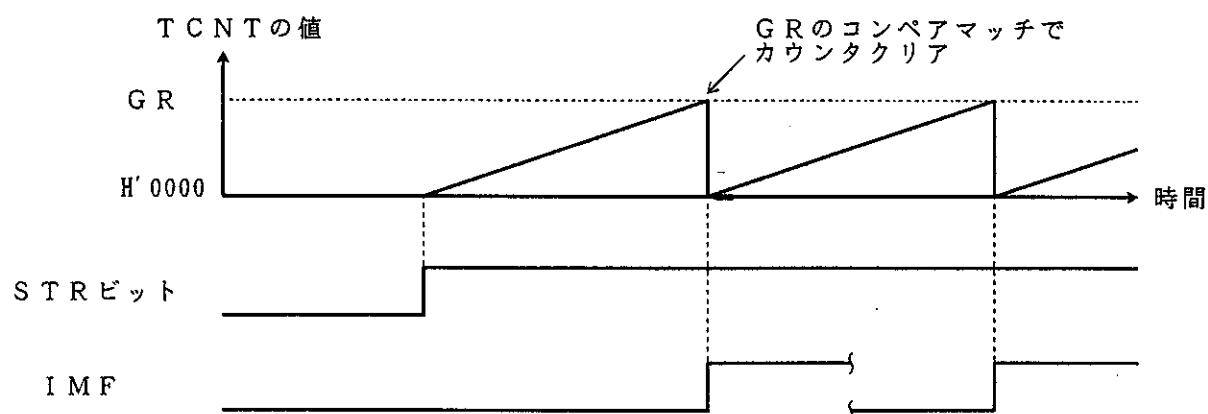

T C N T のクリア要因にコンペアマッチを選択したときは、当該チャネルのT C N Tは周期カウント動作を行います（周期設定用のG R AまたはG R Bをアウトプットコンペアレジスタに設定し、T C RのC C L R 1、C C L R 0ビットにより、コンペアマッチによるカウンタクリアを選択します）。設定後、T S T Rの対応するビットを“1”にセットすると周期カウンタとしてアップカウント動作を開始します。カウント値がG R A/G R Bの値と一致するとT S RのI M F A/I M F Bフラグが“1”にセットされ、T C N TはH'0000にクリアされます。

このとき、対応するT I E RのI M I E A/I M I E Bビットが“1”ならば、C P Uに割込みを要求します。T C N Tはコンペアマッチ後、H'0000から再びアップカウント動作を継続します。

周期カウンタの動作を図10.16に示します。

図10.16 周期カウンタの動作

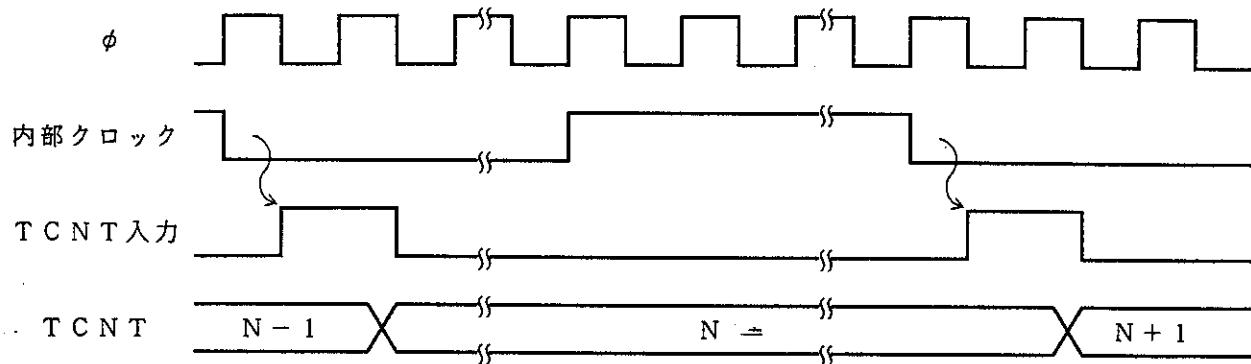

### (c) T C N T のカウントタイミング

#### ①内部クロック動作の場合

T C R の T P S C 2 ~ T P S C 0 ビットにより、システムクロック ( $\phi$ ) またはシステムクロックを周囲した 3 種類のクロック ( $\phi/2$ 、 $\phi/4$ 、 $\phi/8$ ) が選択できます。

このときのタイミングを図 10.17 に示します。

図 10.17 内部クロック動作時のカウントタイミング

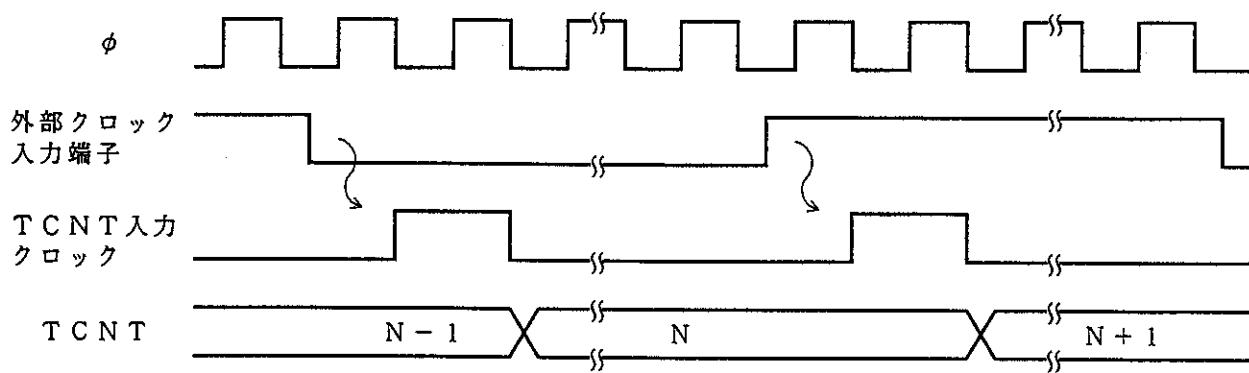

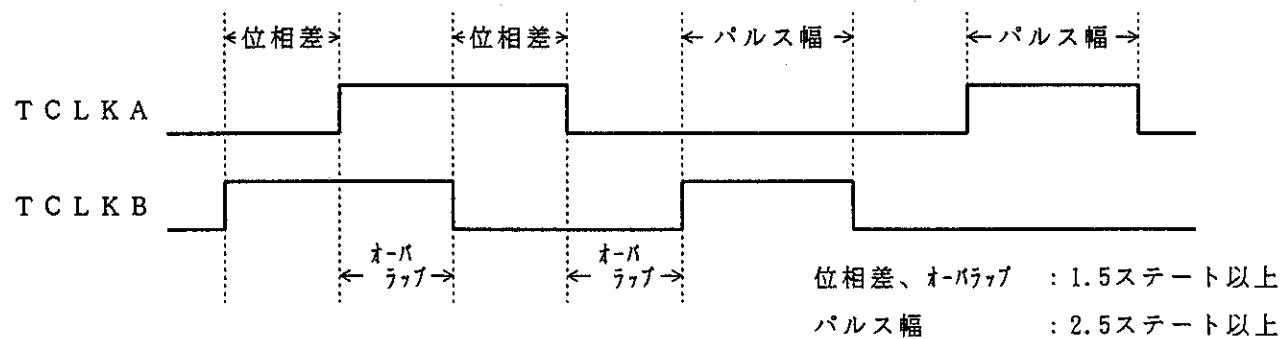

#### ②外部クロック動作の場合

T C R の T P S C 2 ~ T P S C 0 ビットにより外部クロック入力端子 (TCLKA~TCLKD) を、また CKEG1、CKEG0 ビットにより検出エッジを選択できます。外部クロックの検出は、立上がりエッジ／立下がりエッジ／両エッジの選択が可能です。

なお、外部クロックのパルス幅は、単エッジの場合は 1.5 システムクロック以上、両エッジの場合は 2.5 システムクロック以上必要です。これ以下のパルス幅では正しく動作しませんので注意してください。

立上がり／立下がりの両エッジ検出時のタイミングを図 10.18 に示します。

図 10.18 外部クロック動作時のカウントタイミング（両エッジ検出の場合）

(2) コンペアマッチによる波形出力機能

I T Uチャネル0、1、3、4は、コンペアマッチA、-Bにより対応するTIOCA、TIOCB端子から0出力／1出力／トグル出力を行うことができます。

チャネル2は0出力／1出力のみ可能です。

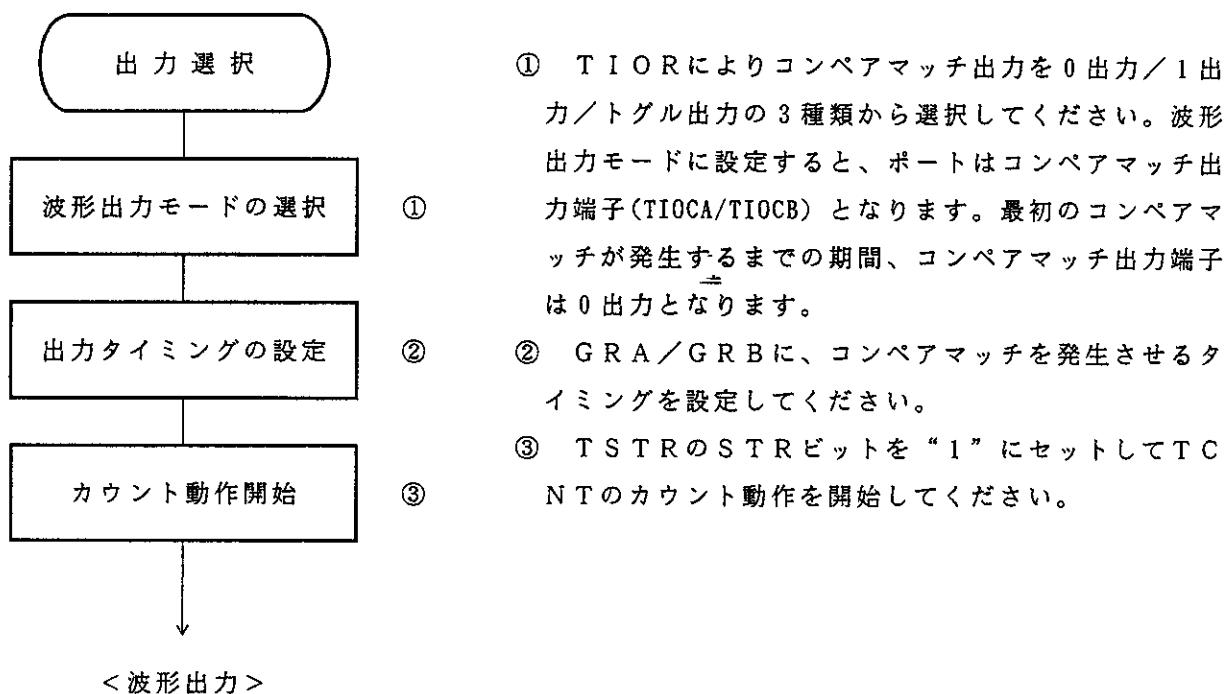

(a) コンペアマッチによる波形出力動作の設定手順例

コンペアマッチによる波形出力動作の設定手順例を図10.19に示します。

図10.19 コンペアマッチによる波形出力動作例

(b) 波形出力動作例

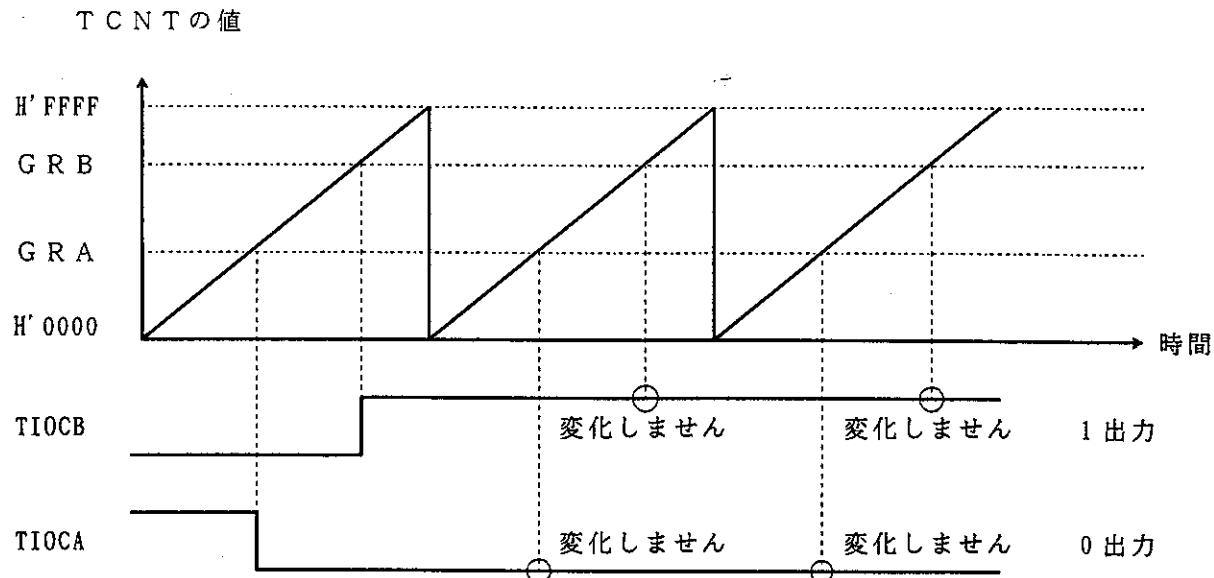

0出力／1出力の例を図10.20に示します。

T C N Tをフリーランニングカウント動作、またコンペアマッチAにより0出力、コンペアマッチBにより1出力となるように設定した場合の例です。設定したレベルと端子のレベルが一致した場合には、端子のレベルは変化しません。

図10.20 0出力、1出力の動作例

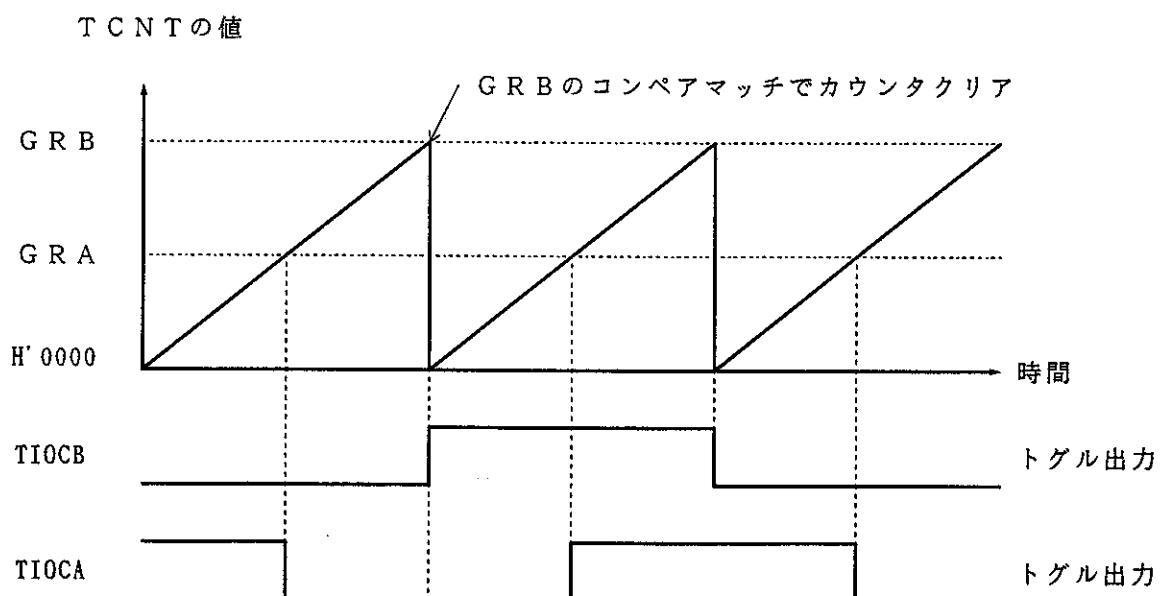

トグル出力の例を図10.21に示します。

T C N T を周期カウント動作（コンペアマッチBでカウンタクリア）に、コンペアマッチA、Bともトグル出力となるように設定した場合の例です。

図10.21 トグル出力の動作例

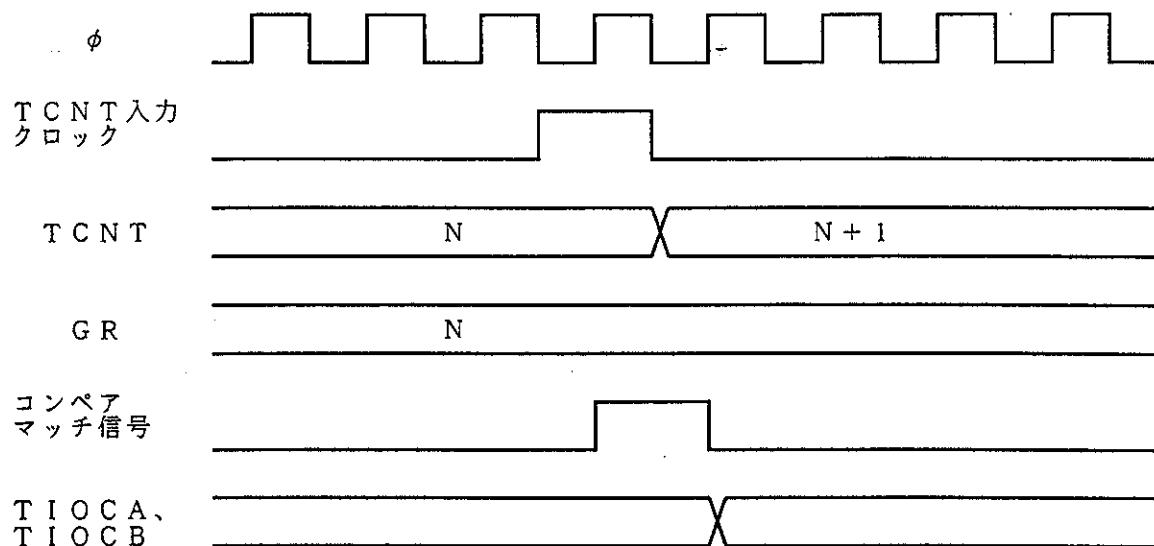

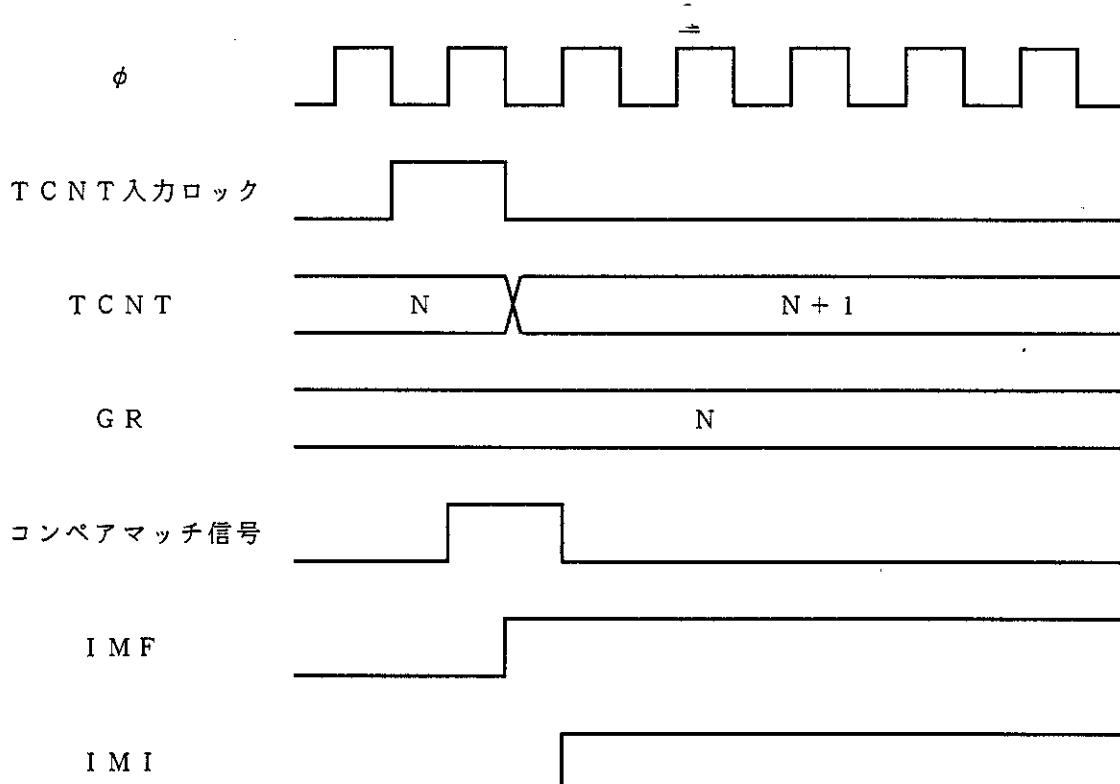

### (c) アウトプットコンペア出力タイミング

コンペアマッチ信号は、T C N T と G R が一致した最後のステート（T C N T が一致したカウント値を更新するタイミング）で発生します。コンペアマッチ信号が発生したとき、T I O R で設定される出力値がアウトプットコンペア出力端子(TIOCA、TIOCB)に出力されます。T C N T と G R が一致した後、T C N T 入力クロックが発生するまでコンペアマッチ信号は発生しません。

アウトプットコンペア出力タイミングを図10.22に示します。

図10.22 アウトプットコンペア出力タイミング

### (3) インプットキャプチャ機能

インプットキャプチャ／アウトプットコンペア端子(TIOCA、TIOCB)の入力エッジを検出して T C N T の値を G R に転送することができます。検出エッジは立上がりエッジ／立下がりエッジ／両エッジから選択できます。

インプットキャプチャ機能を利用することで、パルス幅や周期の測定を行うことができます。

#### (a) インプットキャプチャ動作の設定手順例

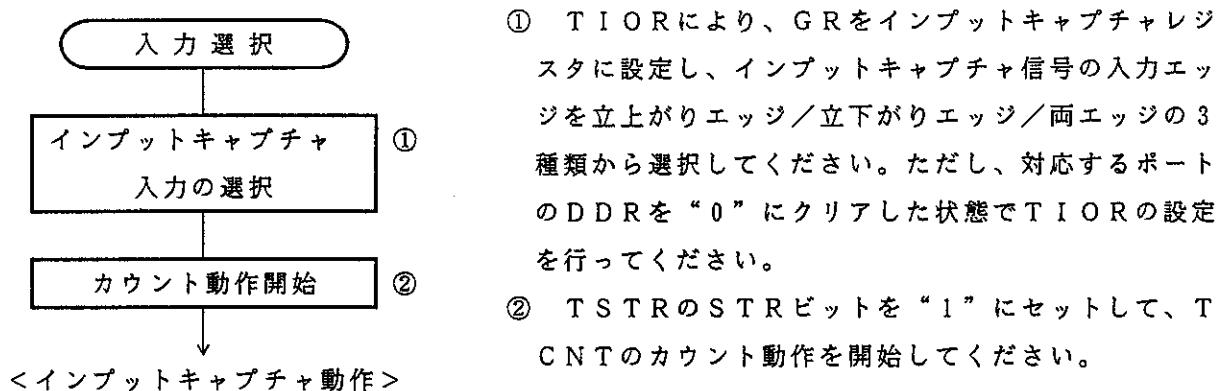

インプットキャプチャ動作の設定手順例を図10.23に示します。

図10.23 インプットキャプチャ動作の設定手順例

(b) インプットキャプチャ動作例

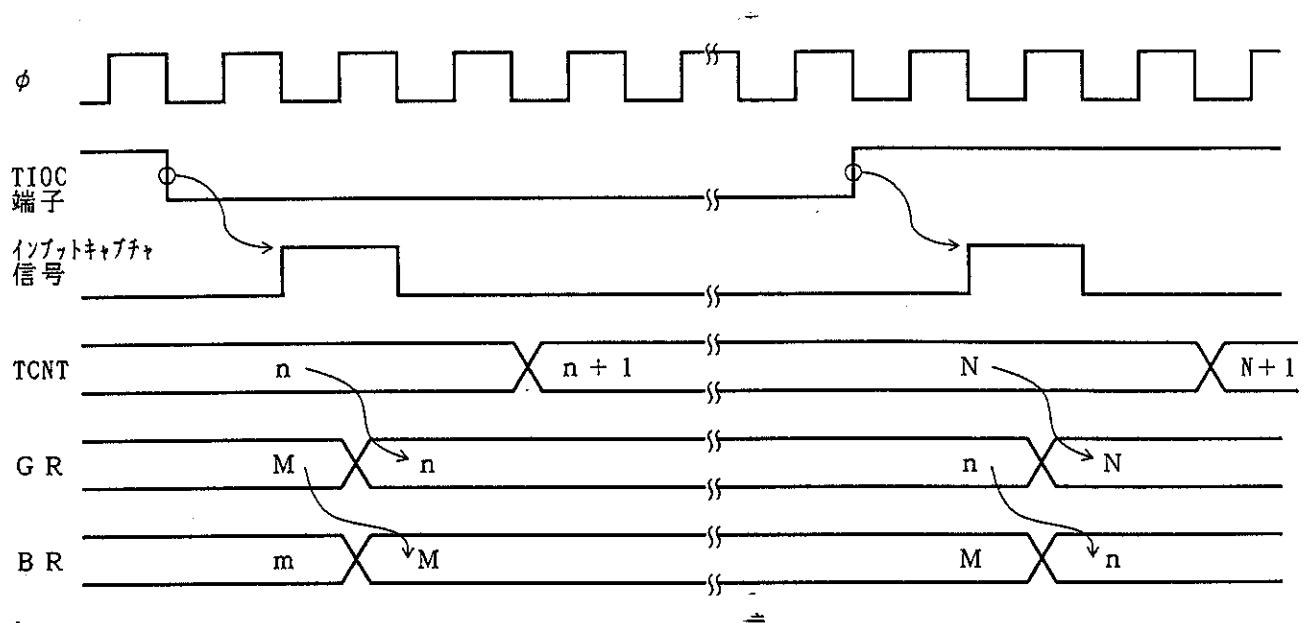

インプットキャプチャ動作例を図10.24に示します。

TIOCA端子のインプットキャプチャ入力エッジは立上がり／立下がりの両エッジ、またTIOCB端子のインプットキャプチャ入力エッジは立下がりエッジを選択し、TCNTはGRBのインプットキャプチャでカウンタクリアされるように設定した場合の例です。

図10.24 インプットキャプチャ動作例

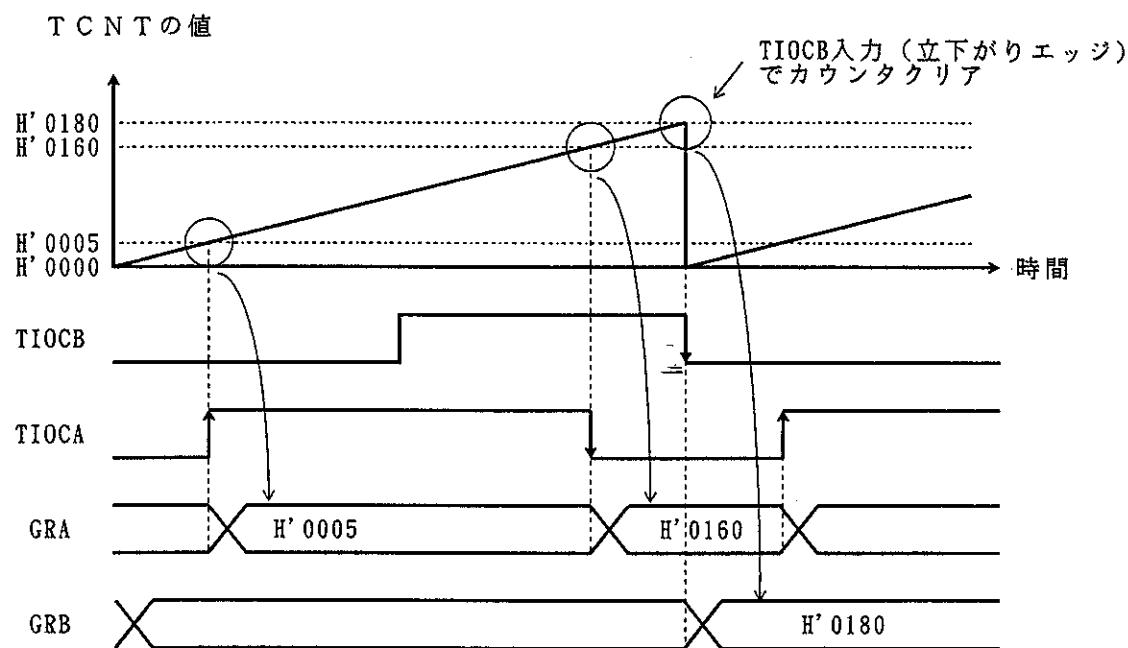

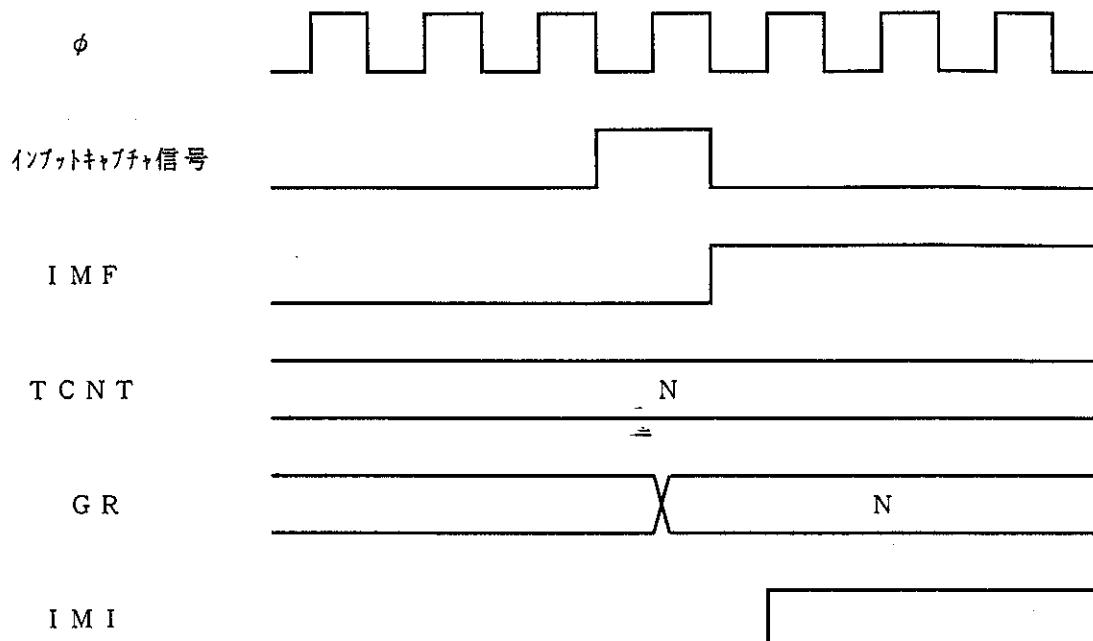

(c) インプットキャプチャ信号タイミング

インプットキャプチャ入力は、T I O Rの設定により立上がりエッジ／立下がりエッジ／両エッジの選択ができます。

立上がりエッジを選択した場合のタイミングを図10.25に示します。

インプットキャプチャ入力信号のパルス幅は、単エッジの場合は1.5システムクロック以上、両エッジの場合は2.5システムクロック以上必要です。

図10.25 インプットキャプチャ入力信号タイミング

### 10.4.3 同期動作

同期動作は、複数の T C N T の値を同時に書き換えることができます（同期プリセット）。また、T C R の設定により複数の T C N T を同時にクリアすることができます（同期クリア）。

同期動作により、1つのタイムベースに対してジェネラルレジスタを増加することができます。チャネル 0～4 はすべて同期動作の設定が可能です。

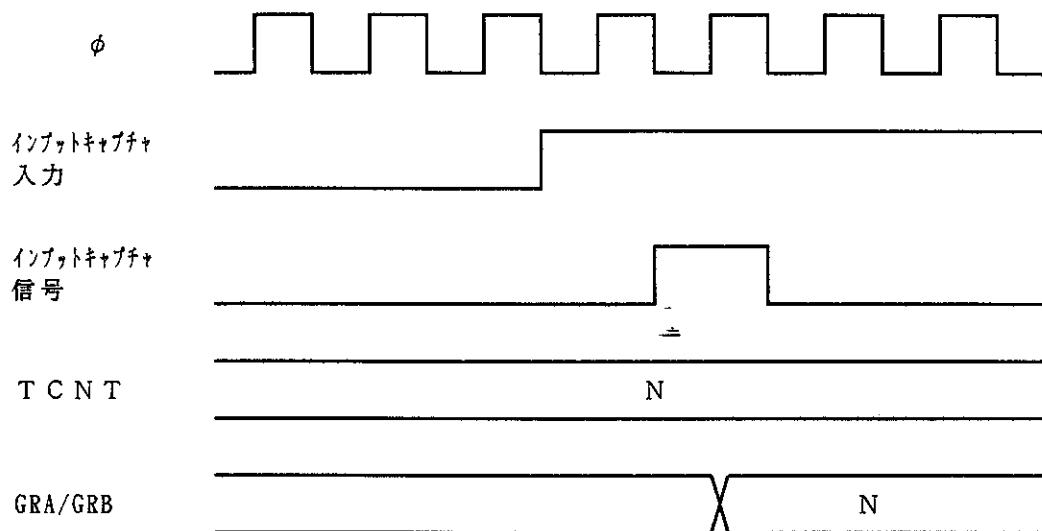

#### (1) 同期動作の設定手順例

同期動作の設定手順例を図10.26に示します。

- ① 同期動作に設定するチャネルに対応した T S N C の S Y N C ビットを “1” にセットしてください。

- ② 同期動作に設定したチャネルのいずれかの T C N T にライトすると、他の T C N T にも同じ値が同時にライトされます。

- ③ T C R の C C L R 1、C C L R 0 ビットにより、コンペアマッチ／インプットキャプチャでカウンタクリアするように設定してください。

- ④ T C R の C C L R 1、C C L R 0 ビットにより、カウンタクリア要因を同期クリアに設定してください。

- ⑤ T S T R の S T R ビットを “1” にセットして、T C N T のカウント動作を開始してください。

図10.26 同期モードの設定手順例

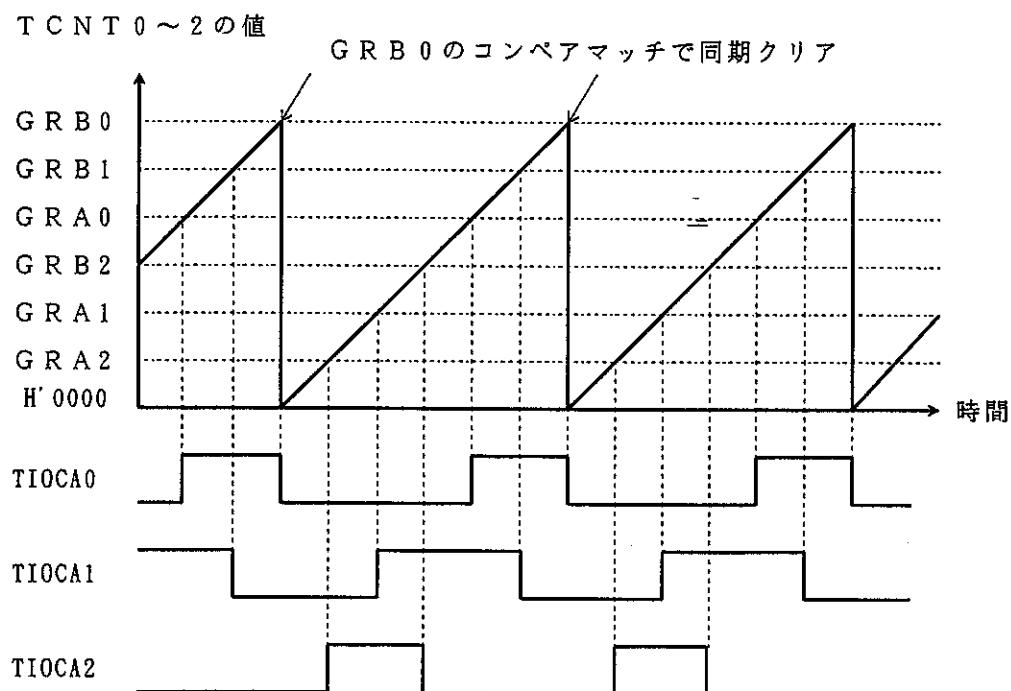

## (2) 同期動作例

同期動作例を図10.27に示します。

チャネル0～2を同期動作かつPWMモードに設定し、チャネル0のカウンタクリア要因をGRB0のコンペアマッチ、またチャネル1、2のカウンタクリア要因を同期クリアに設定した場合の例です。

このとき、チャネル0～2のTCNTは同期プリセット、GRB0のコンペアマッチによる同期クリア動作を行い、3相のPWM波形をTIOCA0、TIOCA1、TIOCA2端子から出力します。

PWMモードについては「10.4.4 PWMモード」を参照してください。

図10.27 同期動作例

#### 10.4.4 PWMモード

PWMモードはGRAとGRBをペアで使用し、TIOCA出力端子よりPWM波形を出力します。GRAにはPWM波形の1出力タイミングを設定し、GRBにはPWM波形の0出力タイミングを設定します。

GRAとGRBのいずれかのコンペアマッチをTCNTのカウンタクリア要因とすることにより、デューティ0～100%のPWM波形をTIOCA端子より出力することができます。チャネル0～4はすべてPWMモードの設定が可能です。

PWM出力端子とレジスタの対応を表10.4に示します。GRAとGRBの設定値が同一の場合、コンペアマッチが発生しても出力値は変化しません。

表10.4 PWM出力端子とレジスタの組み合わせ

| チャネル | 出力端子   | 1出力   | 0出力   |

|------|--------|-------|-------|

| 0    | TIOCA0 | GRA 0 | GRB 0 |

| 1    | TIOCA1 | GRA 1 | GRB 1 |

| 2    | TIOCA2 | GRA 2 | GRB 2 |

| 3    | TIOCA3 | GRA 3 | GRB 3 |

| 4    | TIOCA4 | GRA 4 | GRB 4 |

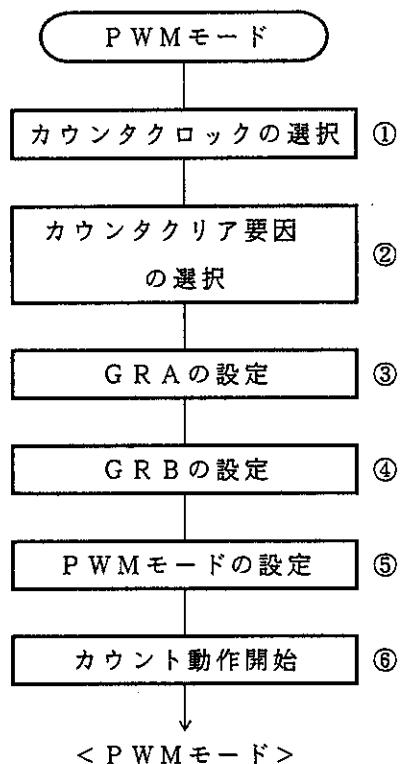

### (1) PWMモードの設定手順例

PWMモードの設定手順例を図10.28に示します。

- ① TCRのTPSC2～TPSC0ビットでカウンタクロックを選択してください。外部クロックを選択した場合は、TCRのCKEG1、CKEG0ビットにより外部クロックのエッジを選択してください。

- ② TCRのCCLR1、CCLR0ビットによりカウンタクリア要因を選択してください。

- ③ GRAに出力PWM波形の1出力タイミングを設定してください。

- ④ GRBに出力PWM波形の0出力タイミングを設定してください。

- ⑤ TMDRのPWMビットでPWMモードを設定してください。PWMモードを設定すると、TIORの内容にかかわらずGRA/GRBは、PWM出力波形の1出力/0出力タイミング設定用アウトプットコンペアレジスタとなります。TI0CA端子は自動的にPWM出力端子となります。ただし、TI0CB端子は、TIORのIOB1、IOB0ビットの設定に従います。TI0CB端子を出力しない場合は、IOB1、IOB0をいずれも“0”にクリアしてください。

- ⑥ TSTRのSTRビットを“1”にセットして、TCNTのカウント動作を開始してください。

図10.28 PWMモードの設定手順例

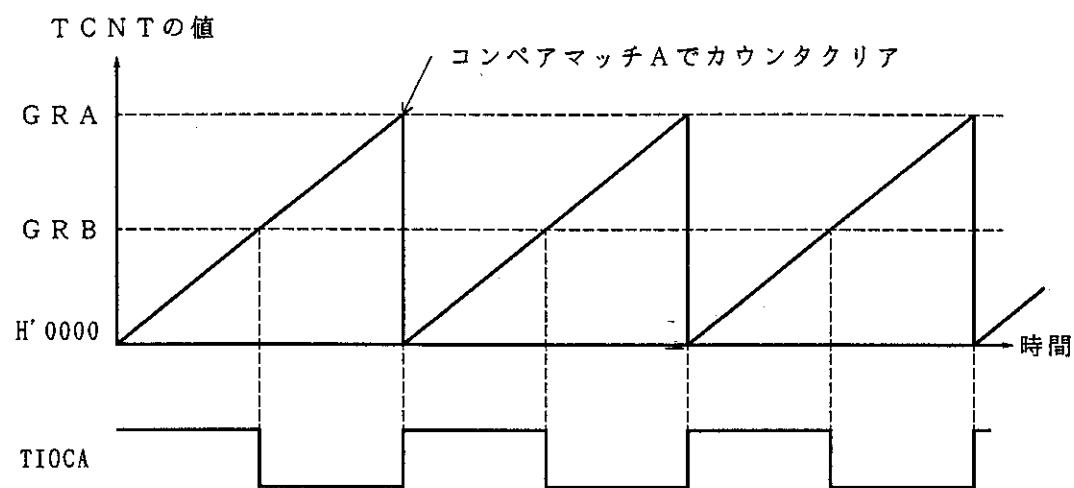

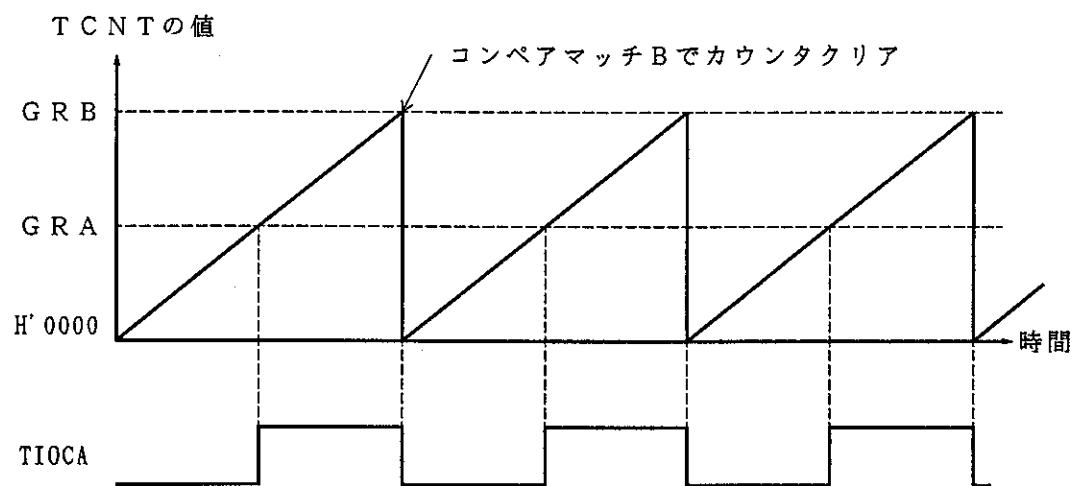

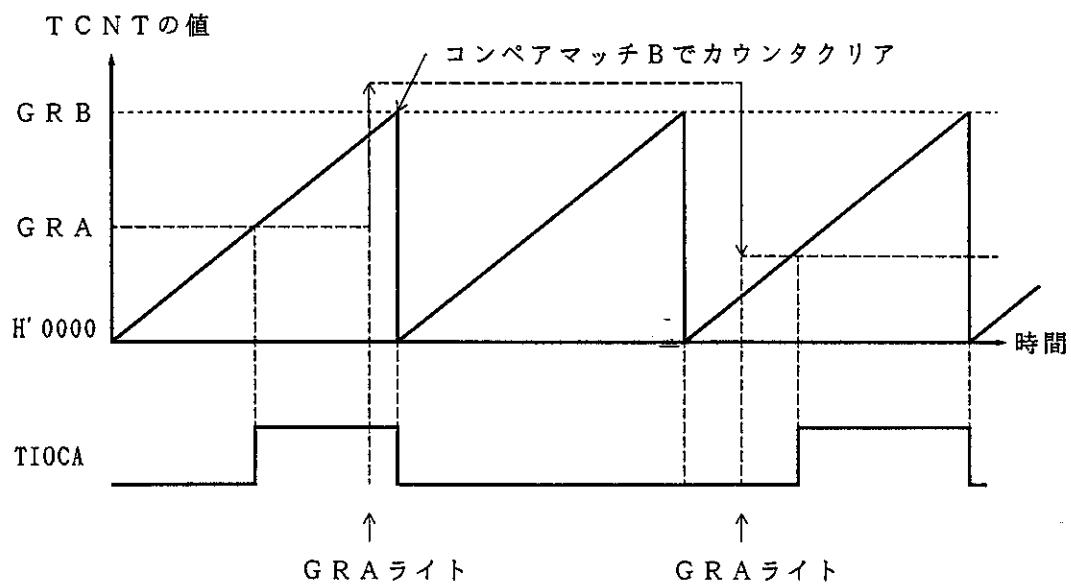

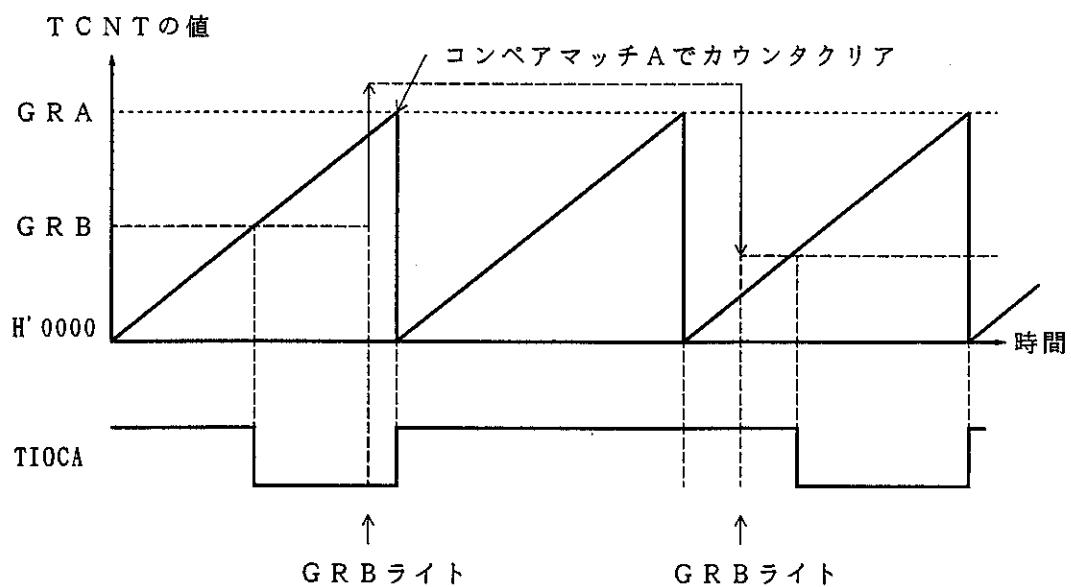

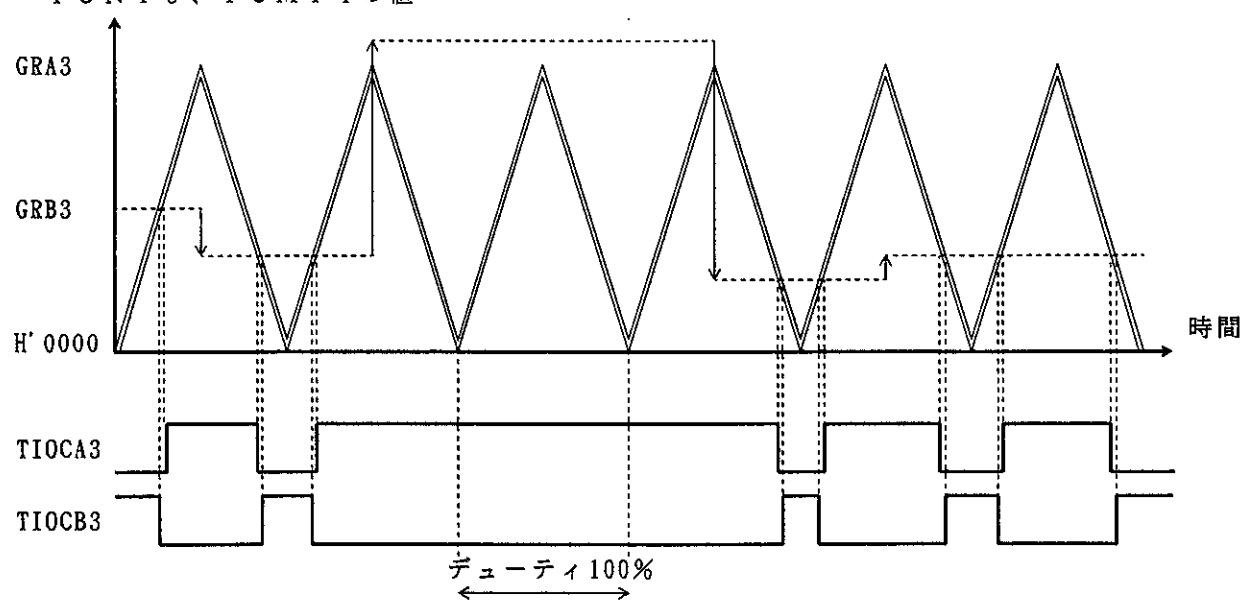

## (2) PWMモードの動作例

PWMモードの動作例を図10.29に示します。

PWMモードに設定するとTIOCA端子は出力端子となり、GRAのコンペアマッチで1出力、GRBのコンペアマッチで0出力となります。

TCNTのカウンタクリア要因をGRA、GRBのコンペアマッチとした場合の例です。同期動作またはフリーランニングカウント動作も使用できます。

(a) GRAでカウンタクリア

(b) GRBでカウンタクリア

図10.29 PWMモードの動作例(1)

PWMモードで、デューティ0%、デューティ100%のPWM波形を出力する例を図10.30に示します。

カウンタクリア要因をGRBのコンペアマッチに設定し、GRAの設定値>GRBの設定値としたとき、PWM波形はデューティ0%となります。また、カウンタクリア要因をGRAのコンペアマッチに設定し、GRBの設定値>GRAの設定値としたときPWM波形はデューティ100%となります。

(a) デューティ0%の場合

(b) デューティ100%の場合

図10.30 PWMモードの動作例(2)

#### 10.4.5 リセット同期 PWMモード

リセット同期 PWMモードは、チャネル3、4を組み合わせることにより、一方の波形変化点が共通の関係となる PWM波形（正相と逆相）を3相出力します。

リセット同期 PWMモードに設定すると、TIOCA3、TIOCB3、TIOCA4、TOCXA4、およびTIOCB4、TOCXB4端子は自動的に PWM出力端子となり、TCNT3はアップカウンタとして機能します。

使用される PWM出力端子を表10.5に、使用するレジスタの設定を表10.6に示します。

表10.5 リセット同期 PWMモード時の出力端子

| チャネル | 出力端子   | 説明                    |

|------|--------|-----------------------|

| 3    | TIOCA3 | PWM出力1                |

|      | TIOCB3 | PWM出力1' (PWM出力1の逆相波形) |

| 4    | TIOCA4 | PWM出力2                |

|      | TOCXA4 | PWM出力2' (PWM出力2の逆相波形) |

|      | TIOCB4 | PWM出力3                |

|      | TOCXB4 | PWM出力3' (PWM出力3の逆相波形) |

表10.6 リセット同期 PWMモード時のレジスタ設定

| レジスタ  | 設定内容                                |

|-------|-------------------------------------|

| TCNT3 | H'0000を初期設定                         |

| TCNT4 | 使用しません（独立に動作）                       |

| GRA3  | TCNT3のカウント周期を設定                     |

| GRB3  | TIOCA3、TIOCB3端子より出力される PWM波形の変化点を設定 |

| GRA4  | TIOCA4、TOCXA4端子より出力される PWM波形の変化点を設定 |

| GRB4  | TIOCB4、TOCXB4端子より出力される PWM波形の変化点を設定 |

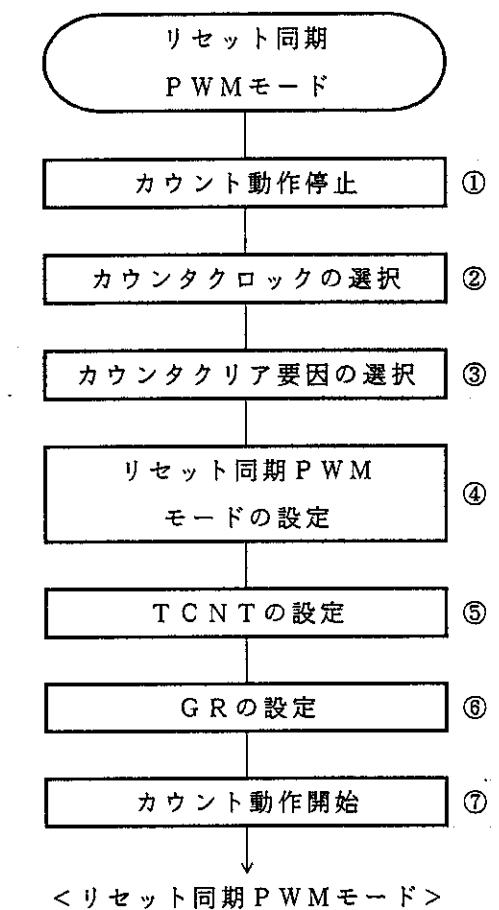

(1) リセット同期 PWMモードの設定手順例

リセット同期 PWMモードの設定手順を図10.31に示します。

- ① TSTRのSTR3ビットを“0”にクリアし、TCNT3のカウント動作を停止してください。リセット同期 PWMモードの設定は、TCNT3が停止した状態で行ってください。

- ② TCRのTPSC2～TPSC0ビットでチャネル3のカウンタクロックを選択してください。外部クロックを選択した場合は、TCRのCKEG1、CKEG0ビットで外部クロックのエッジを選択してください。

- ③ TCR3のCCLR1、CCLR0ビットでカウンタクリア要因をGRA3のコンペアマッチに設定してください。

- ④ TFCRのCMD1、CMD0ビットでリセット同期 PWMモードを設定してください。

TIOCA3、TIOCB3、TIOCA4、TIOCB4、TOCXA4、TOCXB4端子は自動的にPWM出力端子となります。

- ⑤ TCNT3は、H'0000としてください。TCNT4は、設定する必要はありません。

- ⑥ GRA3は周期レジスタです。GRA3には、周期を設定してください。GRB3、GRA4、GRB4には、PWM出力波形変化タイミングを設定してください。ただし、設定値は、TCNT3とコンペアマッチする範囲で設定してください。

$X \leq GRA3$  (X : 設定値)

- ⑦ TSTRのSTR3ビットを“1”にセットして、TCNT3のカウント動作を開始してください。

図10.31 リセット同期 PWMモードの設定手順例

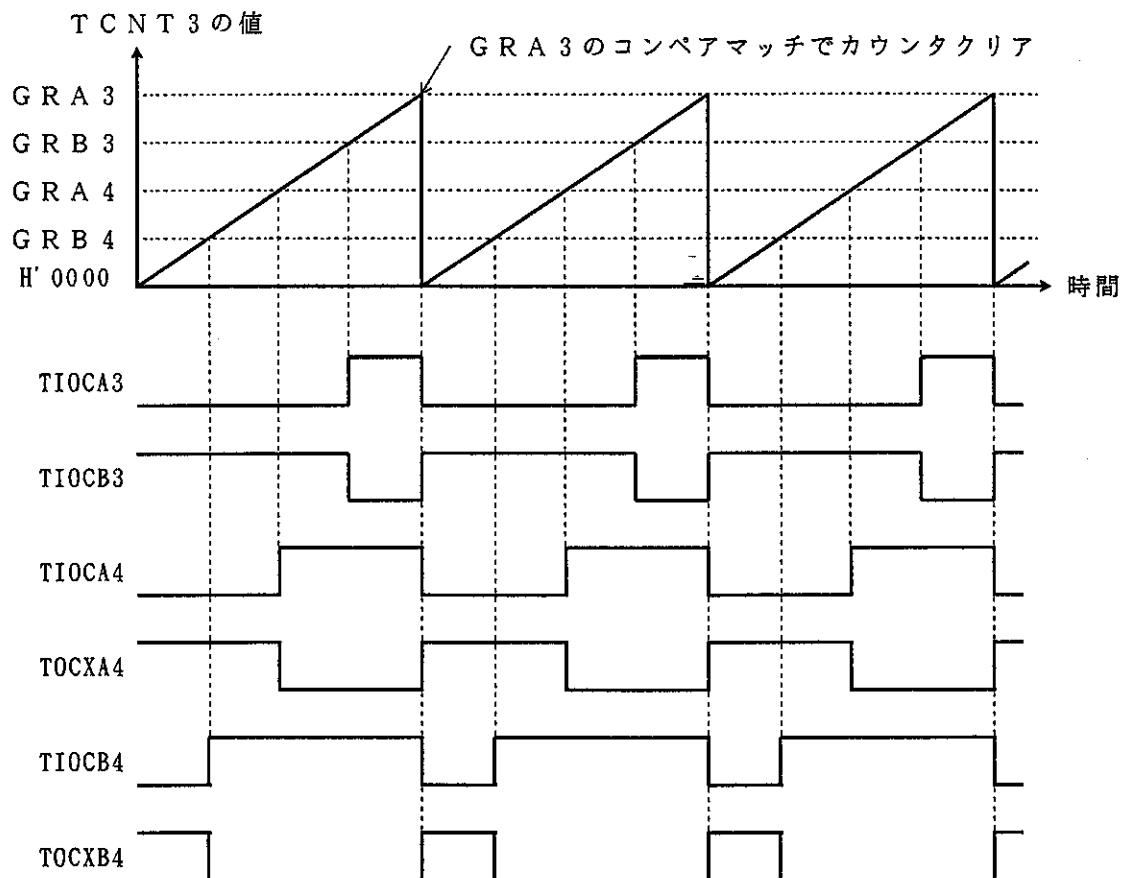

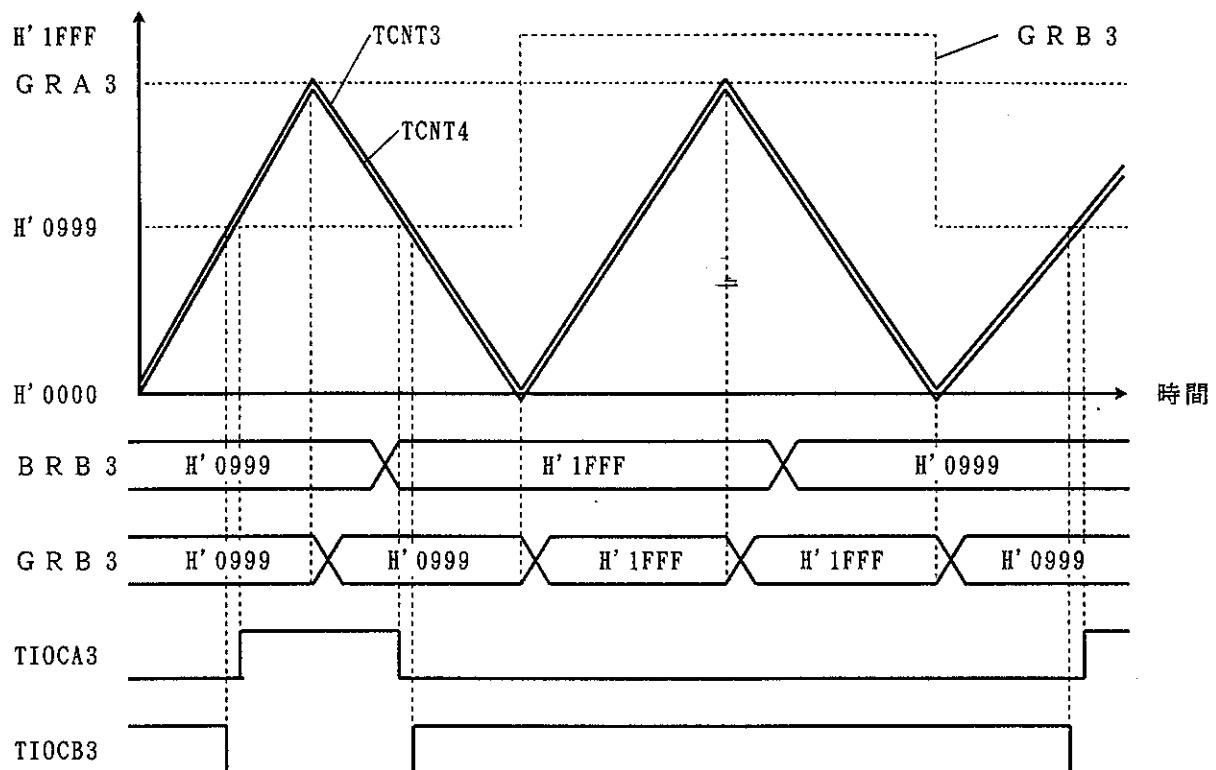

## (2) リセット同期 PWMモードの動作例

リセット同期 PWMモードの動作例を図10.32に示します。

リセット同期 PWMモードでは、TCNT3はアップカウンタとして動作します。TCNT4は独立動作します。ただし、GRA4、GRB4はTCNT4から切り離されます。TCNT3がGRA3とコンペアマッチするとカウンタはクリアされ、H'0000からカウントアップを再開します。

PWM出力端子は、それぞれGRB3、GRA4、GRB4とTCNT3のコンペアマッチおよびカウンタクリアが発生するたびにトグル出力を行います。

図10.32 リセット同期 PWMモードの動作例（OL S3 = OL S4 = 1の場合）

リセット同期 PWMモードとバッファ動作を同時に設定した場合の動作については、「10.4.8 バッファ動作」を参照してください。

#### 10.4.6 相補 PWM モード

相補 PWM モードは、チャネル 3、4 を組み合わせることにより、正相と逆相がノンオーバラップの関係にある PWM 波形を 3 相出力します。

相補 PWM モードに設定すると、TIOCA3、TIOCB3、TIOCA4、TOCXA4、および TIOCB4、TOCXB4 端子は自動的に PWM 出力端子となり、TCNT3 と TCNT4 はアップ／ダウンカウンタとして機能します。

使用される PWM 出力端子を表 10.7 に、使用するレジスタの設定を表 10.8 に示します。

表 10.7 相補 PWM モード時の出力端子

| チャネル | 出力端子   | 説明                                         |

|------|--------|--------------------------------------------|

| 3    | TIOCA3 | PWM 出力 1                                   |

|      | TIOCB3 | PWM 出力 1<br>(PWM 出力 1 とノンオーバラップの関係にある逆相波形) |

| 4    | TIOCA4 | PWM 出力 2                                   |

|      | TOCXA4 | PWM 出力 2<br>(PWM 出力 2 とノンオーバラップの関係にある逆相波形) |

|      | TIOCB4 | PWM 出力 3                                   |

|      | TOCXB4 | PWM 出力 3<br>(PWM 出力 3 とノンオーバラップの関係にある逆相波形) |

表 10.8 相補 PWM モード時のレジスタ設定

| レジスタ  | 設定内容                                        |

|-------|---------------------------------------------|

| TCNT3 | ノンオーバラップ期間を初期設定 (TCNT4 との差がノンオーバラップ期間となります) |

| TCNT4 | H'0000 を初期設定                                |

| GRA3  | TCNT3 の上限値 - 1 を設定                          |

| GRB3  | TIOCA3、TIOCB3 端子より出力される PWM 波形の変化点を設定       |

| GRA4  | TI0CA4、TOCXA4 端子より出力される PWM 波形の変化点を設定       |

| GRB4  | TIOCB4、TOCXB4 端子より出力される PWM 波形の変化点を設定       |

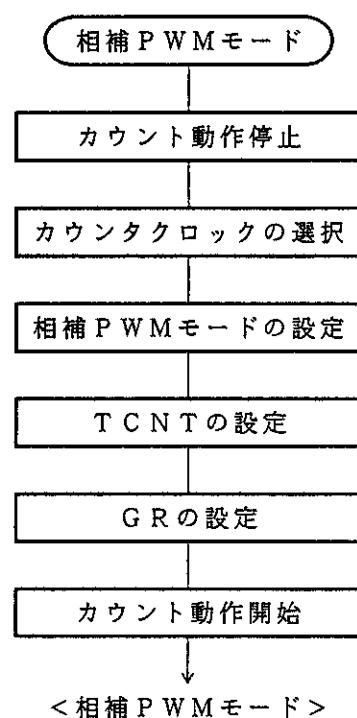

(1) 相補 PWM モードの設定手順

相補 PWM モードの設定手順例を図10.33に示します。

- ① TSTR の STR3、STR4 ビットを “0” にクリアし TCNT のカウント動作を停止してください。

相補 PWM モードの設定は、TCNT3、TCNT4 が停止した状態で行ってください。

- ② TCR の TPSCL2～TPSCH0 ビットでチャネル 3、4 に同一カウンタクロックを選択してください。

外部クロックを選択した場合は、TCR の CKEG1、CKEG0 ビットで外部クロックのエッジを選択してください。TCR の CCLR1、CCLR0 ビットでカウンタクリアは選択しないでください。

- ③ TFCR の CMD1、CMD0 ビットで相補 PWM モードを設定してください。TIOCA3、TIOCB3、TIOCA4、TIOCB4、TOCXA4、TOCXB4 端子は自動的に PWM 出力端子となります。

- ④ TCNT4 は、H'0000 としてください。TCNT3 は、ノンオーバラップ期間を設定してください。

TCNT3 と TCNT4 に同じ値を設定しないでください。

- ⑤ GRA3 は周期レジスタです。GRA3 には、TCNT3 の上限値 - 1 を設定してください。GRB3、GRA4、GRB4 には、PWM 出力波形変化タイミングを設定してください。ただし、設定値は、TCNT3 と TCNT4 がコンペアマッチする範囲で設定してください。

$T \leq X$  ( $X : GRB3, GRA4, GRB4$  の初期設定値、 $T : TCNT3$  の初期設定値)

- ⑥ TSTR の STR3、STR4 ビットを “1” にセットして、TCNT3、TCNT4 のカウント動作を開始してください。

【注】 相補 PWM モードを途中で解除した後、再び相補 PWM モードを開始したい場合、設定手順①から、再設定を行ってください。

図10.33 相補 PWM モードの設定手順例

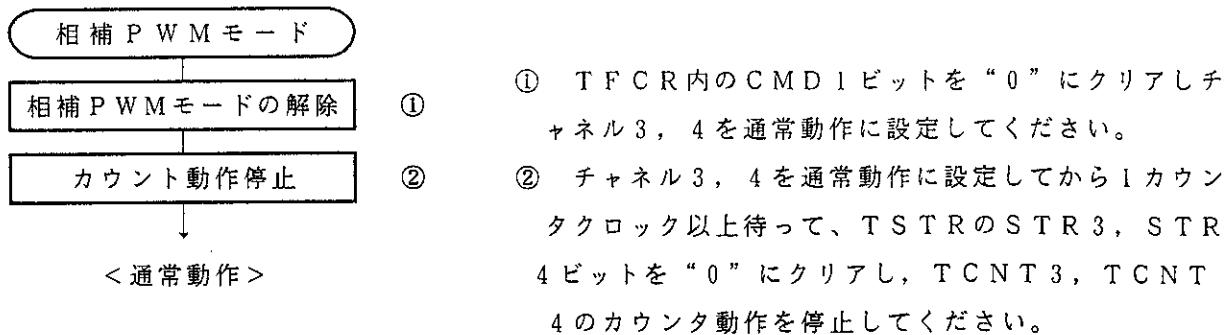

## (2) 相補 PWM モードの解除手順

相補 PWM モードの解除手順を図10.34に示します。

図10.34 相補 PWM モードの解除手順

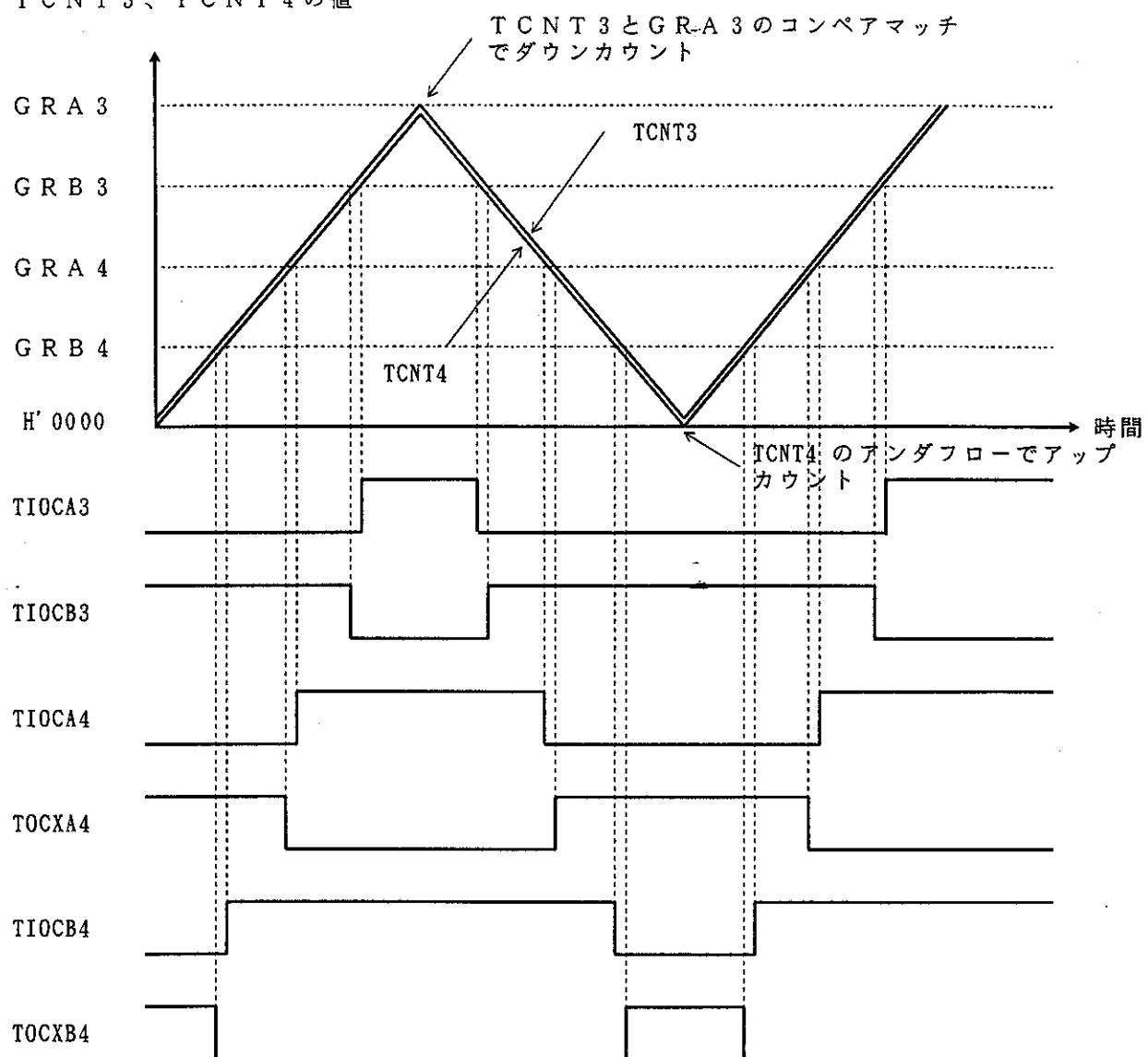

## (3) 相補 PWM モードの動作例

相補 PWM モードの動作例を図10.35に示します。

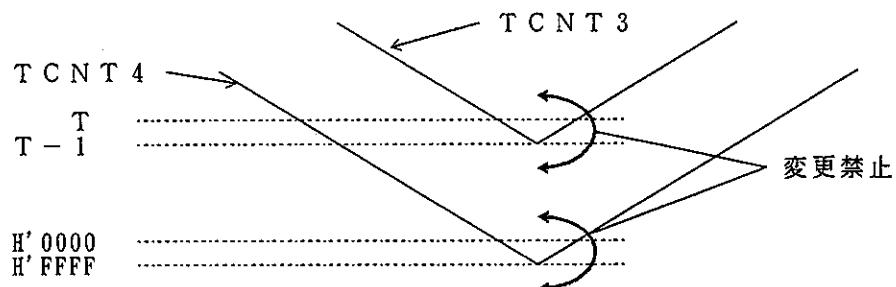

相補 PWM モードでは、TCNT3、TCNT4はアップ／ダウンカウンタとして動作します。TCNT3がGRA3とコンペアマッチするとダウンカウントし、TCNT4がアンダフローするとアップカウントします。

GRB3、GRA4、GRB4はカウンタのアップ／ダウン1周期中、それぞれTCNT3→TCNT4→TCNT4→TCNT3の順にコンペアマッチを行いPWM波形を生成します（本モードでは、TCNT3 > TCNT4に初期設定します）。

T C N T 3、T C N T 4 の値

図10.35 相補PWMモードの動作例(1) (O L S 3 = O L S 4 = 1 の場合)

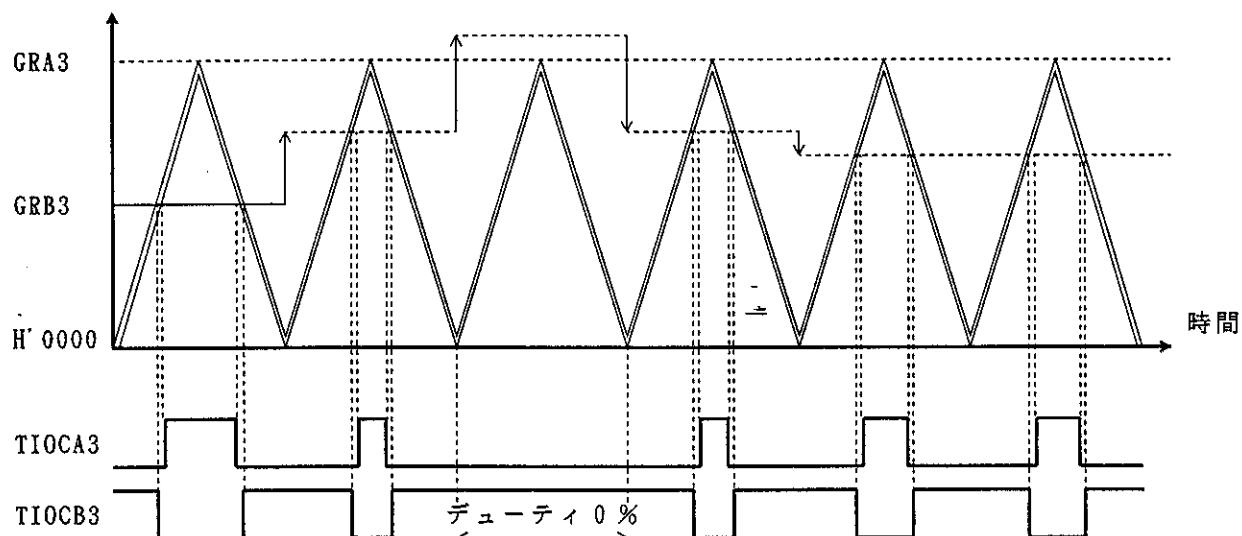

相補 PWM モードで、デューティ 0%、デューティ 100% の PWM 波形を出力する例(1 相分)を図10.36に示します。

本例では G R B 3 のコンペアマッチで端子出力が変化しますので、G R B 3 の値を G R A 3 の値よりも大きい値とすることでデューティ 0%、デューティ 100% の波形出力が可能となります。バッファ動作を併用すると上記操作を含め、動作中のデューティ変更を行なうことができます。

バッファ動作については「10.4.8 バッファ動作」を参照してください。

T C N T 3、T C M T 4 の値

(a) デューティ 0% の場合

T C N T 3、T C M T 4 の値

(b) デューティ 100% の場合

図10.36 相補 PWM モードの動作例(2) (O L S 3 = O L S 4 = 1 の場合)

相補 PWM モードを使用しているときのアップカウント / ダウンカウントの変化点で、T C N T 3、T C N T 4 はそれぞれオーバショート / アンダーショートを発生します。

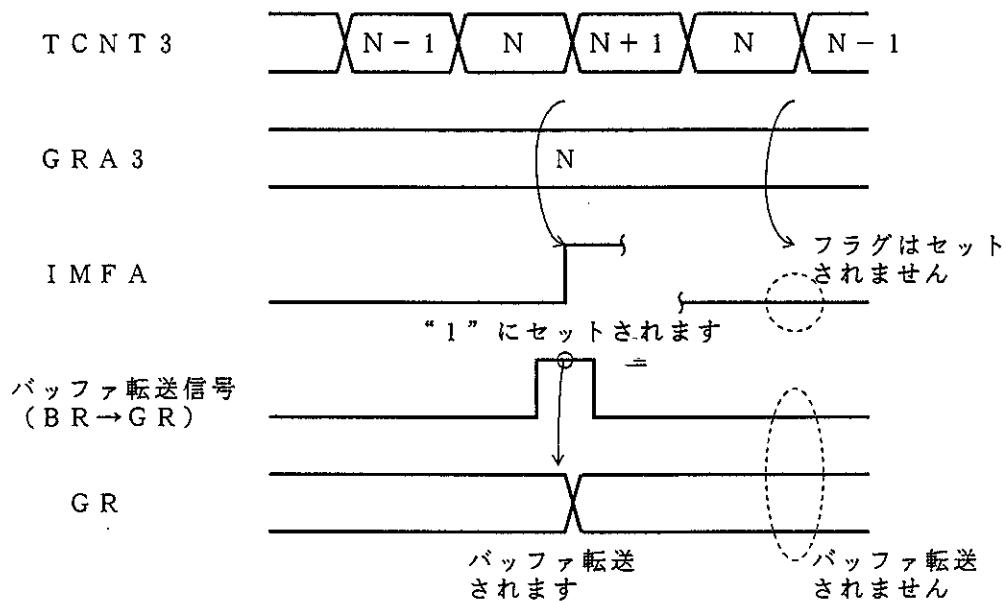

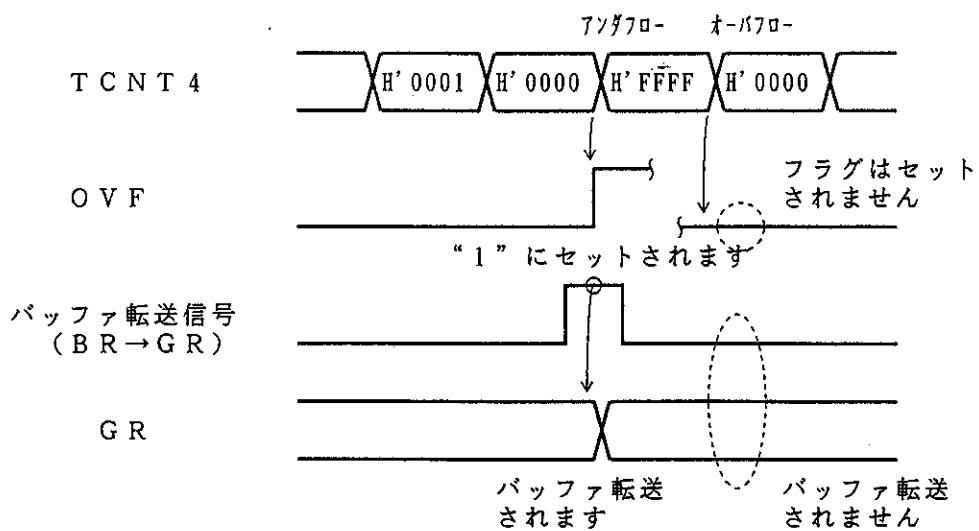

このとき、チャネル 3 の I M F A フラグおよびチャネル 4 の O V F フラグをセットする条件は通常の場合とは異なります。また、バッファ動作での転送条件も異なります。

このタイミングを図10.37、図10.38に示します。

図10.37 オーバショート時のタイミング

図10.38 アンダショート時のタイミング

チャネル3のIMFAフラグはアップカウント時に、チャネル4のOVFフラグはアンダフロー時のみ、それぞれ“1”にセットされます。

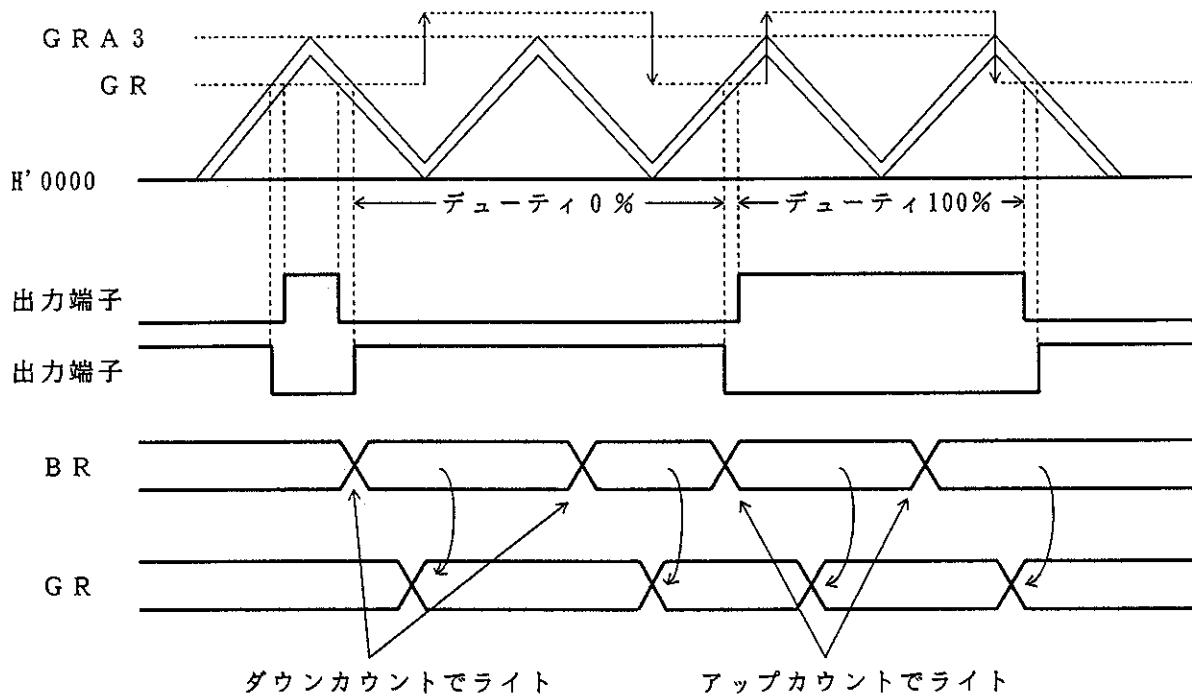

バッファ動作を設定されたBRは、アップカウント動作時のコンペアマッチA3またはTCNT4のアンダフローによってGRに転送されます。

#### (4) 相補 PWM モードでの G R の設定値

相補 PWM モードでの G R の設定および動作中の変更については、以下の点に注意してください。

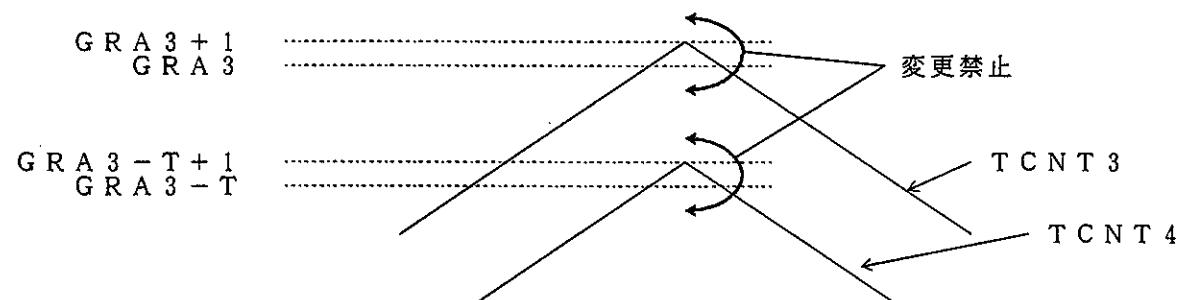

##### ① 初期値

H' 0000～T - 1 (T : T C N T 3 の初期設定値) の設定は禁止です。

なお、カウントスタート後、最初に発生するコンペアマッチ A 3 のタイミング以降では、この設定も可能です。

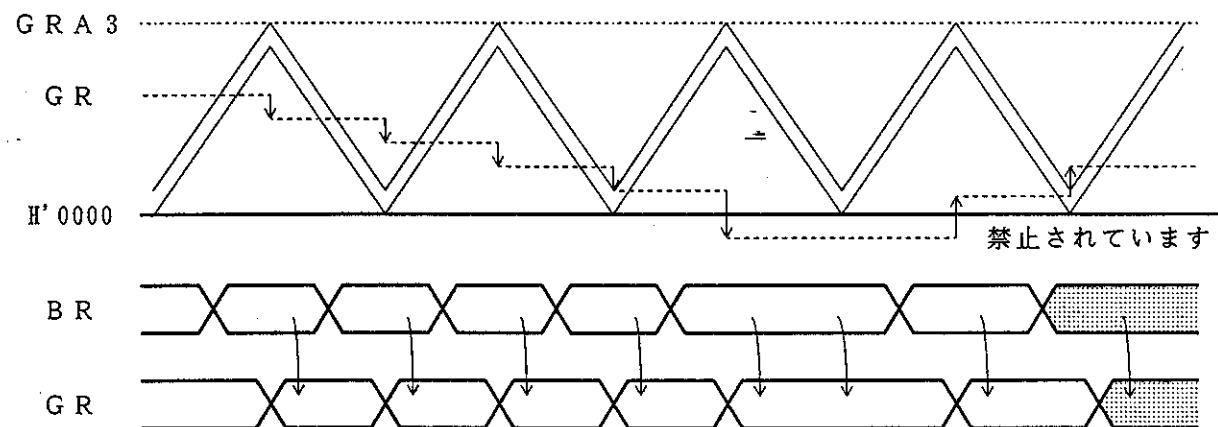

##### ② 設定値の変更方法

バッファ動作を使用してください。直接 G R にライトすると、正しく波形出力されない場合があります。

##### ③ 設定値変更時の注意

図10.39 バッファ動作による G R の設定値変更例(1)

##### (a) アップカウントからダウンカウントへの変化時のバッファ転送