# 9. I/O ポート

## 第9章 目次

|              |     |

|--------------|-----|

| 9.1 概要       | 273 |

| 9.2 ポート1     | 275 |

| 9.2.1 概要     | 275 |

| 9.2.2 レジスタ構成 | 276 |

| 9.3 ポート2     | 278 |

| 9.3.1 概要     | 278 |

| 9.3.2 レジスタ構成 | 278 |

| 9.4 ポート3     | 282 |

| 9.4.1 概要     | 282 |

| 9.4.2 レジスタ構成 | 282 |

| 9.5 ポート4     | 284 |

| 9.5.1 概要     | 284 |

| 9.5.2 レジスタ構成 | 285 |

| 9.6 ポート5     | 288 |

| 9.6.1 概要     | 288 |

| 9.6.2 レジスタ構成 | 288 |

| 9.7 ポート6     | 292 |

| 9.7.1 概要     | 292 |

| 9.7.2 レジスタ構成 | 292 |

| 9.8 ポート7     | 296 |

| 9.8.1 概要     | 296 |

| 9.8.2 レジスタ構成 | 296 |

|               |     |

|---------------|-----|

| 9.9 ポート 8     | 297 |

| 9.9.1 概要      | 297 |

| 9.9.2 レジスタ構成  | 298 |

| 9.10 ポート 9    | 302 |

| 9.10.1 概要     | 302 |

| 9.10.2 レジスタ構成 | 302 |

| 9.11 ポート A    | 306 |

| 9.11.1 概要     | 306 |

| 9.11.2 レジスタ構成 | 308 |

| 9.11.3 端子機能   | 310 |

| 9.12 ポート B    | 315 |

| 9.12.1 概要     | 315 |

| 9.12.2 レジスタ構成 | 317 |

| 9.12.3 端子機能   | 319 |

---

## 9.1 概要

H8/3048シリーズには、10本の入出力ポート（ポート1、2、3、4、5、6、8、9、A、B）と1本の入力専用ポート（ポート7）があります。

ポート機能一覧を表9.1に示します。表9.1に示すように、各ポートは兼用端子になっています。

各ポートは、入出力を制御するデータディレクションレジスタ（DDR）と出力データを格納するデータレジスタ（DR）から構成されています。

DDRとDRのほかに、ポート2、4、5には入力プルアップMOSコントロールレジスタ（PCR）があり、プルアップMOSのオン／オフを制御できます。

ポート1～6、8は1個のTTL負荷と90pFの容量負荷を駆動することができ、ポート9～Bは1個のTTL負荷と30pFの容量負荷を駆動することができます。

また、ポート1～6、8～Bはダーリントントランジスタを駆動することができます。ポート1、2、5、BはLEDを駆動（シンク電流10mA）することができます。また、ポートP8<sub>2</sub>～P8<sub>0</sub>、PA<sub>7</sub>～PA<sub>0</sub>、およびPB<sub>3</sub>～PB<sub>0</sub>はシュミット入力となっています。

各ポートのブロック図は「付録C. I/Oポートブロック図」を参照してください。

表9.1 動作モード別ポート機能一覧

| ポート  | 概要                                                                     | 端子                                                                                                                                                                                                                                                                                                                                               | モード1                                                                                                                                                                                                                      | モード2                                                                                                                                                                                                         | モード3                                                                                                                                                                | モード4                                                                                                                          | モード5                                                                                                                          | モード6                                                                                                                          | モード7                                                              |

|------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| ポート1 | ・8ビットの入出力ポート<br>・LED駆動可能                                               | P1. <sub>1</sub> ~P1. <sub>8</sub> /A <sub>1</sub> ~A <sub>8</sub>                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                           | アドレス出力端子(A <sub>1</sub> ~A <sub>8</sub> )                                                                                                                                                                    |                                                                                                                                                                     |                                                                                                                               | アドレス出力端子(A <sub>1</sub> ~A <sub>8</sub> )と入力ポートの兼用<br>DDR="0"のとき入力ポート<br>DDR="1"のときアドレス出力端子                                   |                                                                                                                               | 入出力ポート                                                            |

| ポート2 | ・8ビットの入出力ポート<br>・ <input type="checkbox"/> MOS内蔵<br>・LED駆動可能           | P2. <sub>1</sub> ~P2. <sub>8</sub> /A <sub>1</sub> ~A <sub>8</sub>                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                           | アドレス出力端子(A <sub>1</sub> ~A <sub>8</sub> )                                                                                                                                                                    |                                                                                                                                                                     |                                                                                                                               | アドレス出力端子(A <sub>1</sub> ~A <sub>8</sub> )と入力ポートの兼用<br>DDR="0"のとき入力ポート<br>DDR="1"のときアドレス出力端子                                   |                                                                                                                               | 入出力ポート                                                            |

| ポート3 | ・8ビットの入出力ポート                                                           | P3. <sub>1</sub> ~P3. <sub>8</sub> /D <sub>1</sub> ~D <sub>8</sub>                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                           | データ入出力端子(D <sub>1</sub> ~D <sub>8</sub> )                                                                                                                                                                    |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | 入出力ポート                                                            |

| ポート4 | ・8ビットの入出力ポート<br>・ <input type="checkbox"/> MOS内蔵                       | P4. <sub>1</sub> ~P4. <sub>8</sub> /D <sub>1</sub> ~D <sub>8</sub>                                                                                                                                                                                                                                                                               | データ入出力端子(D <sub>1</sub> ~D <sub>8</sub> )と8ビットの入出力ポートの兼用<br>8ビットバスモードのとき入出力ポート<br>16ビットバスモードのときデータ入出力端子                                                                                                                   |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | 入出力ポート                                                            |

| ポート5 | ・4ビットの入出力ポート<br>・ <input type="checkbox"/> MOS内蔵<br>・LED駆動可能           | P5. <sub>1</sub> ~P5. <sub>4</sub> /A <sub>1</sub> ~A <sub>4</sub>                                                                                                                                                                                                                                                                               | アドレス出力端子(A <sub>1</sub> ~A <sub>4</sub> )                                                                                                                                                                                 |                                                                                                                                                                                                              | アドレス出力端子(A <sub>1</sub> ~A <sub>4</sub> )と4ビットの入力ポートの兼用<br>DDR="0"のとき入力ポート<br>DDR="1"のときアドレス出力端子                                                                    |                                                                                                                               |                                                                                                                               |                                                                                                                               | 入出力ポート                                                            |

| ポート6 | ・7ビットの入出力ポート                                                           | P6. <sub>1</sub> /INR P6. <sub>1</sub> /INW<br>P6. <sub>1</sub> /RD P6. <sub>1</sub> /RS                                                                                                                                                                                                                                                         | バス制御信号出力端子(INR, INW, RD, RS)                                                                                                                                                                                              |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

|      |                                                                        | P6. <sub>1</sub> /BACK<br>P6. <sub>1</sub> /BREQ<br>P6. <sub>1</sub> /WAIT                                                                                                                                                                                                                                                                       | バス制御信号入出力端子(BACK, BREQ, WAIT)と3ビットの入出力ポートの兼用                                                                                                                                                                              |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | 入出力ポート                                                            |

| ポート7 | ・8ビットの入出力ポート                                                           | P7. <sub>1</sub> /AN <sub>1</sub> /DA <sub>1</sub><br>P7. <sub>1</sub> /AN <sub>8</sub> /DA <sub>8</sub>                                                                                                                                                                                                                                         | A/D変換器のアナログ入力端子(AN <sub>1</sub> , AN <sub>8</sub> )およびD/A変換器のアナログ出力端子(DA <sub>1</sub> , DA <sub>8</sub> )と入力ポートの兼用                                                                                                        |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

|      |                                                                        | P7. <sub>1</sub> ~P7. <sub>8</sub> /AN <sub>1</sub> ~AN <sub>8</sub>                                                                                                                                                                                                                                                                             | A/D変換器のアナログ入力端子(AN <sub>1</sub> ~AN <sub>8</sub> )と入力ポートの兼用                                                                                                                                                               |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

| ポート8 | ・5ビットの入出力ポート<br>・PR <sub>1</sub> ~PR <sub>5</sub> はシミット入力              | P8. <sub>1</sub> /CS <sub>0</sub>                                                                                                                                                                                                                                                                                                                | DDR="0"のとき入力ポート<br>DDR="1"のとき(CS <sub>0</sub> ~CS <sub>4</sub> )出力端子                                                                                                                                                      |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | 入出力ポート                                                            |

|      |                                                                        | P8. <sub>1</sub> /CS <sub>1</sub> /IRQ <sub>1</sub><br>P8. <sub>1</sub> /CS <sub>2</sub> /IRQ <sub>2</sub>                                                                                                                                                                                                                                       | IRQ <sub>1</sub> ~IRQ <sub>5</sub> 入力端子, CS <sub>1</sub> ~CS <sub>4</sub> 出力端子と入力ポートの兼用<br>DDR="0"のとき(CS <sub>0</sub> ~CS <sub>4</sub> )入力ポート                                                                             |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | IRQ <sub>1</sub> ~IRQ <sub>5</sub> 入力端子と入出力ポートの兼用                 |

|      |                                                                        | P8. <sub>1</sub> /CS <sub>3</sub> /IRQ <sub>3</sub>                                                                                                                                                                                                                                                                                              | DDR="1"のときCS <sub>3</sub> ~CS <sub>4</sub> 出力端子                                                                                                                                                                           |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

|      |                                                                        | P8. <sub>1</sub> /RSN/IRQ <sub>4</sub>                                                                                                                                                                                                                                                                                                           | IRQ <sub>4</sub> 入力端子, RSN出力端子と入出力ポートの兼用                                                                                                                                                                                  |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

| ポート9 | ・6ビットの入出力ポート                                                           | P9. <sub>1</sub> /SCK <sub>1</sub> /IRQ <sub>1</sub><br>P9. <sub>1</sub> /SCK <sub>8</sub> /IRQ <sub>8</sub><br>P9. <sub>1</sub> /Rx <sub>D1</sub><br>P9. <sub>1</sub> /Rx <sub>D8</sub><br>P9. <sub>1</sub> /Tx <sub>D1</sub><br>P9. <sub>1</sub> /Tx <sub>D8</sub>                                                                             | シリアルコミュニケーションインターフェースチャネル0, 1(SCIO, 1)の入出力端子(SCK <sub>1</sub> , SCK <sub>8</sub> , Rx <sub>D1</sub> , Rx <sub>D8</sub> , Tx <sub>D1</sub> , Tx <sub>D8</sub> )、およびIRQ <sub>1</sub> , IRQ <sub>8</sub> 入力端子と6ビットの入出力ポートの兼用 |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

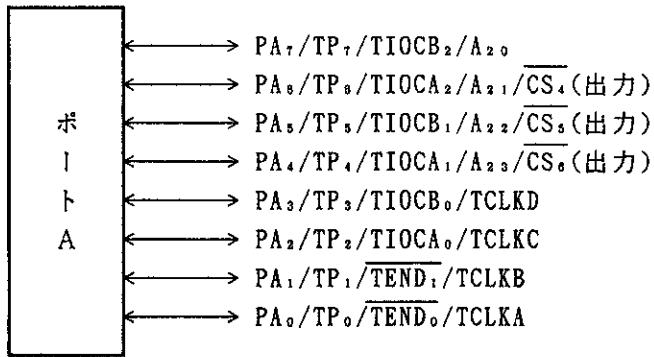

| ポートA | ・8ビットの入出力ポート<br>・シミュット入力                                               | PA. <sub>1</sub> /TP <sub>1</sub> /TIOCB <sub>1</sub> /A <sub>1</sub>                                                                                                                                                                                                                                                                            | プログラマブルタイミングパタンコントローラ(TPC)出力端子(TP <sub>1</sub> ), 16ビットインテグレーテッドタイマユニット(ITU)の入出力端子(TIOCB <sub>1</sub> )と入出力ポートの兼用                                                                                                         | アドレス出力端子(A <sub>1</sub> )                                                                                                                                                                                    | TPC出力端子(TP <sub>1</sub> ) ITUの入出力端子(TIOCB <sub>1</sub> )と入出力ポートの兼用                                                                                                  | アドレス出力端子(A <sub>1</sub> )                                                                                                     | TPC出力端子(TP <sub>1</sub> )、ITUの入出力端子(TIOCB <sub>1</sub> )と入出力ポートの兼用                                                            |                                                                                                                               |                                                                   |

|      |                                                                        | PA. <sub>1</sub> /TP <sub>1</sub> /TIOCA <sub>1</sub> /A <sub>2</sub> /CS <sub>1</sub><br>PA. <sub>1</sub> /TP <sub>1</sub> /TIOCB <sub>1</sub> /A <sub>2</sub> /CS <sub>1</sub><br>PA. <sub>1</sub> /TP <sub>1</sub> /TIOCA <sub>1</sub> /A <sub>2</sub> /CS <sub>1</sub>                                                                       | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )、CS <sub>1</sub> ~CS <sub>8</sub> 出力端子と入出力ポートの兼用                                                       | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )アドレス出力端子(A <sub>1</sub> ~A <sub>8</sub> )、CS <sub>1</sub> ~CS <sub>8</sub> 出力端子と入出力ポートの兼用 | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )、CS <sub>1</sub> ~CS <sub>8</sub> 出力端子と入出力ポートの兼用 | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )と入出力ポートの兼用 | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )と入出力ポートの兼用 | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )と入出力ポートの兼用 |                                                                   |

|      |                                                                        | PA. <sub>1</sub> /TP <sub>1</sub> /TIOCB <sub>1</sub> /TCLKD<br>PA. <sub>1</sub> /TP <sub>1</sub> /TIOCA <sub>1</sub> /TCLKC<br>PA. <sub>1</sub> /TP <sub>1</sub> /TEND <sub>1</sub> /TCLKB<br>PA. <sub>1</sub> /TP <sub>1</sub> /TEND <sub>8</sub> /TCLKA                                                                                       | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、DMAコントローラ(DMAC)の出力端子(TEND <sub>1</sub> , TEND <sub>8</sub> )、ITUの入出力端子(TCLKD, TCLKC, TCLKB, TCLKA, TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )と入出力ポートの兼用                         |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

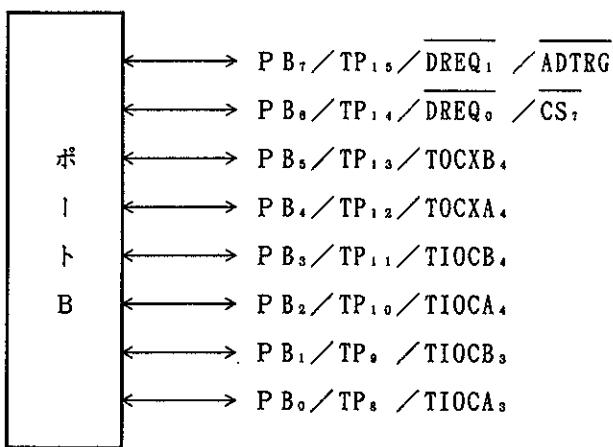

| ポートB | ・8ビットの入出力ポート<br>・LED駆動可能<br>・PB <sub>1</sub> ~PB <sub>8</sub> はシミュット入力 | PB. <sub>1</sub> /TP <sub>1</sub> /DREQ <sub>1</sub> /ADTRG                                                                                                                                                                                                                                                                                      | TPC出力端子(TP <sub>1</sub> )、DMACの入力端子(DREQ <sub>1</sub> )、A/D変換器の外部トリガ入力端子(ADTRG)と入出力ポートの兼用                                                                                                                                 |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

|      |                                                                        | PB. <sub>1</sub> /TP <sub>1</sub> /DREQ <sub>1</sub> /CS <sub>1</sub>                                                                                                                                                                                                                                                                            | TPC出力端子(TP <sub>1</sub> )、DMACの入力端子(DREQ <sub>1</sub> )、CS <sub>1</sub> 出力端子と入出力ポートの兼用                                                                                                                                    |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               | TPC出力端子(TP <sub>1</sub> )、DMACの入力端子(DREQ <sub>1</sub> )と入出力ポートの兼用 |

|      |                                                                        | PB. <sub>1</sub> /TP <sub>1</sub> /TOCX <sub>B</sub><br>PB. <sub>1</sub> /TP <sub>1</sub> /TOXA <sub>1</sub><br>PB. <sub>1</sub> /TP <sub>1</sub> /TIOCB <sub>1</sub><br>PB. <sub>1</sub> /TP <sub>1</sub> /TIOCA <sub>1</sub><br>PB. <sub>1</sub> /TP <sub>1</sub> /TIOCB <sub>1</sub><br>PB. <sub>1</sub> /TP <sub>1</sub> /TIOCA <sub>1</sub> | TPC出力端子(TP <sub>1</sub> ~TP <sub>8</sub> )、ITUの入出力端子(TOCXB <sub>1</sub> , TOXA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> , TIOCB <sub>1</sub> , TIOCA <sub>1</sub> )と8ビットの入出力ポートの兼用                          |                                                                                                                                                                                                              |                                                                                                                                                                     |                                                                                                                               |                                                                                                                               |                                                                                                                               |                                                                   |

## 9.2 ポート1

### 9.2.1 概要

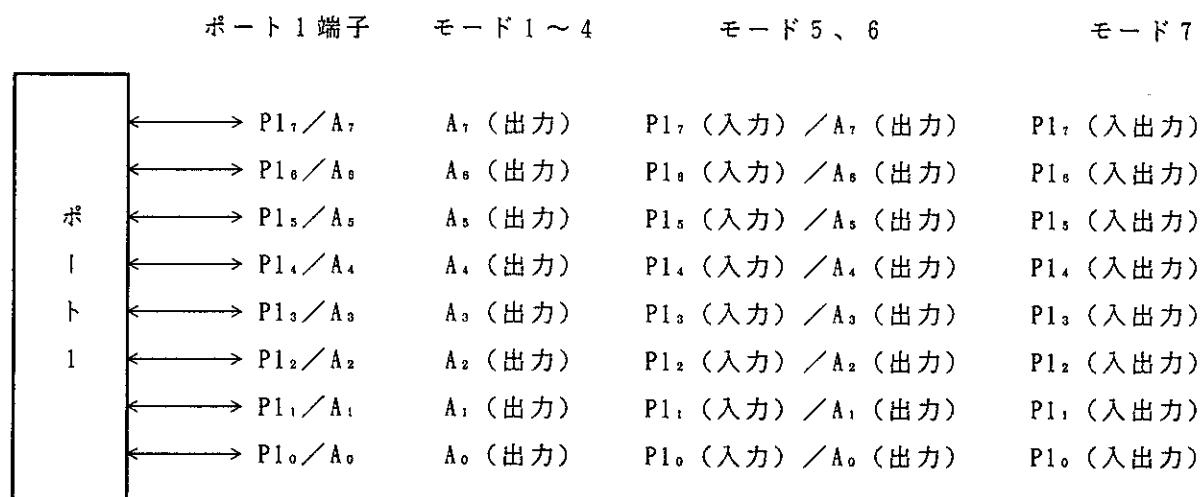

ポート1は、アドレス出力兼用の8ビットの入出力ポートです。ポート1の各端子は、図9.1に示す構成となっており、動作モードにより端子機能が異なります。モード1～4（内蔵ROM無効拡張モード）のときは、アドレスバス（A<sub>7</sub>～A<sub>0</sub>）出力端子となります。

モード5、6（内蔵ROM有効拡張モード）のときは、ポート1データディレクションレジスタ（P1DDR）の設定によりアドレスバス（A<sub>7</sub>～A<sub>0</sub>）出力端子、または入力ポートとなります。モード7（シングルチップモード）のときは、入出力ポートとなります。

エリア3にDRAMを接続する場合には、リード／ライトサイクルでA<sub>7</sub>～A<sub>0</sub>がロウ／カラムアドレス出力となります。詳細は「第7章 リフレッシュコントローラ」を参照してください。

ポート1は、1個のTTL負荷と90pFの容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図9.1 ポート1の端子構成

## 9.2.2 レジスタ構成

表9.2にポート1のレジスタ構成を示します。

表9.2 ポート1レジスタ構成

| アドレス*  | 名 称                | 略 称   | R/W | 初期値    |        |

|--------|--------------------|-------|-----|--------|--------|

|        |                    |       |     | モード1~4 | モード5~7 |

| H'FFC0 | ポート1データディレクションレジスタ | P1DDR | W   | H'FF   | H'00   |

| H'FFC2 | ポート1データレジスタ        | P1DR  | R/W | H'00   |        |

【注】\* アドレスの下位16ビットを示しています。

### (1) ポート1データディレクションレジスタ (P1DDR)

P1DDRは、8ビットのライト専用のレジスタで、ポート1各端子の入出力をビットごとに指定することができます。

| ビット:                    | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|-------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|                         | P1 <sub>7</sub> DDR | P1 <sub>6</sub> DDR | P1 <sub>5</sub> DDR | P1 <sub>4</sub> DDR | P1 <sub>3</sub> DDR | P1 <sub>2</sub> DDR | P1 <sub>1</sub> DDR | P1 <sub>0</sub> DDR |

| モード1~4 { 初期値 :          | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   |

| R/W :                   | —                   | —                   | —                   | —                   | —                   | —                   | —                   | —                   |

| モード5~7 { 初期値 :          | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W :                   | W                   | W                   | W                   | W                   | W                   | W                   | W                   | W                   |

| ポート1データディレクション7~0       |                     |                     |                     |                     |                     |                     |                     |                     |

| ポート1の各端子の入出力を選択するビットです。 |                     |                     |                     |                     |                     |                     |                     |                     |

#### (a) モード1~4 (内蔵ROM無効拡張モード)

P1DDRは“1”に固定され、ポート1はアドレスバスとして機能します。ライトは無効です。

#### (b) モード5、6 (内蔵ROM有効拡張モード)

P1DDRに“1”をセットすると対応するポート1の端子はアドレス出力となり、“0”にクリアすると入力ポートになります。

#### (c) モード7 (シングルチップモード)

ポート1は入出力ポートとして機能します。P1DDRに“1”をセットすると対応するポート1の端子は出力端子となり、“0”にクリアすると入力端子になります。

モード5~7ではP1DDRは、ライト専用のレジスタで、リードは無効です。リードすると“1”が読み出されます。

P1DDRは、リセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。そのため、P1DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移するとその端子は出力状態のままとなっています。

## (2) ポート1データレジスタ (P1DR)

P1DRは、8ビットのリード/ライト可能なレジスタで、ポート1の出力データを格納します。また、このレジスタをリードすると、P1DDRが“0”的ビットは端子のロジックレベルが読み出され、“1”的ビットはP1DRの値が読み出されます。

| ビット: | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|      | P1 <sub>7</sub> | P1 <sub>6</sub> | P1 <sub>5</sub> | P1 <sub>4</sub> | P1 <sub>3</sub> | P1 <sub>2</sub> | P1 <sub>1</sub> | P1 <sub>0</sub> |

| 初期値: | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| R/W: | R/W             |

ポート1データ7～0

ポート1の各端子のデータを格納するビットです。

P1DRは、リセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

## 9.3 ポート2

### 9.3.1 概要

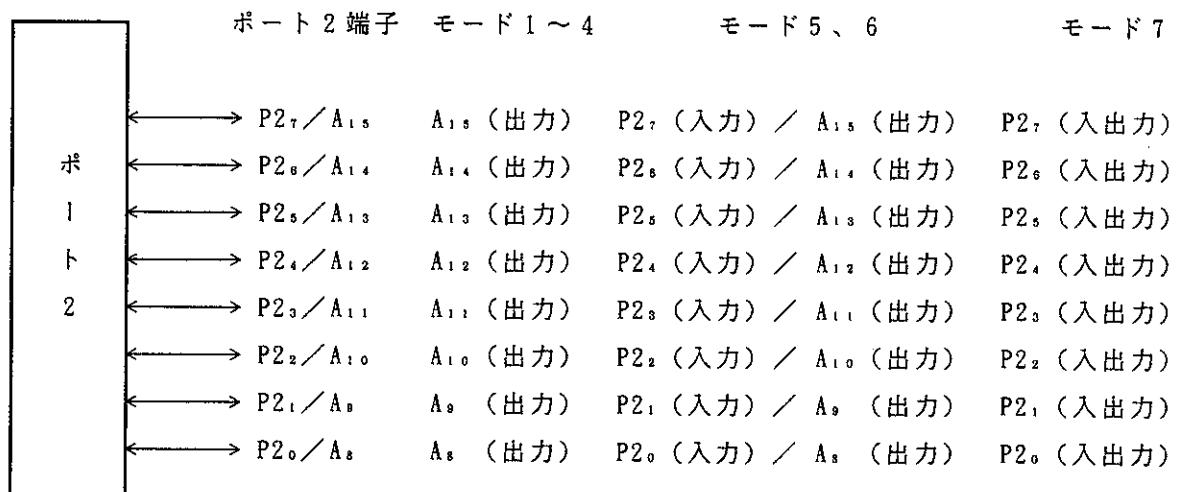

ポート2は、アドレス出力兼用の8ビットの入出力ポートです。ポート2の各端子は、図9.2に示す構成となっており、動作モードにより端子機能が異なります。

モード1～4（内蔵ROM無効拡張モード）のときは、アドレスバス（A<sub>15</sub>～A<sub>8</sub>）出力端子となります。モード5、6（内蔵ROM有効拡張モード）のときは、ポート2データディレクションレジスタ（P2DDR）の設定によりアドレスバス（A<sub>15</sub>～A<sub>8</sub>）または入力ポートとなります。

モード7（シングルチップモード）のときは、入出力ポートとなります。

エリア3にDRAMを接続する場合には、リード／ライトサイクルでA<sub>9</sub>、A<sub>8</sub>がロウ／カラムアドレス出力となります。詳細は「第7章 リフレッシュコントローラ」を参照してください。

ポート2は、プログラムで制御可能なプルアップMOSが内蔵されています。また、1個のTT負荷と90pFの容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図9.2 ポート2の端子構成

### 9.3.2 レジスタ構成

表9.3にポート2のレジスタ構成を示します。

表9.3 ポート2レジスタ構成

| アドレス*  | 名 称                      | 略 称   | R/W | 初期値    |        |

|--------|--------------------------|-------|-----|--------|--------|

|        |                          |       |     | モード1～4 | モード5～7 |

| H'FFC1 | ポート2データディレクションレジスタ       | P2DDR | W   | H'FF   | H'00   |

| H'FFC3 | ポート2データレジスタ              | P2DR  | R/W |        | H'00   |

| H'FFD8 | ポート2入力プルアップMOSコントロールレジスタ | P2PCR | R/W |        | H'00   |

【注】\* アドレスの下位16ビットを示しています。

### (1) ポート2データディレクションレジスタ (P2DDR)

P2DDRは、8ビットのライト専用のレジスタで、ポート2の各端子の入出力をピットごとに指定することができます。

| ビット:   | 7                     | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|--------|-----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|        | P2 <sub>7</sub> DDR   | P2 <sub>6</sub> DDR | P2 <sub>5</sub> DDR | P2 <sub>4</sub> DDR | P2 <sub>3</sub> DDR | P2 <sub>2</sub> DDR | P2 <sub>1</sub> DDR | P2 <sub>0</sub> DDR |

| モード1~4 | { 初期値: 1<br>R/W: —— } | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   | 1                   |

| モード5~7 | { 初期値: 0<br>R/W: W }  | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

ポート2データディレクション7~0

ポート2の各端子の入出力を選択するビットです。

#### (a) モード1~4 (内蔵ROM無効拡張モード)

P2DDRは“1”に固定され、ポート2はアドレスバスとして機能します。ライトは無効です。

#### (b) モード5、6 (内蔵ROM有効拡張モード)

ポート2はリセット直後は入力ポートとなっています。

P2DDRに“1”をセットすると対応するポート2の端子はアドレス出力端子となり、“0”にクリアすると入力ポートになります。

#### (c) モード7 (シングルチップモード)

ポート2は入出力ポートとして機能します。P2DDRに“1”をセットすると対応するポート2の端子は出力ポートとなり、“0”にクリアすると入力ポートとなります。

モード5~7ではP2DDRは、ライト専用のレジスタで、リードは無効です。リードすると“1”が読み出されます。

P2DDRは、リセット、またはハードウェアスタンバイモード時にH'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。そのため、P2DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移するとその端子は出力状態のままとなっています。

### (2) ポート2データレジスタ (P2DR)

P2DRは、8ビットのリード／ライト可能なレジスタで、ポート2の出力データを格納します。また、このレジスタをリードすると、P2DDRが“0”的ビットは端子のロジックレベルが読み出され、“1”的ビットはP2DRの値が読み出されます。

| ビット: | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|      | P2 <sub>7</sub> | P2 <sub>6</sub> | P2 <sub>5</sub> | P2 <sub>4</sub> | P2 <sub>3</sub> | P2 <sub>2</sub> | P2 <sub>1</sub> | P2 <sub>0</sub> |

| 初期値: | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| R/W: | R/W             |

ポート2データ7～0

ポート2の各端子のデータを格納するビットです。

P2DRは、リセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

### (3) ポート2入力プルアップMOSコントロールレジスタ (P2PCR)

P2PCRは8ビットのリード／ライト可能なレジスタで、ポート2に内蔵した入力プルアップMOSをビットごとに制御します。

| ビット: | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | P2 <sub>7</sub> PCR | P2 <sub>6</sub> PCR | P2 <sub>5</sub> PCR | P2 <sub>4</sub> PCR | P2 <sub>3</sub> PCR | P2 <sub>2</sub> PCR | P2 <sub>1</sub> PCR | P2 <sub>0</sub> PCR |

| 初期値: | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W: | R/W                 |

ポート2入力プルアップMOSコントロール7～0

ポート2に内蔵した入力プルアップMOSを制御するビットです。

モード5～7のとき、P2DDRを“0”にクリアした（入力ポートの）状態でP2PCRを“1”にセットすると対応するビットの入力プルアップMOSはONします。

P2PCRは、リセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

表 9.4 入力プルアップMOSの状態（ポート2）

| モード | リセット | ハードウェアスタンバイモード | ソフトウェアスタンバイモード | その他の動作時   |

|-----|------|----------------|----------------|-----------|

| 1   |      |                |                |           |

| 2   |      | O F F          |                | O F F     |

| 3   |      |                |                |           |

| 4   |      |                |                |           |

| 5   |      |                |                |           |

| 6   |      | O F F          |                | O N／O F F |

| 7   |      |                |                |           |

## 《記号説明》

O F F : 入力プルアップMOSは、常にO F F状態です。

O N／O F F : P 2 P C R = “1”かつP 2 D D R = “0”的きO N状態、その他のときはO F F状態です。

## 9.4 ポート3

### 9.4.1 概要

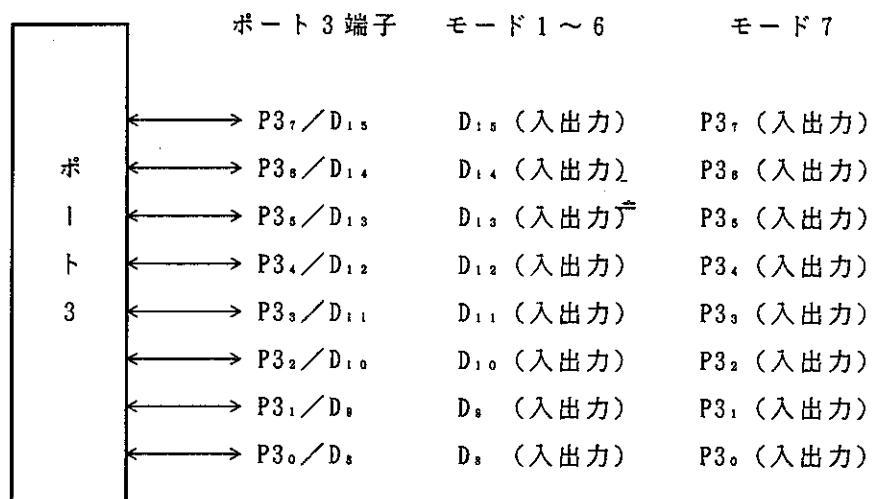

ポート3は、データバス兼用の8ビットの入出力ポートです。ポート3の各端子は、図9.3に示す構成となっており、モード1～6（拡張モード）のときはデータバスとなり、モード7（シングルチップモード）のときは、入出力ポートとなります。

ポート3は、1個のTTL負荷と90pFの容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図9.3 ポート3の端子構成

### 9.4.2 レジスタ構成

表9.5にポート3のレジスタ構成を示します。

表9.5 ポート3レジスタ構成

| アドレス*  | 名 称                | 略 称   | R/W | 初期値  |

|--------|--------------------|-------|-----|------|

| H'FFC4 | ポート3データディレクションレジスタ | P3DDR | W   | H'00 |

| H'FFC6 | ポート3データレジスタ        | P3DR  | R/W | H'00 |

【注】\* アドレスの下位16ビットを示しています。

### (1) ポート 3 データディレクションレジスタ (P3DDR)

P3DDR は、8ビットのライト専用のレジスタで、ポート 3 各端子の入出力をビットごとに指定することができます。

| ビット : | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|-------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|       | P3 <sub>7</sub> DDR | P3 <sub>6</sub> DDR | P3 <sub>5</sub> DDR | P3 <sub>4</sub> DDR | P3 <sub>3</sub> DDR | P3 <sub>2</sub> DDR | P3 <sub>1</sub> DDR | P3 <sub>0</sub> DDR |

| 初期値 : | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W : | W                   | W                   | W                   | W                   | W                   | W                   | W                   | W                   |

ポート 3 データディレクション 7 ~ 0

ポート 3 の各端子の入出力を選択するビットです。

#### (a) モード 1 ~ 6 (拡張モード)

ポート 3 はデータバスとして機能します。P3DDR は無効です。

#### (b) モード 7 (シングルチップモード)

ポート 3 は入出力ポートとして機能します。

P3DDR に “1” をセットすると対応する端子は出力ポートとなり、“0” にクリアすると入力ポートになります。

P3DDR は、ライト専用で、リードは無効です。リードすると、“1” が読み出されます。

P3DDR は、リセット、またはリードウェアスタンバイモード時に H'00 にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。そのため、P3DDR が “1” にセットされた状態でソフトウェアスタンバイモードに遷移するとその端子は出力状態のままとなっています。

### (2) ポート 3 データレジスタ (P3DR)

P3DR は、8ビットのリード/ライト可能なレジスタで、ポート 3 の出力データを格納します。また、このレジスタをリードすると、P3DDR が “0” のビットは端子のロジックレベルが読み出され、“1” のビットは P3DR の値が読み出されます。

| ビット : | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|       | P3 <sub>7</sub> | P3 <sub>6</sub> | P3 <sub>5</sub> | P3 <sub>4</sub> | P3 <sub>3</sub> | P3 <sub>2</sub> | P3 <sub>1</sub> | P3 <sub>0</sub> |

| 初期値 : | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| R/W : | R/W             |

ポート 3 データ 7 ~ 0

ポート 3 の各端子のデータを格納するビットです。

– P3DR は、リセット、またはハードウェアスタンバイモード時に、H'00 にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

## 9.5 ポート 4

### 9.5.1 概要

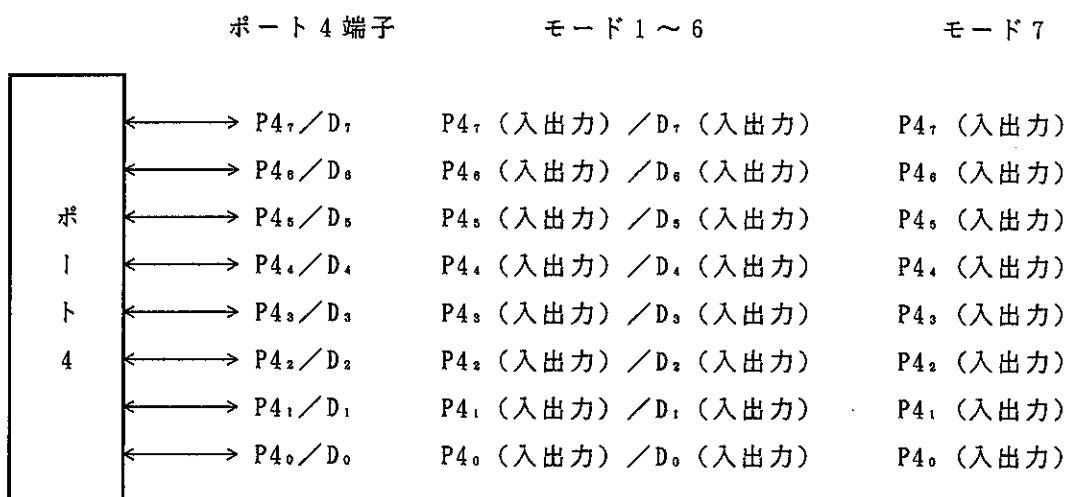

ポート 4 は、データバス兼用の 8 ビットの入出力ポートです。ポート 4 の各端子は、図 9.4 に示す構成となっており、動作モードにより端子機能が異なります。

モード 1 ~ 6 (拡張モード) のときバス幅コントロールレジスタ (A B W C R) により、エリア 0 ~ 7 のすべてを 8 ビットアクセス空間に設定すると、8 ビットバスモードとなり、ポート 4 は入出力ポートとなります。また、エリア 0 ~ 7 のうち少なくとも 1 つのエリアを 16 ビットアクセス空間に設定すると、16 ビットバスモードとなり、ポート 4 はデータバスとなります。

モード 7 (シングルチップモード) のとき、ポート 4 は、入出力ポートとなります。

ポート 4 は、プログラムで制御可能なプルアップ M O S が内蔵されています。

ポート 4 は、1 個の T T L 負荷と 90 pF の容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図 9.4 ポート 4 の端子構成

## 9.5.2 レジスタ構成

表9.6にポート4のレジスタ構成を示します。

表9.6 ポート4レジスタ構成

| アドレス*  | 名 称                      | 略 称   | R/W | 初期値  |

|--------|--------------------------|-------|-----|------|

| H'FFC5 | ポート4データディレクションレジスタ       | P4DDR | W   | H'00 |

| H'FFC7 | ポート4データレジスタ              | P4DR  | R/W | H'00 |

| H'FFDA | ポート4入力プルアップMOSコントロールレジスタ | P4PCR | R/W | H'00 |

【注】\* アドレスの下位16ビットを示しています。

### (1) ポート4データディレクションレジスタ (P4DDR)

P4DDRは、8ビットのライト専用のレジスタで、ポート4各端子の入出力をビットごとに指定することができます。

| ビット: | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | P4 <sub>7</sub> DDR | P4 <sub>6</sub> DDR | P4 <sub>5</sub> DDR | P4 <sub>4</sub> DDR | P4 <sub>3</sub> DDR | P4 <sub>2</sub> DDR | P4 <sub>1</sub> DDR | P4 <sub>0</sub> DDR |

| 初期値: | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W: | W                   | W                   | W                   | W                   | W                   | W                   | W                   | W                   |

ポート4データディレクション7～0

ポート4の各端子の入出力を選択するビットです。

#### (a) モード1～6(拡張モード)

全エリアを8ビットアクセス空間に設定し、8ビットバスモードとしたときポート4は入出力ポートとして機能します。P4DDRに“1”をセットすると対応するポート4の端子は出力ポートとなり、“0”にクリアすると入力ポートになります。

少なくとも1つのエリアを16ビットアクセス空間に設定し、16ビットバスモードとしたとき、ポート4はデータバスとして機能します。

#### (b) モード7(シングルチップモード)

ポート4は入出力ポートとして機能します。P4DDRに“1”をセットすると対応するポート4の端子は出力ポートとなり、“0”にクリアすると入力ポートになります。

P4DDRは、ライト専用レジスタで、リードは無効です。リードすると、“1”が読み出されます。

P4DDRは、リセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。ソフトウェアスタンバイモード時には直前の状態を保持します。

ABWCRおよびP4DDRはソフトウェアスタンバイモード時にはイニシャライズされません。したがって、ポート4が入出力ポートとして機能しているとき、P4DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移すると、その端子は出力状態のままとなっています。

## (2) ポート4データレジスタ (P4DR)

P4DRは、8ビットのリード／ライト可能なレジスタで、ポート4の出力データを格納します。また、このレジスタをリードすると、P4DDRが“0”のビットは端子のロジックレベルが読み出され、“1”的ビットは、P4DRの値が読み出されます。

| ビット: | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|      | P4 <sub>7</sub> | P4 <sub>6</sub> | P4 <sub>5</sub> | P4 <sub>4</sub> | P4 <sub>3</sub> | P4 <sub>2</sub> | P4 <sub>1</sub> | P4 <sub>0</sub> |

| 初期値: | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| R/W: | R/W             |

ポート4データ7～0

ポート4の各端子のデータを格納するビットです。

P4DRは、リセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

## (3) ポート4入力プルアップMOSコントロールレジスタ (P4PCR)

P4PCRは8ビットのリード／ライト可能なレジスタで、ポート4に内蔵した入力プルアップMOSをビットごとに制御します。

| ビット: | 7                   | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | P4 <sub>7</sub> PCR | P4 <sub>6</sub> PCR | P4 <sub>5</sub> PCR | P4 <sub>4</sub> PCR | P4 <sub>3</sub> PCR | P4 <sub>2</sub> PCR | P4 <sub>1</sub> PCR | P4 <sub>0</sub> PCR |

| 初期値: | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W: | R/W                 |

ポート4入力プルアップMOSコントロール7～0

ポート4に内蔵した入力プルアップMOSを制御するビットです。

モード1～6（拡張モード）の8ビットバスモード時とモード7（シングルチップモード）時、P4DDRを“0”にクリアした（入力ポートの）状態で、P4PCRを“1”にセットすると入力プルアップMOSはONします。

P4PCRは、リセット、またはハードウェアスタンバイモード時に、H'00にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

各動作モードでの、入力プルアップMOSの状態を表9.7に示します。

表9.7 入力プルアップMOSの状態（ポート4）

| モード |            | リセット  | ハードウェアスタンバイモード | ソフトウェアスタンバイモード | その他の動作時 |

|-----|------------|-------|----------------|----------------|---------|

| 1～6 | 8ビットバスモード  | O F F | O N / O F F    |                |         |

|     | 16ビットバスモード |       | O F F          |                |         |

|     | 7          |       | O N / O F F    |                |         |

《記号説明》

O F F : 入力プルアップMOSは、常にO F F状態です。

O N / O F F : P 4 P C R = “1”かつP 4 D D R = “0”的きON状態、その他のときはO F F状態です。

## 9.6 ポート5

### 9.6.1 概要

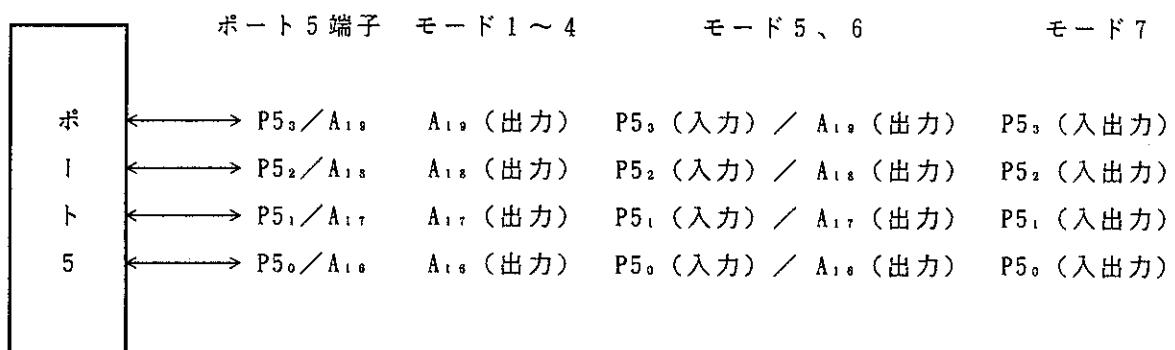

ポート5は、アドレス出力兼用の4ビットの入出力ポートです。ポート5の各端子は、図9.5に示す構成となっており、動作モードにより端子機能が異なります。

モード1～4（内蔵ROM無効拡張モード）に設定したとき、ポート5の各端子はアドレス( $A_{15} \sim A_8$ )出力として機能します。モード5、6（内蔵ROM有効拡張モード）に設定したときは、ポート5データディレクションレジスタ（P5DDR）の設定によりアドレスバス( $A_{15} \sim A_8$ )または入力ポートとなります。

モード7（シングルチップモード）のときは、入出力ポートとなります。

ポート5は、プログラムで制御可能なプルアップMOSが内蔵されています。

ポート5は、1個のTTL負荷と90pFの容量負荷を駆動することができます。また、LED、ダーリントントランジスタを駆動することもできます。

図9.5 ポート5の端子構成

### 9.6.2 レジスタ構成

表9.8にポート5のレジスタ構成を示します。

表9.8 ポート5レジスタ構成

| アドレス*  | 名 称                      | 略 称   | R/W | 初期 値   |        |

|--------|--------------------------|-------|-----|--------|--------|

|        |                          |       |     | モード1～4 | モード5～7 |

| H'FFC8 | ポート5データディレクションレジスタ       | P5DDR | W   | H'FF   | H'F0   |

| H'FFCA | ポート5データレジスタ              | P5DR  | R/W |        | H'F0   |

| H'FFDB | ポート5入力プルアップMOSコントロールレジスタ | P5PCR | R/W |        | H'F0   |

【注】\* アドレスの下位16ビットを示しています。

#### (1) ポート5データディレクションレジスタ (P5DDR)

P5DDRは、8ビットのライト専用のレジスタで、ポート5各端子の入出力をビットごとに指定することができます。

|         | ビット：  |   |   |   |                     |                     |                     |                     |

|---------|-------|---|---|---|---------------------|---------------------|---------------------|---------------------|

|         | 7     | 6 | 5 | 4 | 3                   | 2                   | 1                   | 0                   |

| モード1~4  | —     | — | — | — | P5 <sub>3</sub> DDR | P5 <sub>2</sub> DDR | P5 <sub>1</sub> DDR | P5 <sub>0</sub> DDR |

|         | 初期値：1 | 1 | 1 | 1 | 1                   | 1                   | 1                   | 1                   |

| モード5~7  | R/W：— | — | — | — | —                   | —                   | —                   | —                   |

|         | 初期値：1 | 1 | 1 | 1 | 0                   | 0                   | 0                   | 0                   |

| モード5~7  | R/W：— | — | — | — | W                   | W                   | W                   | W                   |

|         |       |   |   |   |                     |                     |                     |                     |

| リザーブビット |       |   |   |   |                     |                     |                     |                     |

(a) 王一凡 1~4 (內藏 ROM 舞動擴張王一凡)

P5DDRは“1”に固定され、ポート5はアドレス出力として機能します。P5,DDR～P5,DDRビットはリザーブビットで“1”に固定されています。ライトは無効です。

(b) モード5、6(内蔵ROM有効拡張モード)

このモードでは、ポート5はリセット直後は入力ポートとなっています。P5DDRに“1”をセットすると対応するポート5の端子がアドレス出力端子になり、“0”にクリアすると入力ポートになります。

(c) モード7(シングルチップモード)

ポート5は、入出力ポートとして機能します。P5DDRに“1”をセットすると対応する端子は出力ポートになり、“0”にクリアすると入力ポートになります。

P5DDRは、ライト専用レジスタで、リードは無効です。リードすると“1”が読み出されます。

P5DDRは、リセット、またはハードウェアスタンバイモード時に、H'F0にイニシャライズされます。ソフトウェアスタンバイモード時には直前の状態を保持します。そのため、P5DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移すると、その端子は出力状態のままとなっています。

## (2) ポート5データレジスタ (P5DR)

P5DRは、8ビットのリード／ライト可能なレジスタで、ポート5の出力データを格納します。また、このレジスタをリードすると、P5DDRの値が“0”のビットは端子のロジックレベルが読み出され、“1”的ビットは、P5DRの値が読み出されます。

| ビット：           | 7 | 6 | 5 | 4 | 3               | 2               | 1               | 0               |

|----------------|---|---|---|---|-----------------|-----------------|-----------------|-----------------|

| 初期値：           | — | — | — | — | P5 <sub>3</sub> | P5 <sub>2</sub> | P5 <sub>1</sub> | P5 <sub>0</sub> |

| R/W：           | — | — | — | — | R/W             | R/W             | R/W             | R/W             |

| <u>リザーブビット</u> |   |   |   |   |                 |                 |                 |                 |

### ポート5データ3～0

ポート5の各端子のデータを格納するビットです。

ビット7～4は、リザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

P5DRは、リセット、またはハードウェアスタンバイモード時に、H'F0にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

## (3) ポート5入力プルアップMOSコントロールレジスタ (P5PCR)

P5PCRは8ビットのリード／ライト可能なレジスタで、ポート5に内蔵した入力プルアップMOSをビットごとに制御します。

| ビット：           | 7 | 6 | 5 | 4 | 3                   | 2                   | 1                   | 0                   |

|----------------|---|---|---|---|---------------------|---------------------|---------------------|---------------------|

| 初期値：           | — | — | — | — | P5 <sub>3</sub> PCR | P5 <sub>2</sub> PCR | P5 <sub>1</sub> PCR | P5 <sub>0</sub> PCR |

| R/W：           | — | — | — | — | R/W                 | R/W                 | R/W                 | R/W                 |

| <u>リザーブビット</u> |   |   |   |   |                     |                     |                     |                     |

### ポート5入力プルアップMOSコントロール3～0

ポート5に内蔵した入力プルアップMOSを制御するビットです。

モード5～7のとき、P5DDRを“0”にクリアした（入力ポート）状態でP5PCRを“1”にセットすると入力プルアップMOSはONします。

P5PCRは、リセット、またはハードウェアスタンバイモード時に、H'F0にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

各動作モードでの、入力プルアップMOSの状態を表9.9に示します。

表9.9 入力プルアップMOSの状態（ポート5）

| モード | リセット | ハードウェアスタンバイモード | ソフトウェアスタンバイモード | その他の動作時 |

|-----|------|----------------|----------------|---------|

| 1   |      |                |                |         |

| 2   |      | OFF            |                | OFF     |

| 3   |      |                |                |         |

| 4   |      |                |                |         |

| 5   |      |                |                |         |

| 6   |      | OFF            |                | ON/ OFF |

| 7   |      |                |                |         |

《記号説明》

OFF : 入力プルアップMOSは、常にOFF状態です。

ON/ OFF : P5PCR = "1"かつP5DDR = "0"のときON状態、その他のときはOFF状態です。

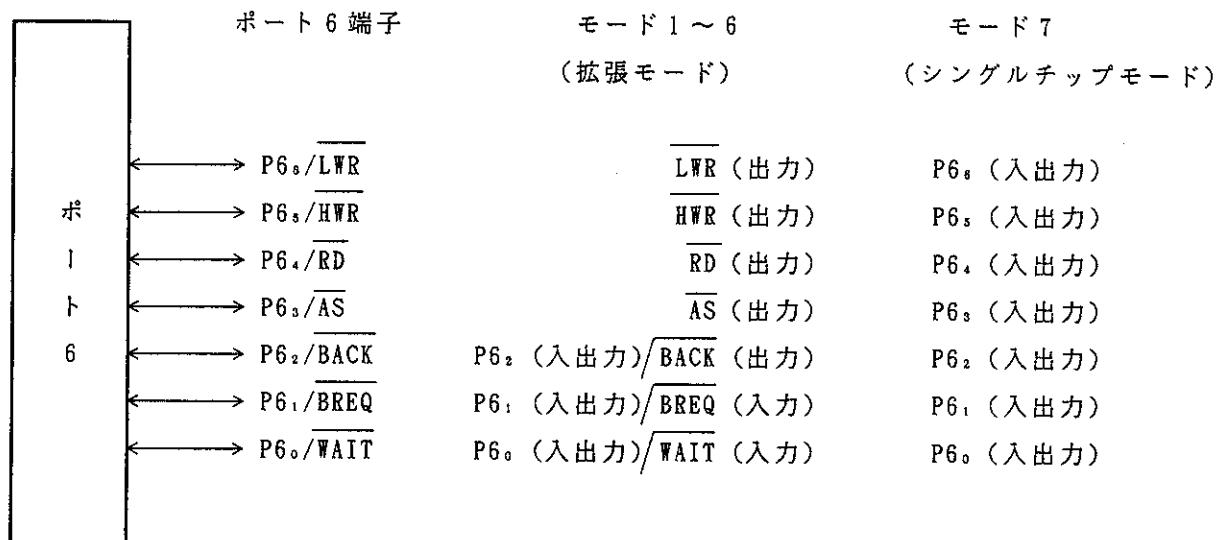

## 9.7 ポート 6

### 9.7.1 概要

ポート 6 は、7 ビットの入出力ポートです。ポート 6 はバス制御入出力端子 (LWR、HWR、RD、AS、BACK、BREQ、WAIT) と兼用になっています。エリア 3 に DRAM を接続する場合には、LWR、HWR、RD がそれぞれ LW、UW、CAS または LCAS、UCAS、WE と兼用になります。詳細は「第 7 章 リフレッシュコントローラ」を参照してください。

ポート 6 の端子構成を図 9.6 に示します。

モード 1 ~ 6 (拡張モード) 時には、LWR、HWR、RD、AS、P6<sub>2</sub>/BACK、P6<sub>1</sub>/BREQ、P6<sub>0</sub>/WAIT として機能します。端子機能の選択方法については表 9.11 を参照してください。モード 7 (シングルチップモード) 時には、入出力ポートとなります。

ポート 6 は、1 個の TTL 負荷と 30pF の容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図 9.6 ポート 6 の端子構成

### 9.7.2 レジスタ構成

表 9.10 にポート 6 のレジスタ構成を示します。

表 9.10 ポート 6 レジスタ構成

| アドレス*  | 名 称                  | 略 称   | R/W | 初期値    |        |

|--------|----------------------|-------|-----|--------|--------|

|        |                      |       |     | モード1~5 | モード6、7 |

| H'FFC9 | ポート 6 データディレクションレジスタ | P6DDR | W   | H'F8   | H'80   |

| H'FFCB | ポート 6 データレジスタ        | P6DR  | R/W | H'80   | H'80   |

【注】\* アドレスの下位 16 ビットを示しています。

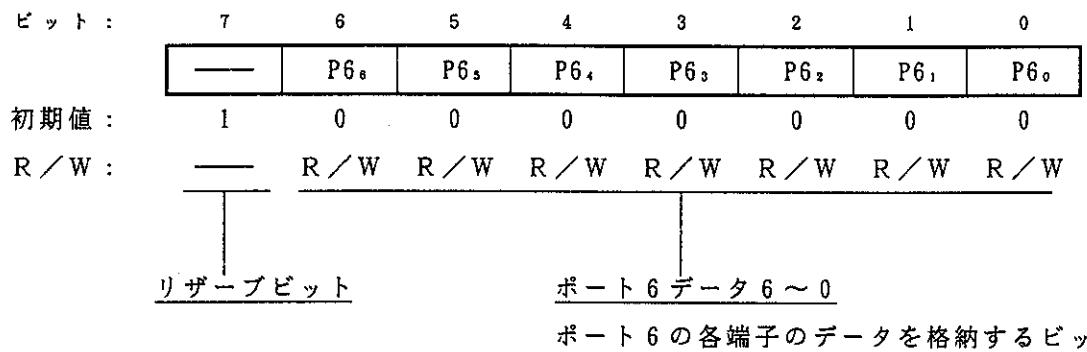

### (1) ポート 6 データディレクションレジスタ (P6DDR)

P6DDRは、8ビットのライト専用のレジスタで、ポート6の各端子の入出力をビットごとに指定することができます。

| ビット : | 7 | 6                   | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|-------|---|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|       | — | P6 <sub>8</sub> DDR | P6 <sub>5</sub> DDR | P6 <sub>4</sub> DDR | P6 <sub>3</sub> DDR | P6 <sub>2</sub> DDR | P6 <sub>1</sub> DDR | P6 <sub>0</sub> DDR |

| 初期値 : | 1 | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W : | — | W                   | W                   | W                   | W                   | W                   | W                   | W                   |

リザーブビット

ポート6データディレクション6～0

ポート6の各端子の入出力を選択するビットです。

#### (a) モード1～6 (拡張モード)

ポートP6<sub>8</sub>～P6<sub>3</sub>はバス制御出力端子 (LWR、HWR、RD、AS) として機能します。P6<sub>2</sub>～P6<sub>0</sub>は、入出力ポートとして機能します。P6DDR2～0に“1”をセットすると対応するポート6の端子は出力ポートとなり、“0”にすると入力ポートになります。

#### (b) モード7 (シングルチップモード)

ポート6は入出力ポートとして機能します。

P6DDRに“1”をセットすると対応するポート6の端子は出力ポートとなり、“0”にクリアすると入力ポートになります。

ビット7はリザーブビットです。

P6DDRは、ライト専用で、リードは無効です。リードすると“1”が読み出されます。

P6DDRは、リセット、またはハードウェアスタンバイモード時に、H'80にイニシャライズされます。ソフトウェアスタンバイモード時には直前の状態を保持します。このため、P6DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移すると、その端子は出力状態のままとなっています。

## (2) ポート 6 データレジスタ (P 6 D R)

P 6 D R は、8ビットのリード／ライト可能なレジスタで、ポート 6 の出力データを格納します。また、このレジスタをリードすると、P 6 D D R が “0” のビットは端子のロジックレベルが読み出され、“1” のビットは P 6 D R の値が読み出されます。

ビット 7 はリザーブビットです。また、ビット 7 はリードすると常に “1” が読み出されます。ライトは無効です。

P 6 D R は、リセット、またはハードウェアスタンバイモード時に、H'80にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

表9.11 モード1～6の端子機能(ポート6)

| 端子                                        | 選択方法と端子機能                                                            |                      |                      |

|-------------------------------------------|----------------------------------------------------------------------|----------------------|----------------------|

| P6 <sub>5</sub> /LWR                      | P6 <sub>5</sub> DDRビットとは無関係に、次のように切り換わります。                           |                      |                      |

|                                           | P6 <sub>5</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | LWR出力端子              |                      |

| P6 <sub>3</sub> /HWR                      | P6 <sub>3</sub> DDRビットとは無関係に、次のように切り換わります。                           |                      |                      |

|                                           | P6 <sub>3</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | HWR出力端子              |                      |

| P6 <sub>4</sub> /RD                       | P6 <sub>4</sub> DDRビットとは無関係に、次のように切り換わります。                           |                      |                      |

|                                           | P6 <sub>4</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | RD出力端子               |                      |

| P6 <sub>3</sub> /AS                       | P6 <sub>3</sub> DDRビットとは無関係に、次のように切り換わります。                           |                      |                      |

|                                           | P6 <sub>3</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | AS出力端子               |                      |

| P6 <sub>2</sub> /BACK                     | BRCRのBRLEビットとP6 <sub>2</sub> DDRビットの組合せにより、次のように切り換わります。             |                      |                      |

|                                           | BRLE                                                                 | 0                    | 1                    |

|                                           | P6 <sub>2</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | P6 <sub>2</sub> 入力端子 | P6 <sub>2</sub> 出力端子 |

|                                           |                                                                      | BACK出力端子             |                      |

| P6 <sub>1</sub> /BREQ                     | BRCRのBRLEビットとP6 <sub>1</sub> DDRビットの組合せにより、次のように切り換わります。             |                      |                      |

|                                           | BRLE                                                                 | 0                    | 1                    |

|                                           | P6 <sub>1</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | P6 <sub>1</sub> 入力端子 | P6 <sub>1</sub> 出力端子 |

|                                           |                                                                      | BREQ入力端子             |                      |

| P6 <sub>0</sub> /WAIT                     | WCERのWCE7～WCE0、WCRのWMS1ビットとP6 <sub>0</sub> DDRビットの組合せで、次のように切り換わります。 |                      |                      |

|                                           | WCER                                                                 | すべてが“1”              |                      |

|                                           | WMS1                                                                 | 0                    | 1                    |

|                                           | P6 <sub>0</sub> DDR                                                  | 0                    | 1                    |

|                                           | 端子機能                                                                 | P6 <sub>0</sub> 入力端子 | P6 <sub>0</sub> 出力端子 |

|                                           |                                                                      | WAIT入力端子             |                      |

| 【注】* P6 <sub>0</sub> DDRは“1”にセットしないでください。 |                                                                      |                      |                      |

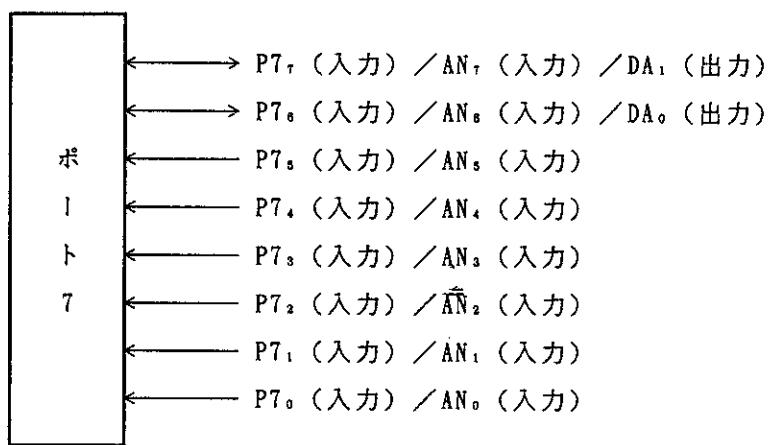

## 9.8 ポート 7

### 9.8.1 概要

ポート 7 は 8 ビットの入力専用ポートです。ポート 7 は、A/D 変換器のアナログ入力端子と D/A 変換器のアナログ出力端子と兼用になっています。これらの端子機能はいずれの動作モードでも共通です。ポート 7 の端子構成を図 9.7 に示します。

ポート 7 端子

図 9.7 ポート 7 の端子構成

### 9.8.2 レジスタ構成

表 9.12 にポート 7 のレジスタ構成を示します。ポート 7 は入力専用ポートであり、データディレクションレジスタはありません。

表 9.12 ポート 7 レジスタ構成

| アドレス*  | 名 称           | 略 称  | R/W | 初期値 |

|--------|---------------|------|-----|-----|

| H'FFCE | ポート 7 データレジスタ | P7DR | R   | 不 定 |

【注】\* アドレスの下位16ビットを示しています。

#### (1) ポート 7 データレジスタ (P7DR)

| ビット : | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|-------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|       | P7 <sub>7</sub> | P7 <sub>6</sub> | P7 <sub>5</sub> | P7 <sub>4</sub> | P7 <sub>3</sub> | P7 <sub>2</sub> | P7 <sub>1</sub> | P7 <sub>0</sub> |

| 初期値 : | —               | *               | —               | *               | —               | *               | —               | *               |

| R/W : | R               | R               | R               | R               | R               | R               | R               | R               |

【注】\* P7<sub>7</sub>～P7<sub>0</sub>端子により決定されます。

P7DR のリードを行うと、常に端子の状態が読み出されます。

## 9.9 ポート8

### 9.9.1 概要

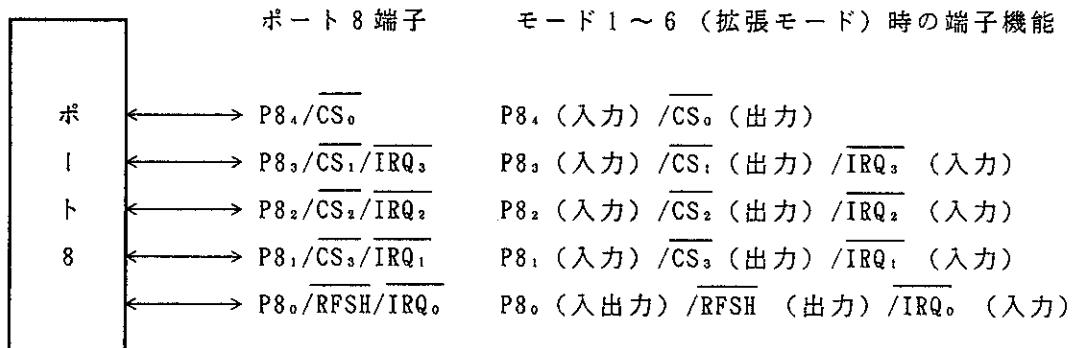

ポート8は、5ビットの入出力ポートです。ポート8は、 $\overline{CS_4} \sim \overline{CS_0}$ 出力端子、RFSH出力端子、 $\overline{IRQ_3} \sim \overline{IRQ_0}$ 入力端子と兼用になっています。ポート8の端子構成を図9.8に示します。

モード1～6（拡張モード）時には、ポート8は、 $\overline{CS_4} \sim \overline{CS_0}$ 出力端子、RFSH出力端子、 $\overline{IRQ_3} \sim \overline{IRQ_0}$ 入力端子と兼用になります。拡張モードでの端子機能の選択方法については表9.14を参照してください。

モード7（シングルチップモード）時には、ポート8は、 $\overline{IRQ_3} \sim \overline{IRQ_0}$ 入力端子と兼用となります。シングルチップモードでの端子機能の選択方法については表9.15を参照してください。

$\overline{IRQ_3} \sim \overline{IRQ_0}$ の機能は端子の入出力にかかわらずI E Rをセットすることにより選択されます。詳細は「第5章 割込みコントローラ」を参照してください。

ポート8は、1個のTTL負荷と90pFの容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

$P_{8_4} \sim P_{8_0}$ 端子はシュミットトリガ入力です。

モード7（シングルチップモード）時の端子機能

$P_{8_4}$ （入出力）

$P_{8_3}$ （入出力） $/IRQ_3$ （入力）

$P_{8_2}$ （入出力） $/IRQ_2$ （入力）

$P_{8_1}$ （入出力） $/IRQ_1$ （入力）

$P_{8_0}$ （入出力） $/IRQ_0$ （入力）

図9.8 ポート8の端子構成

## 9.9.2 レジスタ構成

表9.13にポート8のレジスタ構成を示します。

表9.13 ポート8 レジスタ構成

| アドレス*  | 名 称                | 略 称   | R/W | 初期値    |        |

|--------|--------------------|-------|-----|--------|--------|

|        |                    |       |     | モード1~4 | モード5~7 |

| H'FFCD | ポート8データディレクションレジスタ | P8DDR | W   | H'F0   | H'E0   |

| H'FFCF | ポート8データレジスタ        | P8DR  | R/W | H'E0   |        |

【注】\* アドレスの下位16ビットを示しています。

### (1) ポート8データディレクションレジスタ (P8DDR)

P8DDRは、8ビットのライト専用のレジスタで、ポート8各端子の入出力をビットごとに指定することができます。

| ビット :    | 7       | 6 | 5 | 4                   | 3                       | 2                   | 1                   | 0                   |

|----------|---------|---|---|---------------------|-------------------------|---------------------|---------------------|---------------------|

|          | —       | — | — | P8 <sub>4</sub> DDR | P8 <sub>3</sub> DDR     | P8 <sub>2</sub> DDR | P8 <sub>1</sub> DDR | P8 <sub>0</sub> DDR |

| モード1~4 { | 初期値 : 1 | 1 | 1 | 1                   | 0                       | 0                   | 0                   | 0                   |

| R/W : —  | —       | — | — | W                   | W                       | W                   | W                   | W                   |

| モード5~7 { | 初期値 : 1 | 1 | 1 | 0                   | 0                       | 0                   | 0                   | 0                   |

| R/W : —  | —       | — | — | W                   | W                       | W                   | W                   | W                   |

|          | リザーブビット |   |   |                     | ポート8データディレクション4~0       |                     |                     |                     |

|          |         |   |   |                     | ポート8の各端子の入出力を選択するビットです。 |                     |                     |                     |

#### (a) モード1~6 (拡張モード)

P8<sub>4</sub>~P8<sub>1</sub>はP8DDRの対応するビットが“1”的ときCS<sub>0</sub>~CS<sub>3</sub>出力端子となり、“0”的とき入力ポートとなります。モード1~4(内蔵ROM無効拡張モード)ではリセット直後CS<sub>0</sub>のみ出力となり、他の3端子は入力ポートとなります。モード5~6(内蔵ROM有効拡張モード)ではリセット直後4端子共入力ポートとなります。

P8<sub>0</sub>はリフレッシュコントローラをイネーブルにすると強制的にRFSH出力となり、ディスエーブルのとき入出力ポートとなってP8DDRの設定値に従います。詳細は表9.15を参照してください。

#### (b) モード7 (シングルチップモード)

入出力ポートとして機能します。P8DDRを“1”にセットすると対応する端子は出力ポートとなり、“0”にクリアすると入力ポートとなります。

P8DDRは、ライト専用レジスタで、リードは無効です。リードすると“1”が読み出されます。

P8DDRは、リセット、またはハードウェアスタンバイモード時に、動作モードによりH'E0かH'F0にイニシャライズされます。P8DDRは、ソフトウェアスタンバイモード時には直前の状態を保持します。したがって、P8DDRが“1”にセットされた状態でソフトウェアスタンバイモードに遷移すると、その端子は出力状態のままとなっています。

## (2) ポート8データレジスタ (P8DR)

P8DRは、8ビットのリード/ライト可能なレジスタで、ポート8の出力データを格納します。また、このレジスタをリードすると、P8DDRが“0”的ビットは端子のロジックレベルが読み出され、“1”的ビットはP8DRの値が読み出されます。

| ビット: | 7 | 6 | 5 | 4               | 3               | 2               | 1               | 0               |

|------|---|---|---|-----------------|-----------------|-----------------|-----------------|-----------------|

|      | — | — | — | P8 <sub>4</sub> | P8 <sub>3</sub> | P8 <sub>2</sub> | P8 <sub>1</sub> | P8 <sub>0</sub> |

| 初期値: | 1 | 1 | 1 | 0               | 0               | 0               | 0               | 0               |

| R/W: | — | — | — | R/W             | R/W             | R/W             | R/W             | R/W             |

リザーブビット                            ポート8データ4~0

ポート8の各端子のデータを格納するビットです。

ビット7～5はリザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

P8DRは、リセット、またはハードウェアスタンバイモード時に、H'E0にイニシャライズされます。ソフトウェアスタンバイモード時には、直前の状態を保持します。

表 9.14 モード 1 ~ 6 時の端子機能 (ポート 8)

| 端 子                                                | 選 択 方 法 と 端 子 機 能                                              |                      |                       |

|----------------------------------------------------|----------------------------------------------------------------|----------------------|-----------------------|

| P8 <sub>4</sub> /CS <sub>0</sub>                   | P8 <sub>4</sub> DDRビットにより、次のように切り換わります。                        |                      |                       |

| P8 <sub>3</sub> /CS <sub>1</sub> /IRQ <sub>3</sub> | P8 <sub>3</sub> DDRビットにより、次のように切り換わります。                        | 0                    | 1                     |

|                                                    | 端子機能                                                           | P8 <sub>3</sub> 入力端子 | CS <sub>1</sub> 出力端子  |

|                                                    |                                                                |                      | IRQ <sub>3</sub> 入力端子 |

| P8 <sub>2</sub> /CS <sub>2</sub> /IRQ <sub>2</sub> | P8 <sub>2</sub> DDRビットにより、次のように切り換わります。                        |                      |                       |

| P8 <sub>1</sub> /CS <sub>3</sub> /IRQ <sub>1</sub> | P8 <sub>1</sub> DDRビットにより、次のように切り換わります。                        | 0                    | 1                     |

|                                                    | 端子機能                                                           | P8 <sub>1</sub> 入力端子 | CS <sub>3</sub> 出力端子  |

|                                                    |                                                                |                      | IRQ <sub>1</sub> 入力端子 |

| P8 <sub>0</sub> /RFSH/IRQ <sub>0</sub>             | RFSHCRのRFSHEビット、およびP8 <sub>0</sub> DDRビットの組合せにより、次のように切り換わります。 |                      |                       |

|                                                    | RFSHE                                                          | 0                    | 1                     |

|                                                    | P8 <sub>0</sub> DDR                                            | 0                    | 1                     |

|                                                    | 端子機能                                                           | P8 <sub>0</sub> 入力端子 | P8 <sub>0</sub> 出力端子  |

|                                                    |                                                                |                      | RFSH出力端子              |

|                                                    |                                                                |                      | IRQ <sub>0</sub> 入力端子 |

表 9.15 モード7時の端子機能(ポート8)

| 端子                                | 選択方法と端子機能                               |                       |                      |

|-----------------------------------|-----------------------------------------|-----------------------|----------------------|

| P8 <sub>4</sub>                   | P8 <sub>4</sub> DDRビットにより、次のように切り換わります。 |                       |                      |

| P8 <sub>3</sub> /IRQ <sub>3</sub> | P8 <sub>3</sub> DDR                     | 0                     | 1                    |

|                                   | 端子機能                                    | P8 <sub>3</sub> 入力端子  | P8 <sub>3</sub> 出力端子 |

|                                   |                                         | IRQ <sub>3</sub> 入力端子 |                      |

| P8 <sub>2</sub> /IRQ <sub>2</sub> | P8 <sub>2</sub> DDRビットにより、次のように切り換わります。 |                       |                      |

| P8 <sub>1</sub> /IRQ <sub>1</sub> | P8 <sub>1</sub> DDR                     | 0                     | 1                    |

|                                   | 端子機能                                    | P8 <sub>1</sub> 入力端子  | P8 <sub>1</sub> 出力端子 |

|                                   |                                         | IRQ <sub>1</sub> 入力端子 |                      |

| P8 <sub>0</sub> /IRQ <sub>0</sub> | P8 <sub>0</sub> DDRビットにより、次のように切り換わります。 |                       |                      |

|                                   | P8 <sub>0</sub> DDR                     | 0                     | 1                    |

|                                   | 端子機能                                    | P8 <sub>0</sub> 入力端子  | P8 <sub>0</sub> 出力端子 |

|                                   |                                         | IRQ <sub>0</sub> 入力端子 |                      |

## 9.10 ポート 9

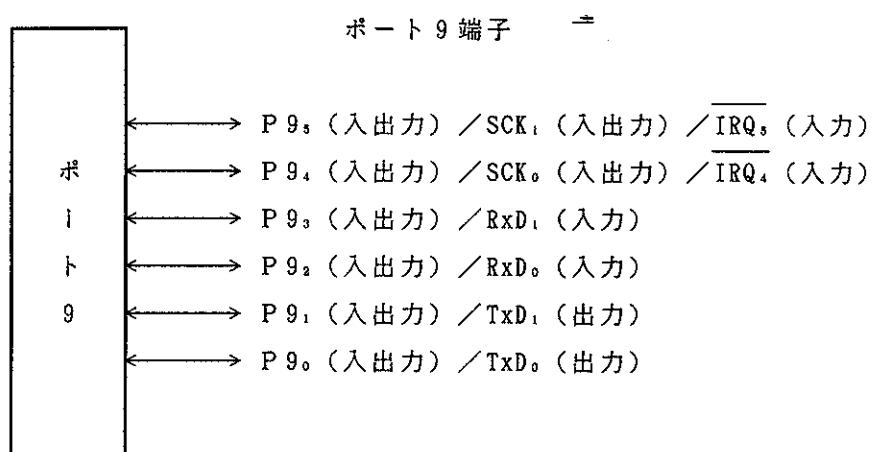

### 9.10.1 概要

ポート 9 は、6 ビットの入出力ポートです。ポート 9 はシリアルコミュニケーションインターフェースチャネル 0、1 (SCI 0、1) の入出力端子(TxD<sub>0</sub>、TxD<sub>1</sub>、RxD<sub>0</sub>、RxD<sub>1</sub>、SCK<sub>0</sub>、SCK<sub>1</sub>)、IRQ<sub>5</sub>、IRQ<sub>4</sub>、入力端子と兼用になっています。端子機能の選択方法については表 9.17 を参照してください。

IRQ<sub>5</sub>、IRQ<sub>4</sub>の機能は端子の入出力にかかわらず IER をセットすることにより選択されます。詳細は「第 5 章 割込みコントローラ」を参照してください。

ポート 9 の端子機能はいずれの動作モードでも共通です。ポート 9 の端子構成を図 9.9 に示します。

ポート 9 は、1 個の TTL 負荷と 30pF の容量負荷を駆動することができます。また、ダーリントントランジスタを駆動することもできます。

図 9.9 ポート 9 の端子構成

### 9.10.2 レジスタ構成

表 9.16 にポート 9 のレジスタ構成を示します。

表 9.16 ポート 9 レジスタ構成

| アドレス*  | 名 称                  | 略 称       | R/W | 初期値  |

|--------|----------------------|-----------|-----|------|

| H'FFD0 | ポート 9 データディレクションレジスタ | P 9 D D R | W   | H'C0 |

| H'FFD2 | ポート 9 データレジスタ        | P 9 D R   | R/W | H'C0 |

【注】\* アドレスの下位 16 ビットを示しています。

### (1) ポート 9 データディレクションレジスタ (P9DDR)

P9DDRは、8ビットのライト専用のレジスタで、ポート9各端子の入出力をビットごとに指定することができます。

| ビット: | 7 | 6 | 5                   | 4                   | 3                   | 2                   | 1                   | 0                   |

|------|---|---|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|      | — | — | P9 <sub>5</sub> DDR | P9 <sub>4</sub> DDR | P9 <sub>3</sub> DDR | P9 <sub>2</sub> DDR | P9 <sub>1</sub> DDR | P9 <sub>0</sub> DDR |

| 初期値: | 1 | 1 | 0                   | 0                   | 0                   | 0                   | 0                   | 0                   |

| R/W: | — | — | W                   | W                   | W                   | W                   | W                   | W                   |

リザーブビット

ポート9データディレクション5～0

ポート9の各端子の入出力を選択するビットです。

P9DDRを“1”にセットすると対応するポート9の各端子は出力ポートとなり、“0”にクリアすると入力ポートになります。

P9DDRは、ライト専用レジスタで、リードは無効です。リードすると“1”が読み出されます。

P9DDRは、リセット、またはハードウェアスタンバイモード時に、H'COにイニシャライズされます。ソフトウェアスタンバイモード時には直前の状態を保持します。そのため、P9DDRが、“1”にセットされた状態でソフトウェアスタンバイモードに遷移すると、その端子は出力状態のままとなっています。

### (2) ポート9データレジスタ (P9DR)

P9DRは、8ビットのリード/ライト可能なレジスタで、ポート9の出力データを格納します。また、このレジスタをリードすると、P9DDRが“0”的ビットは端子のロジックレベルが読み出され、“1”的ビットはP9DRの値が読み出されます。

| ビット: | 7 | 6 | 5               | 4               | 3               | 2               | 1               | 0               |

|------|---|---|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|