# 8. DMA コントローラ

## 第8章 目次

|       |                            |     |

|-------|----------------------------|-----|

| 8.1   | 概要                         | 213 |

| 8.1.1 | 特長                         | 213 |

| 8.1.2 | ブロック図                      | 214 |

| 8.1.3 | 機能概要                       | 215 |

| 8.1.4 | 端子構成                       | 216 |

| 8.1.5 | レジスタ構成                     | 216 |

| 8.2   | 各レジスタの説明(1) (ショートアドレスモード)  | 218 |

| 8.2.1 | メモリアドレスレジスタ (MAR)          | 219 |

| 8.2.2 | I/Oアドレスレジスタ (IOAR)         | 220 |

| 8.2.3 | 転送カウントレジスタ (ETCR)          | 221 |

| 8.2.4 | データransファコントロールレジスタ (DTCR) | 222 |

| 8.3   | 各レジスタの説明(2) (フルアドレスモード)    | 226 |

| 8.3.1 | メモリアドレスレジスタ (MAR)          | 226 |

| 8.3.2 | I/Oアドレスレジスタ (IOAR)         | 227 |

| 8.3.3 | 転送カウントレジスタ (ETCR)          | 227 |

| 8.3.4 | データransファコントロールレジスタ (DTCR) | 229 |

| 8.4   | 動作説明                       | 236 |

| 8.4.1 | 概要                         | 236 |

| 8.4.2 | I/Oモード                     | 238 |

| 8.4.3 | アイドルモード                    | 241 |

| 8.4.4 | リピートモード                    | 244 |

| 8.4.5 | ノーマルモード                    | 247 |

|        |                                 |     |

|--------|---------------------------------|-----|

| 8.4.6  | ブロック転送モード                       | 250 |

| 8.4.7  | DMA Cの起動要因                      | 255 |

| 8.4.8  | DMA Cのバスサイクル                    | 257 |

| 8.4.9  | DMA C複数チャネルの動作                  | 261 |

| 8.4.10 | 外部バス権要求、リフレッシュコントローラとDMA Cの関係   | 262 |

| 8.4.11 | NMI割込みとDMA C                    | 263 |

| 8.4.12 | DMA C動作の強制終了                    | 264 |

| 8.4.13 | フルアドレスモードの解除                    | 264 |

| 8.4.14 | リセット、スタンバイモード、スリープモード時のDMA Cの状態 | 265 |

| 8.5    | 割込み                             | 266 |

| 8.6    | 使用上の注意                          | 267 |

| 8.6.1  | ワードデータ転送時の注意                    | 267 |

| 8.6.2  | DMA CによるDMA C自体のアクセス            | 267 |

| 8.6.3  | MARのロングワードアクセス                  | 267 |

| 8.6.4  | フルアドレスモード設定時の注意                 | 267 |

| 8.6.5  | 内部割込みでDMA Cを起動する場合の注意           | 268 |

| 8.6.6  | NMI割込みとブロック転送モード                | 269 |

| 8.6.7  | MAR、IOARのアドレス指定                 | 269 |

| 8.6.8  | 転送中断時のバスサイクル                    | 270 |

## 8.1 概要

SH8/3048シリーズは、DMAコントローラ（DMAC）を内蔵しています。DMACは最大4チャネルのデータ転送を行うことができます。

消費電流低減のためDMAコントローラを使用しない場合には、DMAコントローラを単独で停止することができます。詳細は「20.6 モジュールスタンバイ機能」を参照してください。

### 8.1.1 特長

DMACには次の特長があります。

#### ■ショートアドレスモードとフルアドレスモードを選択可能

##### (1) ショートアドレスモード

- ・転送元、転送先アドレスの一方を24ビット、他方を8ビットで指定

- ・最大4チャネルを使用可能

- ・I/Oモード／アイドルモード／リピートモードの選択が可能

##### (2) フルアドレスモード

- ・転送元、転送先アドレスを24ビットで指定

- ・最大2チャネルを使用可能

- ・ノーマルモード／ブロック転送モードの選択が可能

#### ■16Mバイトのアドレス空間を直接指定可能

#### ■転送単位をバイト／ワードに設定可能

#### ■起動要因は、内部割込み、外部リクエスト、オートリクエスト（転送モードに依存）

- ・16ビットインテグレーテッドタイマユニット（ITU）のコンペアマッチ／インプットキャプチャ割込み×4

- ・シリアルコミュニケーションインターフェース（SCIチャネル0）の送信データエンブティ割込み、受信データフル割込み

- ・外部リクエスト

- ・オートリクエスト

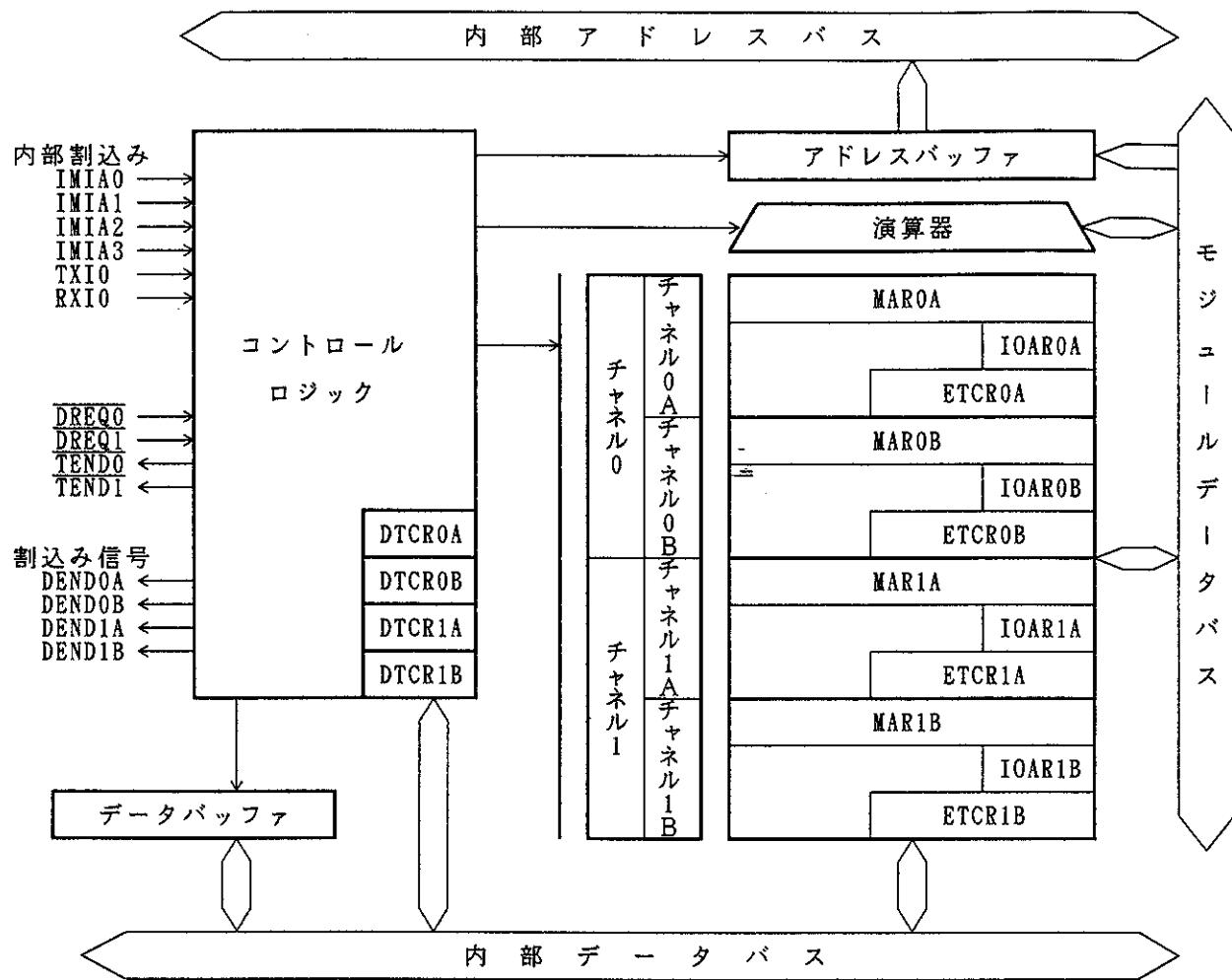

### 8.1.2 ブロック図

DMAのブロック図を図8.1に示します。

#### 《記号説明》

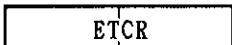

DTCR : データトランスマルチコントロールレジスタ

MAR : メモリアドレスレジスタ

IOAR : I/Oアドレスレジスタ

ETCR : 転送カウントレジスタ

図8.1 DMAのブロック図

### 8.1.3 機能概要

D M A C の機能概要を表 8.1 に示します。

表 8.1 D M A C の機能概要

| 転送モード                                               |                                                                                                                                                                                                                                                                                                                            | 転送要因                                                                                                                                     | アドレスレジスタビット長 |           |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|

| ソース                                                 | デスティネーション                                                                                                                                                                                                                                                                                                                  |                                                                                                                                          | ソース          | デスティネーション |

| シ<br>ヨ<br>ー<br>ト<br>ア<br>ド<br>レ<br>ス<br>モ<br>ー<br>ド | (1) I / O モード <ul style="list-style-type: none"> <li>1回の転送要求で1バイトまたは1ワードの転送を実行</li> <li>メモリアドレスを1または2増減</li> <li>転送回数は1～65536</li> </ul>                                                                                                                                                                                   | <ul style="list-style-type: none"> <li>I T U チャネル<br/>0～3のコンバマッシュ/インプットキャプチャA割込み</li> <li>S C I チャネル<br/>0の送信データ<br/>エンプティ割込み</li> </ul> | 24           | 8         |

|                                                     | (2) アイドルモード <ul style="list-style-type: none"> <li>1回の転送要求で1バイトまたは1ワードの転送を実行</li> <li>メモリアドレスは固定</li> <li>転送回数は1～65536</li> </ul>                                                                                                                                                                                          | <ul style="list-style-type: none"> <li>S C I チャネル<br/>0の受信データ<br/>フル割込み</li> </ul>                                                       | 8            | 24        |

|                                                     | (3) リピートモード <ul style="list-style-type: none"> <li>1回の転送要求で1バイトまたは1ワードの転送を実行</li> <li>メモリアドレスを1または2増減</li> <li>指定回数(1～255)転送後、初期状態を回復して動作を継続</li> </ul>                                                                                                                                                                    | <ul style="list-style-type: none"> <li>外部リクエスト</li> </ul>                                                                                | 24           | 8         |

| フル<br>ア<br>ド<br>レ<br>ス<br>モ<br>ー<br>ド               | (1) ノーマルモード <ul style="list-style-type: none"> <li>① オートリクエスト <ul style="list-style-type: none"> <li>転送要求を内部保持</li> <li>指定回数(1～65536)継続して転送</li> <li>バーストモード/サイクルスチールモードを選択可能</li> </ul> </li> <li>② 外部リクエスト <ul style="list-style-type: none"> <li>1回の転送要求で1バイトまたは1ワードの転送を実行</li> <li>転送回数は1～65536</li> </ul> </li> </ul> | <ul style="list-style-type: none"> <li>オートリクエスト</li> <li>外部リクエスト</li> </ul>                                                              | 24           | 24        |

|                                                     | (2) ブロック転送モード <ul style="list-style-type: none"> <li>1回の転送要求で指定したブロックサイズの転送</li> <li>転送回数は1～65536</li> <li>ソースまたはデスティネーションのいずれかをブロックエリアに指定可能</li> <li>ブロックサイズ1～255バイトまたはワード</li> </ul>                                                                                                                                     | <ul style="list-style-type: none"> <li>I T U チャネル<br/>0～3のコンバマッシュ/インプットキャプチャA割込み</li> <li>外部リクエスト</li> </ul>                             | 24           | 24        |

#### 8.1.4 端子構成

DMAの端子構成を表8.2に示します。

表8.2 端子構成

| チャネル | 名 称    | 略 称               | 入出力 | 機 能              |

|------|--------|-------------------|-----|------------------|

| 0    | DMA要求0 | DREQ <sub>0</sub> | 入力  | DMAチャネル0の外部リクエスト |

|      | DMA終了0 | TEND <sub>0</sub> | 出力  | DMAチャネル0の転送終了    |

| 1    | DMA要求1 | DREQ <sub>1</sub> | 入力  | DMAチャネル1の外部リクエスト |

|      | DMA終了1 | TEND <sub>1</sub> | 出力  | DMAチャネル1の転送終了    |

【注】 ショートアドレスモードでは、チャネルAに対する外部リクエストは行えません。

#### 8.1.5 レジスタ構成

DMAのレジスタ構成を表8.3に示します。

表 8.3 レジスタ構成

| チャネル | アドレス*  | 名 称                       | 略 称     | R/W | 初期値  |

|------|--------|---------------------------|---------|-----|------|

| 0    | H'FF20 | メモリアドレスレジスタ0AR            | MAR0AR  | R/W | 不定   |

|      | H'FF21 | メモリアドレスレジスタ0AE            | MAR0AE  | R/W | 不定   |

|      | H'FF22 | メモリアドレスレジスタ0AH            | MAR0AH  | R/W | 不定   |

|      | H'FF23 | メモリアドレスレジスタ0AL            | MAR0AL  | R/W | 不定   |

|      | H'FF26 | I/Oアドレスレジスタ0A             | IOAR0A  | R/W | 不定   |

|      | H'FF24 | 転送カウントレジスタ0AH             | ETCR0AH | R/W | 不定   |

|      | H'FF25 | 転送カウントレジスタ0AL             | ETCR0AL | R/W | 不定   |

|      | H'FF27 | データトランスファ<br>コントロールレジスタ0A | DTCTR0A | R/W | H'00 |

|      | H'FF28 | メモリアドレスレジスタ0BR            | MAR0BR  | R/W | 不定   |

|      | H'FF29 | メモリアドレスレジスタ0BE            | MAR0BE  | R/W | 不定   |

|      | H'FF2A | メモリアドレスレジスタ0BH            | MAR0BH  | R/W | 不定   |

|      | H'FF2B | メモリアドレスレジスタ0BL            | MAR0BL  | R/W | 不定   |

|      | H'FF2E | I/Oアドレスレジスタ0B             | IOAR0B  | R/W | 不定   |

|      | H'FF2C | 転送カウントレジスタ0BH             | ETCR0BH | R/W | 不定   |

|      | H'FF2D | 転送カウントレジスタ0BL             | ETCR0BL | R/W | 不定   |

|      | H'FF2F | データトランスファ<br>コントロールレジスタ0B | DTCTR0B | R/W | H'00 |

| 1    | H'FF30 | メモリアドレスレジスタ1AR            | MAR1AR  | R/W | 不定   |

|      | H'FF31 | メモリアドレスレジスタ1AE            | MAR1AE  | R/W | 不定   |

|      | H'FF32 | メモリアドレスレジスタ1AH            | MAR1AH  | R/W | 不定   |

|      | H'FF33 | メモリアドレスレジスタ1AL            | MAR1AL  | R/W | 不定   |

|      | H'FF36 | I/Oアドレスレジスタ1A             | IOAR1A  | R/W | 不定   |

|      | H'FF34 | 転送カウントレジスタ1AH             | ETCR1AH | R/W | 不定   |

|      | H'FF35 | 転送カウントレジスタ1AL             | ETCR1AL | R/W | 不定   |

|      | H'FF37 | データトランスファ<br>コントロールレジスタ1A | DTCTR1A | R/W | H'00 |

|      | H'FF38 | メモリアドレスレジスタ1BR            | MAR1BR  | R/W | 不定   |

|      | H'FF39 | メモリアドレスレジスタ1BE            | MAR1BE  | R/W | 不定   |

|      | H'FF3A | メモリアドレスレジスタ1BH            | MAR1BH  | R/W | 不定   |

|      | H'FF3B | メモリアドレスレジスタ1BL            | MAR1BL  | R/W | 不定   |

|      | H'FF3E | I/Oアドレスレジスタ1B             | IOAR1B  | R/W | 不定   |

|      | H'FF3C | 転送カウントレジスタ1BH             | ETCR1BH | R/W | 不定   |

|      | H'FF3D | 転送カウントレジスタ1BL             | ETCR1BL | R/W | 不定   |

|      | H'FF3F | データトランスファ<br>コントロールレジスタ1B | DTCTR1B | R/W | H'00 |

【注】\* アドレスの下位16ビットを示しています。

## 8.2 各レジスタの説明(1) (ショートアドレスモード)

ショートアドレスモード転送は、チャネルA、B独立に行うことができます。

表8.4に示すようにDTCRAのDTS2A、DTS1Aビットにより各チャネルのショートアドレスモード転送を指定します。

表8.4 ショートアドレスモード、フルアドレスモードの設定

| チャネル | ビット2  | ビット1  | 説明                                             |

|------|-------|-------|------------------------------------------------|

|      | DTS2A | DTS1A |                                                |

| 0    | 1     | 1     | DMA Cチャネル0は、1チャネルのフルアドレスモード転送                  |

|      | 上記以外  |       | DMA Cチャネル0A、チャネル0Bは、各々独立動作で2チャネルのショートアドレスモード転送 |

| 1    | 1     | 1     | DMA Cチャネル1は、1チャネルのフルアドレスモード転送                  |

|      | 上記以外  |       | DMA Cチャネル1A、チャネル1Bは、各々独立動作で2チャネルのショートアドレスモード転送 |

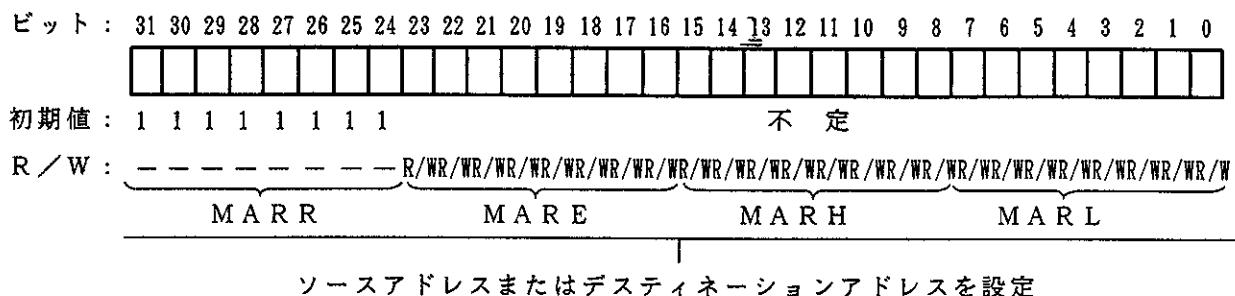

### 8.2.1 メモリアドレスレジスタ (MAR)

IMARは32ビットのリード／ライト可能なレジスタで、転送のソースアドレスまたはデスティネーションアドレスを指定します。転送方向は起動要因により自動的に決定されます。

MARは4本の8ビットレジスタMARR、MARE、MARCH、およびMARLにより構成されています。MARRは全ビットリザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

ビット : 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ソースアドレスまたはデスティネーションアドレスを設定

M A Rがソースアドレスレジスタとして機能するか、デスティネーションアドレスレジスタとして機能するかは、起動要因によって自動的に決定されます。起動要因がS C Iチャネル0の受信完了割込みの場合はデスティネーションアドレスレジスタとして、それ以外の場合にはソースアドレスレジスタとして機能します。

MARは1回のバイト転送またはワード転送のたびにインクリメント/デクリメントされ、ソースまたはデスティネーションのメモリアドレスを自動的に更新していきます。詳細は、「8.2.4 データransファコントロールレジスタ(DTCR)」を参照してください。

MARは、リセット、またはスタンバイモード時にイニシャライズされません。

### 8.2.2 I/Oアドレスレジスタ (I O A R)

I O A Rは8ビットのリード/ライト可能なレジスタで、転送のソースアドレスまたはデスティネーションアドレスを指定します。I O A Rはアドレスの下位8ビットを指定し、上位16ビットはすべて“1”(H'FFFF)となります。

| ビット: | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|---|---|---|---|---|---|---|---|

| 初期値: |   |   |   |   |   |   |   |   |

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

ソースアドレスまたはデスティネーションアドレスを設定

I O A Rがソースアドレスレジスタとして機能するか、デスティネーションアドレスレジスタとして機能するかは、起動要因によって自動的に決定されます。起動要因がS C Iチャネル0の受信完了割込みの場合はソースアドレスレジスタとして、それ以外の場合にはデスティネーションアドレスレジスタとして機能します。

I O A Rは転送によってインクリメント/デクリメントされず、固定されます。

I O A Rは、リセット、またはスタンバイモード時にイニシャライズされません。

### 8.2.3 転送カウントレジスタ (ETCR)

ETCRは16ビットのリード/ライト可能なレジスタで、転送回数の指定に使用します。このレジスタは、I/Oモードおよびアイドルモードと、リピートモードとでは機能が異なります。

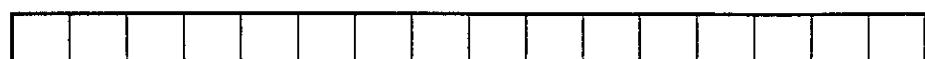

#### (1) I/Oモードまたはアイドルモード

ビット : 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

初期値 : 不定

R/W : R/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/WR/W

|

転送カウンタ

I/Oモードとアイドルモードでは、ETCRは16ビットの転送カウンタとして機能します。1回の転送を行うたびに、1だけデクリメントされカウンタ値がH'0000になると転送を終了します。

#### (2) リピートモード

ビット : 7 6 5 4 3 2 1 0

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

初期値 : 不定

R/W : R/WR/WR/WR/WR/WR/WR/WR/WR/W

|

ETCRH

転送カウンタ

ビット : 7 6 5 4 3 2 1 0

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

|  |  |  |  |  |  |  |  |  |

|--|--|--|--|--|--|--|--|--|

初期値 : 不定

R/W : R/WR/WR/WR/WR/WR/WR/WR/W

|

ETCR L

転送回数保持

リピードモードでは、ETCRHは8ビットの転送カウンタとして機能し、ETCR Lは転送回数を保持します。ETCRHは1回の転送を行うたびに1だけデクリメントされ、H'00になるとETCR Lの内容が転送されます。以降この動作を繰り返して転送が行われます。

ETCRは、リセット、またはスタンバイモード時にイニシャライズされません。

#### 8.2.4 データransファコントロールレジスタ (D T C R)

DTCRは8ビットのリード／ライト可能なレジスタで、DMACの各チャネルの動作を制御します。

D T C R はリセット、またはスタンバイモード時にH'00にイニシャライズされます。

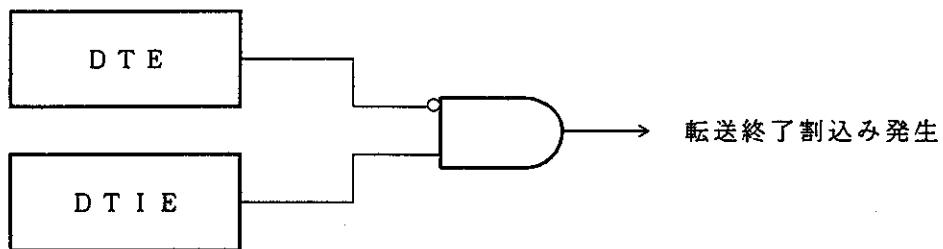

### ビット7：データトランスマネーブル (DTE)

当該チャネルのデータ転送を許可／禁止します。DTEビットを“1”にセットすると、そのチャネルは転送要求待ち状態となり、DTS2～DTS0ビットで指定された起動要因によりデータ転送が行われます。本ビットが“0”的とき、当該チャネルは停止状態となり転送要求を受け付けません。DTEビットは、DTE = “0”的状態をリードした後、“1”をライトしたとき“1”にセットされます。

| ビット7 | 説明                                                       |

|------|----------------------------------------------------------|

| DTE  |                                                          |

| 0    | データ転送禁止。I/Oモードとアイドルモードでは、指定された回数の転送を終了したとき、“0”にクリア (初期値) |

| 1    | データ転送許可                                                  |

DTE = “1”的状態で、本ビットが“0”にクリアされるとCPUに割込みを要求します。

### ビット6：データトランスマニフェザイズ (DTSZ)

1回に転送されるデータサイズを選択します。

| ビット6 | 説明             |

|------|----------------|

| DTSZ |                |

| 0    | バイトサイズ転送 (初期値) |

| 1    | ワードサイズ転送       |

### ビット5：データトランスマニクリメント／デクリメント (DTID)

I/Oモードまたはリピートモードの場合、データ転送後のMARのインクリメント／デクリメントを選択します。

| ビット5 | 説明                                                                              |

|------|---------------------------------------------------------------------------------|

| DTID |                                                                                 |

| 0    | データ転送後MARをインクリメント<br>(1) DTSZ = “0”的とき、転送後MARを+1<br>(2) DTSZ = “1”的とき、転送後MARを+2 |

| 1    | データ転送後MARをデクリメント<br>(1) DTSZ = “0”的とき、転送後MARを-1<br>(2) DTSZ = “1”的とき、転送後MARを-2  |

アイドルモードの場合、MARはインクリメントもデクリメントもされません。

#### ビット4：リピートイネーブル (RPE)

データ転送をI/Oモード、アイドルモード、またはリピートモードで行うかを選択します。

| ビット4 | ビット3 | 説明                 |

|------|------|--------------------|

| RPE  | DTIE |                    |

| 0    | 0    | I/Oモードで転送<br>(初期値) |

|      | 1    |                    |

| 1    | 0    | リピートモードで転送         |

|      | 1    | アイドルモードで転送         |

I/Oモード、アイドルモード、およびリピートモードの動作については、「8.4.2 I/Oモード」、「8.4.3 アイドルモード」、および「8.4.4 リピートモード」を参照してください。

#### ビット3：データransファインタラプトイネーブル (DTIE)

DTEビットが“0”にクリアされたとき、DTEビットによる割込み (DEN) 要求を許可／禁止します。

| ビット3 | 説明                             |

|------|--------------------------------|

| DTIE |                                |

| 0    | DTEによる割込み (DEN) 要求を禁止<br>(初期値) |

| 1    | DTEによる割込み (DEN) 要求を許可          |

ビット2～0：データトランスマセレクト (DTS2～DTS0)

データ転送の起動要因を選択します。チャネルAとチャネルBでは一部指定内容が異なります。\*

【注】\*「8.3.4 データトランスマコントロールレジスタ (DTCR)」を参照してください。

| ビット2<br>DTS2 | ビット1<br>DTS1 | ビット0<br>DTS0 | 説明                                                         |

|--------------|--------------|--------------|------------------------------------------------------------|

| 0            | 0            | 0            | ITUチャネル0のコンペアマッチ／インプットキャプチャA割込みで起動<br>(初期値)                |

|              |              | 1            | ITUチャネル1のコンペアマッチ／インプットキャプチャA割込みで起動                         |

|              | 1            | 0            | ITUチャネル2のコンペアマッチ／インプットキャプチャA割込みで起動                         |

|              |              | 1            | ITUチャネル3のコンペアマッチ／インプットキャプチャA割込みで起動                         |

| 1            | 0            | 0            | SCIチャネル0の送信データソブティ割込みで起動                                   |

|              |              | 1            | SCIチャネル0の受信データフル割込みで起動                                     |

|              | 1            | 0            | DREQ端子の立下がりエッジ入力で起動(チャネルBの場合)<br>フルアドレスモード転送を指定(チャネルAの場合)  |

|              |              | 1            | DREQ端子の"Low"レベル入力で起動(チャネルBの場合)<br>フルアドレスモード転送を指定(チャネルAの場合) |

内部割込みによる起動では、複数のチャネル間で同一の起動要因を指定することができます。この場合、チャネル間の優先順位に従い優先順位の高いチャネルから起動されます。優先順位については、「8.4.9 DMA複数チャネルの動作」を参照してください。

転送許可の状態 (DTE = "1") では、DMAの起動要因に選択された割込みは、CPUに対して割込みを要求しません。

### 8.3 各レジスタの説明(2) (フルアドレスモード)

フルアドレスモード転送は、チャネルAとチャネルBを組み合わせて行います。フルアドレスモード転送の設定については、表8.4を参照してください。

### 8.3.1 メモリアドレスレジスタ (MAR)

MARは32ビットのリード／ライト可能なレジスタで、MARAは転送のソースアドレスレジスタとして、MAR Bはデスティネーションアドレスレジスタとして機能します。

MARは4本の8ビットレジスタMARR、MARE、MARCH、およびMARLにより構成されています。MARRはすべてリザーブビットです。リードすると常に“1”が読み出されます。ライトは無効です。

MAR は 1 回のバイト転送またはワード転送のたびにインクリメント／デクリメントされ、ソースまたはデスティネーションのメモリアドレスを自動的に更新することができます。詳細は、「8.3.4 データransファントロールレジスタ (DTCR)」を参照してください。

MARは、リセット、またはスタンバイモード時にイニシャライズされません。

### 8.3.2 I/Oアドレスレジスタ (I OAR)

I/O ARはフルアドレスモード転送では使用しません。

### 8.3.3 転送カウントレジスタ (ETCR)

ETCRは16ビットのリード/ライト可能なレジスタで、転送回数の指定に使用します。このレジスタは、ノーマルモードとブロック転送モードとでは機能が異なります。

### (1) ノーマルモード

① E T C R A

バ ッ ド ト : 1 5 1 4 1 3 1 2 1 1 1 0 9 8 7 6 5 4 3 2 1 0

初期值： 不定

### 転送カウンタ

② E T C R B

ETCRBはノーマルモードでは使用しません。

ノーマルモードでは、ETCR Aは16ビットの転送カウンタとして機能します。1回の転送を行うたびに1だけデクリメントされ、カウンタ値がH'0000になると転送を終了します。このとき、ETCR Bは使用されません。

## (2) ブロック転送モード

① E T C R A

ビット : 7 6 5 4 3 2 1 0

初期値： 不 定

R / W : R / WR / W

# ETCRAH

### ブロックサイズカウンタ

ビット: 7 6 5 4 3 2 1 0

初期値： 不 定

R / W : R / WR / W

ETCRAI

## ブロックサイズ保持

② . E T C R B

初期值： 不定

### ブロック転送カウンタ

ブロック転送モードでは、ETCRAHは8ビットのブロックサイズカウンタとして機能し、ETCRALはブロックサイズを保持します。ETCRAHは、1バイトまたは1ワードの転送を行うたびに1だけデクリメントされ、H'00になるとETCRALの内容が転送されます。したがって、ETCRAHとETCRALにブロックサイズを初期設定することにより、任意のバイト数またはワード数のブロック転送を繰り返し行うことができます。

また、ブロック転送モードではETCRBは16ビットのブロック転送カウンタとして機能します。一回のブロック転送を行うたびに1だけデクリメントされ、カウンタ値がH'0000になると転送を終了します。

ETCRは、リセット、またはスタンバイモード時にはイニシャライズされません。

#### 8.3.4 データトランスマニコントロールレジスタ (DTCR)

D T C R は 8 ビットのリード／ライト可能なレジスタで、D M A C の各チャネルの動作を制御します。D T C R A の D T S 2 A 、 D T S 1 A ビットをいずれも “ 1 ” にセットすると当該チャネルはフルアドレスモードとなります。フルアドレスモードでは D T C R A と D T C R B では機能が異なります。

(1) D T C R A

D T C R A はリセット、またはスタンバイモード時にH'00にイニシャライズされます。

### ビット7：データトランスマティネーブル (DTE)

DTCRBのDTMEビットとともに当該チャネルのデータ転送の許可／禁止を制御します。DTMEビットとDTEビットをいずれも“1”にセットすると、そのチャネルは転送許可状態となります。オートリクエストを指定したときはただちにデータ転送を開始し、その他のときは転送要求待ち状態となります。指定された回数の転送を終了するとDTEビットは自動的に“0”にクリアされます。本ビットが“0”にクリアされているとき、当該チャネルは停止状態となり転送要求を受け付けません。DTEビットは“0”的状態をリードした後、“1”をライトしたとき“1”にセットされます。

| ビット7 | 説明                                          |

|------|---------------------------------------------|

| DTE  |                                             |

| 0    | データ転送禁止 (指定された回数の転送を終了したとき“0”にクリア)<br>(初期値) |

| 1    | データ転送許可                                     |

DTE = “1”的状態で、本ビットが“0”にクリアされるとCPUに割込みを要求します。

### ビット6：データトランスマティサイズ (DTSZ)

1回に転送されるデータサイズを選択します。

| ビット6 | 説明                |

|------|-------------------|

| DTSZ |                   |

| 0    | バイトサイズ転送<br>(初期値) |

| 1    | ワードサイズ転送          |

### ビット5：ソースアドレスインクリメント／デクリメント (SAID)

### ビット4：ソースアドレスインクリメント／デクリメントイネーブル (SAIDE)

データ転送時、ソースアドレスレジスタMARAをインクリメントするかデクリメントするか、または固定とするかを指定します。

| ビット5 | ビット4  | 説明                                                                                       |

|------|-------|------------------------------------------------------------------------------------------|

| SAID | SAIDE |                                                                                          |

| 0    | 0     | MARA固定<br>(初期値)                                                                          |

|      | 1     | データ転送後MARAをインクリメント<br>(1) DTSZ = “0”的とき、データ転送後MARAを+1<br>(2) DTSZ = “1”的とき、データ転送後MARAを+2 |

| 1    | 0     | MARA固定                                                                                   |

|      | 1     | データ転送後MARAをデクリメント<br>(1) DTSZ = “0”的とき、データ転送後MARAを-1<br>(2) DTSZ = “1”的とき、データ転送後MARAを-2  |

### ビット3：データトランスマインタラプトイネーブル (D T I E)

D T Eビットが“0”にクリアされたとき、D T Eによる割込み (D E N D) 要求を許可／禁止します。

| ビット3    | 説明                          |       |

|---------|-----------------------------|-------|

| D T I E |                             |       |

| 0       | D T Eによる割込み (D E N D) 要求を禁止 | (初期値) |

| 1       | D T Eによる割込み (D E N D) 要求を許可 |       |

### ビット2、1：データトランスマインタラプトイネーブル (D T S 2 A、D T S 1 A)

D T S 2 A、D T S 1 Aビットをいずれも“1”にセットしたとき、当該チャネルはフルアドレスモードとなります。

### ビット0：データトランスマインタラプトイネーブル (D T S 0 A)

D M A Cをノーマルモードで動作させるか、ブロック転送モードで動作させるかを選択します。

| ビット0      | 説明           |       |

|-----------|--------------|-------|

| D T S 0 A |              |       |

| 0         | ノーマルモードで動作   | (初期値) |

| 1         | ブロック転送モードで動作 |       |

ノーマルモード、ブロック転送モードの動作については、「8.4.5 ノーマルモード」、「8.4.6 ブロック転送モード」を参照してください。

(2) D T C R B

| ビット: | 7    | 6 | 5    | 4     | 3   | 2     | 1     | 0     |

|------|------|---|------|-------|-----|-------|-------|-------|

|      | DTME | — | DAID | DAIDE | TMS | DTS2B | DTS1B | DTS0B |

| 初期値: | 0    | 0 | 0    | 0     | 0   | 0     | 0     | 0     |

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

データトランスマスファセレクト 2～0 B

データ転送の起動要因を設定するビットです。

トランスマスファモードセレクト

ブロック転送モード時、ソース側とデスティネーション側のどちらをブロックエリアとするかを選択するビットです。

デスティネーションアドレスインクリメント/デクリメント

デスティネーションアドレスインクリメント/

デクリメントイネーブル

データ転送時 M A R B をインクリメントするかデクリメントするか、または固定とするかを選択するビットです。

リザーブビット

データトランスマスファマスティネーブル

D T E ビットとともに転送の許可/禁止を制御するビットです。

割込みが発生すると “0” にクリアされます。

D T C R B は、リセット、またはスタンバイモード時に、H'00にイニシャライズされます。

### ビット7：データransファマスタイル（DTME）

DT CRAのDTEビットとともに当該チャネルのデータ転送の許可／禁止を制御します。DTMEビットとDTEビットをいずれも“1”にセットすると、そのチャネルは転送許可状態となります。NMI割込みが発生したときDTMEビットは“0”にクリアされ、転送を中断してCPUにバス権を移します。その後、本ビットを“1”にセットすると中断された転送が再開されます。ただし、ブロック転送モード時の動作については「8.6.6 NMI割込みとブロック転送モード」を参照してください。

DTMEビットは、DTME = “0”的状態をリードした後、“1”をライトすると“1”にセットされます。

| ビット7 | 説明                           |       |

|------|------------------------------|-------|

| DTME |                              |       |

| 0    | データ転送禁止。NMI割込みが発生したとき“0”にクリア | (初期値) |

| 1    | データ転送許可                      |       |

—

### ビット6：リザーブビット

リザーブビットです。リード／ライト可能です。

### ビット5：デスティネーションアドレスインクリメント／デクリメント（DAID）

### ビット4：デスティネーションアドレスインクリメント／デクリメントイネーブル（DAIDE）

データ転送時、MAR Bをインクリメントするかデクリメントするか、または固定とするかを指定します。

| ビット5 | ビット4  | 説明                                                                                          |

|------|-------|---------------------------------------------------------------------------------------------|

| DAID | DAIDE |                                                                                             |

| 0    | 0     | MAR B固定                                                                                     |

|      | 1     | データ転送後MAR Bをインクリメント<br>(1) DTSZ = “0”的とき、データ転送後MAR Bを+1<br>(2) DTSZ = “1”的とき、データ転送後MAR Bを+2 |

| 1    | 0     | MAR B固定                                                                                     |

|      | 1     | データ転送後MAR Bをデクリメント<br>(1) DTSZ = “0”的とき、データ転送後MAR Bを-1<br>(2) DTSZ = “1”的とき、データ転送後MAR Bを-2  |

ビット3: トランスマードセレクト (TMS)

ブロック転送モード時、ソース側とデスティネーション側のどちらをブロックエリアとして転送するかを選択します。

| ビット3 | 説明                                          |

|------|---------------------------------------------|

| TMS  |                                             |

| 0    | ブロック転送モード時、デスティネーション側をブロックエリアとして転送<br>(初期値) |

| 1    | ブロック転送モード時、ソース側をブロックエリアとして転送                |

ビット2～0: データトランスマードセレクト 2～0 B (DTS2B～DTS0B)

データ転送の起動要因を選択します。ノーマルモードとブロック転送モードでは指定できる起動要因が異なります。

(ノーマルモード)

| ビット2  | ビット1  | ビット0  | 説明                       |

|-------|-------|-------|--------------------------|

| DTS2B | DTS1B | DTS0B |                          |

| 0     | 0     | 0     | オートリクエスト (バーストモード) (初期値) |

|       |       | 1     | 使用できません。                 |

|       | 1     | 0     | オートリクエスト (サイクルスチールモード)   |

|       |       | 1     | 使用できません。                 |

| 1     | 0     | 0     | 使用できません。                 |

|       |       | 1     | 使用できません。                 |

|       | 1     | 0     | DREQ端子の立下がりエッジ入力で起動      |

|       |       | 1     | DREQ端子の“Low”レベル入力で起動     |

## (ブロック転送モード)

| ビット2<br>D T S 2 B | ビット1<br>D T S 1 B | ビット0<br>D T S 0 B | 説明                                                       |

|-------------------|-------------------|-------------------|----------------------------------------------------------|

| 0                 | 0                 | 0                 | I T U チャネル 0 のコンペアマッチ / インプットキ<br>ャブチャ A 割込みで起動<br>(初期値) |

|                   |                   | 1                 | I T U チャネル 1 のコンペアマッチ / インプットキ<br>ャブチャ A 割込みで起動          |

|                   | 1                 | 0                 | I T U チャネル 2 のコンペアマッチ / インプットキ<br>ャブチャ A 割込みで起動          |

|                   |                   | 1                 | I T U チャネル 3 のコンペアマッチ / インプットキ<br>ャブチャ A 割込みで起動          |

| 1                 | 0                 | 0                 | 使用できません。                                                 |

|                   |                   | 1                 | 使用できません。                                                 |

|                   | 1                 | 0                 | <u>DREQ</u> 端子の立下がりエッジ入力で起動                              |

|                   |                   | 1                 | 使用できません。                                                 |

内部割込みによる起動では、複数のチャネル間で同一の起動要因を指定することが可能です。この場合、チャネル間の優先順位に従い優先順位の高いチャネルから起動されます。優先順位については、「8.4.9 D M A C 複数チャネルの動作」を参照してください。

## 8.4 動作説明

### 8.4.1 概要

D M A C のモード一覧を表 8.5 に示します。

表 8.5 モード一覧

| 転送モード       | 起動要因                                                                         | 備考                                                                                               |

|-------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| ショートアドレスモード | (1) I/O モード<br>(2)アイドルモード<br>(3)リピートモード                                      | I T U チャネル 0 ~ 3 のコンペアマッチ / インプットキャプチャ A 割込み<br>S C I チャネル 0 の送信データエンプティ / 受信データフル割込み<br>外部リクエスト |

|             | ・最大 4 チャネルを独立に動作可能<br>・外部リクエストはチャネル B のみ可能                                   |                                                                                                  |

|             |                                                                              |                                                                                                  |

| フルアドレスモード   | (4)ノーマルモード                                                                   | オートリクエスト<br>外部リクエスト                                                                              |

|             | ・チャネル A、B を組み合わせて最大 2 チャネルを動作可能<br>・オートリクエストではバーストモード転送 / サイクルスチールモード転送の選択可能 |                                                                                                  |

|             |                                                                              |                                                                                                  |

|             | (5)ロック転送モード                                                                  | I T U チャネル 0 ~ 3 のコンペアマッチ / インプットキャプチャ A 割込み<br>外部リクエスト                                          |

各モードの動作概要を以下に示します。

#### (1) I/O モード

一回の転送要求に対して 1 バイトまたは 1 ワードずつ、指定された回数だけ転送を行います。指定された回数の転送が終了すると C P U に割込みを要求することができます。アドレスの一方は 24 ビット、他方は 8 ビットで指定します。転送方向は起動要因により自動的に決定されます。

#### (2) アイドルモード

一回の転送要求に対して 1 バイトまたは 1 ワードずつ、指定された回数だけ転送を行います。指定された回数の転送が終了すると C P U に割込みを要求することができます。アドレスの一方は 24 ビット、他方は 8 ビットで指定します。アドレスは固定になっています。転送方向は起動要因により自動的に決定されます。

### (3) リピートモード

一回の転送要求に対して1バイトまたは1ワードずつ、指定された回数だけ転送を行います。指定された回数の転送が終了するとアドレスと転送カウンタを設定値に戻し、動作を継続します。C P Uに対して割込みは要求しません。アドレスの一方は24ビット、他方は8ビットで指定します。転送方向は起動要因により自動的に決定されます。

### (4) ノーマルモード

#### ① オートリクエスト

レジスタ設定のみでD M A Cを起動し、指定された回数の転送が完了するまで転送を継続します。転送が完了するとC P Uに割込みを要求することができます。アドレスはいずれも24ビットで指定します。

- ・サイクルスチールモード 1バイトまたは1ワード転送ごとにバスを一旦他のバスマスターに解放します。

- ・バーストモード 他の優先順位の高いバスマスターからのバス権要求がなければ、指定された転送が完了するまでバスを専有して転送を行います。

#### ② 外部リクエスト

一回の転送要求に対して1バイトまたは1ワードずつ、指定された回数だけ転送を行います。指定された回数の転送が終了するとC P Uに割込みを要求することができます。アドレスはいずれも24ビットで指定します。

### (5) ブロック転送モード

一回の転送要求に対して指定されたブロックサイズのブロック転送を行い、これを転送要求のあるごとに指定された回数だけ繰り返します。一回のブロック転送が終了するたびに一方のアドレスは設定値に戻ります。指定された回数のブロック転送が終了するとC P Uに割込みを要求することができます。アドレスはいずれも24ビットで指定します。

## 8.4.2 I/Oモード

I/Oモードは各チャネル独立に設定可能です。

I/Oモードでは、一回の転送要求に対して1バイトまたは1ワードずつ転送を行い、これを指定された回数だけ実行します。アドレスの一方はMAR、他方はIOARで指定します。転送方向は起動要因によって自動的に決定され、SCIチャネル0の受信データフル割込みで起動される場合はIOARで指定されるアドレスからMARで指定されるアドレスへ、それ以外の場合はMARで指定されるアドレスからIOARで指定されるアドレスへ転送されます。

I/Oモード時のレジスタの機能を表8.6に示します。

表8.6 I/Oモード時のレジスタの機能

| 対象レジスタ                                                                                        | 機能                  |                   | 初期設定値            | 動作                               |

|-----------------------------------------------------------------------------------------------|---------------------|-------------------|------------------|----------------------------------|

|                                                                                               | SCI0受信データフル割込みによる起動 | その他の起動            |                  |                                  |

| 23 0<br>     | デステイネーションアドレスレジスタ   | ソースアドレスレジスタ       | 転送先または転送元の先頭アドレス | 一回の転送ごとにインクリメント/デクリメント           |

| 23 7 0<br> | ソースアドレスレジスタ         | デステイネーションアドレスレジスタ | 転送元または転送先のアドレス   | 固定                               |

| 15 0<br>   | 転送カウンタ              |                   | 転送回数             | 一回の転送ごとにデクリメント<br>H'0000になると転送終了 |

### 《記号説明》

MAR : メモリアドレスレジスタ

IOAR : I/Oアドレスレジスタ

ETCR : 転送カウントレジスタ

転送元および転送先アドレスは、MARとIOARによって指定します。MARには転送元または転送先の先頭アドレスを24ビットで指定します。MARは1回のバイト転送またはワード転送のたびにインクリメント/デクリメントされます。IOARはアドレス下位8ビットを指定し、上位16ビットは“1”となります。IOARはインクリメントもデクリメントもされません。

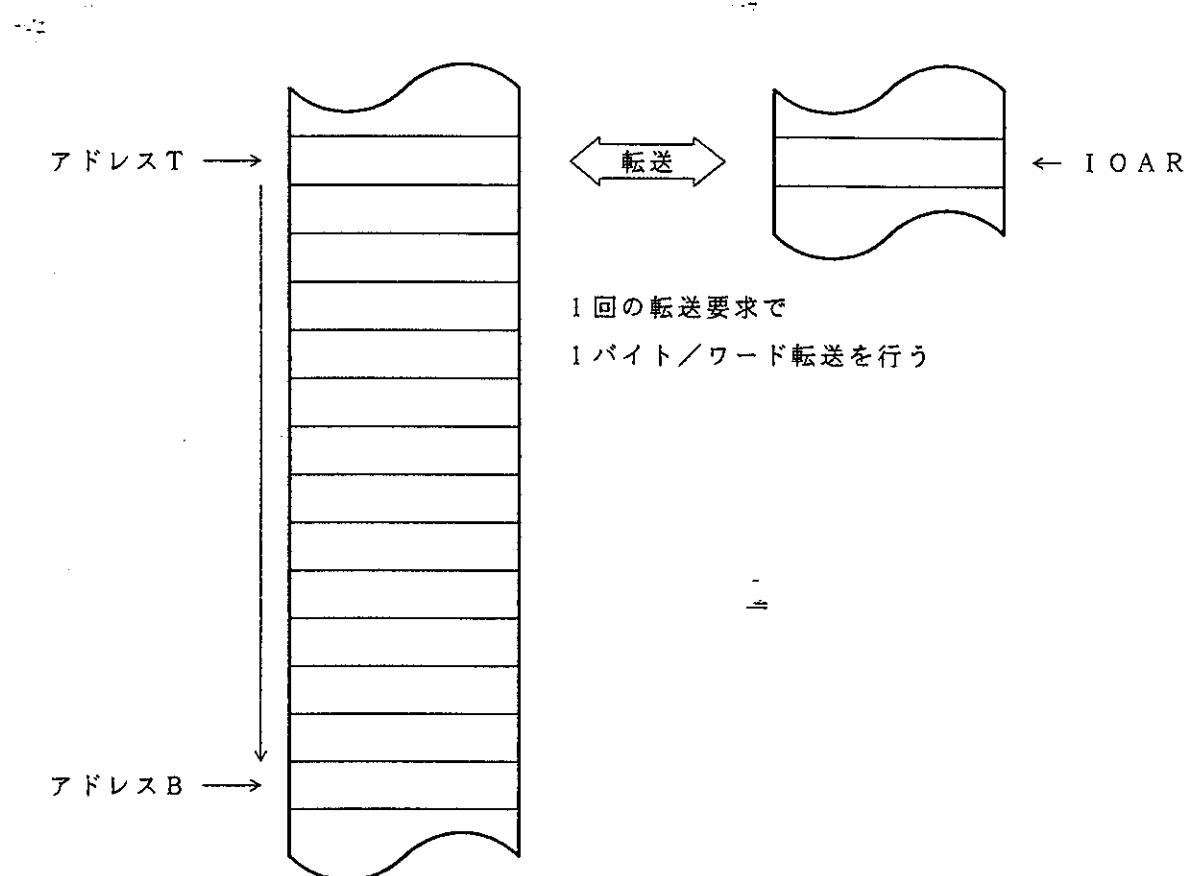

図 8.2 に I/O モードの動作を示します。

《記号説明》

L = M A R の初期設定値

N = E T C R の初期設定値

アドレス T = L

アドレス B =  $L + (-1)^{DTID} \cdot (2^{DTSZ} \cdot N - 1)$

図 8.2 I/O モードの動作

転送回数は E T C R より 16 ビットで指定します。 E T C R は一回の転送を行うたびに 1 だけデクリメントされ、 H' 0000 となったときに D T E ビットをクリアして転送を終了します。このとき、 D T I E ビットが “ 1 ” にセットされていると C P U に割込みを要求します。

なお、転送回数の最大値は E T C R に H' 0000 を設定したときで、 65536 となります。

転送要求（起動要因）には、 I T U チャネル 0 ～ 3 のコンペアマッチ／インプットキャプチャ A 割込み、 S C I チャネル 0 の送信データエンプティ、受信データフル割込み、および外部リクエストがあります。

設定の詳細は「 8.2.4 データransファコントロールレジスタ（ D T C R ）」を参照してください。

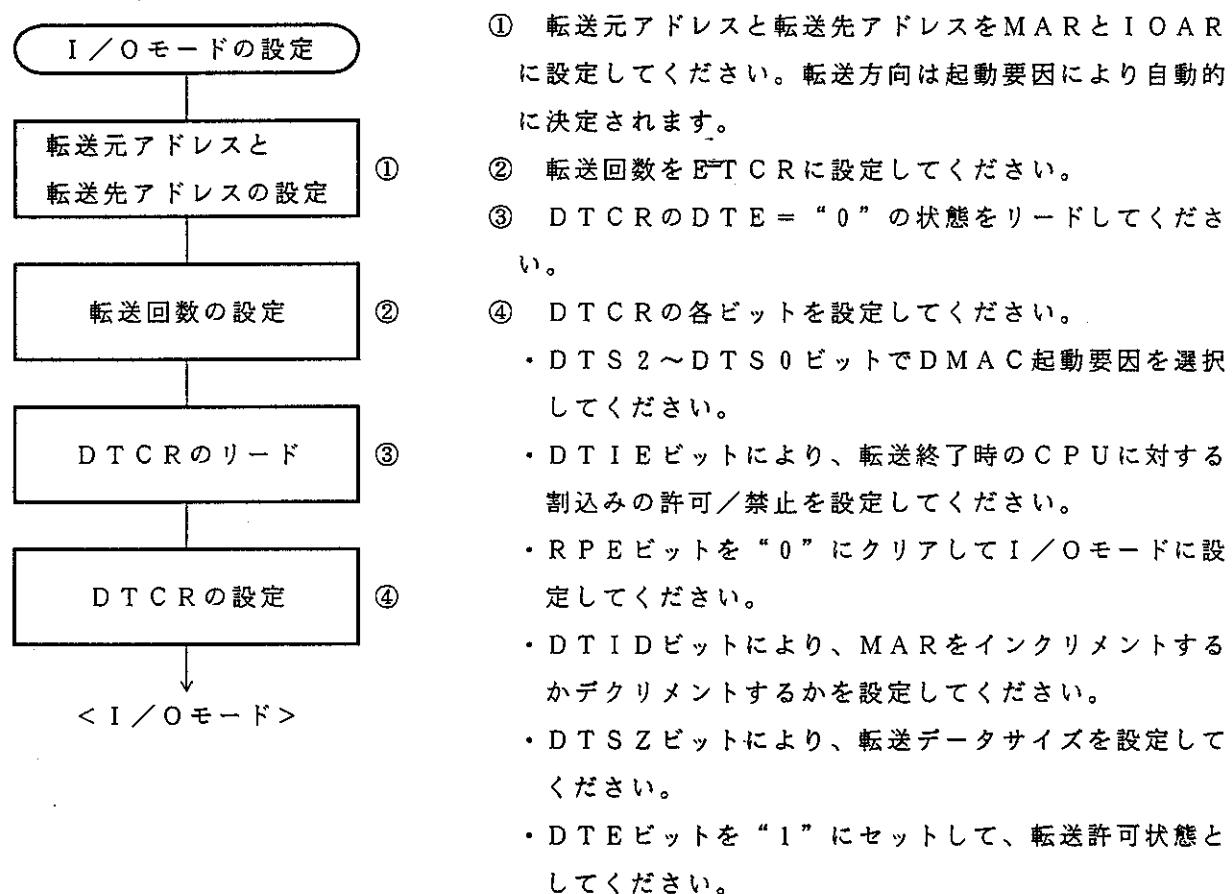

I / O モードの設定手順例を図 8.3 に示します。

図 8.3 I / O モードの設定手順例

### 8.4.3 アイドルモード

アイドルモードは各チャネル独立に設定可能です。

アイドルモードでは、一回の転送要求に対して1バイトまたは1ワードずつ転送を行い、これを指定された回数だけ実行します。アドレスの一方はMAR、他方はIOARで指定します。転送方向は起動要因によって自動的に決定され、SCIチャネル0の受信データフル割込みで起動される場合はIOARで指定されるアドレスからMARで指定されるアドレスへ、それ以外の場合はMARで指定されるアドレスからIOARで指定されるアドレスへ転送されます。

アイドルモード時のレジスタの機能を表8.7に示します。

表8.7 アイドルモード時のレジスタの機能

| 対象レジスタ                                                                                        | 機能                  |                   | 初期設定値          | 動作                                |

|-----------------------------------------------------------------------------------------------|---------------------|-------------------|----------------|-----------------------------------|

|                                                                                               | SCI0受信データフル割込みによる起動 | その他の起動            |                |                                   |

| 23 0<br>     | デスティネーションアドレスレジスタ   | ソースアドレスレジスタ       | 転送先または転送元のアドレス | 固定                                |

| 23 7 0<br> | ソースアドレスレジスタ         | デスティネーションアドレスレジスタ | 転送元または転送先のアドレス | 固定                                |

| 15 0<br>   | 転送カウンタ              |                   | 転送回数           | 一回の転送ごとにインクリメント<br>H'0000になると転送終了 |

#### 《記号説明》

MAR : メモリアドレスレジスタ

IOAR : I/Oアドレスレジスタ

ETCR : 転送カウントレジスタ

転送元および転送先アドレスは、MARとIOARによって指定します。MARには転送元または転送先のアドレスを24ビットで指定します。IOARはアドレス下位8ビットを指定し、上位16ビットは“1”となります。MAR、IOARはインクリメントもデクリメントもされません。

図 8.4 にアイドルモードの動作を示します。

図 8.4 アイドルモードの動作

転送回数は E T C R より 16 ビットで指定します。 E T C R は一回の転送を行ったびに 1 だけデクリメントされ、 H' 0000 となつたときに D T E ビットをクリアして転送を終了します。このとき、 C P U に割込みを要求します。

なお、転送回数の最大値は E T C R に H' 0000 を設定したときで、 65536 となります。

転送要求（起動要因）には、 I T U チャネル 0 ～ 3 のコンペアマッチ／インプットキャプチャ割込み、 S C I チャネル 0 の送信データエンプティ、受信データフル割込み、および外部リクエストがあります。

設定の詳細は「 8.2.4 データトランスファコントロールレジスタ（ D T C R ）」を参照してください。

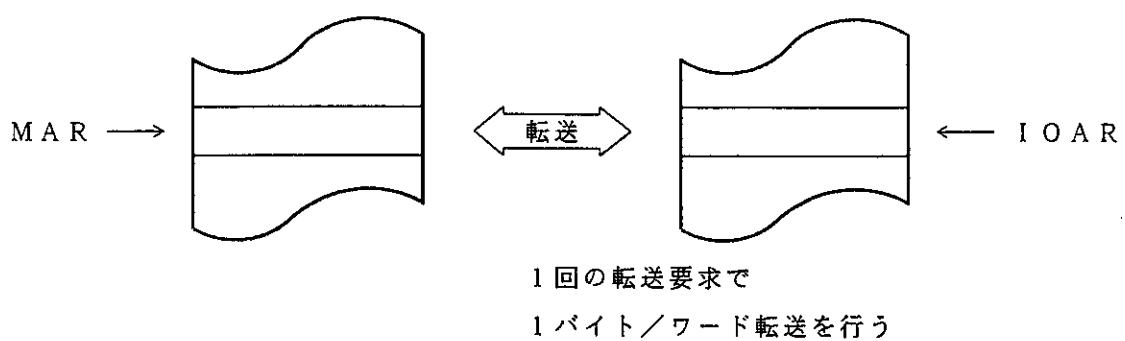

アイドルモードの設定手順例を図 8.5 に示します。

図 8.5 アイドルモードの設定手順例

#### 8.4.4 リピートモード

リピートモードは I T U のコンペアマッチなどに同期して、テーブル上のデータをプログラマブルタイミングパターンコントローラ (T P C) に対して繰り返し転送するのに便利なモードです。各チャネル独立に設定可能です。

リピートモードでは、I/Oモードと同様に一回の転送要求に対して1バイトまたは1ワードずつ転送を行い、これを指定された回数だけ実行します。アドレスの一方はMAR、他方はIOARで指定します。指定された回数の転送終了時、MAR、およびETCRHの内容が初期設定値となり、さらに動作を継続します。転送方向は起動要因によって自動的に決定され、SCIチャネル0の受信データフル割込みで起動される場合はIOARで指定されるアドレスからMARで指定されるアドレスへ、それ以外の場合はMARで指定されるアドレスからIOARで指定されるアドレスへ転送されます。

リピートモード時のレジスタの機能を表8.8に示します。

表8.8 リピートモード時のレジスタの機能

| 対象レジスタ                  | 機能                  |                   | 初期設定値            | 動作                                             |

|-------------------------|---------------------|-------------------|------------------|------------------------------------------------|

|                         | SCI0受信データフル割込みによる起動 | その他の起動            |                  |                                                |

| 23 0<br>  MAR           | デステイネーションアドレスレジスタ   | ソースアドレスレジスタ       | 転送先または転送元の先頭アドレス | 一回の転送ごとにインクリメント/デクリメントETCRHがH'0000になると初期設定値を回復 |

| 23 7 0<br>"1" 固定   IOAR | ソースアドレスレジスタ         | デステイネーションアドレスレジスタ | 転送元または転送先のアドレス   | 固定                                             |

| 7 0<br>ETCRH<br>↑       | 転送カウンタ              |                   | 転送回数             | 一回の転送ごとにデクリメントH'0000になるとETCRLの内容を格納            |

| 7 0<br>ETCRL            | 転送回数保持              |                   | 転送回数             | 固定                                             |

#### 《記号説明》

MAR : メモリアドレスレジスタ

IOAR : I/Oアドレスレジスタ

ETCR : 転送カウントレジスタ

リピートモードではETCRHを転送カウンタとし、ETCRLは転送回数保持に使用します。ETCRHは1回の転送を行うたびに1だけデクリメントされ、H'00になるとETCRLの値が格納されます。また、MARはDTCRのDTSZビットおよびDTIDビットの値に応じて初期設定値を回復します。このときのMARの動作は次のようにになります。

$$MAR \leftarrow MAR - (-1)^{DTID} \cdot 2^{DTSZ} \cdot ETCRL$$

ETCRHとETCRLには同じ値を初期設定してください。

リピートモードではCPUがDTEビットを“0”にクリアするまで転送を繰り返します。DTEビットを“0”にクリアした後、CPUがDTEビットを“1”にセットすると、クリアした時点の状態から転送を再開します。CPUに対して割込み要求は発生しません。

転送元および転送先アドレスは、I/Oモードと同様、MARとIOARによって指定します。MARには転送元または転送先の先頭アドレスを24ビットで指定します。IOARにはアドレス下位8ビットを指定し、上位16ビットは“1”となります。IOARは転送によりインクリメントもデクリメントもされません。

図8.6にリピートモードの動作を示します。

図8.6 リピートモードの動作

転送回数は E T C R H、E T C R L に 8 ビットで指定します。転送回数の最大値は E T C R H、E T C R L にそれぞれ H'FF を設定したときで、255 となります。

転送要求（起動要因）には、I T U チャネル 0～3 のコンペアマッチ／インプットキャプチャ A 割込み、S C I チャネル 0 の送信データエンプティ、受信データフル割込み、および外部リクエストがあります。

設定の詳細は「8.2.4 データトランスマニコントロールレジスタ (D T C R)」を参照してください。

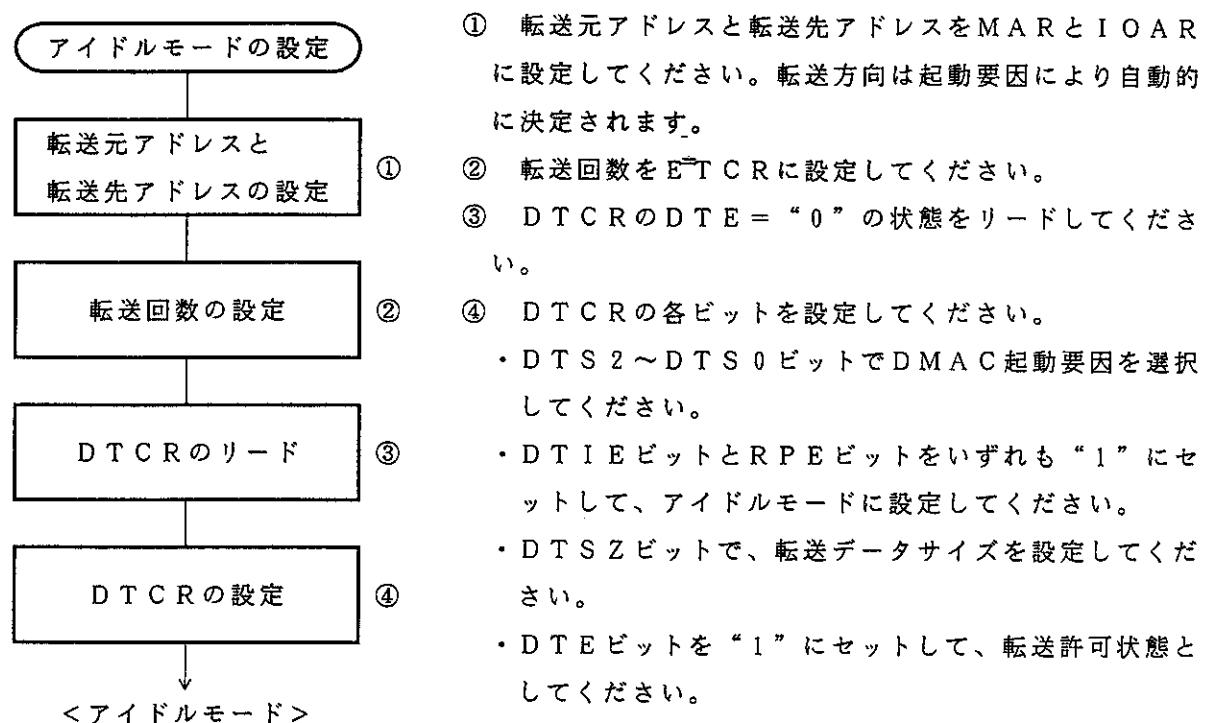

リピートモードの設定手順例を図 8.7 に示します。

- ① 転送元先頭アドレスと転送先先頭アドレスを M A R と I O A R に設定してください。転送方向は起動要因により自動的に決定されます。

- ② 転送回数を E T C R H と E T C R L の両方に設定してください。

- ③ D T C R の D T E = “0” の状態をリードしてください。

- ④ D T C R の各ビットを設定してください。

- ・ D T S 2～D T S 0 ビットにより D M A C 起動要因を選択してください。

- ・ D T I E ビットを “0” にクリア、R P E ビットを “1” にセットしてリピートモードに設定してください。

- ・ D T I D ビットにより、M A R をインクリメントするかデクリメントするかを設定してください。

- ・ D T S Z ビットにより、転送データサイズを設定してください。

- ・ D T E ビットを “1” にセットして、転送許可状態としてください。

図 8.7 リピートモードの設定手順例

#### 8.4.5 ノーマルモード

ノーマルモードは、チャネルA、Bを組み合わせて転送を行います。

ノーマルモードでは、一回の転送要求に対して1バイトまたは1ワードずつ転送を行い、これを指定された回数だけ実行します。アドレスはMARA、MAR Bで指定します。

ノーマルモード時のレジスタの機能を表8.9に示します。

表8.9 ノーマルモード時のレジスタの機能

| 対象レジスタ        | 機能                | 初期設定値     | 動作                          |

|---------------|-------------------|-----------|-----------------------------|

| 23 0<br>MARA  | ソースアドレスレジスタ       | 転送元先頭アドレス | 1回の転送ごとにインクリメント/デクリメントまたは固定 |

| 23 0<br>MAR B | デスティネーションアドレスレジスタ | 転送先先頭アドレス | 1回の転送ごとにインクリメント/デクリメントまたは固定 |

| 15 0<br>ETCRA | 転送カウンタ            | 転送回数      | 1回の転送ごとにデクリメント              |

##### 《記号説明》

MARA : メモリアドレスレジスタA

MAR B : メモリアドレスレジスタB

ETCRA : 転送カウントレジスタA

転送元および転送先アドレスはともに24ビットで指定し、MARAがソースアドレスレジスタ、MAR Bがデスティネーションアドレスレジスタとなります。転送によるアドレスのインクリメント、デクリメントまたは固定の制御はMARA、MAR B独立に行うことができます。

転送回数はETCRAによって16ビットで指定します。転送を行うたびに1だけデクリメントされ、H'0000となったときにDTEビットをクリアして転送を終了します。このとき、DTIEビットが“1”にセットされるとCPUに割込みを要求します。

なお、転送回数の最大値はETCRAにH'0000を設定したときで、65536となります。

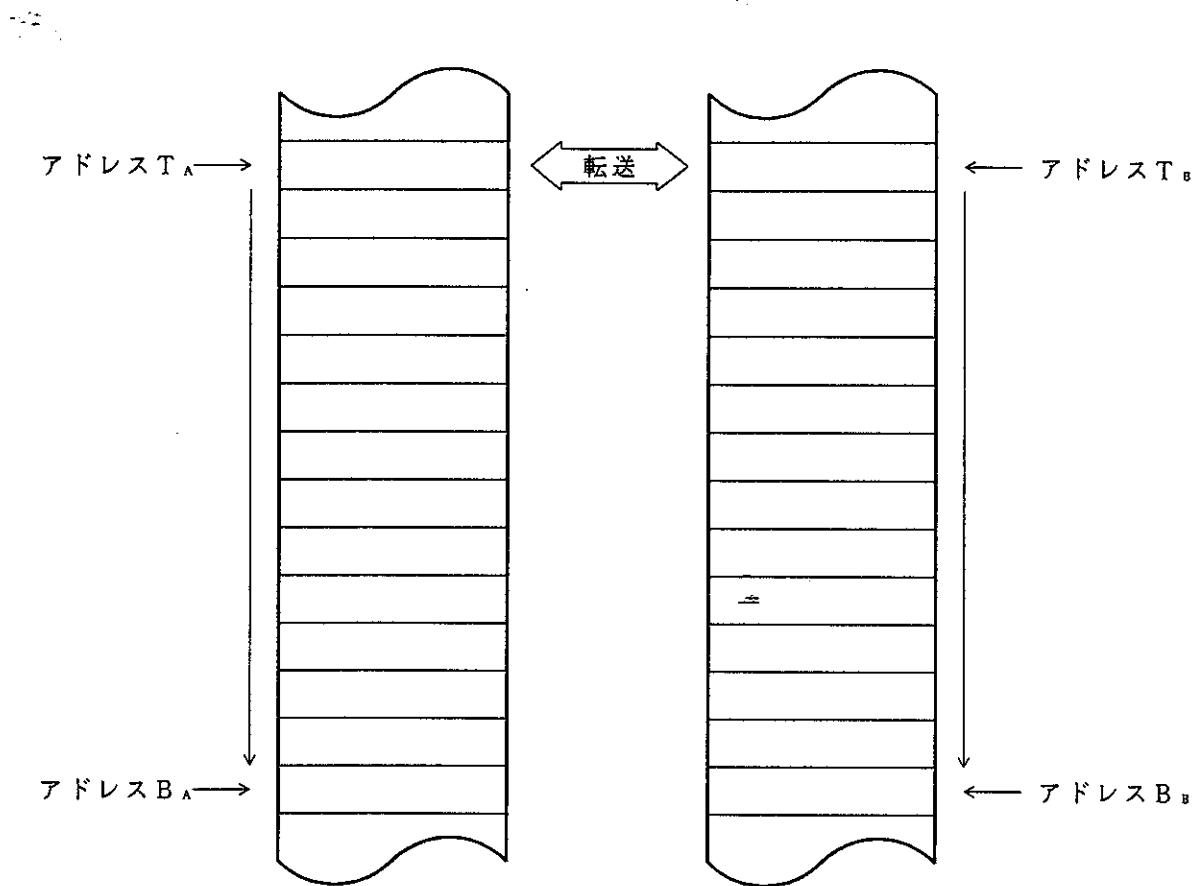

図 8.8 にノーマルモードの動作を示します。

#### 《記号説明》

$L_A = M A R A$  の初期設定値

$L_B = M A R B$  の初期設定値

$N = E T C R A$  の初期設定値

$T_A = L_A$

$B_A = L_A + S A I D E \cdot (-1)^{S A I D} \cdot (2^{D T S Z} \cdot N - 1)$

$T_B = L_B$

$B_B = L_B + D A I D E \cdot (-1)^{D A I D} \cdot (2^{D T S Z} \cdot N - 1)$

図 8.8 ノーマルモードの動作

転送要求（起動要因）には、外部リクエストとオートリクエストがあります。オートリクエストはレジスタの設定のみで起動され、指定された回数の転送を自動的に行います。オートリクエスト時にはサイクルスチールモードとバーストモードを選択できます。サイクルスチールモードでは DMA C は 1 回の転送を行うたびにバスを一旦解放します。バーストモードでは、より優先順位の高いバスマスターからのバス権要求がないかぎり転送終了までバスを占有し続けます。

設定の詳細は「8.3.4 データトランスマニコントロールレジスタ (D T C R)」を参照してください。

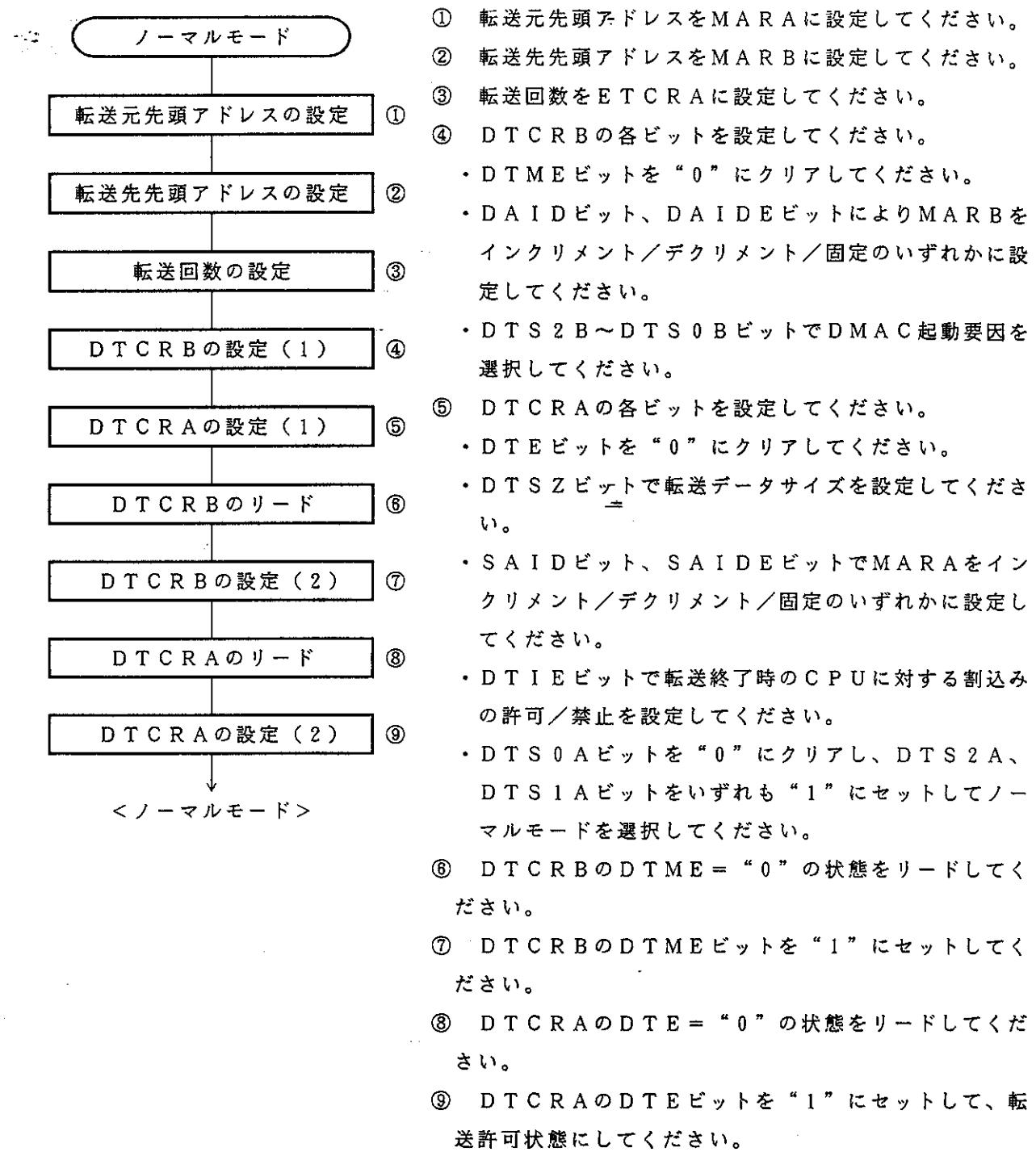

ノーマルモードの設定手順例を図8.9に示します。

【注】 ①～⑨の設定は、DEN D割込みをCPU側でマスクした状態で行ってください。また、設定中にNMI割込みが入力されると、DTMEビットが“0”にクリアされ起動されない場合があります。

図8.9 ノーマルモードの設定手順例

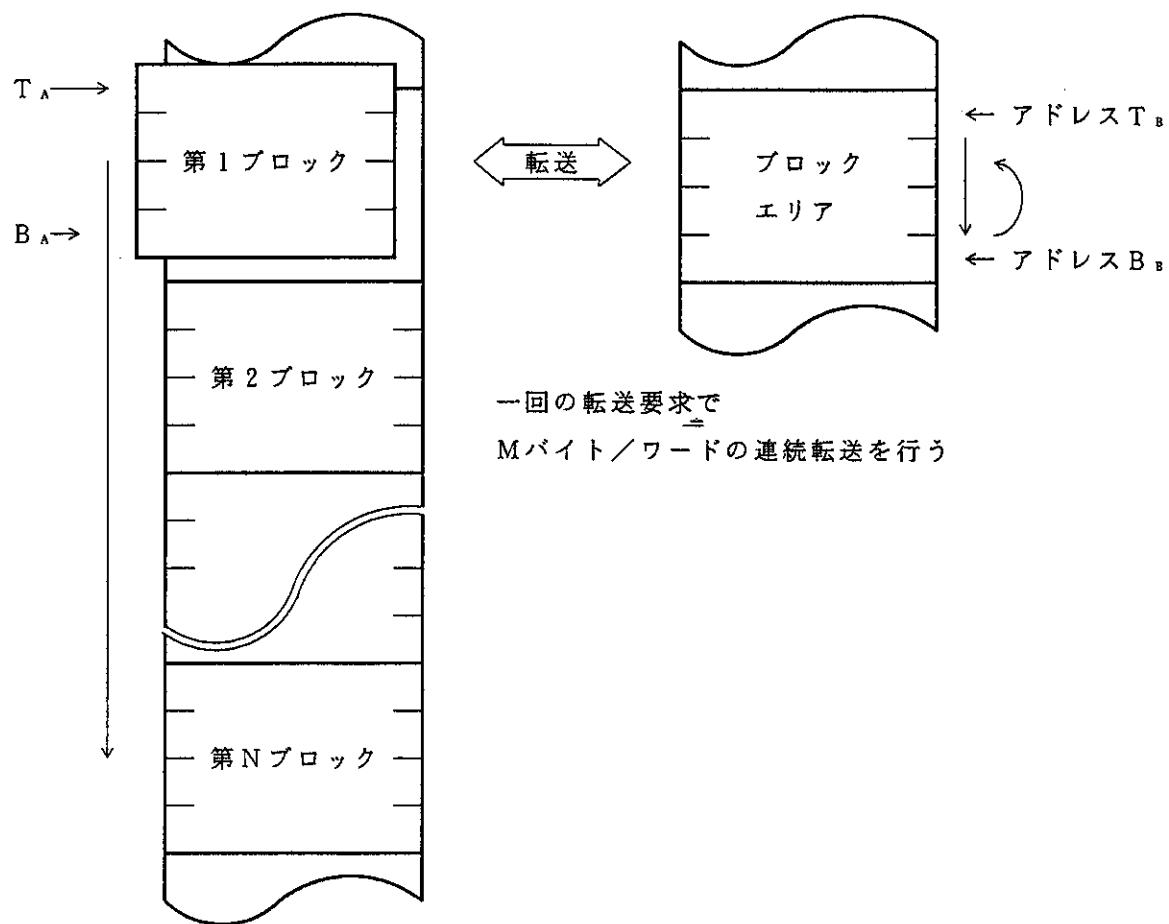

#### 8.4.6 ブロック転送モード

このブロック転送モードは、チャネルA、Bを組み合わせて転送を行います。

ブロック転送モードでは、一回の転送要求に対して、指定されたブロックサイズの転送を行い、これを指定された回数だけ実行します。アドレスはMARA、MAR Bで指定します。ブロックエリア側のアドレスは固定とするか、連続したアドレスとするかを選択できます。

ブロック転送モード時のレジスタの機能を表8.10に示します。

表8.10 ブロック転送モード時のレジスタの機能

| 対象レジスタ                                                                                      | 機能                | 初期設定値     | 動作                                  |

|---------------------------------------------------------------------------------------------|-------------------|-----------|-------------------------------------|

| 23 0<br>   | ソースアドレスレジスタ       | 転送元先頭アドレス | 1回の転送ごとにインクリメント/デクリメントまたは固定         |

| 23 0<br>   | デスティネーションアドレスレジスタ | 転送先先頭アドレス | 1回の転送ごとにインクリメント/デクリメントまたは固定         |

| 7 0<br>   | ブロックサイズカウンタ       | ブロックサイズ   | 1回の転送ごとにデクリメント H'00になると ETCRALの値を格納 |

| 7 0<br>  | ブロックサイズ保持         | ブロックサイズ   | 固定                                  |

| 15 0<br> | ブロック転送カウンタ        | ブロック転送回数  | ブロック転送ごとにデクリメント H'0000になると転送を終了     |

#### 《記号説明》

MARA : メモリアドレスレジスタA

MARB : メモリアドレスレジスタB

ETCRA : 転送カウントレジスタA

ETCRB : 転送カウントレジスタB

転送元および転送先アドレスはともに24ビットで指定し、MARAがソースアドレスレジスタ、MAR Bがデスティネーションアドレスレジスタとなります。転送によるアドレスのインクリメント、デクリメントまたは固定の制御は、MARA、MAR B独立に行うことができます。ブロックエリアを指定するMARは、インクリメント/デクリメントを指定した場合でも一回のブロック転送を終了するたびに初期設定値に戻ります。ソースアドレスとデスティネーションアドレスのどちらをブロックエリアとみなすかはDTCRBのTMSビットにより指定します。

一回の転送要求で転送するブロックサイズをM ( $M = 1 \sim 255$ ) とし、N回 ( $N = 1 \sim 65,536$ ) の転送を行うとき、ETCRAHとETCRALにそれぞれMを、ETCRBにNを設定します。

図8.10にブロック転送モードの動作を示します。TMSビットを“0”にクリアして、デスティネーションアドレスをブロックエリアとした場合の例です。

#### 《記号説明》

$L_A = MAR_A$  の初期設定値

$L_B = MAR_B$  の初期設定値

$M = ETCRAH, ETCRAL$  の初期設定値

$N = ETCRB$  の初期設定値

$T_A = L_A$

$B_A = L_A + S A I D E \cdot (-1)^{S A I D} \cdot (2^{D T S Z} \cdot M - 1)$

$T_B = L_B$

$B_B = L_B + D A I D E \cdot (-1)^{D A I D} \cdot (2^{D T S Z} \cdot M - 1)$

図8.10 ブロック転送モードの動作

転送要求によって D M A C が起動されるとバースト転送を行います。この間、M A R A 、 M A R B とも D T C R の設定に従い更新され、 E T C R A H をデクリメントします。 E T C R A H が H' 00 になると、 E T C R A H は E T C R A L の値が格納され初期設定値に戻ります。同時にロックエリア側の M A R も初期設定値に戻り、 E T C R B をデクリメントして H' 0000 でなければ次の転送要求待ちとなります。 E T C R A H と E T C R A L には同じ値を初期設定してください。

この動作を繰り返して E T C R B の値が H' 0000 となったとき、 D T E ビットを “ 0 ” にクリアして転送を終了します。このとき D T I E ビットが “ 1 ” にセットされていると C P U に対して割込みを要求します。

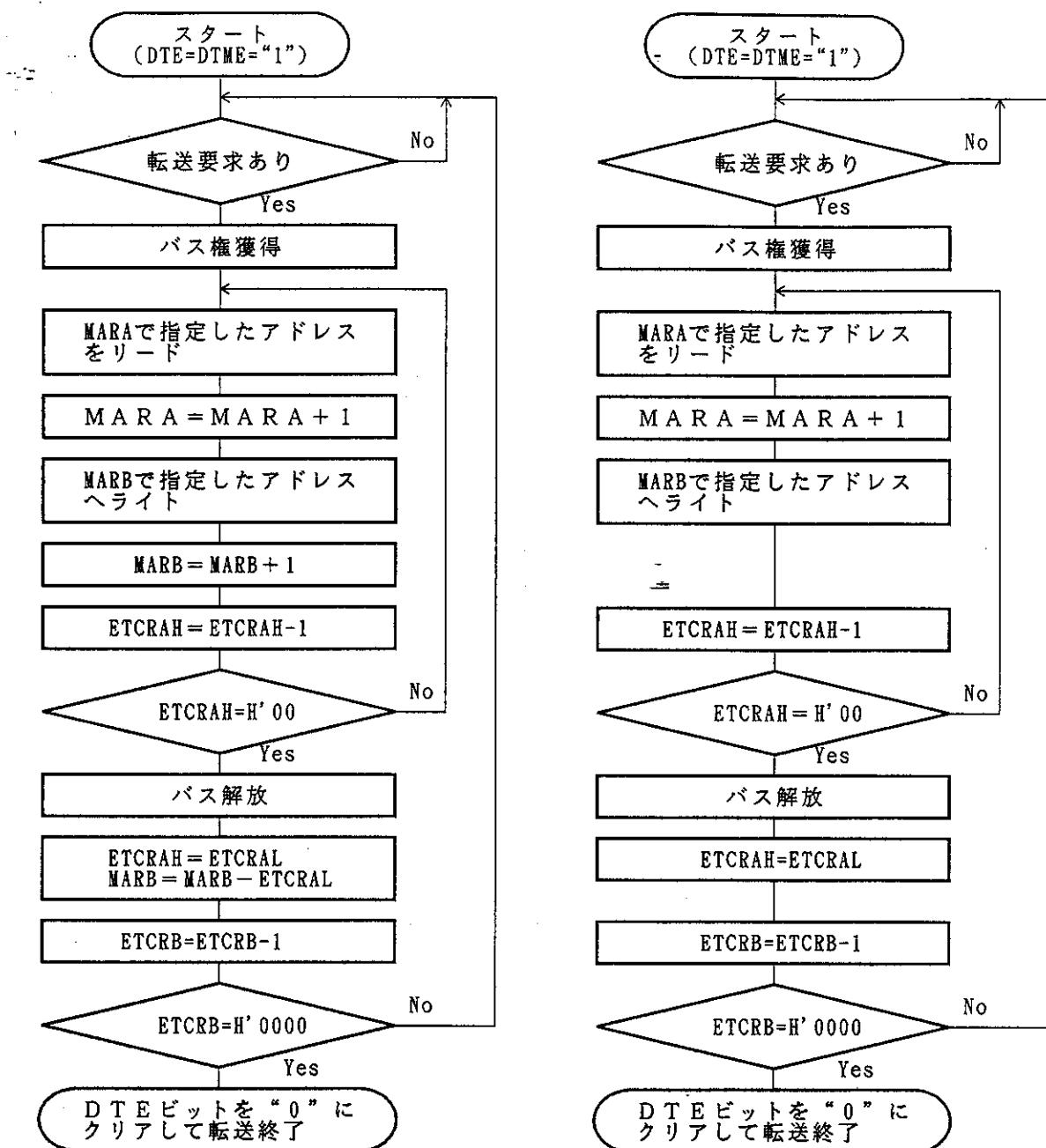

デスティネーションアドレスをロックエリアとしてバイト単位でロック転送する場合の D M A C の動作フロー例を図 8.11 に示します。(a) はロックエリアのアドレスが連続する場合、(b) はロックエリアのアドレス固定の場合を示します。

転送要求（起動要因）には、 I T U チャネル 0 ～ 3 コンペアマッチ / インプットキャプチャ A 割込みと外部リクエストがあります。

設定の詳細は「 8.3.4 データトランスマニコントロールレジスタ ( D T C R ) 」を参照してください。

(a)  $DTSZ = TMS = "0"$ 、

$SAID = DAID = "0"$ 、

$SAIDE = DAIDE = "1"$  の場合

(b)  $DTSZ = TMS = "0"$ 、

$SAID = "0"$ 、

$SAIDE = "1"$ 、

$DAIDE = "0"$  の場合

図 8.11 ブロック転送モードの動作フロー例

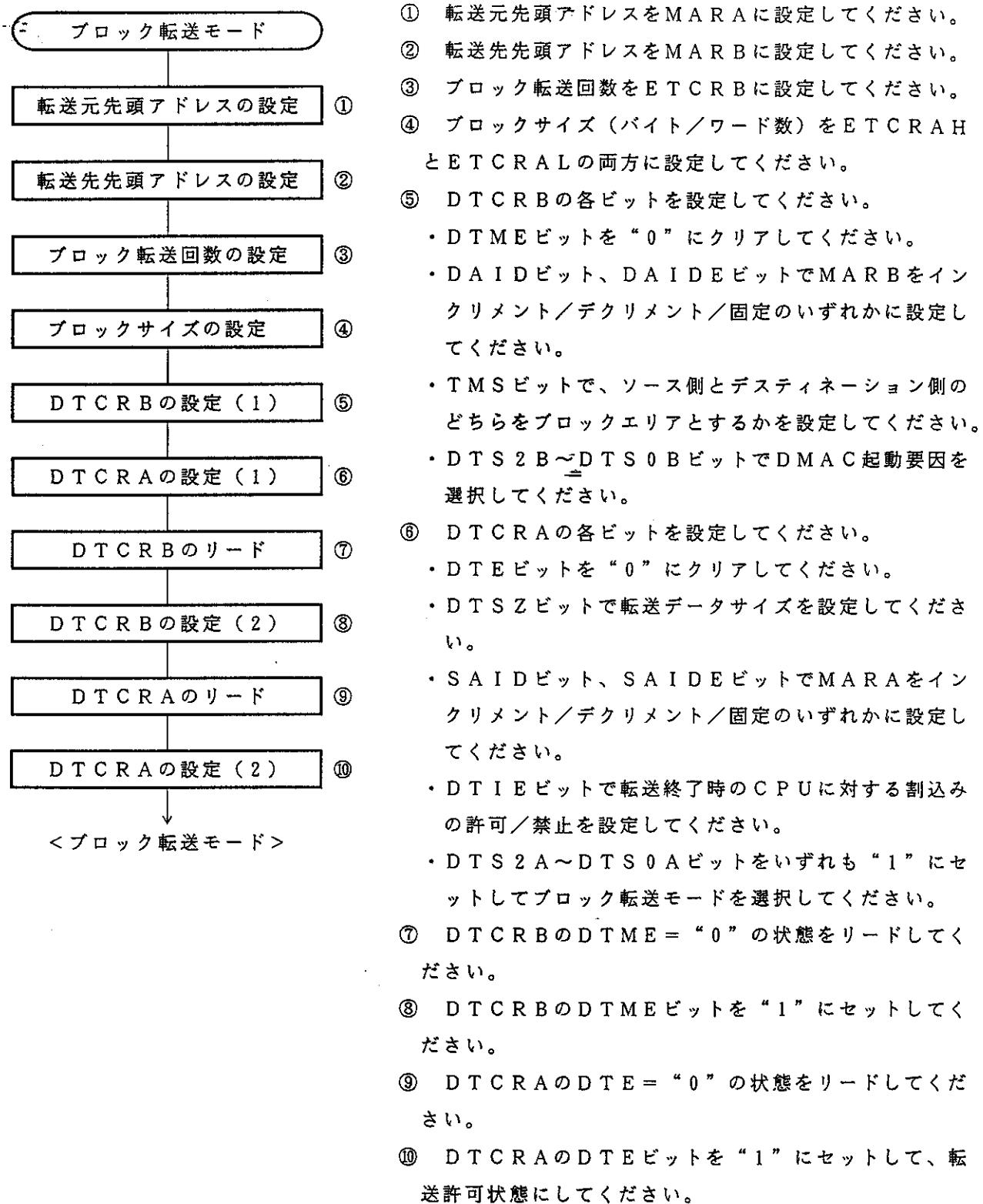

ブロック転送モードの設定手順例を図8.12に示します。

【注】 ①～⑩の設定は、DEN D割込みをCPU側でマスクした状態で行ってください。また、設定中にNMI割込みが入力されると、DTMEビットが“0”にクリアされ起動されない場合があります。

図8.12 ブロック転送モードの設定手順例

#### 8.4.7 D M A C の起動要因

- D M A C の起動要因には、内部割込み、外部リクエスト、およびオートリクエストがあります。

- 転送モードおよびチャネルにより指定できる要因が表 8.11 に示すように異なります。

表 8.11 D M A C の起動要因

| 起 動 要 因     |                    | ショートアドレスモード       |                   | フルアドレスモード |      |

|-------------|--------------------|-------------------|-------------------|-----------|------|

|             |                    | チャネル<br>0A,<br>1A | チャネル<br>0B,<br>1B | ノーマル      | ブロック |

| 内部<br>割込み   | I M I A 0          | ○                 |                   | ×         | ○    |

|             | I M I A 1          | ○                 |                   | ×         | ○    |

|             | I M I A 2          | ○                 |                   | ×         | ○    |

|             | I M I A 3          | ○                 |                   | ×         | ○    |

|             | T X I 0            | ○                 |                   | ×         | ×    |

|             | R X I 0            | ○                 |                   | ×         | ×    |

| 外部<br>リクエスト | DREQ端子の立下がり        | ×                 | ○                 | ○         | ○    |

|             | DREQ端子の“Low” レベル入力 | ×                 | ○                 | ○         | ×    |

| オートリクエスト    |                    | ×                 |                   | ○         | ×    |

##### (1) 内部割込みによる起動

D M A C の起動要因として選択された割込み要求は、D T E = “1” の状態では C P U に対しては要求されません。したがって、起動要因として使用している割込みで同時に C P U に割込みを発生させることはできません。

割込み要求により D M A C が起動されると、割込み要求フラグは自動的にクリアされます。複数のチャネルで同一の割込みを起動要因として指定した場合、最初に最も優先順位の高いチャネルが起動された時点で割込み要求フラグがクリアされます。その他のチャネルの転送要求は D M A C 内部で保持されて、優先順位に従って起動されます。

## (2) 外部リクエストによる起動

起動要因として外部リクエスト (DREQ端子) を指定した場合は、該当するDREQ端子とTEND端子が対応するポートのデータディレクションレジスタ (DDR) の設定にかかわらず、それぞれ入力端子、出力端子になります。

DREQ端子入力にはレベルセンスとエッジセンスがあります。

ショートアドレスモードとノーマルモード時の外部リクエスト動作は次のようにになります。

エッジセンスを選択した場合はDREQ端子入力の“High”レベルから“Low”レベルへの変化を検出するたびに、1バイトまたは1ワードの転送を行います。転送完了前に次のエッジが入力された場合は次の転送が行われない場合があります。

レベルセンスを選択した場合はDREQ端子が“Low”レベルに保持されている間は、転送終了まで転送を継続します。ただし、1バイトまたは1ワードの転送を行うたびに一旦バスを解放します。転送の途中でDREQ端子入力が“High”レベルとなった場合、転送中の1バイトまたは1ワードを転送した時点で転送を中断します。なお、DREQ端子を“Low”レベルにすると、起動要因は1バイトまたは1ワードの転送が行われるまで内部で保持されています。

TEND端子は最後の転送のライトサイクル中“Low”レベルとなります。

ブロック転送モード時の外部リクエスト動作は次のようにになります。

ブロック転送モードはエッジセンスの転送要求のみ可能です。DREQ端子入力の“High”レベルから“Low”レベルへの変化を検出するたびに、指定された1ブロックを転送します。

TEND端子は1ブロック転送の最後のライトサイクル中“Low”レベルとなります。

## (3) オートリクエストによる起動

オートリクエストはレジスタ設定のみで起動され、転送終了まで継続して転送を行います。

サイクルスチールモードとバーストモードが選択できます。

サイクルスチールモードでは、DMACは1バイトまたは1ワードの転送を行うたびにバスを一旦解放しますので、通常、DMACサイクルとCPUサイクルが交互に繰り返されます。

バーストモードでは、より優先順位の高いバス権要求がないかぎり転送終了までバスを占有し続けます。優先順位の高いバス権要求があった場合は、転送中の1バイトまたは1ワードを転送した時点でバスを解放します。

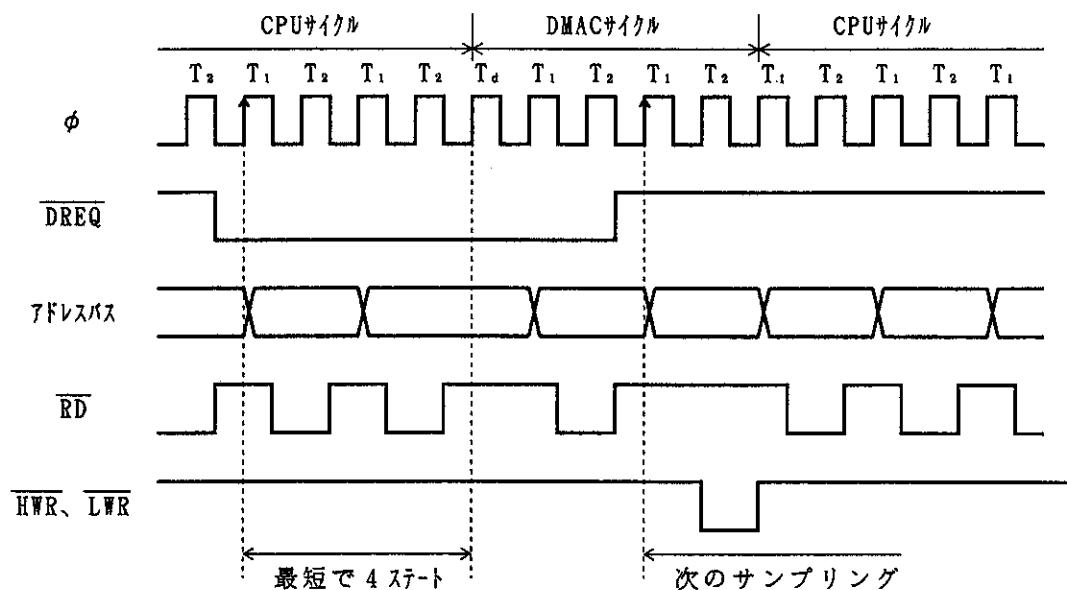

#### 8.4.8 DMAのバスサイクル

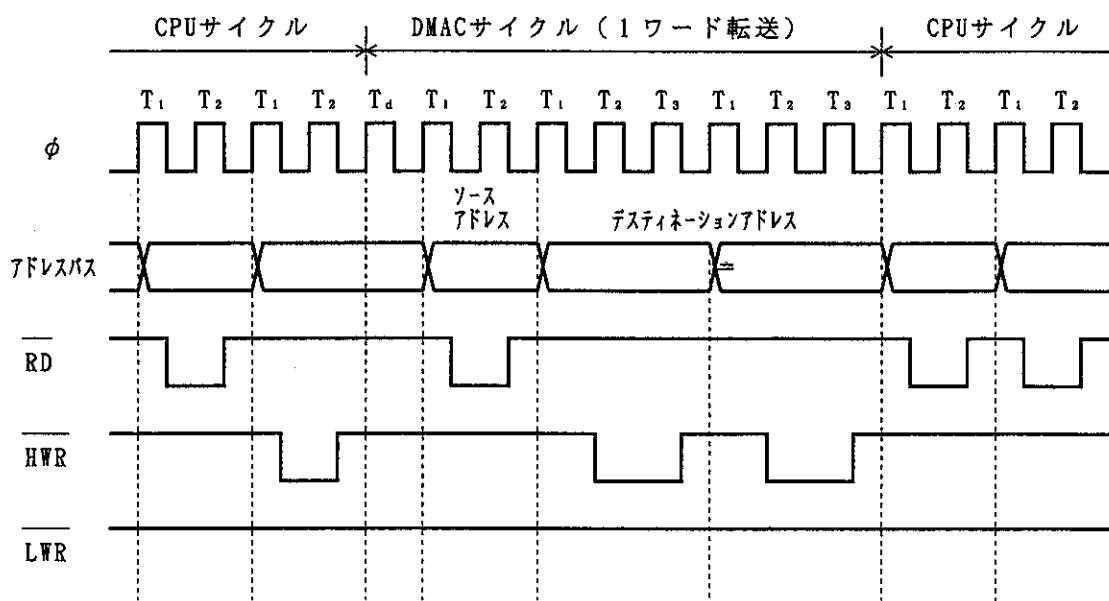

DMAの基本的なバスサイクルのタイミング例を図8.13に示します。この例はワードサイズで16ビット2ステートアクセス空間から8ビット3ステートアクセス空間へ転送する場合の例です。CPUからDMAにバス権が移ると、1サイクルのデッドサイクル( $T_d$ )の後、ソースアドレスのリード、デスティネーションアドレスのライトを行います。このリード、ライト動作の間に、他のバス権要求などによってバスを解放することはありません。DMAサイクルはCPUサイクルと同様、バスコントローラの設定にしたがいます。

図 8.13 DMA転送バスタイミング例

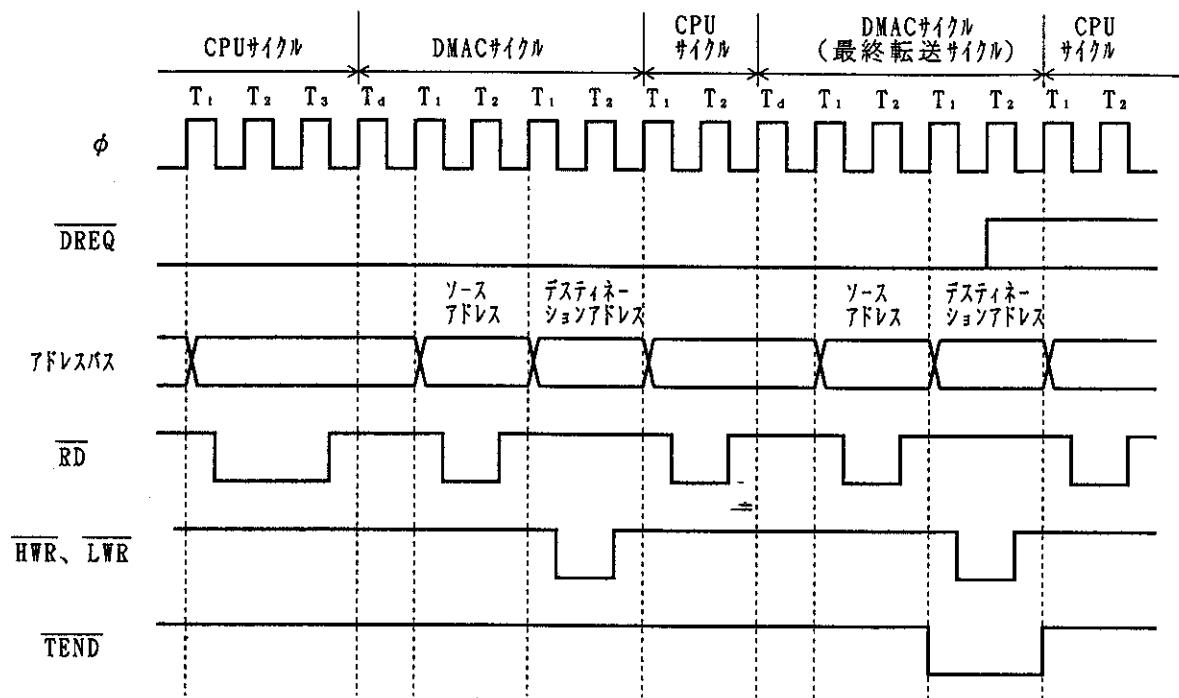

DREQ端子“Low”レベルでDMA Cを起動した場合のタイミングを図8.14に示します。ワードサイズで16ビット2ステートアクセス空間から16ビット2ステートアクセス空間へ転送する場合の例です。DREQ端子が“Low”レベルに保持されている間、DMA Cは転送を継続します。

図8.14 DREQ端子“Low”レベル入力選択時のDMA転送バスタイミング

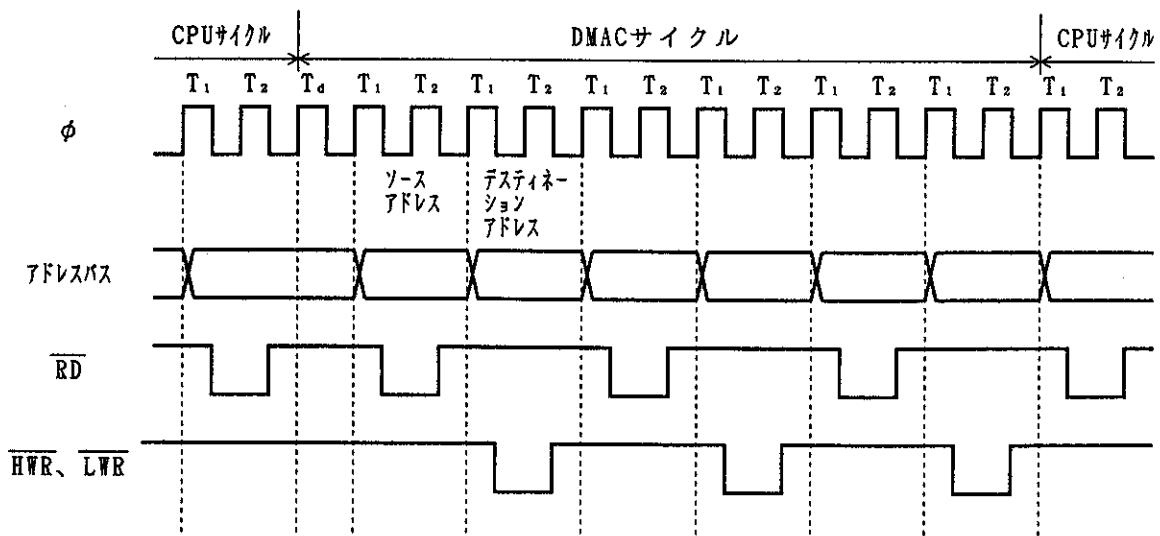

オートリクエストバーストモードの場合のタイミングを図8.15に示します。ワードサイズで16ビット2ステートアクセス空間から16ビット2ステートアクセス空間へ、3ワード転送する場合の例です。

図8.15 バーストモードDMA転送バスタイミング

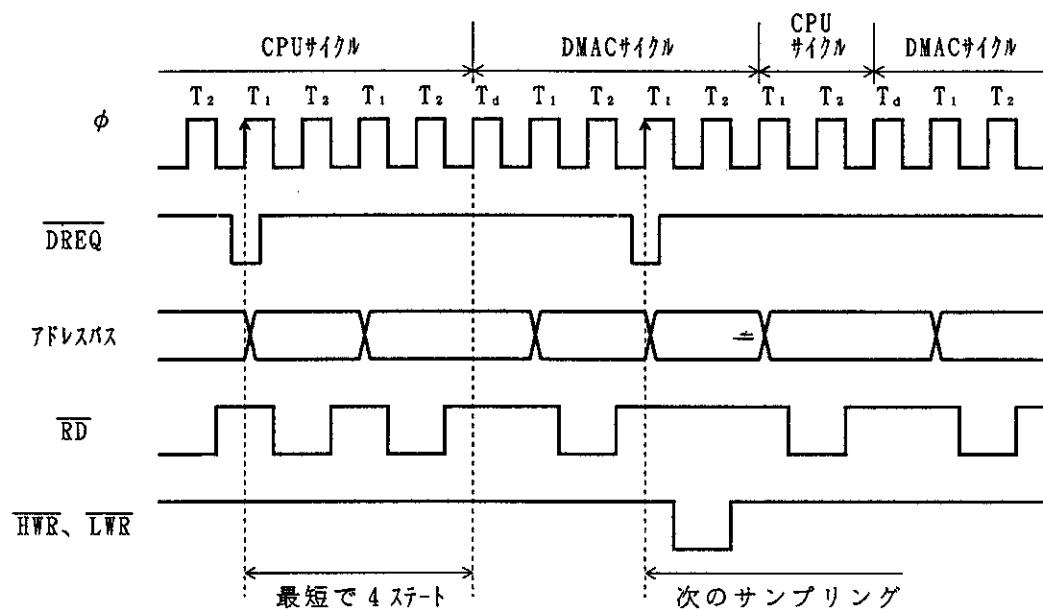

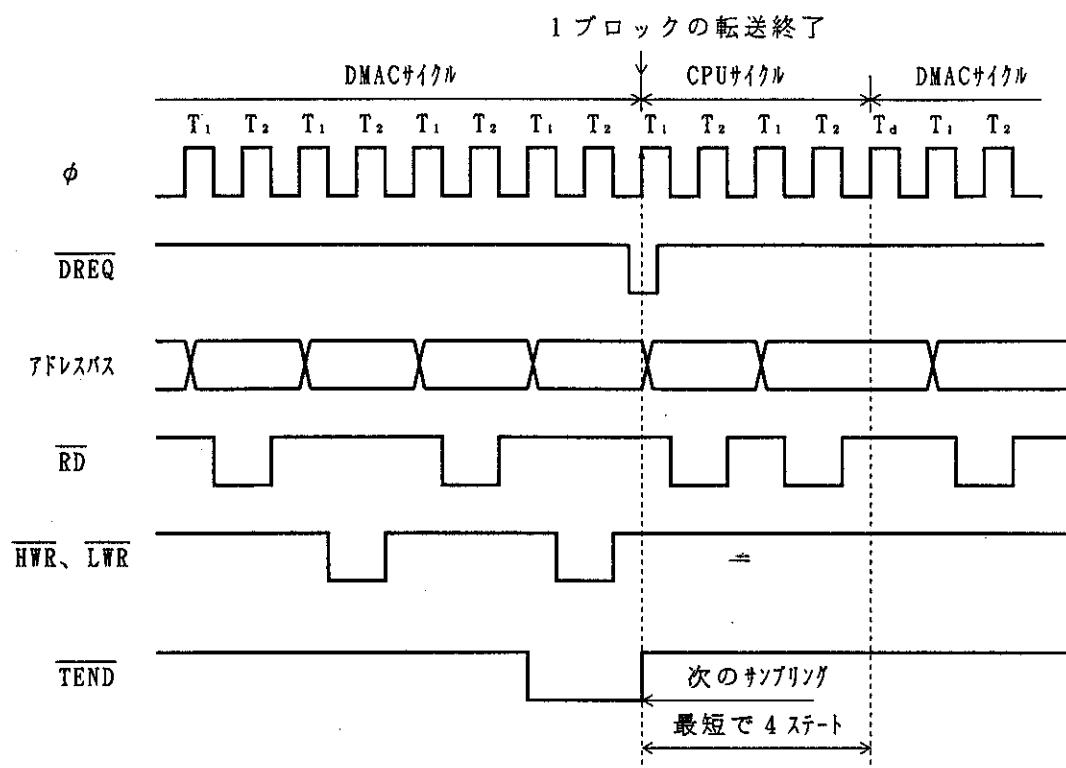

DREQ端子でDMAを起動する場合、転送要求が発生してからDMAが動作を開始するまでの期間は最短で4ステートです。

転送要求発生後、DMAが動作を開始し転送を行うまで、DREQ端子のサンプリングは行いません。次のサンプリングは、ショートアドレスモードとノーマルモードの場合、リードサイクル終了後から行い、ブロック転送モードの場合、1ブロックの転送終了後から行います。

ノーマルモード時、DREQ端子の立下がりエッジでDMAを起動する場合のタイミングを図8.16に示します。

図8.16 ノーマルモード時のDREQ端子の立下がりエッジによるDMA起動タイミング

ノーマルモード時、DREQ端子の“Low”レベルでDMAを起動する場合のタイミングを図8.17に示します。

図8.17 ノーマルモード時のDREQ端子の“Low”レベルによるDMA起動タイミング

ブロック転送モード時、DREQ端子の立下がりエッジでDMA Cを起動する場合のタイミングを図8.18に示します。

図 8.18 ブロック転送モード時のDREQ端子の立下がりエッジによるDMA C起動タイミング

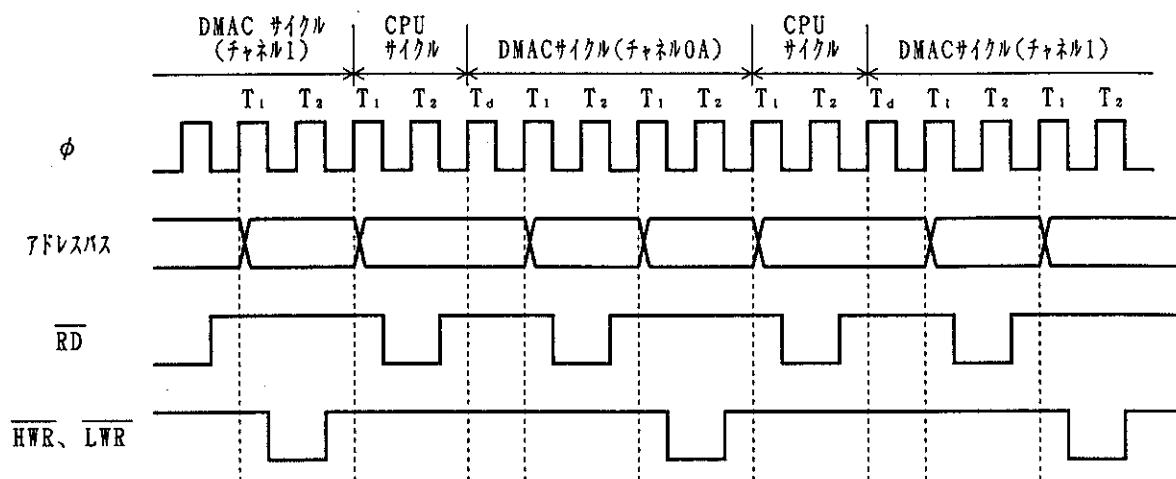

#### 8.4.9 D M A C 複数チャネルの動作

D M A C のチャネル間順位はチャネル 0 > チャネル 1 、また、チャネル A > チャネル B の順に優先順位が高くなっています。表 8.12 に D M A C のチャネル間優先順位を示します。

表 8.12 チャネル間優先順位

| ショートアドレスモード | フルアドレスモード | 優先度    |

|-------------|-----------|--------|

| チャネル 0 A    | チャネル 0    | 高<br>↑ |

| チャネル 0 B    |           |        |

| チャネル 1 A    | チャネル 1    | ↓<br>低 |

| チャネル 1 B    |           |        |

複数のチャネルに対して同時に転送要求が発生した場合、または転送中に他のチャネルの転送要求が発生した場合、 D M A C は以下のように動作します。

- ① 転送要求が発生するとバス権を要求し、 D M A C がバス権を獲得する時点で最も優先順位の高いチャネルの転送が起動されます。

- ② 1つのチャネルが起動されると、そのチャネルがバス権を解放するまで他のチャネルは保留となります。

- ③ ショートアドレスモードおよびノーマルモードの外部リクエスト、サイクルスチールモードの場合、1回の転送を行った後、バスを解放して①に戻ります。バスを解放した後、他のチャネルの転送要求が存在すると、再度バス権を要求します。

- ④ バーストモードの場合は転送終了後、ブロック転送モードの場合は1ブロックの転送後、バスを解放して①に戻ります。ただし、優先順位の高いチャネルの転送要求または優先順位の高いバスマスクのバス権要求が存在すると、転送中の1バイトまたは1ワードの転送を終了した時点でバスを解放します。バスを解放した後、他のチャネルの転送要求が存在すると、再度バス権を要求します。

チャネル0 AをI/Oモード、チャネル1をバーストモードとし、チャネル1が動作中、チャネル0 Aの転送要求が発生した場合のタイミングを図8.19に示します。

図8.19 複数チャネルの動作タイミング

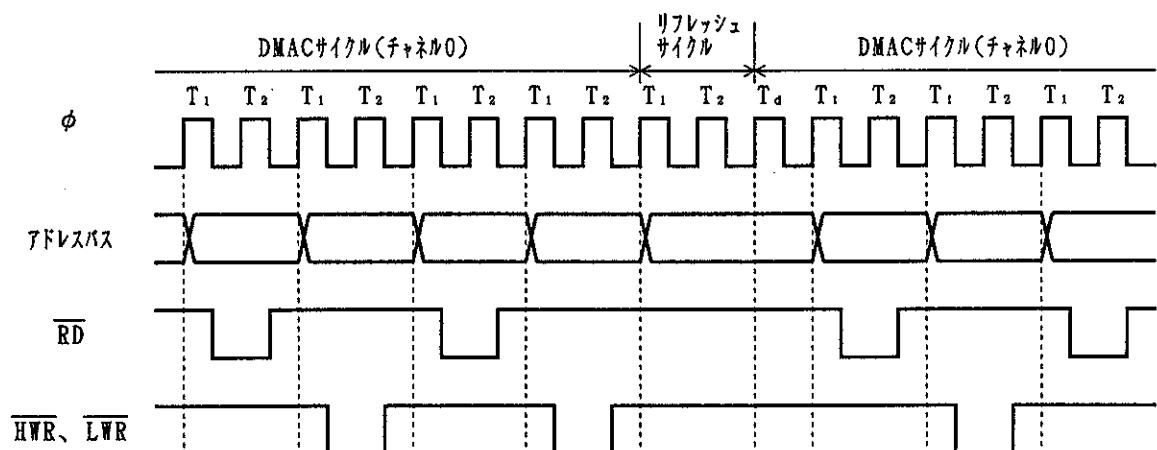

#### 8.4.10 外部バス権要求、リフレッシュコントローラとDMACの関係

DMAC動作中に、BREQ端子による外部バス権要求、リフレッシュコントローラによるバス権要求があった場合、DMACは転送中の1バイトまたは1ワードの転送を終了した時点でバスを解放します。この時点で転送要求が存在する場合、DMACは再度バス権を要求します。

チャネル0でバーストモード転送中にリフレッシュサイクルが挿入される場合のタイミングを図8.20に示します。

図8.20 リフレッシュコントローラとDMACの動作タイミング

### 8.4.11 NMI 割込みと DMA C

ショートアドレスモードでは、NMI 割込みは DMA C の動作に影響を与えません。

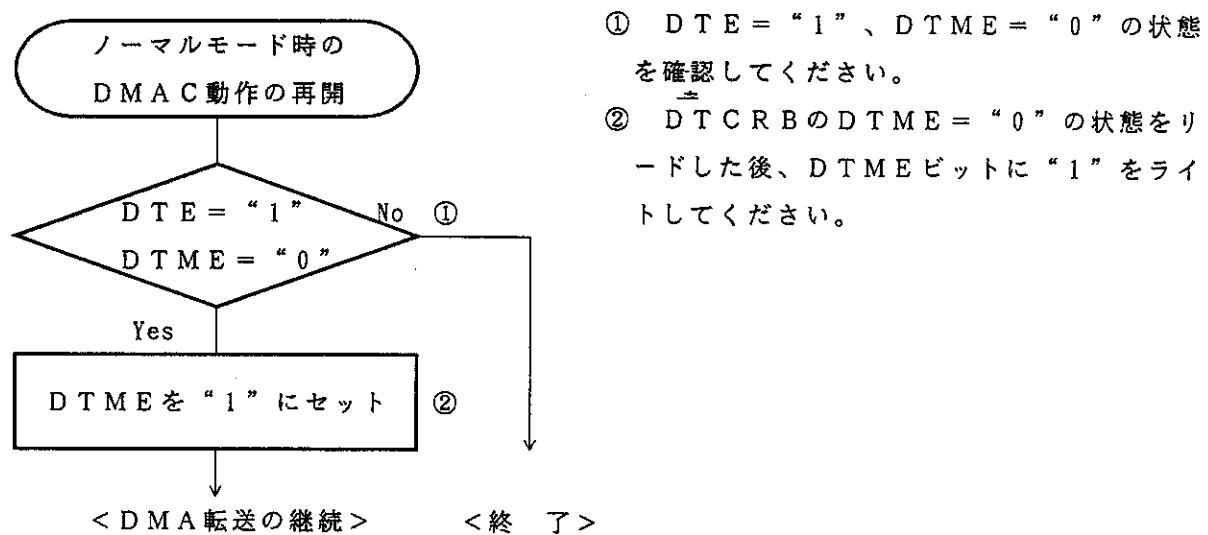

フルアドレスモードでは、転送中に NMI 割込みが発生すると DMA C は動作を中断します。フルアドレスモードでは、DTE ビットと DTME ビットがいずれも “1” にセットされているとき、そのチャネルが転送許可状態となります。NMI 割込みが発生すると DTME ビットが “0” にクリアされ、DMA C は転送中の 1 バイトまたは 1 ワードの転送を終了した時点でバスを解放し、CPU にバス権が移ります。ノーマルモードのときは、その後 CPU が DTME ビットを “1” にセットすると中断した動作を再開します。この場合、事前に DTE ビットが “1” にセットされ、DTME ビットが “0” にクリアされていることを確認してください。

チャネル 0 をノーマルモードとしたときに、NMI 割込みにより DMA C 動作が停止したとき、動作を再開する手順を図 8.21 に示します。

図 8.21 NMI 割込みにより停止した DMA C 動作の再開手順例

ブロック転送モード時の NMI 割込みについては「8.6.6 NMI 割込みとブロック転送モード」を参照してください。

#### 8.4.12 DMA動作の強制終了

動作中のチャネルのDTEビットを“0”にクリアすると、転送中の1バイトまたは1ワードの転送を終了した時点でDMAは停止します。この後、DTEビットを“1”にセットするとDMAは動作を再開します。

フルアドレスモードの場合、DTMEビットを使用しても同様です。

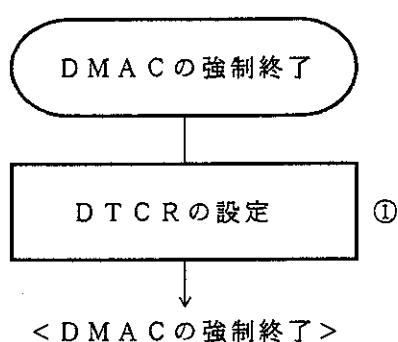

DMAをソフトウェアで強制終了させる場合の手順を図8.22に示します。

① DTCRのDTEビットを“0”にクリアしてください。DMA動作強制終了後、割込みを発生させたくない場合はDTIEビットも同時に“0”にクリアしてください。

図8.22 DMA動作の強制終了手順

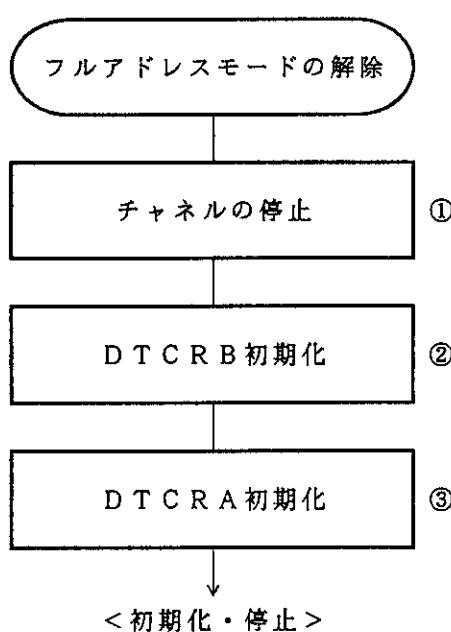

#### 8.4.13 フルアドレスモードの解除

フルアドレスモードに設定したチャネルを解除し、初期化する場合の手順を図8.23に示します。解除後に再設定する場合には各転送モードの設定手順に従ってください。

① DTCRAのDTEビットを“0”にクリアするか、転送が終了し、DTEビットが“0”になるまで待ってください。

② DTCRBの全ビットを“0”にクリアしてください。

③ DTCRAの全ビットを“0”にクリアしてください。

図8.23 フルアドレスモードの解除手順例

#### 8.4.14 リセット、スタンバイモード、スリープモード時のDMAの状態

リセット、ハードウェアスタンバイモード、またはソフトウェアスタンバイモード時、DMAはイニシャライズされ、停止します。

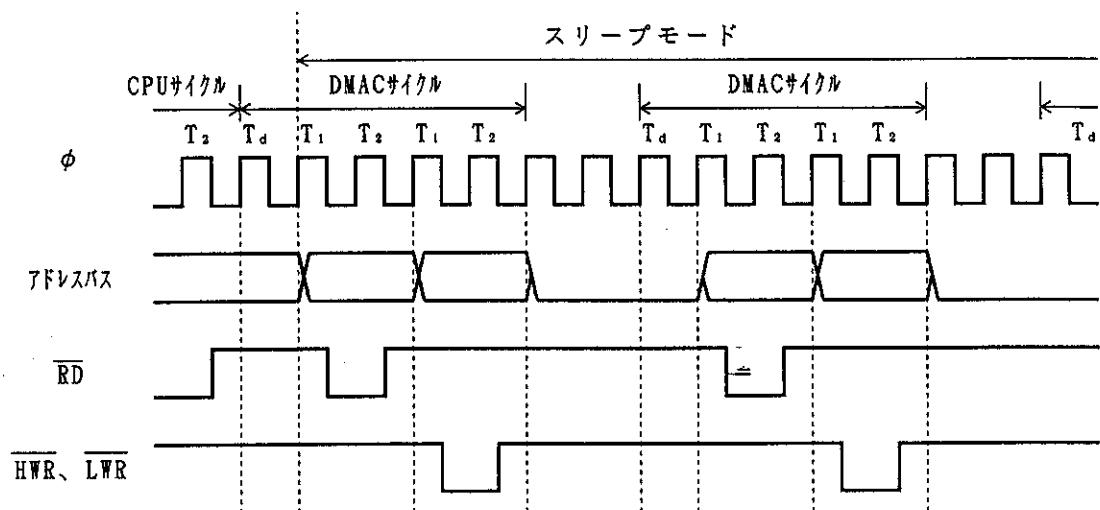

スリープモード中はDMAは動作を継続します。

スリープモード中のサイクルスチールモードのタイミングを図8.24に示します。

図8.24 スリープモード中のサイクルスチールモードのタイミング

## 8.5 割込み

DMAの割込み要因は転送終了のみです。表8.13に割込み要因と優先度を示します。

表8.13 DMAの割込み要因

| 割込み要因  | 内 容               |                  | 割込み優先順位 |

|--------|-------------------|------------------|---------|

|        | ショートアドレスモード       | フルアドレスモード        |         |

| DEND0A | チャネル0Aの転送終了による割込み | チャネル0の転送終了による割込み | 高<br>↑  |

| DEND0B | チャネル0Bの転送終了による割込み | _____            |         |

| DEND1A | チャネル1Aの転送終了による割込み | チャネル1の転送終了による割込み |         |

| DEND1B | チャネル1Bの転送終了による割込み | _____            |         |

各割込み要因は、対応するDTCRのDTEビットにより許可／禁止が設定されており、それぞれ独立に割込みコントローラに送られます。

チャネル間の割込みの優先順位は、チャネル0 > チャネル1、またチャネルA > チャネルBのように優先順位が高くなっています。

転送終了の割込みブロック図を図8.25に示します。

DTE = “0”の状態でDTEビットを“1”に設定すると、常に割込みが発生します。

図8.25 転送終了割込みブロック図

フルアドレスモードでは、チャネルBの転送終了割込み(DENDB)は使用できません。また、DTMEビットは割込み動作に影響を与えません。

## 8.6 使用上の注意

### 8.6.1 ワードデータ転送時の注意

奇数アドレスから始まるワードデータはアクセスできません。転送データサイズをワードにした場合、M A R および I O A R は偶数値としてください。

### 8.6.2 D M A C による D M A C 自体のアクセス

D M A C サイクル中はD M A C 自体へのアクセスが禁止されています。したがって、D M A C のレジスタをソースまたはデスティネーションとして転送することはできません。

### 8.6.3 M A R のロングワードアクセス

M A R はM A R R から始まるロングワードデータとしてアクセスすることができます。

(例)

```

MOV.L  #LBL, ERO

MOV.L  ERO, @MARR

```

このとき、バイトデータアクセスが4回行われます。第2バイト(M A R E)と第3バイト(M A R H)アクセスの間に、C P Uがバスを解放する場合がありますので注意してください。

M A R のリード/ライトはD M A C 停止中に行ってください。

### 8.6.4 フルアドレスモード設定時の注意

フルアドレスモードは、2つのレジスタD T C R A、D T C R Bによって制御されます。これらレジスタの設定時には、チャネルBがショートアドレスモードで動作しないように注意してください。許可ビット(D T E、D T M E)は、最後に“1”にセットしてください。

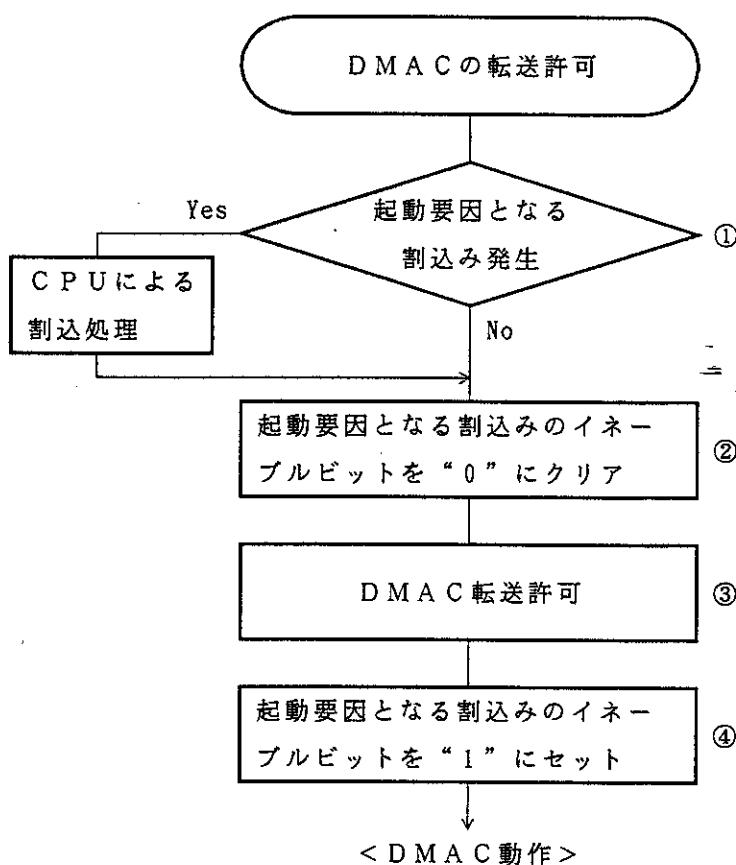

### 8.6.5 内部割込みでDMAを起動する場合の注意

(1) 内部割込みでDMAを起動する場合、起動要因を選択してからDMAを転送許可状態にするまでの期間に選択した起動要因が発生しないようにしてください。すなわち、DMAを転送許可状態にした後、起動要因となる内蔵周辺モジュールを動作させてください。内蔵周辺モジュールの動作中にDMAを許可状態にする場合、図8.26の手順で行ってください。

- ① DTE = “0”の状態では、割込みはCPUに要求されます。

- ② 起動要因となる内蔵周辺モジュールの割込みイネーブルビットを“0”にクリアします。

- ③ DMAを転送許可状態にします。

- ④ DMAに対する割込みを許可します。

図8.26 内蔵周辺モジュールが動作中にDMAを転送許可状態にする場合の手順例

なお、DTE = “1”なおかつDTME = “0”的状態では、DMAは停止状態であり、またCPUにも起動要因となる割込みは要求されません。例えば、NMI割込みにより、DMAを停止状態にした場合は、起動要因となる割込みはCPUには要求されません。このとき、DMA動作を打ち切る場合には、DTEビットを“0”にクリアし、CPUに割込みを要求させてください。DMA動作を継続する場合には、DTMEビットを“1”にセットする前後で、図8.26の②、④の操作を行ってください。

(2) ITUの割込み要求でDMAを起動する場合、割込みによって起動されるDMA転送が終了するまで、次の割込みが発生しないようにしてください。1つのITUの割込み要求で複数チャネルを起動する場合には、起動されるすべてのDMA転送が終了するまで、次の割込みが発生しないようにしてください。転送が終了するまでに次の割込みが発生すると、その割込みを選択しているチャネルが以降の起動要求を受け付けなくなる場合があります。

### 8.6.6 NMI割込みとブロック転送モード

ブロック転送モード中にNMI割込みが発生するとDMAは以下のように動作します。

(1) NMI割込みが発生するとDMAは転送中の1バイトまたは1ワードの転送終了後、DTMEビットを“0”にクリアして停止します。したがって、1つのブロックの転送途中で停止する場合があります。

ブロックの転送途中で停止したことは、ブロックサイズカウンタで判定できます。ブロックサイズカウンタが初期設定値以外の場合はブロックの転送途中で停止したことになります。

(2) ブロックの転送途中で停止した場合、起動要因となる割込みフラグは“0”にクリアされています。起動要因の内部保持は行っていません。

(3) DTMEビットが“1”にセットされ、DTMEビットが“0”にクリアされた状態では、DMAは停止中であり、DMAは起動要因となる割込み要求を受付けません。この状態で起動要因となる割込みが発生するとDMAは動作せず、転送要求の内部保持も行いません。また、CPUにも割込みは要求されません。

このため、DTMEビットを“1”にセットする前に起動要因となる割込みのイネーブルビットを“0”にクリアし、次にDTMEビットを“1”にセットし、その後、割込みイネーブルビットを“1”にセットしてください。「8.6.5 内部割込みでDMAを起動する場合の注意」を参照してください。

(4) DTMEビットを“1”にセットすると、DMAは次の転送要求を待ちます。ブロックの転送途中で停止した場合、次の転送要求が発生するとブロックの残りを転送します。それ以外の場合、転送要求が発生すると次のブロックの転送を行います。

### 8.6.7 MAR、IOARのアドレス指定

MAR、IOARで指定できるアドレスの範囲を表8.14に示します。

表8.14 MAR、IOARで指定できるアドレスの範囲

|      | 1Mバイトモード                             | 16Mバイトモード                               |

|------|--------------------------------------|-----------------------------------------|

| MAR  | H'00000~H'FFFFF<br>(0~1048575)       | H'000000~H'FFFFFF<br>(0~16777215)       |

| IOAR | H'FFF00~H'FFFFF<br>(1048320~1048575) | H'FFF00~H'FFFFFF<br>(16776960~16777215) |

1Mバイトモードのとき、MARのビット23~ビット20は無視されます。

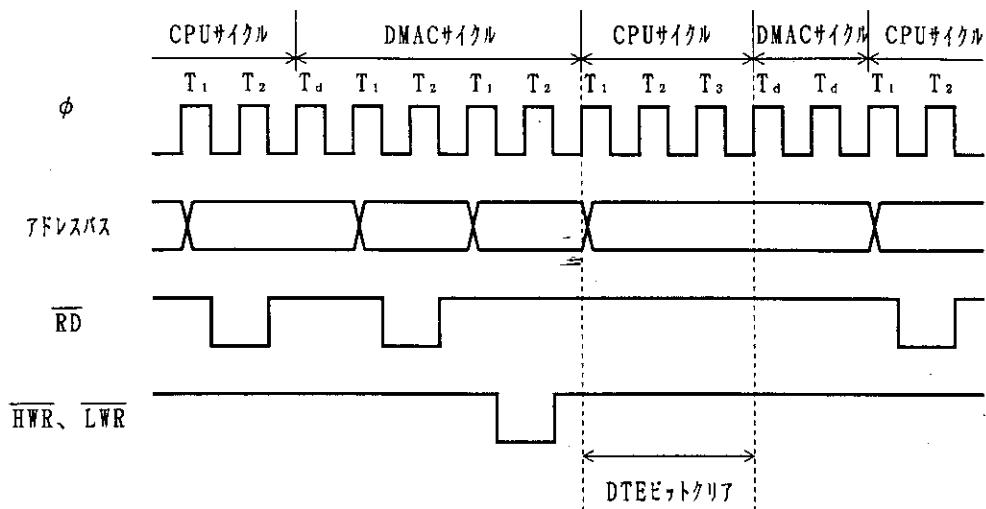

### 8.6.8 転送中断時のバスサイクル

DTE ビットクリアによる強制終了や、NMI 割込みによる DTMF ビットクリアの転送停止により、DMAC 内部で、すでに要求を保持しているチャネルを停止させるとデッドサイクルを発生することがあります。このデッドサイクルにより中断したチャネルのアドレスレジスタおよびカウンタの値が更新されることはありません。チャネル 0 でオートリクエストサイクルスチール転送中に、チャネル 0 の DTE ビットをクリアした場合のタイミングを図 8.27 に示します。

図 8.27 サイクルスチールモード DMA 転送の強制終了バスタイミング