# 付 錄

## 付 錄

|                                   |     |

|-----------------------------------|-----|

| A. 命 令                            | 767 |

| A. 1 命令一覧                         | 767 |

| A. 2 オペレーションコードマップ                | 782 |

| A. 3 命令実行ステート数                    | 785 |

| B. 内部 I/O レジスター一覧                 | 795 |

| B. 1 アドレス一覧                       | 795 |

| B. 2 機能一覧                         | 803 |

| C. I/O ポートブロック図                   | 886 |

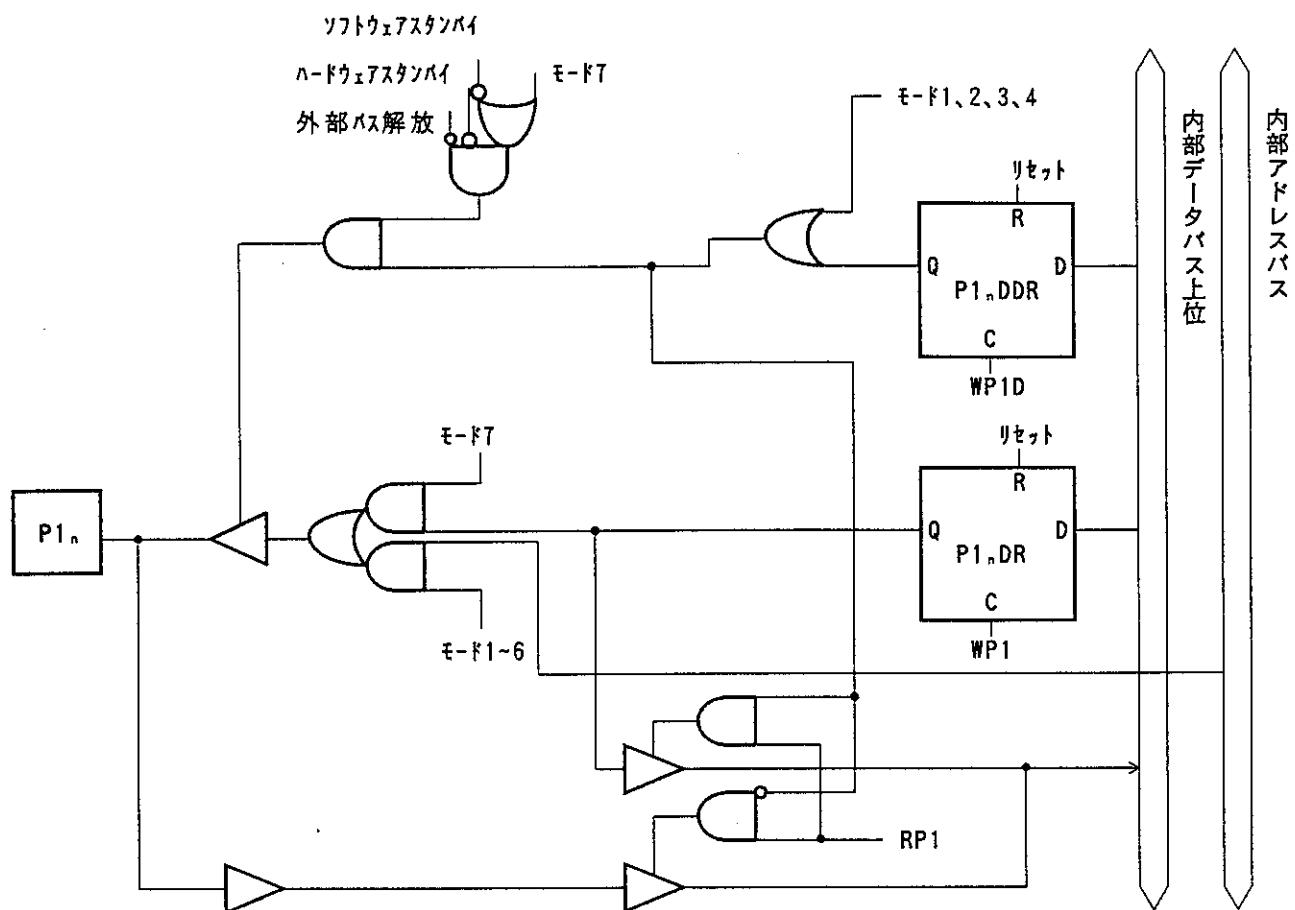

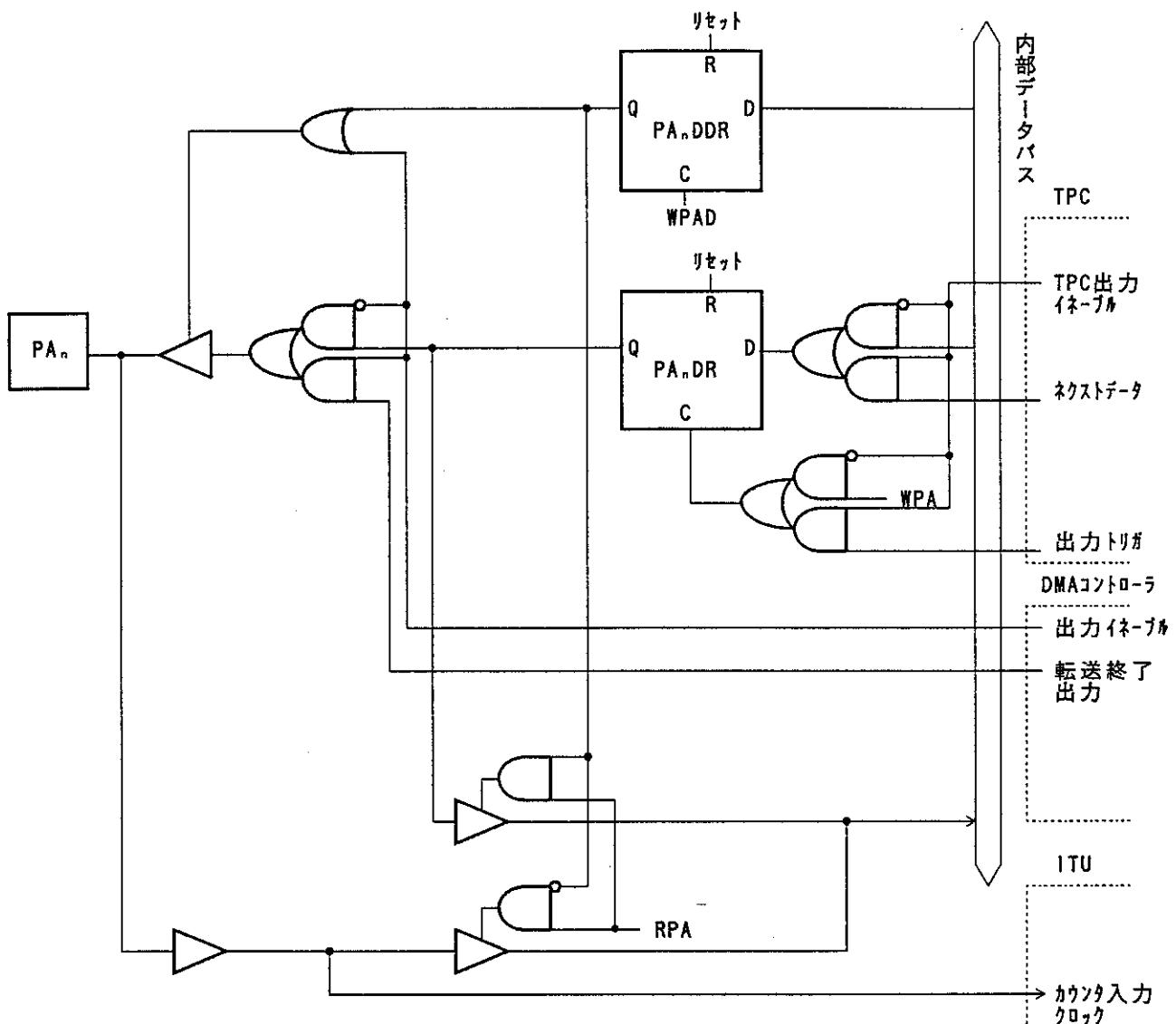

| C. 1 ポート 1 ブロック図                  | 886 |

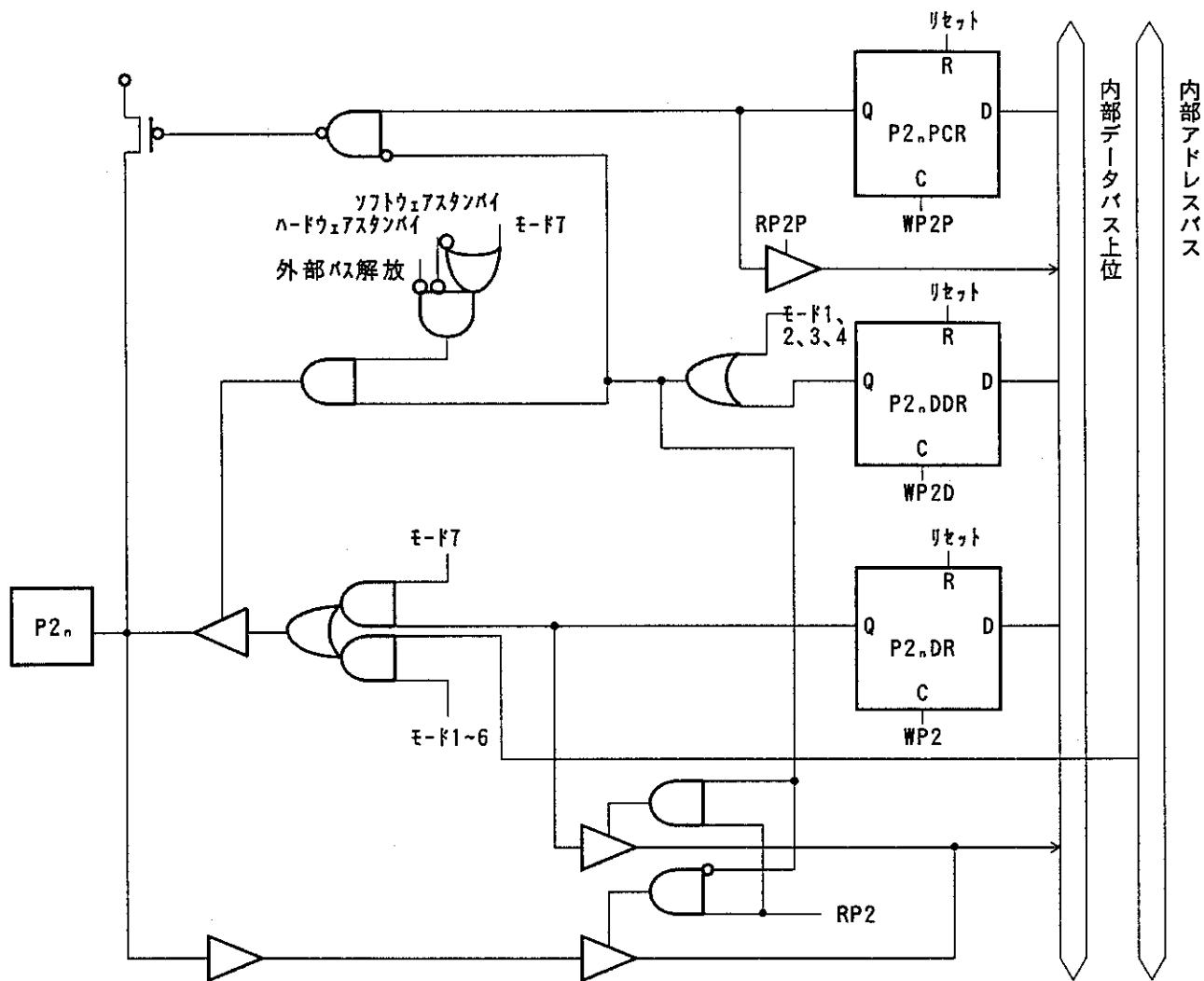

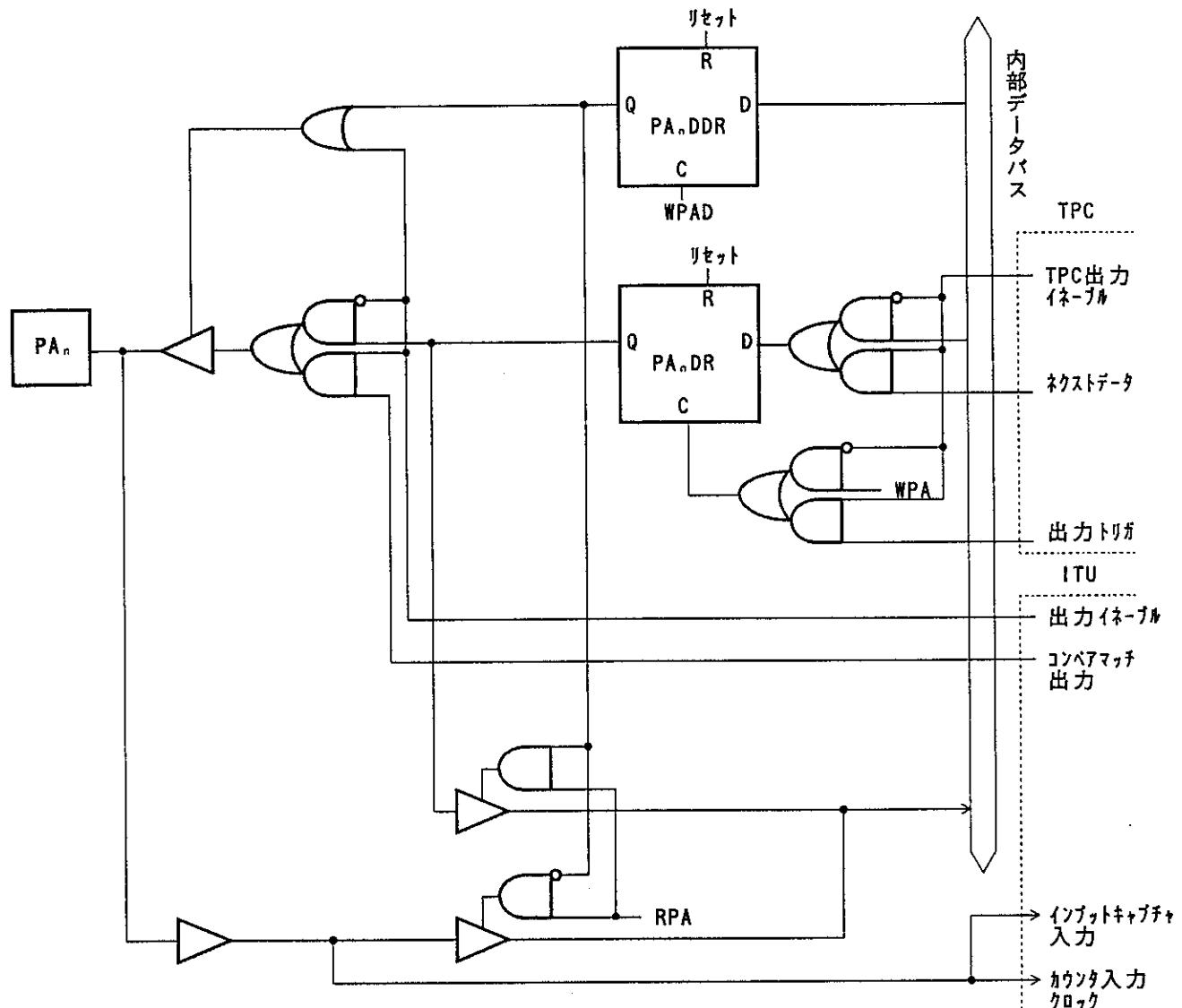

| C. 2 ポート 2 ブロック図                  | 887 |

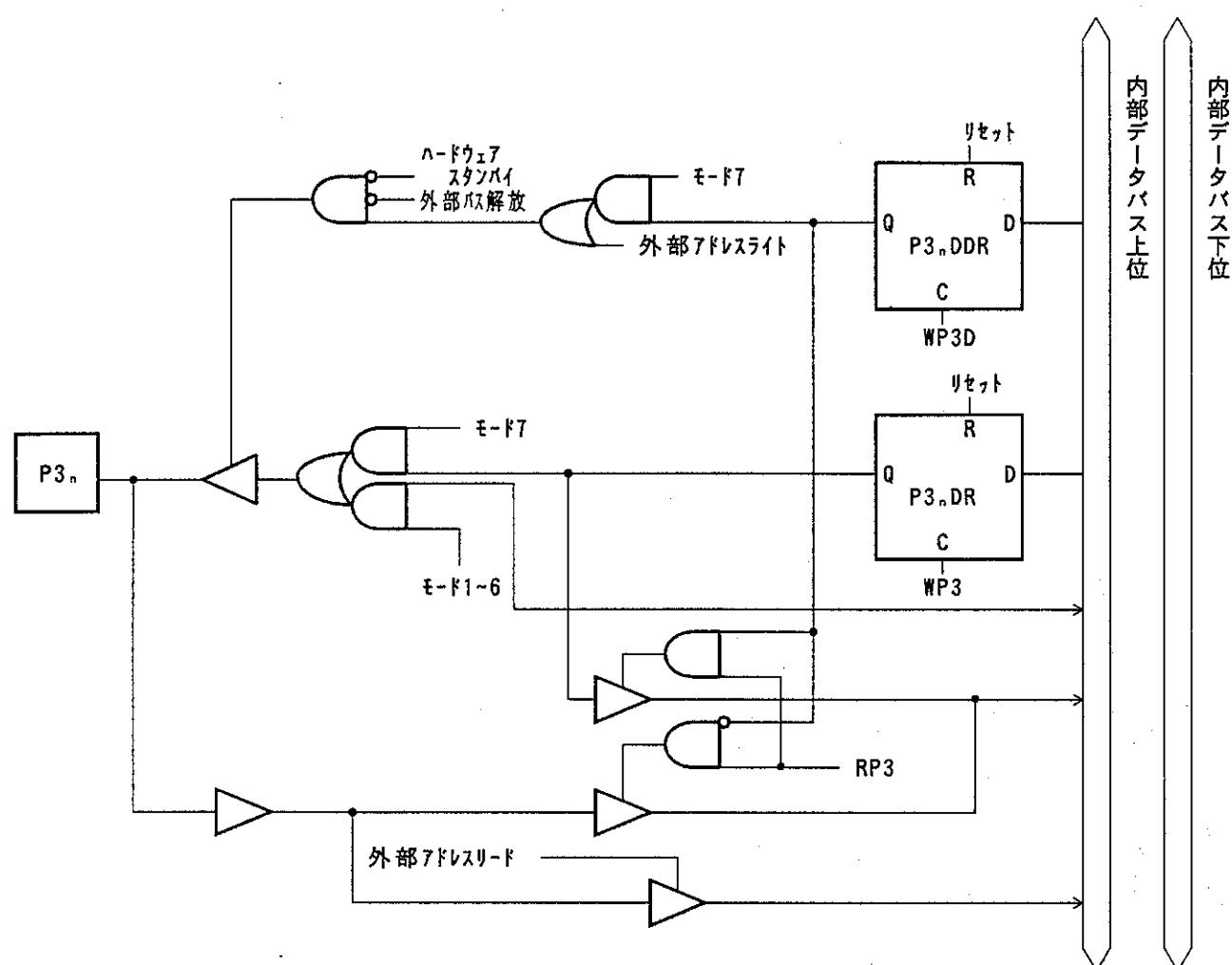

| C. 3 ポート 3 ブロック図                  | 888 |

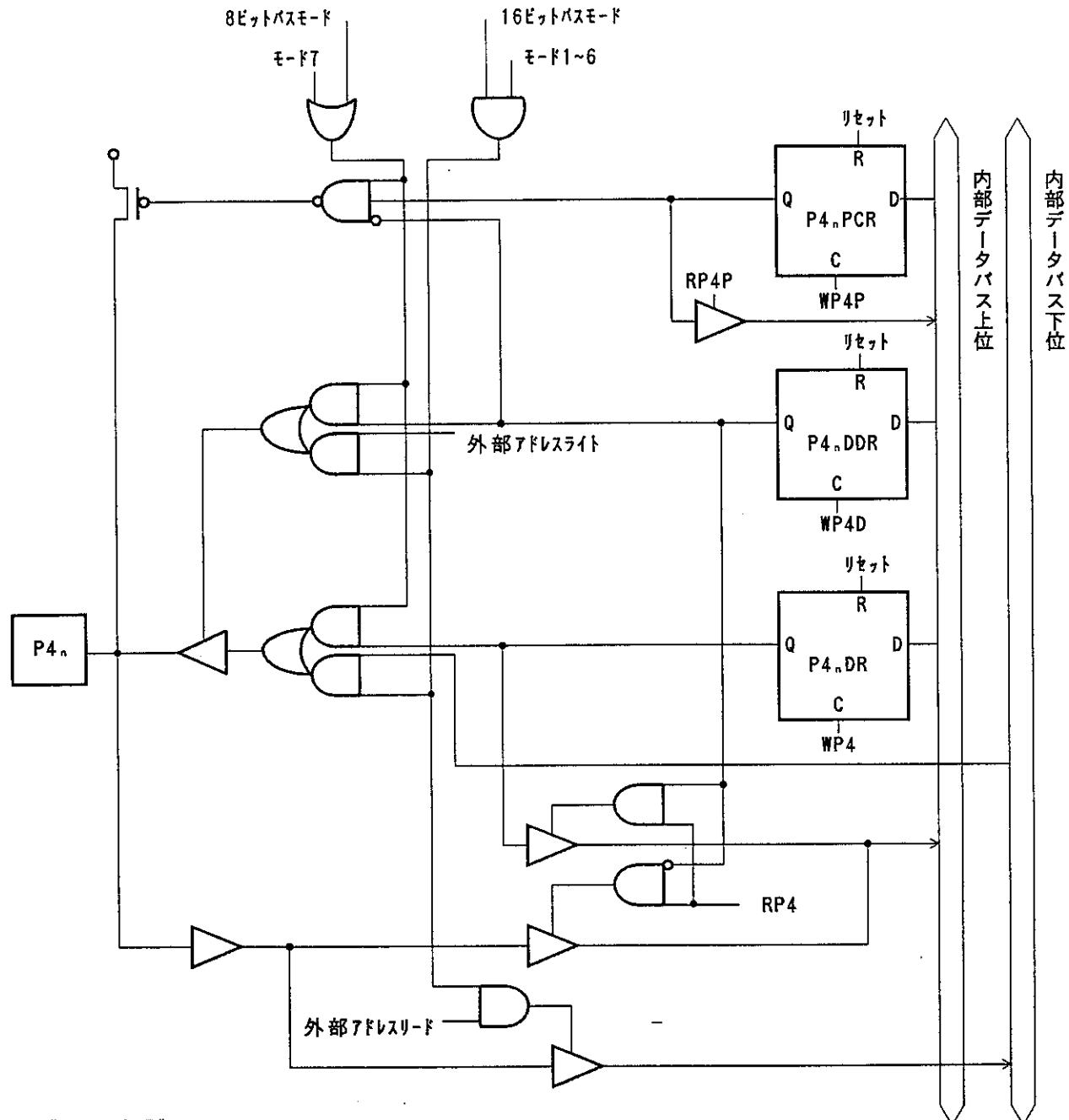

| C. 4 ポート 4 ブロック図                  | 889 |

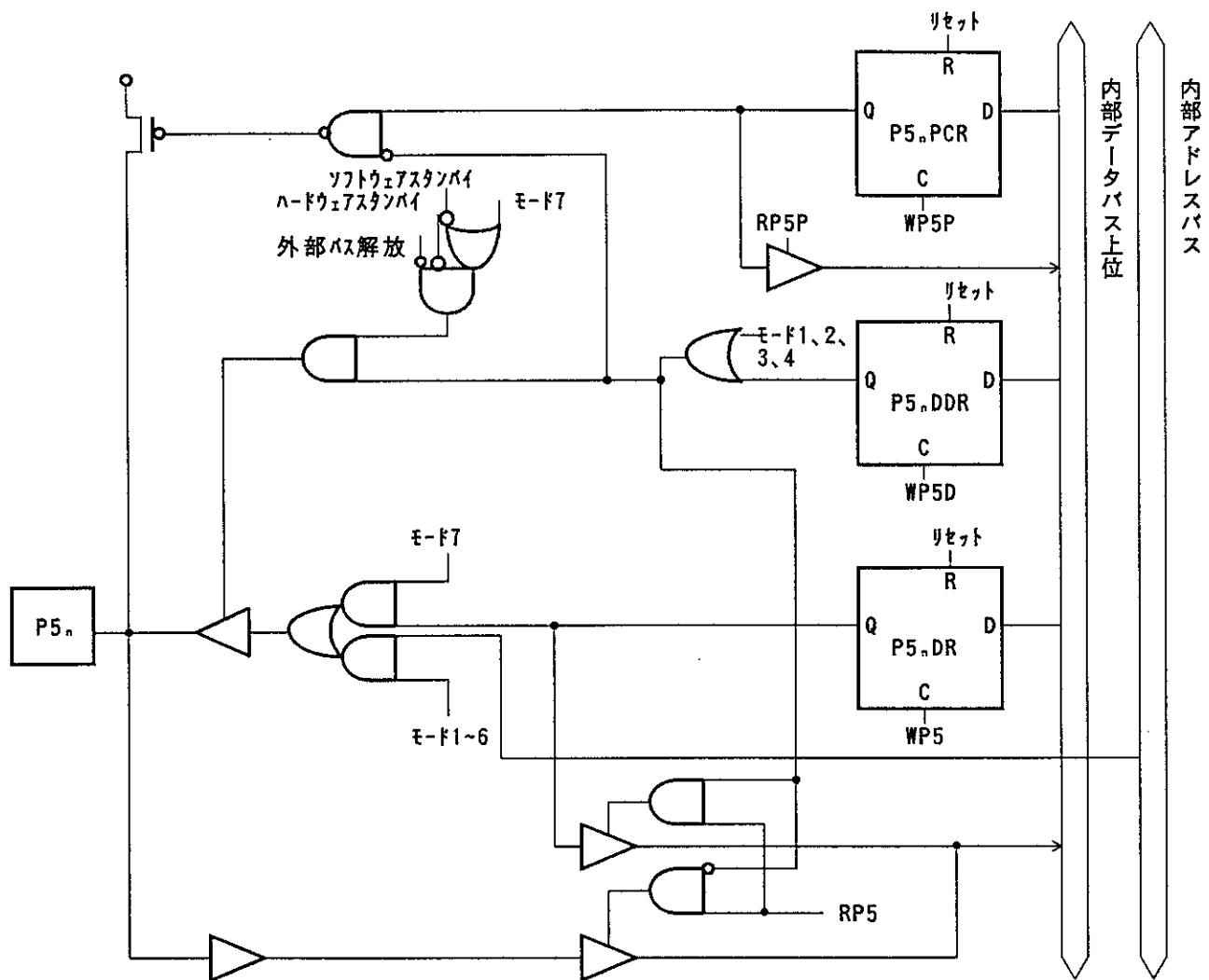

| C. 5 ポート 5 ブロック図                  | 890 |

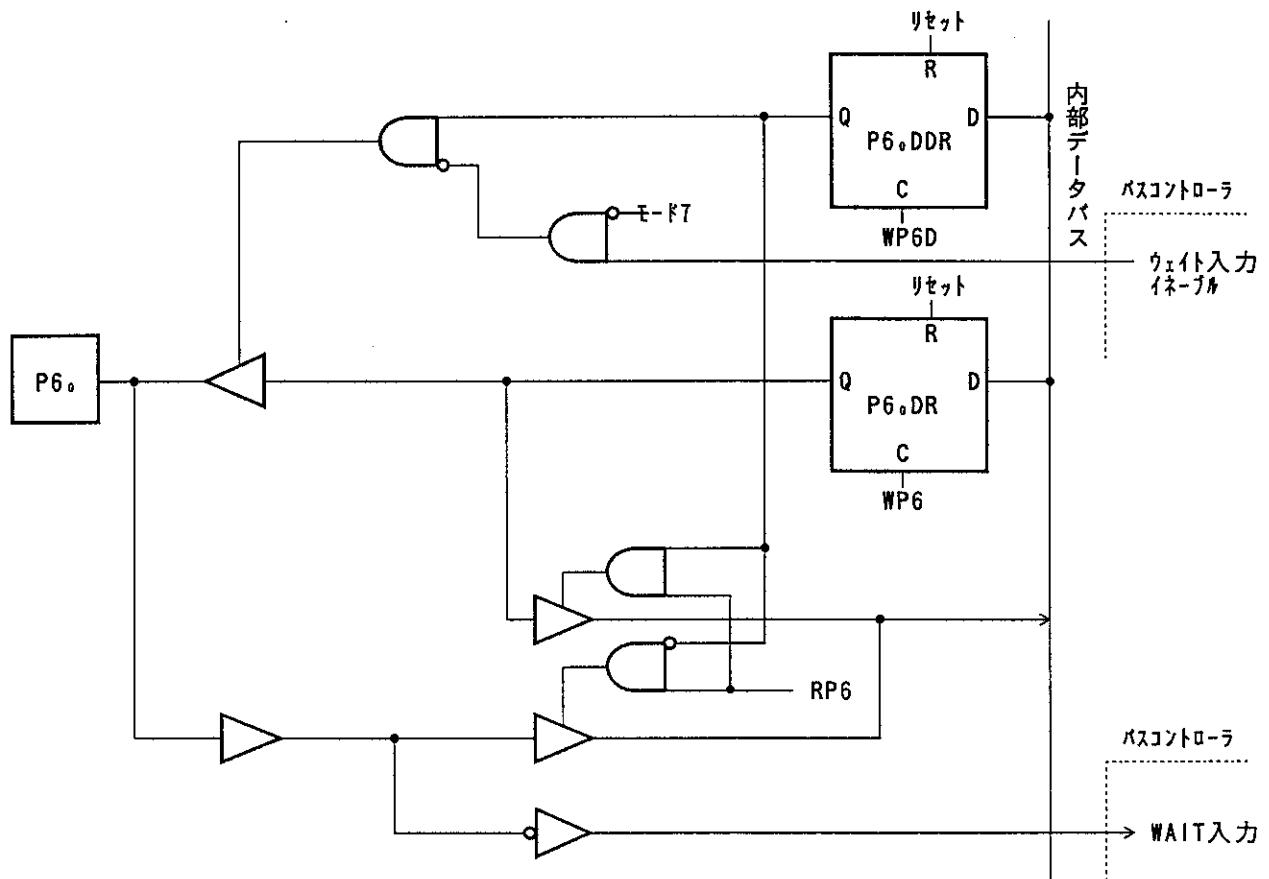

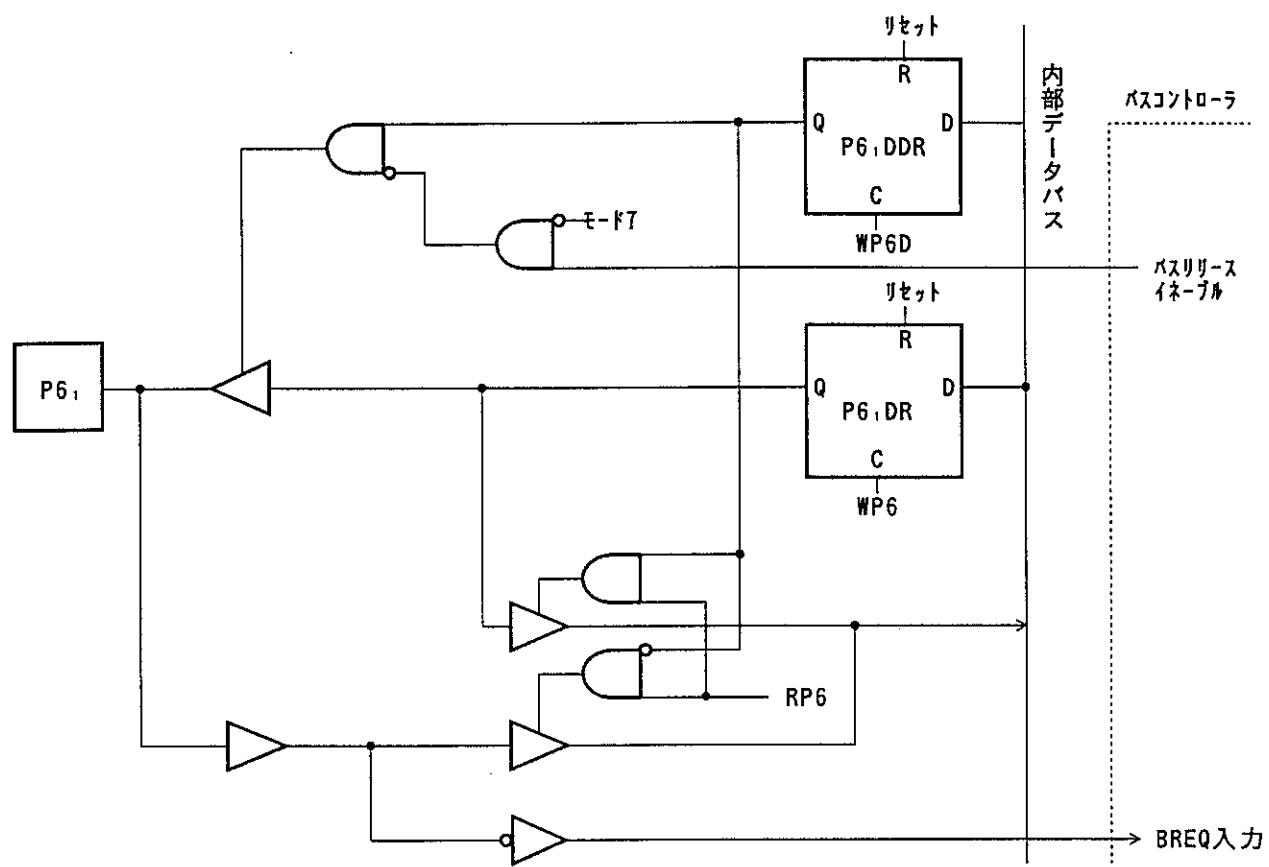

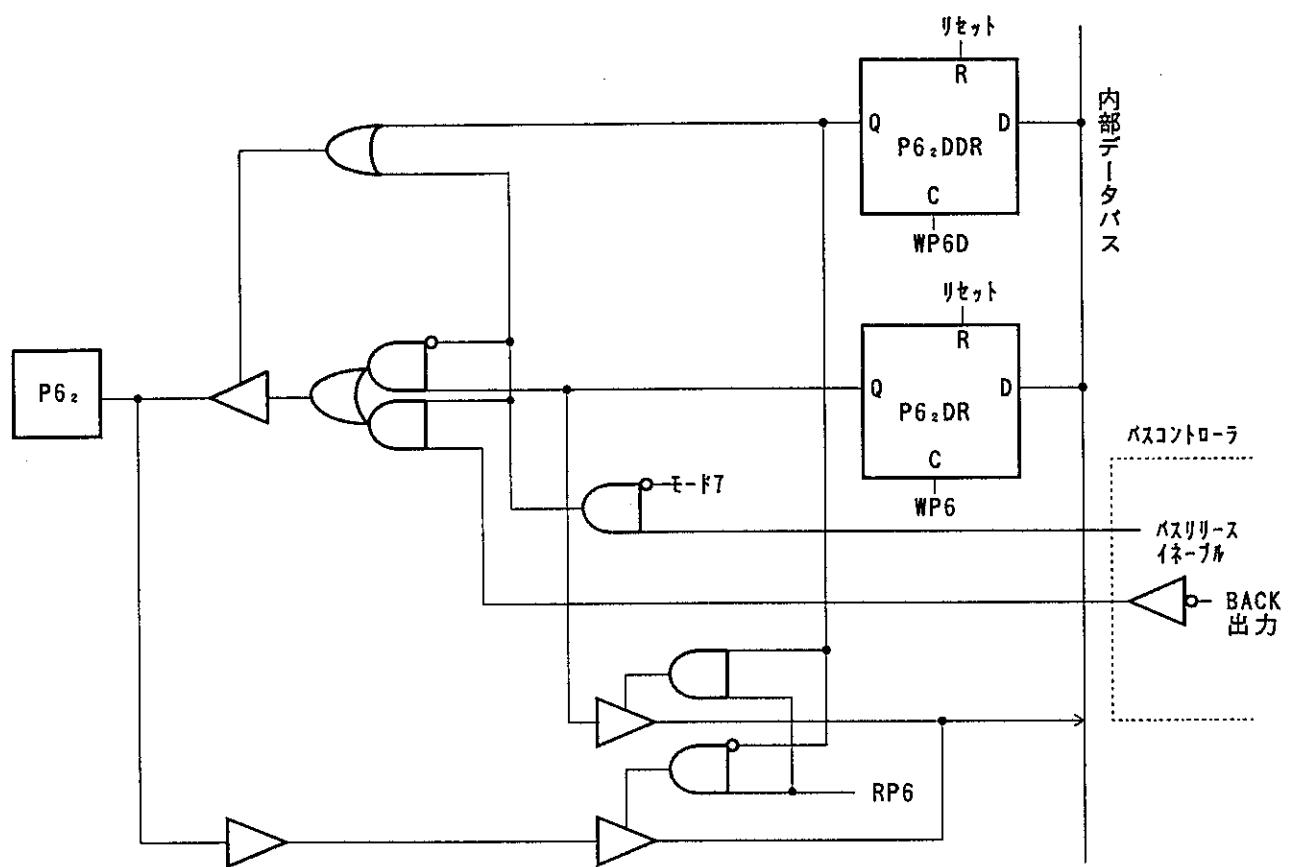

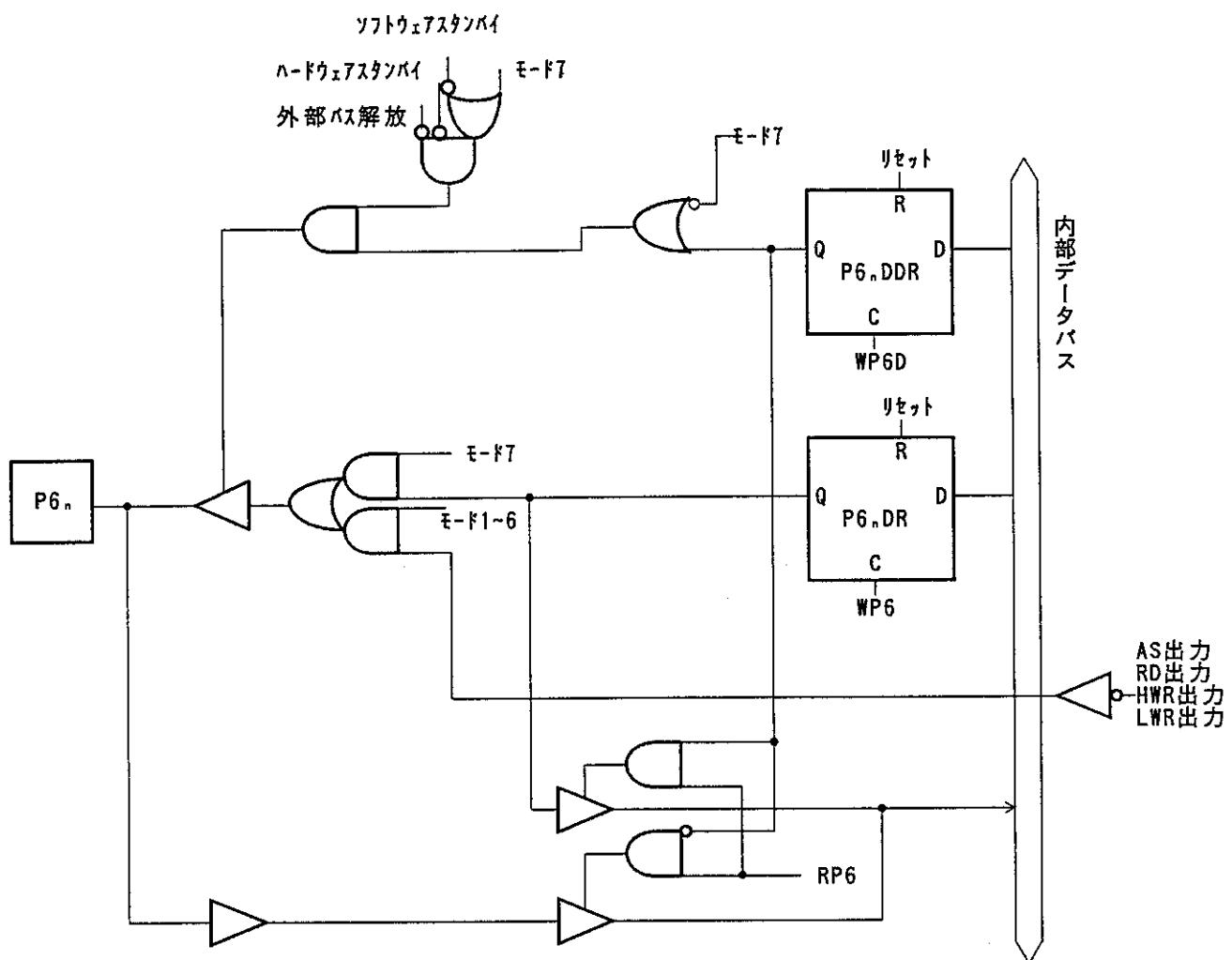

| C. 6 ポート 6 ブロック図                  | 891 |

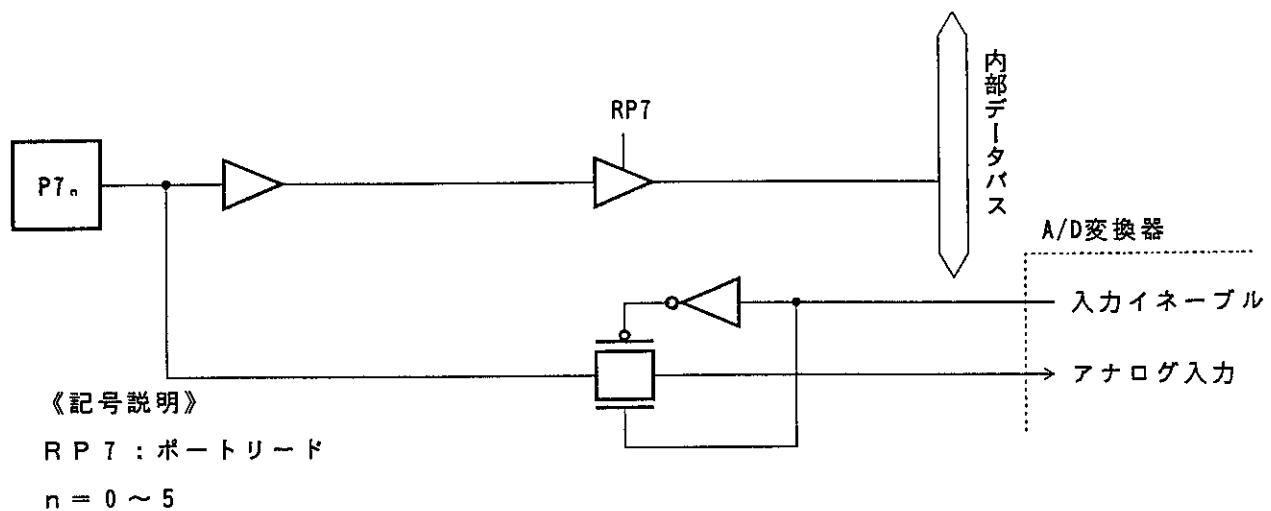

| C. 7 ポート 7 ブロック図                  | 895 |

| C. 8 ポート 8 ブロック図                  | 896 |

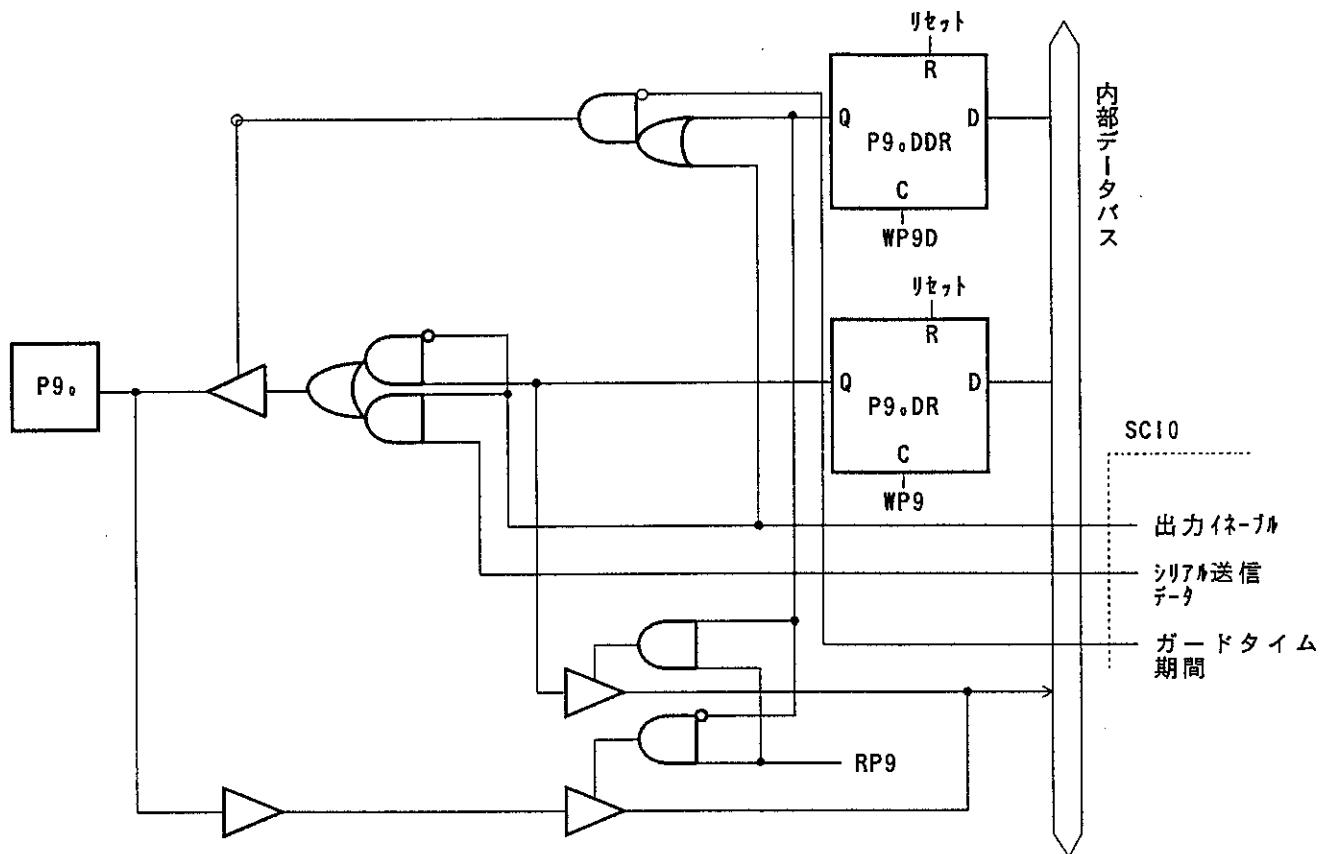

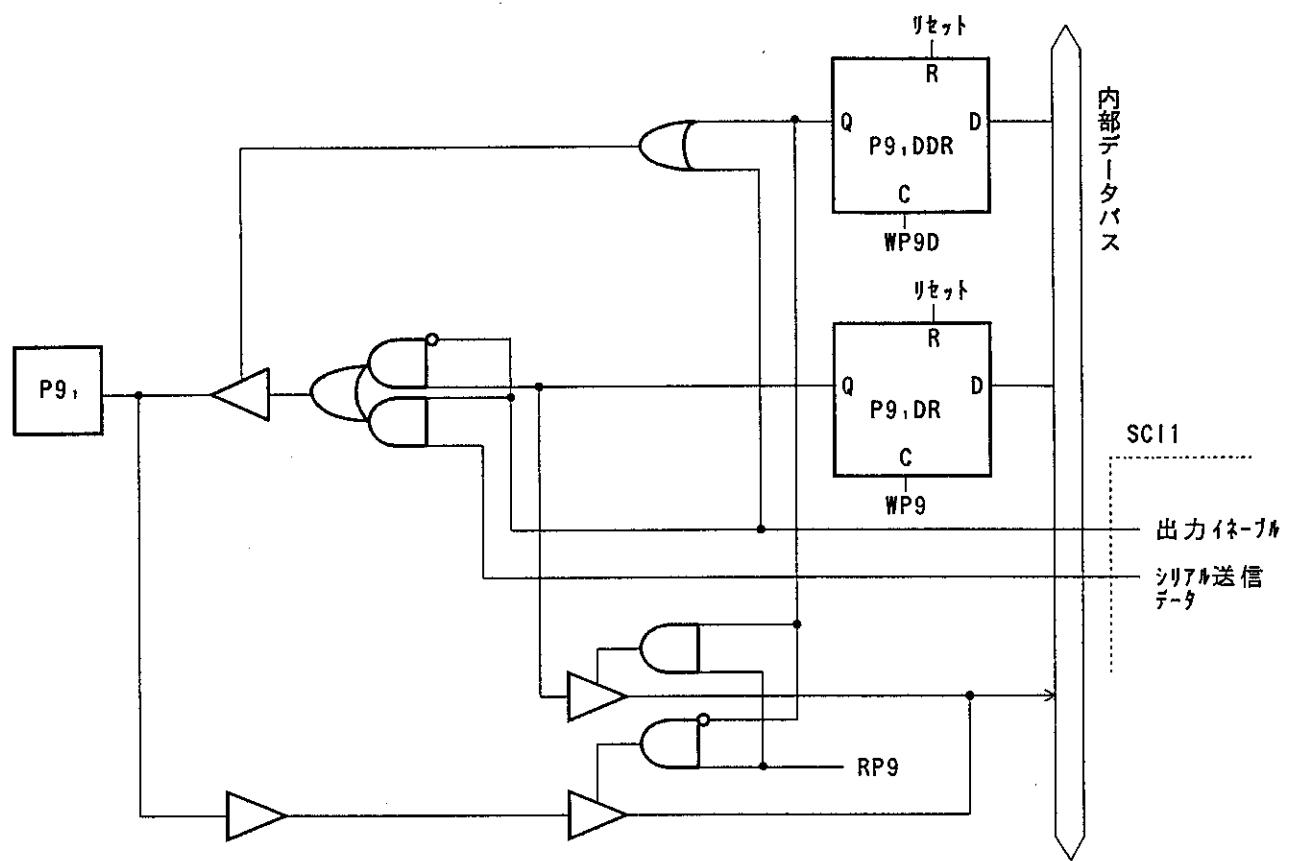

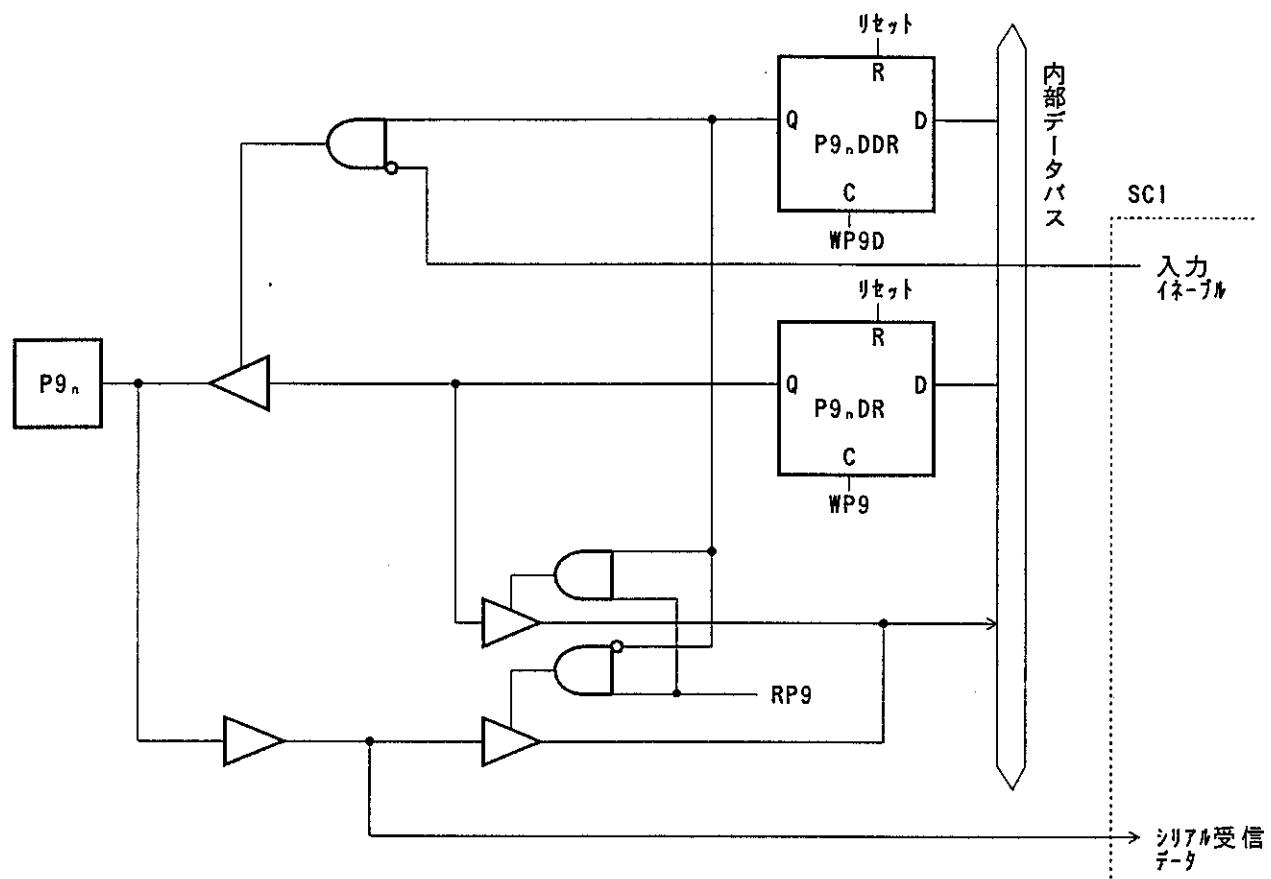

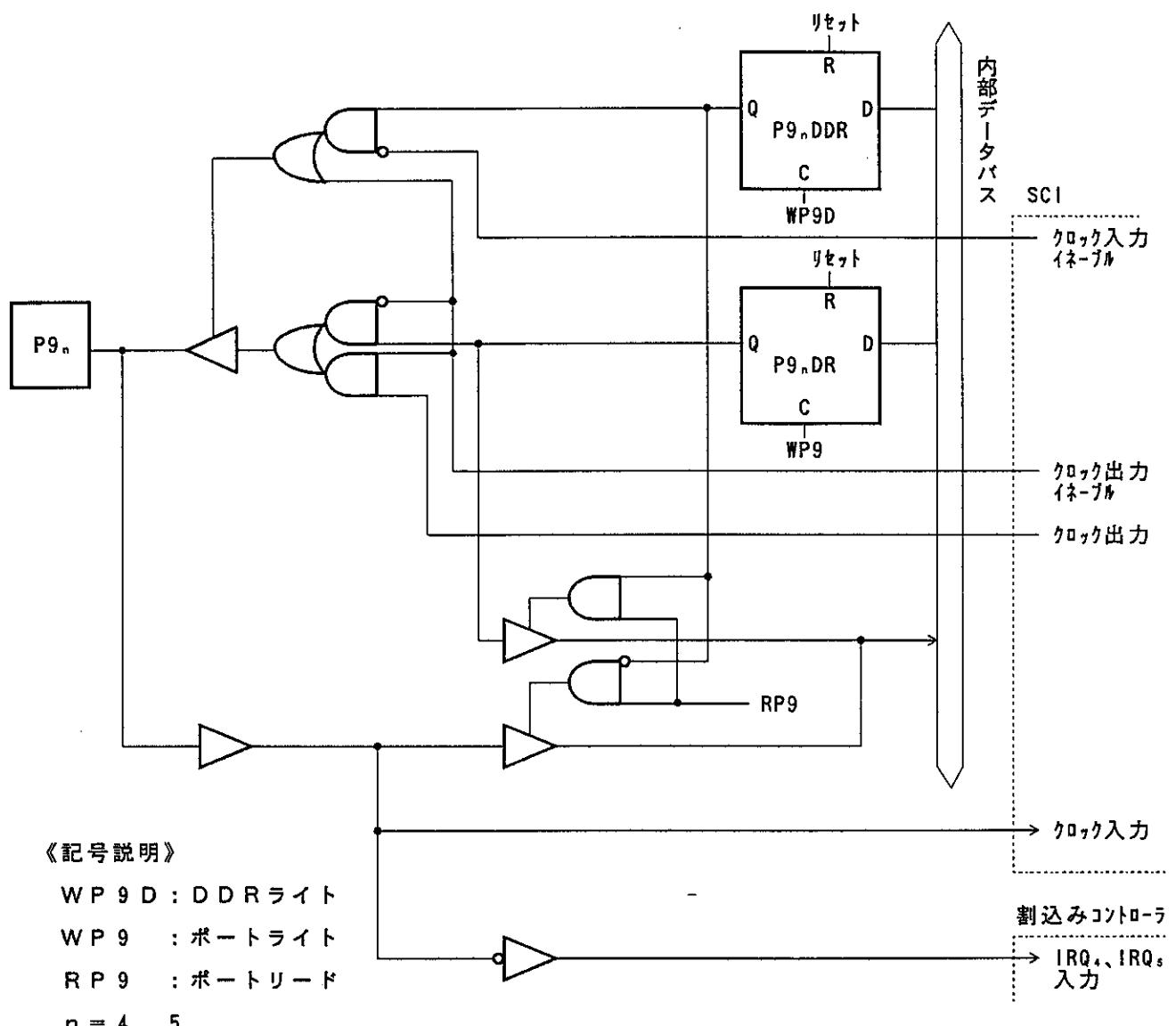

| C. 9 ポート 9 ブロック図                  | 899 |

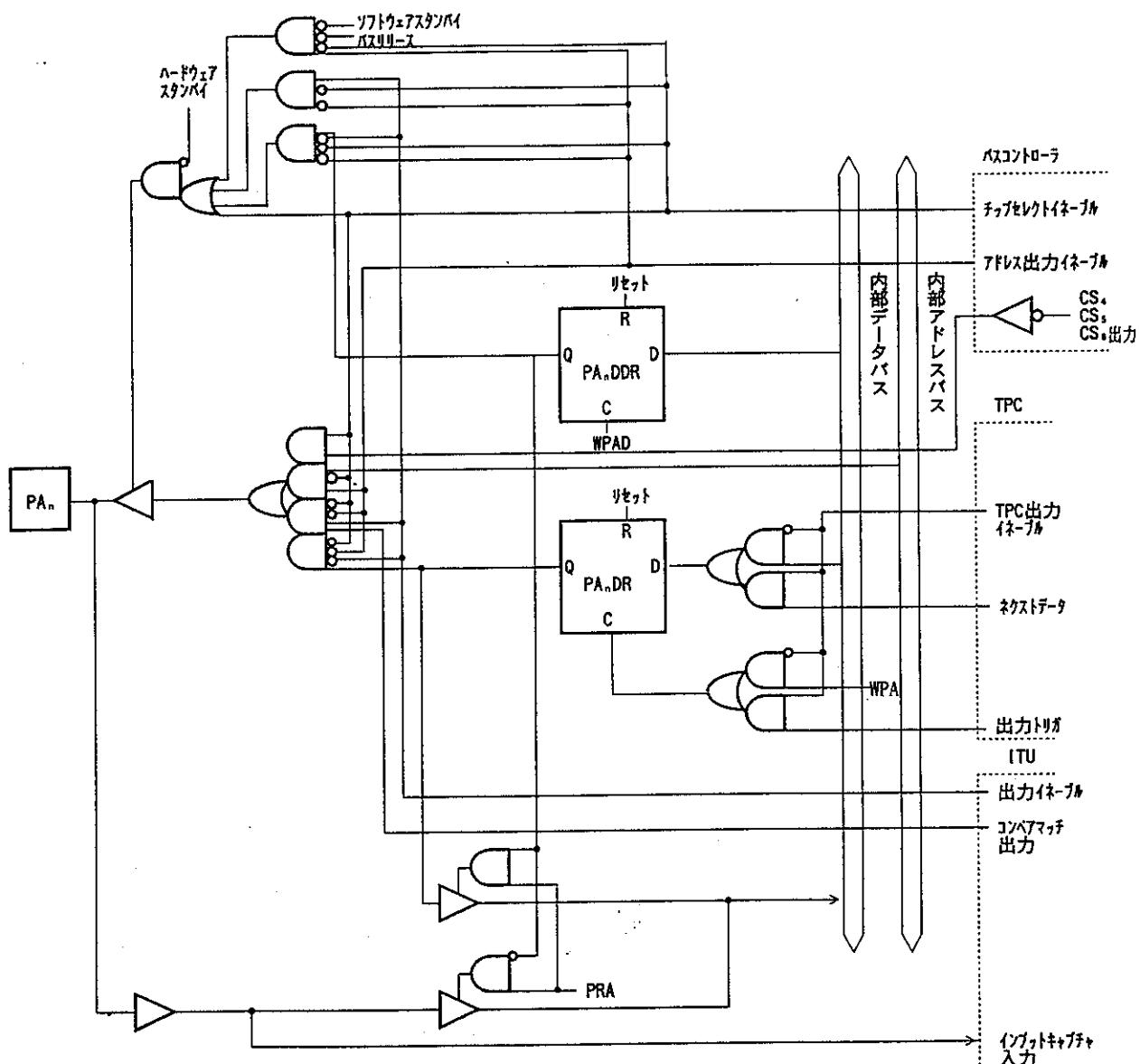

| C. 10 ポート A ブロック図                 | 903 |

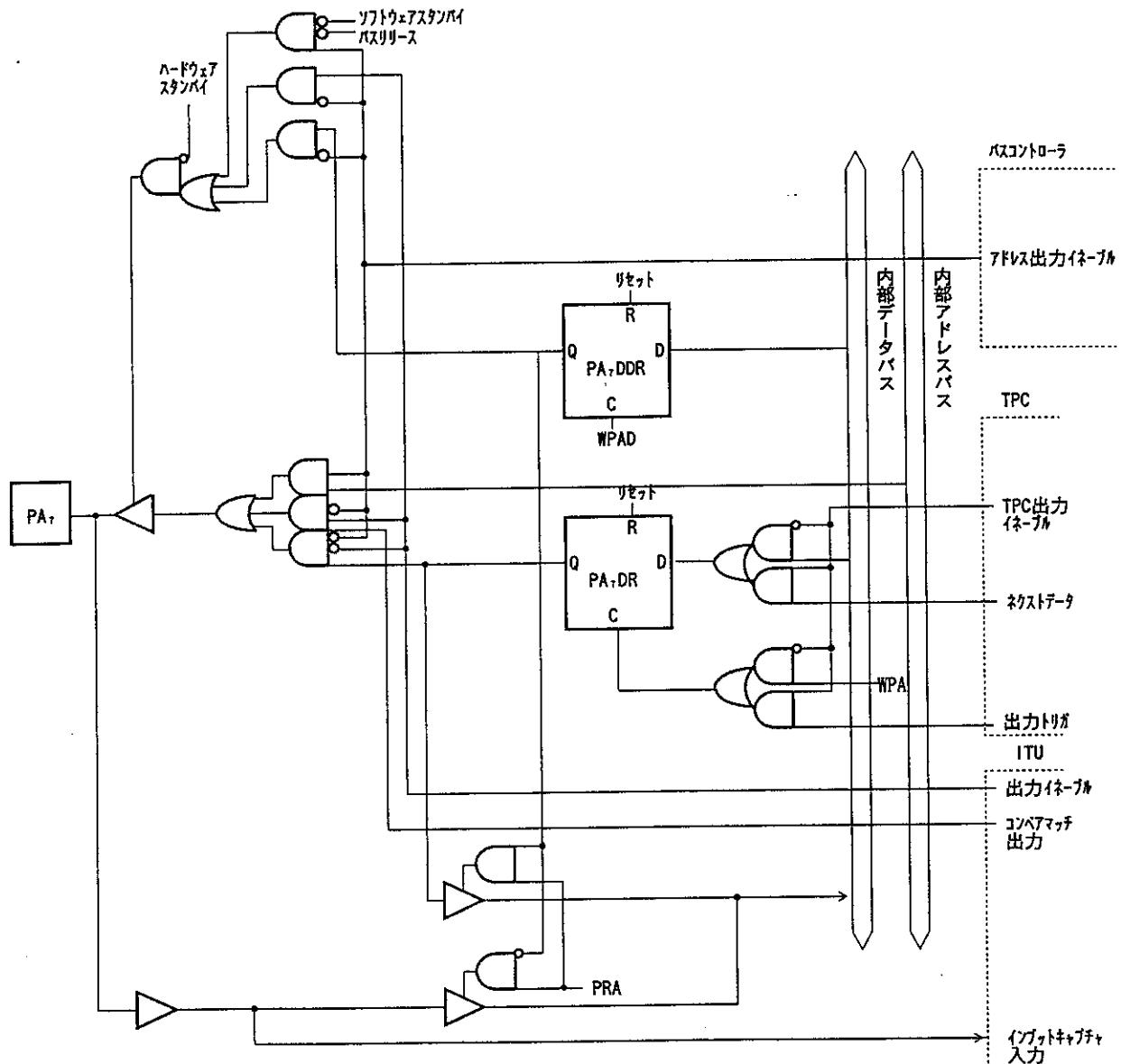

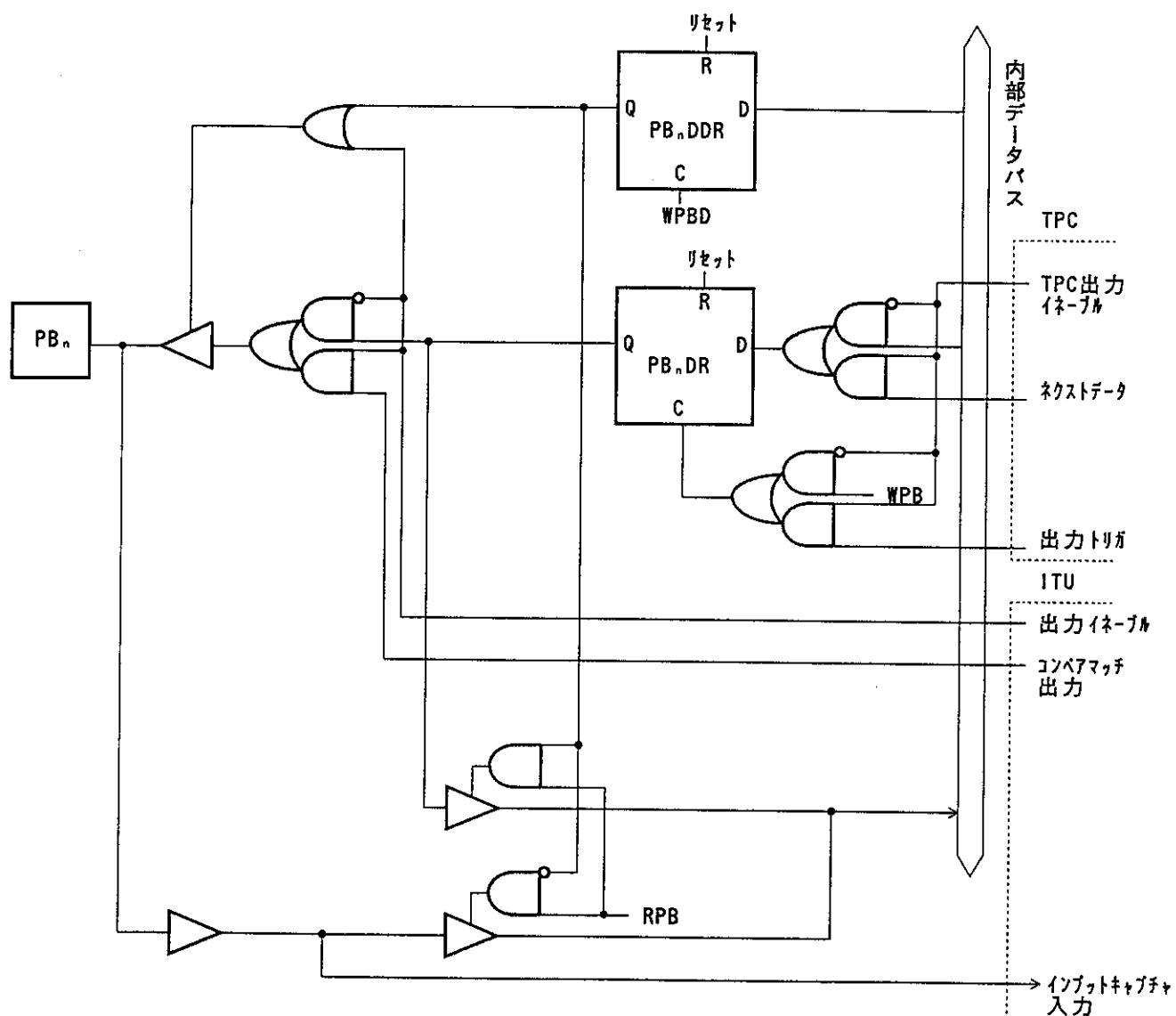

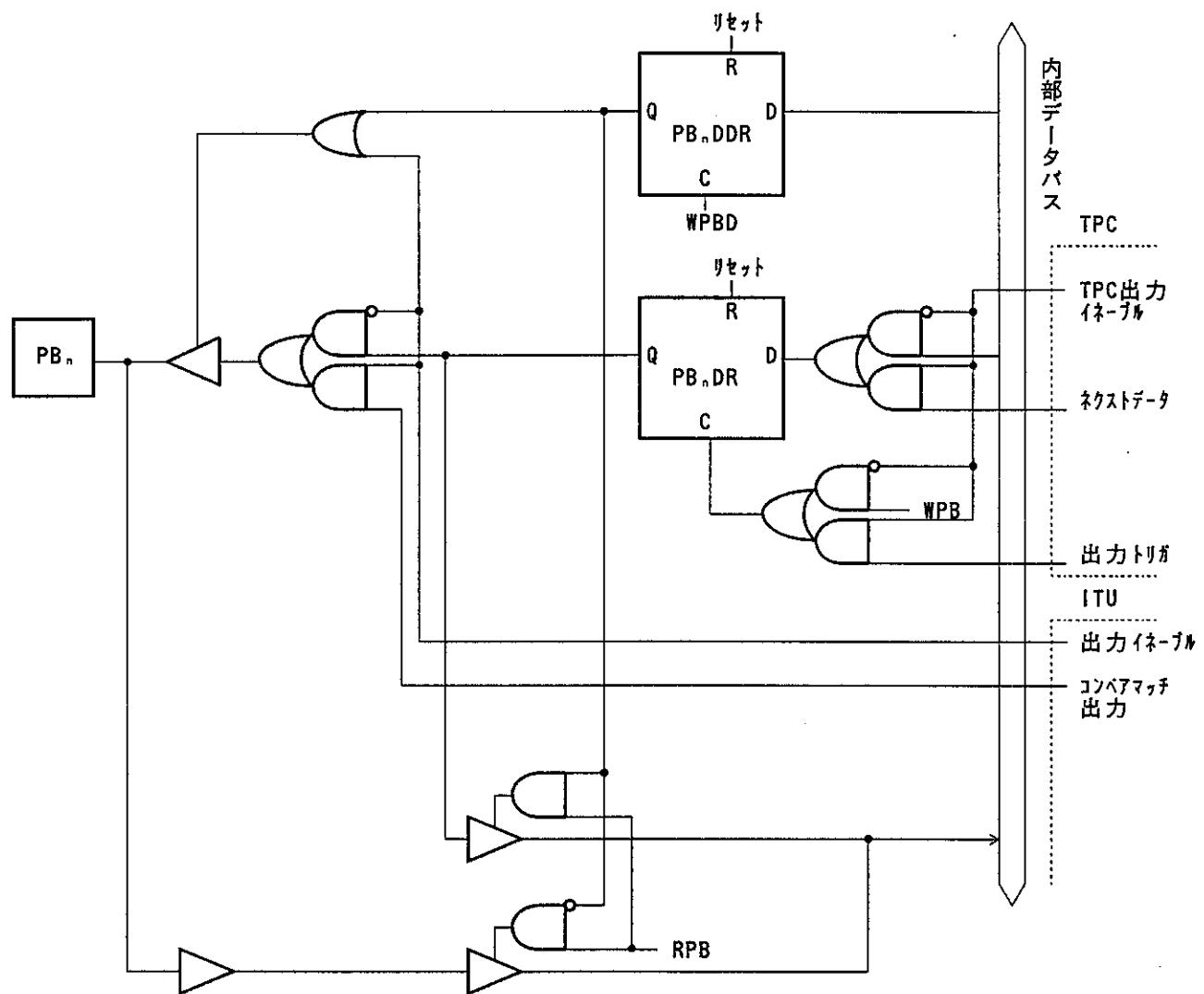

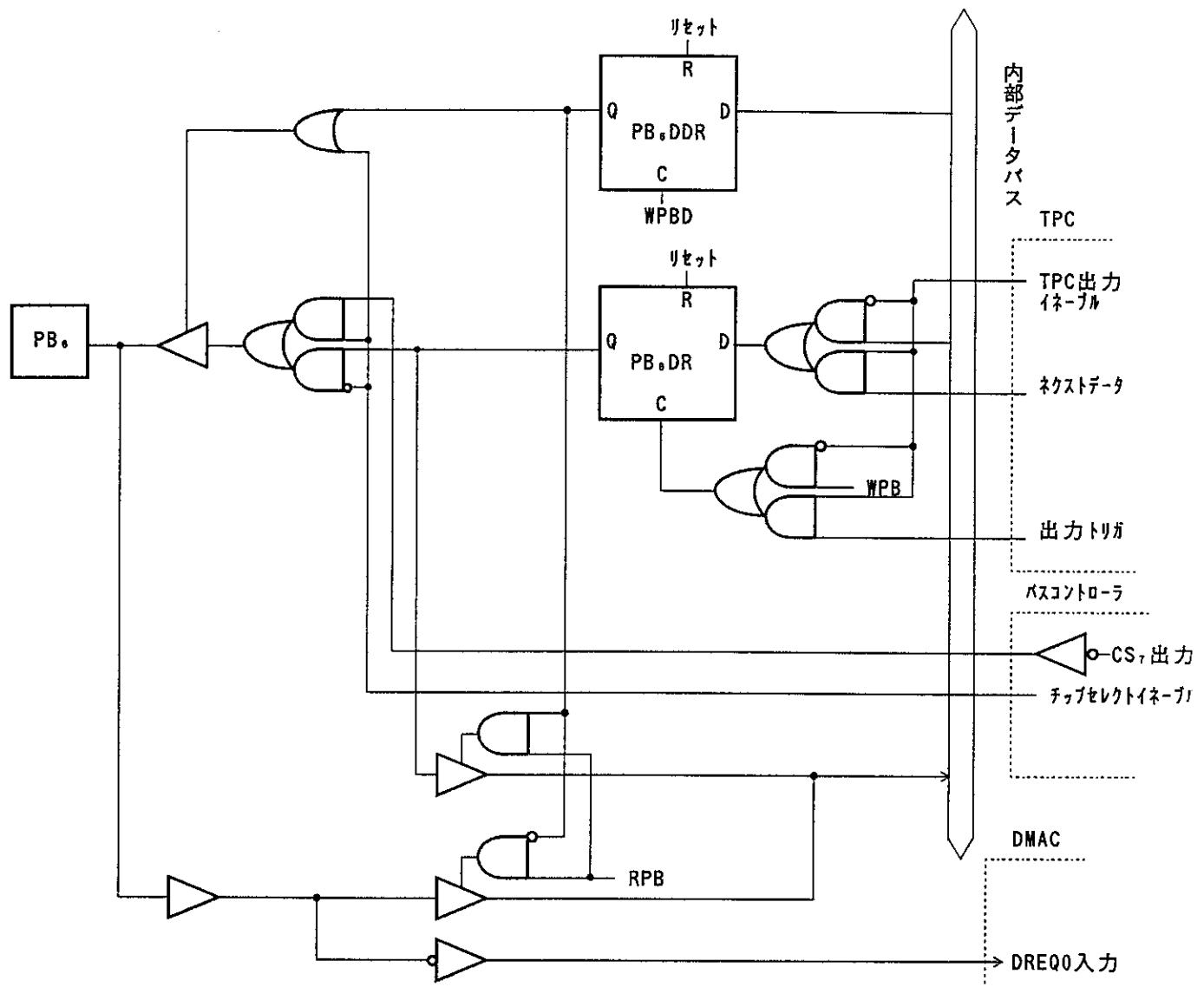

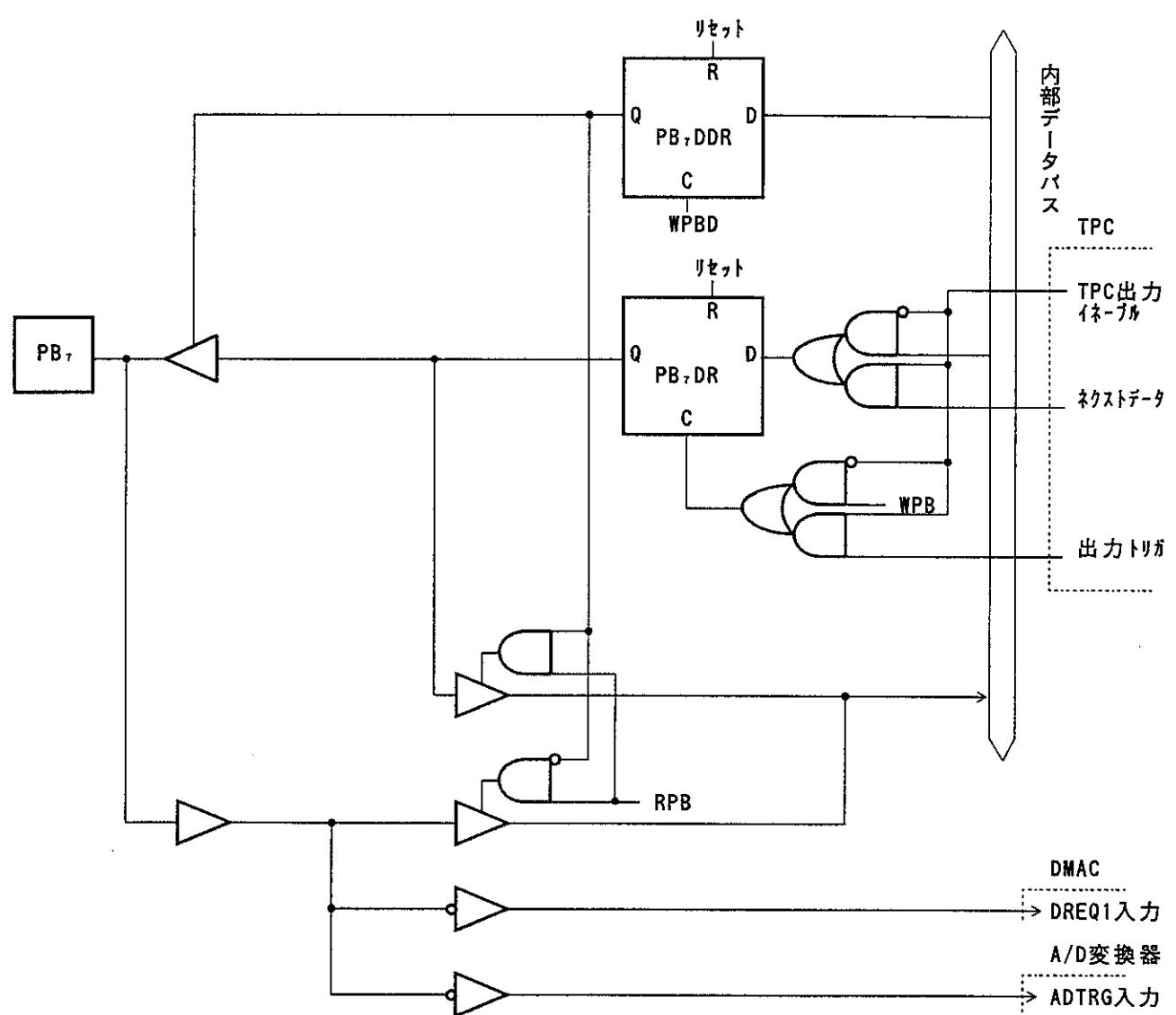

| C. 11 ポート B ブロック図                 | 907 |

| D. 端子状態                           | 911 |

| D. 1 各処理状態におけるポートの状態              | 911 |

| D. 2 リセット時の端子状態                   | 914 |

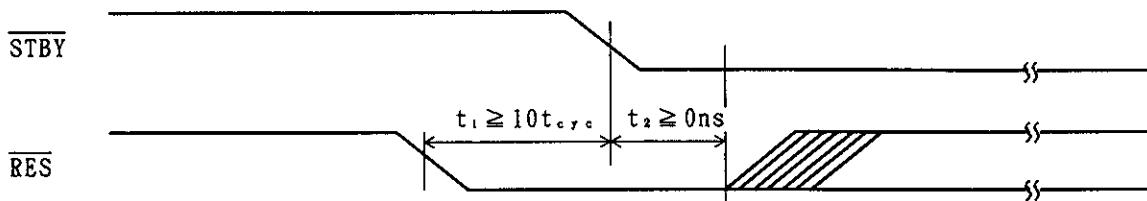

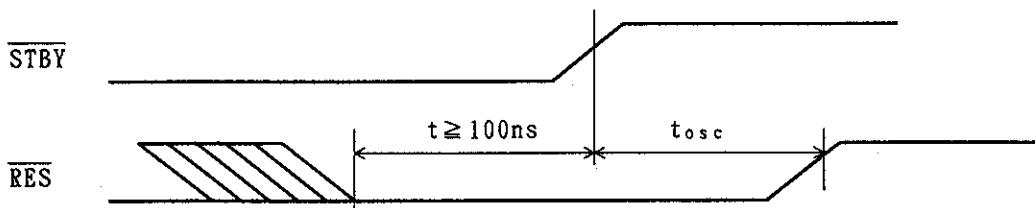

| E. ハードウェアスタンバイモード遷移／復帰時のタイミングについて | 917 |

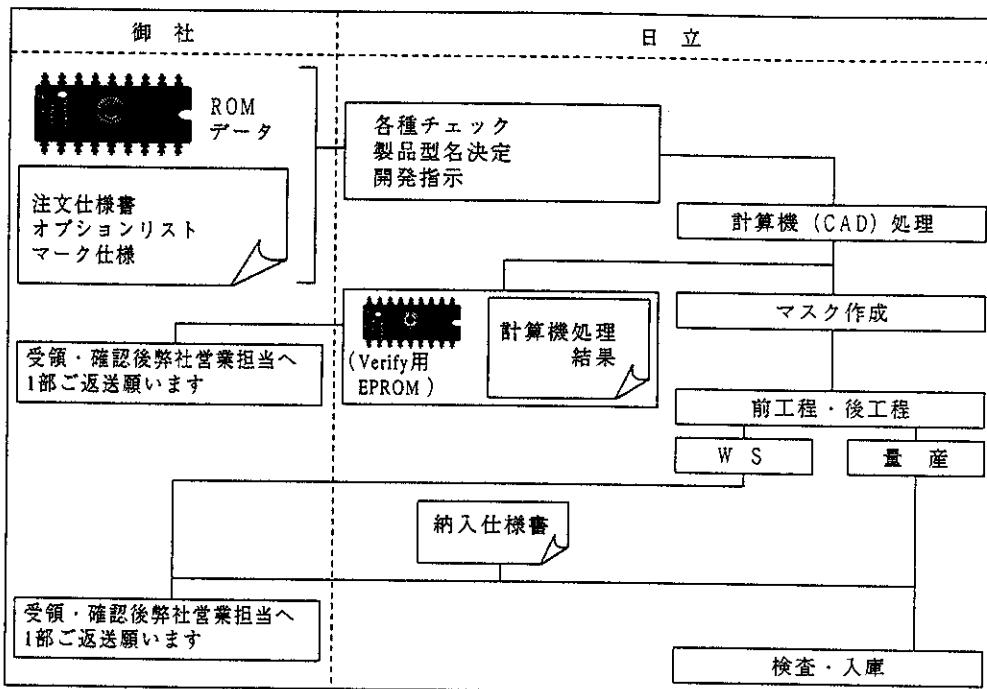

| F. ROM発注手順                        | 918 |

| F. 1 ROM書き換え品開発の流れ（発注手順）          | 918 |

| F. 2 ROM発注時の注意事項                  | 919 |

| G. 型名一覧                           | 920 |

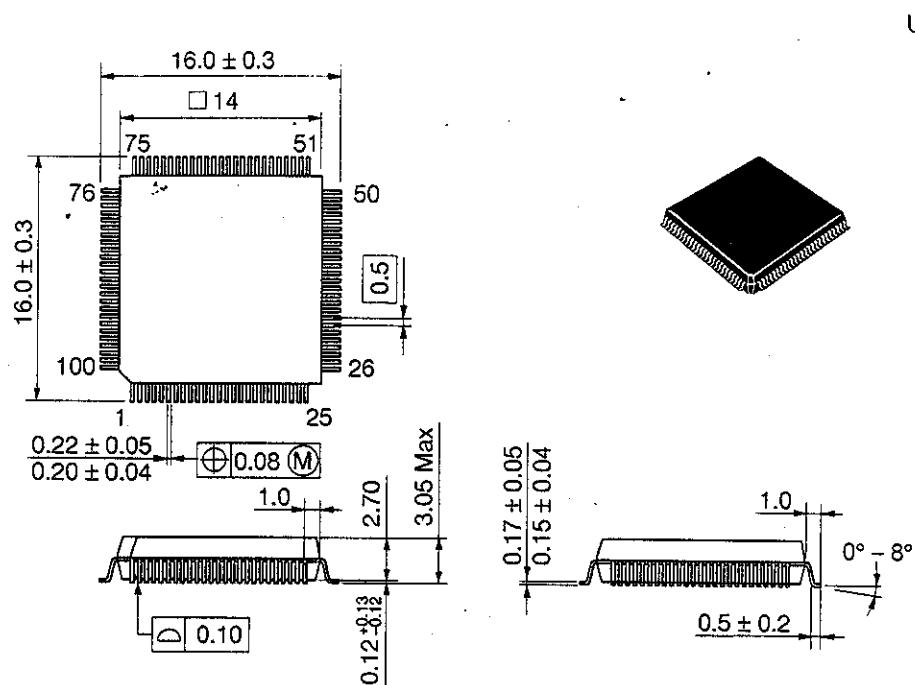

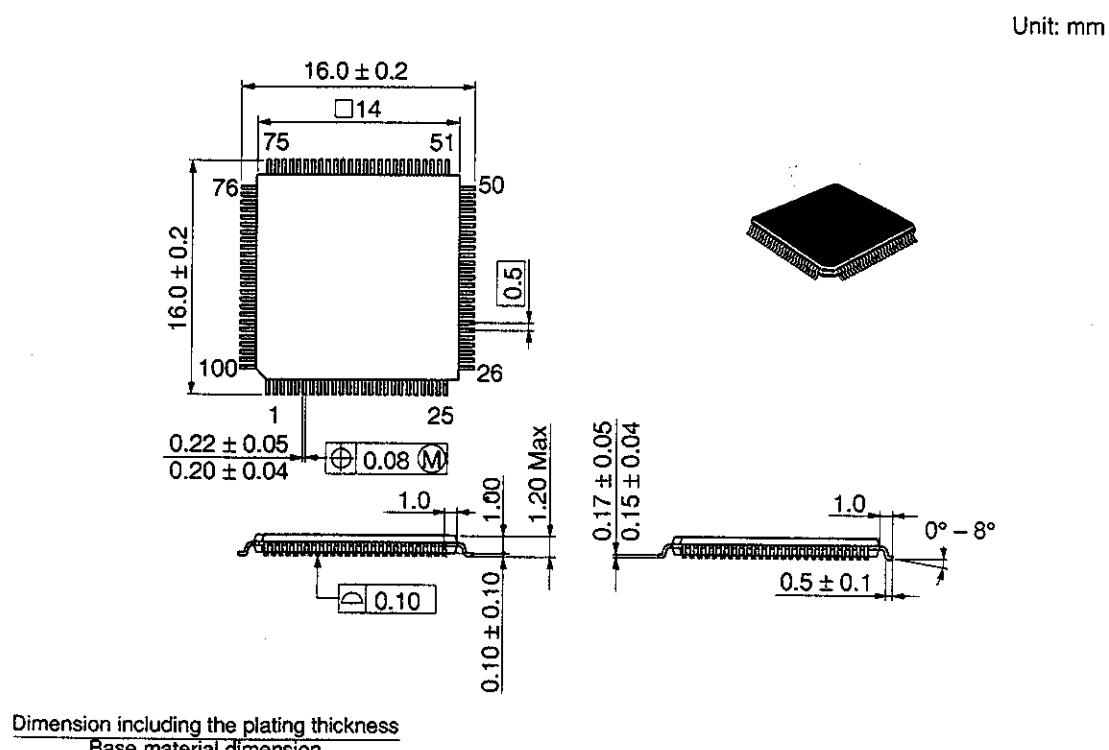

| H. 外形寸法図                          | 921 |

付録

## A. 命令

### A. 1 命令一覧

《オペレーションの記号》

| 記号      | 内容                                             |

|---------|------------------------------------------------|

| R d     | デスティネーション側の汎用レジスタ                              |

| R s     | ソース側の汎用レジスタ                                    |

| R n     | 汎用レジスタ                                         |

| E R d   | デスティネーション側の汎用レジスタ<br>(アドレスレジスタまたは32ビットレジスタ)    |

| E R s   | ソース側の汎用レジスタ (アドレスレジスタまたは32ビットレジスタ)             |

| E R n   | 汎用レジスタ (32ビットレジスタ)                             |

| (E A d) | デスティネーションオペランド                                 |

| (E A s) | ソースオペランド                                       |

| P C     | プログラムカウンタ                                      |

| S P     | スタックポインタ                                       |

| C C R   | コンディションコードレジスタ                                 |

| N       | C C R の N (ネガティブ) フラグ                          |

| Z       | C C R の Z (ゼロ) フラグ                             |

| V       | C C R の V (オーバフロー) フラグ                         |

| C       | C C R の C (キャリ) フラグ                            |

| d i s p | ディスペリースメント                                     |

| →       | 左辺のオペランドから右辺のオペランドへの転送、<br>または左辺の状態から右辺の状態への遷移 |

| +       | 両辺のオペランドを加算                                    |

| -       | 左辺のオペランドから右辺のオペランドを減算                          |

| ×       | 両辺のオペランドを乗算                                    |

| ÷       | 左辺のオペランドを右辺のオペランドで除算                           |

| ^       | 両辺のオペランドの論理積                                   |

| ∨       | 両辺のオペランドの論理和                                   |

| ⊕       | 両辺のオペランドの排他的論理和                                |

| ～       | 反転論理 (論理的補数)                                   |

| ( ) < > | オペランドの内容                                       |

【注】 汎用レジスタは、8ビット (R 0 H～R 7 H、R 0 L～R 7 L) または16ビット (R 0～R 7、E 0～E 7) です。

《コンディションコードの記号》

| 記号 | 内容                         |

|----|----------------------------|

| ↑  | 実行結果にしたがって変化することを表します。     |

| *  | 不確定であることを表します（値を保証しません）。   |

| 0  | 常に“0”にクリアされることを表します。       |

| 1  | 常に“1”にセットされることを表します。       |

| -  | 実行結果に影響を受けないことを表します。       |

| △  | 条件によって異なります。注意事項を参照してください。 |

表 A. 1 命令セット一覧(1)

## (1) データ転送命令

| データモード | サイズ                     | アドレッシングモード/命令長(バイト) |    |      |           | オペレーション     |     |          |      | コンディショナルコード               |   |   |   | 実行バス数 |   |   |      |

|--------|-------------------------|---------------------|----|------|-----------|-------------|-----|----------|------|---------------------------|---|---|---|-------|---|---|------|

|        |                         | #xx                 | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @@aa | -                         | I | H | N | Z     | V | C | J-ZW |

| MOV    | B #xx:8, Rd             | B                   | 2  |      |           |             |     |          |      | #xx:8→Rd8                 | - | - | ↑ | ↑     | 0 | - | 2    |

|        | MOV, B Rs, Rd           | B                   | 2  |      |           |             |     |          |      | Rs8→Rd8                   | - | - | ↑ | ↑     | 0 | - | 2    |

|        | MOV, B @ERs, Rd         | B                   | 2  |      |           |             |     |          |      | @ERs→Rd8                  | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, B @(d:16, ERs), Rd | B                   | 4  |      |           |             |     |          |      | @(d:16, ERs)→Rd8          | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B @(d:24, ERs), Rd | B                   | 8  |      |           |             |     |          |      | @(d:24, ERs)→Rd8          | - | - | ↑ | ↑     | 0 | - | 10   |

|        | MOV, B @ERs+, Rd        | B                   |    |      |           |             |     |          |      | @ERs+→Rd8, ERs32+1→ERs32  | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B @@aa:8, Rd       | B                   |    |      |           |             |     |          |      | @aa:8→Rd8                 | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, B @aa:16, Rd       | B                   |    |      |           |             |     |          |      | @aa:16→Rd8                | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B @aa:24, Rd       | B                   |    |      |           |             |     |          |      | @aa:24→Rd8                | - | - | ↑ | ↑     | 0 | - | 8    |

|        | MOV, B Rs, @ERd         | B                   | 2  |      |           |             |     |          |      | Rs8→@ERd                  | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, B Rs, @(d:16, ERd) | B                   | 4  |      |           |             |     |          |      | Rs8→@(d:16, ERd)          | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B Rs, @(d:24, ERd) | B                   | 8  |      |           |             |     |          |      | Rs8→@(d:24, ERd)          | - | - | ↑ | ↑     | 0 | - | 10   |

|        | MOV, B Rs, @(d:32, ERd) | B                   | 2  |      |           |             |     |          |      | ERd32-1→ERd32, Rs3→@ERd   | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B Rs, @aa:8        | B                   |    |      |           |             |     |          |      | Rs8→@aa:8                 | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, B Rs, @aa:16       | B                   |    |      |           |             |     |          |      | Rs8→@aa:16                | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, B Rs, @aa:24       | B                   |    |      |           |             |     |          |      | Rs8→@aa:24                | - | - | ↑ | ↑     | 0 | - | 8    |

|        | MOV, W #xx:16, Rd       | W                   | 4  |      |           |             |     |          |      | #xx:16→Rd16               | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, W Rs, Rd           | W                   | 2  |      |           |             |     |          |      | Rs16→Rd16                 | - | - | ↑ | ↑     | 0 | - | 2    |

|        | MOV, W @ERs, Rd         | W                   | 2  |      |           |             |     |          |      | @ERs→Rd16                 | - | - | ↑ | ↑     | 0 | - | 4    |

|        | MOV, W @(d:16, ERs), Rd | W                   | 4  |      |           |             |     |          |      | @(d:16, ERs)→Rd16         | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, W @(d:24, ERs), Rd | W                   | 8  |      |           |             |     |          |      | @(d:24, ERs)→Rd16         | - | - | ↑ | ↑     | 0 | - | 10   |

|        | MOV, W @ERs+, Rd        | W                   |    |      |           |             |     |          |      | @ERs+→Rd16, ERs32+2→@Rd32 | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, W @aa:16, Rd       | W                   |    |      |           |             |     |          |      | @aa:16→Rd16               | - | - | ↑ | ↑     | 0 | - | 6    |

|        | MOV, W @@aa:24, Rd      | W                   |    |      |           |             |     |          |      | @aa:24→Rd16               | - | - | ↑ | ↑     | 0 | - | 8    |

表 A. 1 命令セット一覧(2)

|      | ニーモニック                   | サイズ | アドレッシングモード/命令長(バイト) |    |      |           | オペレーション    |     |          |      | コンディションコード                |   |   |   | 実行バス数 |   |   |      |

|------|--------------------------|-----|---------------------|----|------|-----------|------------|-----|----------|------|---------------------------|---|---|---|-------|---|---|------|

|      |                          |     | #xx                 | Rn | @ERn | @(d, ERn) | @ERn/@Rn+1 | @aa | @(d, PC) | @@aa | -                         | I | H | N | Z     | V | C | J-Z# |

| MOV  | MOV. W Rs, @ERd          | W   |                     | 2  |      |           |            |     |          |      | Rs16→@ERd                 | - | - | ↑ | 0     | - | - | 4    |

|      | MOV. W Rs, @(d:16, ERd)  | W   |                     | 4  |      |           |            |     |          |      | Rs16→@(d:16, ERd)         | - | - | ↑ | 0     | - | - | 6    |

|      | MOV. W Rs, @(d:24, ERd)  | W   |                     | 8  |      |           |            |     |          |      | Rs16→@(d:24, ERd)         | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. W Rs, @-ERd         | W   |                     | 2  |      |           |            |     |          |      | ERd32/2→ERd32, Rs16→@ERd  | - | - | ↑ | 0     | - | - | 6    |

|      | MOV. W Rs, @aa:16        | W   |                     | 4  |      |           |            |     |          |      | Rs16→@aa:16               | - | - | ↑ | 0     | - | - | 6    |

|      | MOV. W Rs, @aa:24        | W   |                     | 6  |      |           |            |     |          |      | Rs16→@aa:24               | - | - | ↑ | 0     | - | - | 8    |

|      | MOV. L #xx:32, Rd        | L   | 6                   |    |      |           |            |     |          |      | #xx:32→Rd32               | - | - | ↑ | 0     | - | - | 6    |

|      | MOV. L ERs, ERd          | L   | 2                   |    |      |           |            |     |          |      | ERS32→ERd32               | - | - | ↑ | 0     | - | - | 2    |

|      | MOV. L @ERs, ERd         | L   | 4                   |    |      |           |            |     |          |      | @ERs→ERd32                | - | - | ↑ | 0     | - | - | 8    |

|      | MOV. L @(d:16, ERs), ERd | L   | 6                   |    |      |           |            |     |          |      | @(d:16, ERs)→ERd32        | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L @(d:24, ERs), ERd | L   | 10                  |    |      |           |            |     |          |      | @(d:24, ERs)→ERd32        | - | - | ↑ | 0     | - | - | 14   |

|      | MOV. L @ERs1, ERd        | L   | 4                   |    |      |           |            |     |          |      | @ERs→ERd32, ERS32/4→ERS32 | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L @aa:16, ERd       | L   | 6                   |    |      |           |            |     |          |      | @aa:16→ERd32              | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L @aa:24, ERd       | L   | 8                   |    |      |           |            |     |          |      | @aa:24→ERd32              | - | - | ↑ | 0     | - | - | 12   |

|      | MOV. L ERs, @ERd         | L   | 4                   |    |      |           |            |     |          |      | ERs32→@ERd                | - | - | ↑ | 0     | - | - | 8    |

|      | MOV. L ERs, @(d:16, ERd) | L   | 6                   |    |      |           |            |     |          |      | ERS32→@(d:16, ERd)        | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L ERs, @(d:24, ERd) | L   | 10                  |    |      |           |            |     |          |      | ERS32→@(d:24, ERd)        | - | - | ↑ | 0     | - | - | 14   |

|      | MOV. L ERs, @-ERd        | L   | 4                   |    |      |           |            |     |          |      | ERd32/4→ERd32, ERS32→@ERd | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L ERs, @aa:16       | L   | 6                   |    |      |           |            |     |          |      | ERS32→@aa:16              | - | - | ↑ | 0     | - | - | 10   |

|      | MOV. L ERs, @aa:24       | L   | 8                   |    |      |           |            |     |          |      | ERS32→@aa:24              | - | - | ↑ | 0     | - | - | 12   |

| POP  | POP. W Rn                | W   |                     |    |      |           |            | 6   |          |      | 2 @SP→Rn16, SP+2→SP       | - | - | ↑ | 0     | - | - | 6    |

|      | POP. L ERn               | L   |                     |    |      |           |            | 8   |          |      | 4 @SP→ERn32, SP+4→SP      | - | - | ↑ | 0     | - | - | 10   |

| PUSH | PUSH. W Rn               | W   |                     |    |      |           |            |     |          |      | 2 SP-2→SP, Rn16→@SP       | - | - | ↑ | 0     | - | - | 6    |

|      | PUSH. L ERn              | L   |                     |    |      |           |            |     |          |      | 4 SP-4→SP, ERn32→@SP      | - | - | ↑ | 0     | - | - | 10   |

| MVPP | MVPP. @aa:16, Rd         | B   |                     |    |      |           |            | 4   |          |      | 本L.S Iでは使用できません           |   |   |   |       |   |   |      |

| MVTP | MVTP. Rs, @aa:16         | B   |                     |    |      |           |            | 4   |          |      | 本L.S Iでは使用できません           |   |   |   |       |   |   |      |

(2) 算術演算命令

表 A. 1 命令セット一覧(3)

| 二-モニック<br>サイズ                                                                                                                                                                                                                                                                                                                                                                                          | アドレッシングモード/命令長(バイト) |    |      |          |             |     | オペレーション |      |   |                    |   |   | コンディションコード |   |   |   |     |    | 実行ガート数 |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----|------|----------|-------------|-----|---------|------|---|--------------------|---|---|------------|---|---|---|-----|----|--------|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                        | #xx                 | Rn | @ERn | @(d,ERn) | @-ERn/@ERn+ | @aa | @(d,PC) | @@aa | - | Rd8+#xx:8→Rd8      | - | H | N          | Z | V | C | J-N | DN | J-N    |  |  |  |

| ADD ADD. B #xx:8, Rd ADD. B Rs, Rd ADD. W #xx:16, Rd ADD. W Rs, Rd ADD. L #xx:32, Erd ADD. L ERs, Erd ADDX ADDX. B #xx:8, Rd ADDX. B Rs, Rd ADDS ADDS. L #1, Erd ADDS. L #2, Erd ADDS. L #4, Erd INC INC. B Rd INC. W #1, Rd INC. W #2, Rd INC. L #1, Erd INC. L #2, Erd DMA SUB SUB. B Rs, Rd SUB. W #xx:16, Rd SUB. W Rs, Rd SUB. L #xx:32, Erd SUB. L ERs, Rd SUBX SUBX. B #xx:8, Rd SUBX. B Rs, Rd | B                   | 2  |      |          |             |     |         |      |   | Rd8+Rs8→Rd8        | - | ↑ | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd16+#xx:16→Rd16   | - | ① | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 4      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 4  |      |          |             |     |         |      |   | Rd16+Rs16→Rd16     | - | ① | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | ERd32:#xx:32→ERd32 | - | ② | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 6      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 6  |      |          |             |     |         |      |   | ERd32:ERs32→ERd32  | - | ② | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 2  |      |          |             |     |         |      |   | Rd8+#xx:8+C→Rd8    | - | ↑ | ↑          | ③ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8+Rs8+C→Rd8      | - | ↑ | ↑          | ③ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | ERd32+1→ERd32      | - | - | -          | - | - | - | -   | -  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 2  |      |          |             |     |         |      |   | ERd32+2→ERd32      | - | - | -          | - | - | - | -   | -  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 2  |      |          |             |     |         |      |   | ERd32+4→ERd32      | - | - | -          | - | - | - | -   | -  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8+1→Rd8          | - | - | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | Rd16+1→Rd16        | - | - | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | Rd16+2→Rd16        | - | - | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 2  |      |          |             |     |         |      |   | ERd32+1→ERd32      | - | - | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | Rd16+1→Rd16        | - | - | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | ERd32+2→ERd32      | - | * | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8 10進補正→Rd8      | - | ① | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8-Rs8→Rd8        | - | ↑ | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 4  |      |          |             |     |         |      |   | Rd16+#xx:16→Rd16   | - | ① | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 4      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | W                   | 2  |      |          |             |     |         |      |   | Rd16-Rs16→Rd16     | - | ① | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 6  |      |          |             |     |         |      |   | ERd32:#xx:32→ERd32 | - | ② | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 6      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | L                   | 2  |      |          |             |     |         |      |   | ERd32:ERs32→ERd32  | - | ② | ↑          | ↑ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8-#xx:8-C→Rd8    | - | ↑ | ↑          | ③ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                        | B                   | 2  |      |          |             |     |         |      |   | Rd8-Rs8-C→Rd8      | - | ↑ | ↑          | ③ | ↑ | ↑ | ↑   | ↑  | 2      |  |  |  |

表 A. 1 命令セット一覧(4)

| 一一モニック |                  | サイズ |    | アドレスシングモード/命令長(ハイイト) |           |             |     | オペレーション  |      |   |                                        | コンディションコード |   |   |   | 実行時間(ナミ) |   |     |       |

|--------|------------------|-----|----|----------------------|-----------|-------------|-----|----------|------|---|----------------------------------------|------------|---|---|---|----------|---|-----|-------|

| SUBS   | SUBS.L #1, Erd   | #xx | Rn | @ERn                 | @(d, ERn) | @-ERn/@BRn+ | @aa | @(d, PC) | @@aa | - | ERd32-1→ERd32                          | -          | H | N | Z | V        | C | /A# | TKV/T |

| SUBS   | SUBS.L #2, Erd   | L   | 2  |                      |           |             |     |          |      |   | ERd32-2→ERd32                          | -          | - | - | - | -        | - | -   | 2     |

| SUBS   | SUBS.L #3, Erd   | L   | 2  |                      |           |             |     |          |      |   | ERd32-4→ERd32                          | -          | - | - | - | -        | - | -   | 2     |

| DEC    | DEC.B Rd         | B   | 2  |                      |           |             |     |          |      |   | Rd8-1→Rd8                              | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| DEC    | DEC.W #1, Rd     | W   | 2  |                      |           |             |     |          |      |   | Rd16-1→Rd16                            | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| DEC    | DEC.W #2, Rd     | W   | 2  |                      |           |             |     |          |      |   | Rd16-2→Rd16                            | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| DEC    | DEC.L #1, Erd    | L   | 2  |                      |           |             |     |          |      |   | ERd32-1→ERd32                          | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| DEC    | DEC.L #2, Erd    | L   | 2  |                      |           |             |     |          |      |   | ERd32-2→ERd32                          | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| DAS    | DAS.Rd           | B   | 2  |                      |           |             |     |          |      |   | Rd8 10進補正→Rd8                          | -          | * | ↑ | ↑ | ↑        | * | -   | 2     |

| MULXU  | MULXU.B Rs, Rd   | B   | 2  |                      |           |             |     |          |      |   | Rd8×Rs3→Rd16 (符号なし乗算)                  | -          | - | - | - | -        | - | -   | 14    |

| MULXU  | MULXU.W Rs, Erd  | W   | 2  |                      |           |             |     |          |      |   | Rd16×Rs16→ERd32 (符号なし乗算)               | -          | - | - | - | -        | - | -   | 22    |

| MULXS  | MULXS.B Rs, Rd   | B   | 4  |                      |           |             |     |          |      |   | Rd8×Rs8→Rd16 (符号付乗算)                   | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 16    |

| MULXS  | MULXS.W Rs, Erd  | W   | 4  |                      |           |             |     |          |      |   | Rd16×Rs16→ERd32 (符号付乗算)                | -          | - | ↑ | ↑ | ↑        | ↑ | -   | 24    |

| DIVXU  | DIVXU.B Rs, Rd   | B   | 2  |                      |           |             |     |          |      |   | Rd16÷Rs8→Rd16(RdH:余り, RdL:商) (符号なし除算)  | -          | - | ⑥ | ⑦ | -        | - | 14  |       |

| DIVXU  | DIVXU.W Rs, Erd  | W   | 2  |                      |           |             |     |          |      |   | ERd32÷Rs16→ERd32(Ed:余り, Rd:商) (符号なし除算) | -          | - | ⑥ | ⑦ | -        | - | 22  |       |

| DIVXS  | DIVXS.B Rs, Rd   | B   | 4  |                      |           |             |     |          |      |   | Rd16÷Rs8→Rd16(RdH:余り, RdL:商) (符号付除算)   | -          | - | ⑧ | ⑨ | -        | - | 16  |       |

| DIVXS  | DIVXS.W Rs, Erd  | W   | 4  |                      |           |             |     |          |      |   | ERd32÷Rs16→ERd32(Ed:余り, Rd:商) (符号付除算)  | -          | - | ⑧ | ⑨ | -        | - | 24  |       |

| CMP    | CMP.B #xx:8, Rd  | B   | 2  |                      |           |             |     |          |      |   | Rd8 #xx:8                              | -          | ↑ | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| CMP    | CMP.B Rs, Rd     | B   | 2  |                      |           |             |     |          |      |   | Rd8-Rs8                                | -          | ↑ | ↑ | ↑ | ↑        | ↑ | -   | 2     |

| CMP    | CMP.W #xx:16, Rd | W   | 4  |                      |           |             |     |          |      |   | Rd16-#xx:16                            | -          | ① | ↑ | ↑ | ↑        | ↑ | 4   |       |

| CMP    | CMP.W Rs, Rd     | W   | 2  |                      |           |             |     |          |      |   | Rd16-Rs16                              | -          | ① | ↑ | ↑ | ↑        | ↑ | 2   |       |

表 A. 1 命令セット一覧(5)

| 二-モニック |                   | アドレッシングモード/命令長(ハイト) |      |          |            |      |         | オペレーションコード |   |                                 |   |   |   |   |   |   |      |       |

|--------|-------------------|---------------------|------|----------|------------|------|---------|------------|---|---------------------------------|---|---|---|---|---|---|------|-------|

| サイズ    | #xx               | Rn                  | @ERn | @(d,ERn) | @-Rn/@ERn+ | @aa, | @(d,PC) | @@aa       | - | コンディションコード                      | I | H | N | Z | V | C | J-ZW | JNW&Z |

| CMP    | CMP.L #xx:32, ERd | L                   | 6    |          |            |      |         |            |   | ERd32:#xx:32                    | - | ② | ↑ | ↑ | ↑ | ↑ | ↑    | 4     |

|        | CMP.L ERs, ERd    | L                   | 2    |          |            |      |         |            |   | ERd32-ERs32                     | - | ② | ↑ | ↑ | ↑ | ↑ | ↑    | 2     |

| NEG    | NEG.B Rd          | B                   | 2    |          |            |      |         |            |   | 0-Rd8→Rd8                       | - | ↑ | ↑ | ↑ | ↑ | ↑ | ↑    | 2     |

|        | NEG.W Rd          | W                   | 2    |          |            |      |         |            |   | 0-Rd16→Rd16                     | - | ↑ | ↑ | ↑ | ↑ | ↑ | ↑    | 2     |

| NEGL   | NEGL ERd          | L                   | 2    |          |            |      |         |            |   | 0-ER32→ER32                     | - | ↑ | ↑ | ↑ | ↑ | ↑ | ↑    | 2     |

|        | EXTU.W Rd         | W                   | 2    |          |            |      |         |            |   | 0→(<#t15~8>of Rd16)             | - | 0 | ↑ | 0 | 0 | 0 | -    | 2     |

| EXTL   | EXTL ERd          | L                   | 2    |          |            |      |         |            |   | 0→(<#t131~16>of ER32)           | - | 0 | ↑ | 0 | 0 | 0 | -    | 2     |

|        | EXTS.W Rd         | W                   | 2    |          |            |      |         |            |   | (<t17>of Rd16)→(<t15~8>of Rd16) | - | 0 | ↑ | 0 | 0 | 0 | -    | 2     |

| EXTS   | EXTS.L Rd         | L                   | 2    |          |            |      |         |            |   | (<t11>of ER32)→                 | - | 0 | ↑ | 0 | 0 | 0 | -    | 2     |

|        | EXTS.L ERd        | W                   | 2    |          |            |      |         |            |   | (<t131~16>of ER32)              | - | 0 | ↑ | 0 | 0 | 0 | -    | 2     |

### (3) 論理演算命令

| 二-モニック |                   | アドレッシングモード/命令長(ハイト) |      |          |            |      |         | オペレーションコード |   |                         |   |   |   |   |   |   |      |       |

|--------|-------------------|---------------------|------|----------|------------|------|---------|------------|---|-------------------------|---|---|---|---|---|---|------|-------|

| サイズ    | #xx               | Rn                  | @ERn | @(d,ERn) | @-Rn/@ERn+ | @aa, | @(d,PC) | @@aa       | - | コンディションコード              | I | H | N | Z | V | C | J-ZW | JNW&Z |

| AND    | AND.B #xx:8, Rd   | B                   | 2    |          |            |      |         |            |   | Rd8 ∧ #xx: 8 → Rd8      | - | ↑ | 0 | 0 | - | - | 2    |       |

|        | AND.B Rs, Rd      | B                   | 2    |          |            |      |         |            |   | Rd8 ∧ Rs8 → Rd8         | - | ↑ | 0 | 0 | - | - | 2    |       |

| AND.W  | AND.W #xx:16, Rd  | W                   | 4    |          |            |      |         |            |   | Rd16 ∧ #xx: 16 → Rd16   | - | ↑ | 0 | 0 | - | - | 4    |       |

|        | AND.W Rs, Rd      | W                   | 2    |          |            |      |         |            |   | Rd16 ∧ Rs16 → Rd16      | - | ↑ | 0 | 0 | - | - | 2    |       |

| AND.L  | AND.L #xx:32, ERd | L                   | 6    |          |            |      |         |            |   | ERd32 ∧ #xx: 32 → ERd32 | - | ↑ | 0 | 0 | - | - | 6    |       |

|        | AND.L ERs, ERd    | L                   | 4    |          |            |      |         |            |   | ERd32 ∧ ERs32 → ERd32   | - | ↑ | 0 | 0 | - | - | 4    |       |

| OR     | OR.B #xx:8, Rd    | B                   | 2    |          |            |      |         |            |   | Rd8 ∨ #xx: 8 → Rd8      | - | ↑ | 0 | 0 | - | - | 2    |       |

|        | OR.B Rs, Rd       | B                   | 2    |          |            |      |         |            |   | Rd8 ∨ Rs8 → Rd8         | - | ↑ | 0 | 0 | - | - | 2    |       |

| OR.W   | OR.W #xx:16, Rd   | W                   | 4    |          |            |      |         |            |   | Rd16 ∨ #xx: 16 → Rd16   | - | ↑ | 0 | 0 | - | - | 4    |       |

|        | OR.W Rs, Rd       | W                   | 2    |          |            |      |         |            |   | Rd16 ∨ Rs16 → Rd16      | - | ↑ | 0 | 0 | - | - | 2    |       |

表 A. 1 命令セット一覧(6)

|        |                   | アドレッシングモード/命令長(バイト) |     |    |      |           |             | オペレーション |          |      |   | コンディションコード             |   |   |   | 実行bit-数* |   |      |       |

|--------|-------------------|---------------------|-----|----|------|-----------|-------------|---------|----------|------|---|------------------------|---|---|---|----------|---|------|-------|

| 二-モニック |                   | サイズ                 | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa     | @(d, PC) | @@aa | - | I                      | H | N | Z | V        | C | J-ZH | J-NZP |

| OR     | OR.L #xx:32, ERd  | L                   | 6   |    |      |           |             |         |          |      |   | ERd32 ∨ #xx:32 → ERd32 | - | - | ↑ | 0        | - | 6    |       |

|        | OR.L ERs, ERd     | L                   | 4   |    |      |           |             |         |          |      |   | ERd32 ∨ ERs32 → ERd32  | - | - | ↑ | 0        | - | 4    |       |

| XOR    | XOR.B #xx:8, Rd   | B                   | 2   |    |      |           |             |         |          |      |   | Rd8⊕#xx:8 → Rd8        | - | - | ↑ | 0        | - | 2    |       |

|        | XOR.B Rs, Rd      | B                   | 2   |    |      |           |             |         |          |      |   | Rd8⊕Rs8 → Rd8          | - | - | ↑ | 0        | - | 2    |       |

|        | XOR.W #xx:16, Rd  | W                   | 4   |    |      |           |             |         |          |      |   | Rd16⊕#xx:16 → Rd16     | - | - | ↑ | 0        | - | 4    |       |

|        | XOR.W Rs, Rd      | W                   | 2   |    |      |           |             |         |          |      |   | Rd16⊕Rs16 → Rd16       | - | - | ↑ | 0        | - | 2    |       |

|        | XOR.L #xx:32, ERd | L                   | 6   |    |      |           |             |         |          |      |   | ERd32⊕#xx:32 → ERd32   | - | - | ↑ | 0        | - | 6    |       |

|        | XOR.L ERs, ERd    | L                   | 4   |    |      |           |             |         |          |      |   | ERd32⊕ERs32 → ERd32    | - | - | ↑ | 0        | - | 4    |       |

| NOT    | NOT.B Rd          | B                   | 2   |    |      |           |             |         |          |      |   | ~Rd8 → Rd8             | - | - | ↑ | 0        | - | 2    |       |

|        | NOT.W Rd          | W                   | 2   |    |      |           |             |         |          |      |   | ~Rd16 → Rd16           | - | - | ↑ | 0        | - | 2    |       |

|        | NOT.L ERd         | L                   | -   | 2  |      |           |             |         |          |      |   | ~Rd32 → Rd32           | - | - | ↑ | 0        | - | 2    |       |

## (4) シフト命令

|        |            | アドレッシングモード/命令長(バイト) |     |    |      |           |             | オペレーション |          |      |   | コンディションコード |   |   |   | 実行bit-数* |   |      |       |

|--------|------------|---------------------|-----|----|------|-----------|-------------|---------|----------|------|---|------------|---|---|---|----------|---|------|-------|

| 二-モニック |            | サイズ                 | #xx | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa     | @(d, PC) | @@aa | - | I          | H | N | Z | V        | C | J-ZH | J-NZP |

| SHAL   | SHAL.B Rd  | B                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | ↑        | ↑ | 2    |       |

|        | SHAL.W Rd  | W                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | ↑        | ↑ | 2    |       |

|        | SHAL.L ERd | L                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | ↑        | ↑ | 2    |       |

| SHAR   | SHAR.B Rd  | B                   | 2   |    |      |           |             |         |          |      |   | [ ] → [ ]  | - | - | ↑ | 0        | ↑ | 2    |       |

|        | SHAR.W Rd  | W                   | 2   |    |      |           |             |         |          |      |   | [ ] → [ ]  | - | - | ↑ | 0        | ↑ | 2    |       |

|        | SHAR.L ERd | L                   | 2   |    |      |           |             |         |          |      |   | [ ] → [ ]  | - | - | ↑ | 0        | ↑ | 2    |       |

| SLLL   | SLLL.B Rd  | B                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | 0        | ↑ | 2    |       |

|        | SLLL.W Rd  | W                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | 0        | ↑ | 2    |       |

|        | SLLL.L ERd | L                   | 2   |    |      |           |             |         |          |      |   | ↑ ← [ ]    | - | - | ↑ | 0        | ↑ | 2    |       |

表 A. 1 命令セット一覧(7)

| 二モニック | サイズ         | アドレッシングモード／命令長(バイト) |    |      |          | オペレーション     |     |         |      | コンディションコード |     |     |     | 実行ガート数 <sup>11</sup> |   |      |        |

|-------|-------------|---------------------|----|------|----------|-------------|-----|---------|------|------------|-----|-----|-----|----------------------|---|------|--------|

|       |             | #xx                 | Rn | @ERn | @(d,ERn) | @-ERn/@ERn+ | @aa | @(d,PC) | @@aa | I          | H   | N   | Z   | V <sub>f</sub>       | C | J-ZW | TFN/AT |

| SHLR  | SHLR.B Rd   | B                   | 2  |      |          |             |     |         |      | -          | -   | -   | -   | -                    | - | -    | 2      |

|       | SHLR.W Rd   | W                   | 2  |      |          |             |     |         |      | -          | -   | -   | -   | -                    | - | -    | 2      |

|       | SHLR.L Erd  | L                   | 2  |      |          |             |     |         |      | -          | -   | -   | -   | -                    | - | -    | 2      |

| ROTXL | ROTXL.B Rd  | B                   | 2  |      |          |             |     |         |      | 0→         | →   |     |     |                      |   |      |        |

|       | ROTXL.W Rd  | W                   | 2  |      |          |             |     |         |      | MSB        | →   | LSB | C   | -                    | - | -    | 2      |

|       | ROTXL.L Erd | L                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

| ROTR  | ROTR.B Rd   | B                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTR.W Rd   | W                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTR.L Erd  | L                   | 2  |      |          |             |     |         |      | C          | MSB | ←   | LSB | -                    | - | ↓    | 2      |

| ROTL  | ROTL.B Rd   | B                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTL.W Rd   | W                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTL.L Erd  | L                   | 2  |      |          |             |     |         |      | MSB        | →   | LSB | C   | -                    | - | ↓    | 2      |

| ROTR  | ROTR.B Rd   | B                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTR.W Rd   | W                   | 2  |      |          |             |     |         |      | ↓          | ↓   | ↓   | ↓   | ↓                    | ↓ | ↓    | 2      |

|       | ROTR.L Erd  | L                   | 2  |      |          |             |     |         |      | C          | MSB | ←   | LSB | -                    | - | ↓    | 2      |

## (5) ビット操作命令

| 二モニック | サイズ                | アドレッシングモード／命令長(バイト) |    |      |          | オペレーション     |     |         |      | コンディションコード         |   |   |   | 実行ガート数 <sup>11</sup> |   |      |        |

|-------|--------------------|---------------------|----|------|----------|-------------|-----|---------|------|--------------------|---|---|---|----------------------|---|------|--------|

|       |                    | #xx                 | Rn | @ERn | @(d,ERn) | @-ERn/@ERn+ | @aa | @(d,PC) | @@aa | I                  | H | N | Z | V                    | C | J-ZW | TFN/AT |

| BSET  | BSET #xx:3, Rd     | B                   | 2  |      |          |             |     |         |      | (#xx:3 of Rd8)←1   | - | - | - | -                    | - | -    | 2      |

|       | BSET #xx:3, @(ERd) | B                   |    | 4    |          |             |     |         |      | (#xx:3 of @ERd)←1  | - | - | - | -                    | - | -    | 8      |

|       | BSET #xx:3, @aa:8  | B                   |    |      | 4        |             |     |         |      | (#xx:3 of @aa:8)←1 | - | - | - | -                    | - | -    | 8      |

|       | BSET Rn, Rd        | B                   | 2  |      |          |             |     |         |      | (Rn8 of Rd8)←1     | - | - | - | -                    | - | -    | 2      |

|       | BSET Rn, @(ERd)    | B                   |    | 4    |          |             |     |         |      | (Rn8 of @ERd)←1    | - | - | - | -                    | - | -    | 8      |

|       | BSET Rn, @aa:8     | B                   |    |      | 4        |             |     |         |      | (Rn8 of @aa:8)←1   | - | - | - | -                    | - | -    | 8      |

表 A. 1 命令セット一覧(8)

| 二一モニック |                   | アドレッシングモード/命令長(バイト) |    |      |           |              |     | オペレーションコード |      |                                    |   |   |   | コンディションコード |   | 実行行数 <sup>*1</sup> |     |       |

|--------|-------------------|---------------------|----|------|-----------|--------------|-----|------------|------|------------------------------------|---|---|---|------------|---|--------------------|-----|-------|

|        | サイン               | #xx                 | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+t | @aa | @(d, PC)   | @@aa | -                                  | I | H | N | Z          | V | C                  | J-N | TKYJ# |

| BCLR   | BCLR #xx:3, Rd    | B                   | 2  |      |           |              |     |            |      | (#xx:3 of Rd8)→0                   | - | - | - | -          | - | -                  | 2   |       |

|        | BCLR #xx:3, @ERd  | B                   | 4  |      |           |              |     |            |      | (#xx:3 of @ERd)→0                  | - | - | - | -          | - | -                  | 8   |       |

|        | BCLR #xx:3, @aa:8 | B                   |    |      |           |              | 4   |            |      | (#xx:3 of @aa:8)→0                 | - | - | - | -          | - | -                  | 8   |       |

|        | BCLR Rn, Rd       | B                   | 2  |      |           |              |     |            |      | (Rn8 of Rd8)→0                     | - | - | - | -          | - | -                  | 2   |       |

|        | BCLR Rn, @ERd     | B                   | 4  |      |           |              |     |            |      | (Rn8 of @ERd)→0                    | - | - | - | -          | - | -                  | 8   |       |

|        | BCLR Rn, @aa:8    | B                   |    |      |           |              | 4   |            |      | (Rn8 of @aa:8)→0                   | - | - | - | -          | - | -                  | 8   |       |

| BNOT   | BNOT #xx:3, Rd    | B                   | 2  |      |           |              |     |            |      | (#xx:3 of Rd8)↔~(#xx:3 of Rd8)     | - | - | - | -          | - | -                  | 2   |       |

|        | BNOT #xx:3, @ERd  | B                   | 4  |      |           |              |     |            |      | (#xx:3 of @ERd)↔~(#xx:3 of @ERd)   | - | - | - | -          | - | -                  | 8   |       |

|        | BNOT #xx:3, @aa:8 | B                   |    |      |           |              | 4   |            |      | (#xx:3 of @aa:8)↔~(#xx:3 of @aa:8) | - | - | - | -          | - | -                  | 8   |       |

|        | BNOT Rn, Rd       | B                   | 2  |      |           |              |     |            |      | (Rn8 of Rd8)↔~(Rn8 of Rd8)         | - | - | - | -          | - | -                  | 2   |       |

|        | BNOT Rn, @ERd     | B                   | 4  |      |           |              |     |            |      | (Rn8 of @ERd)↔~(Rn8 of @ERd)       | - | - | - | -          | - | -                  | 8   |       |

|        | BNOT Rn, @aa:8    | B                   |    |      |           |              | 4   |            |      | (Rn8 of @aa:8)↔~(Rn8 of @aa:8)     | - | - | - | -          | - | -                  | 8   |       |

| BTST   | BTST #xx:3, Rd    | B                   | 2  |      |           |              |     |            |      | ~(#xx:3 of Rd8)→Z                  | - | - | ↑ | -          | - | -                  | 2   |       |

|        | BTST #xx:3, @ERd  | B                   | 4  |      |           |              |     |            |      | ~(#xx:3 of @ERd)→Z                 | - | - | ↑ | -          | - | -                  | 6   |       |

|        | BTST #xx:3, @aa:8 | B                   |    |      |           |              | 4   |            |      | ~(#xx:3 of @aa:8)→Z                | - | - | ↑ | -          | - | -                  | 6   |       |

|        | BTST Rn, Rd       | B                   | 2  |      |           |              |     |            |      | ~(Rn8 of @Rd8)→Z                   | - | - | ↑ | -          | - | -                  | 2   |       |

|        | BTST Rn, @ERd     | B                   | 4  |      |           |              |     |            |      | ~(Rn8 of @ERd)→Z                   | - | - | ↑ | -          | - | -                  | 6   |       |

|        | BTST Rn, @aa:8    | B                   |    |      |           |              | 4   |            |      | ~(Rn8 of @aa:8)→Z                  | - | - | ↑ | -          | - | -                  | 6   |       |

| BLD    | BLD #xx:3, Rd     | B                   | 2  |      |           |              |     |            |      | (#xx:3 of Rd8)→C                   | - | - | - | ↑          | 2 | 2                  |     |       |

|        | BLD #xx:3, @ERd   | B                   | 4  |      |           |              |     |            |      | (#xx:3 of @ERd)→C                  | - | - | - | ↑          | 6 | 6                  |     |       |

|        | BLD #xx:3, @aa:8  | B                   |    |      |           |              | 4   |            |      | (#xx:3 of @aa:8)→C                 | - | - | - | ↑          | 6 | 6                  |     |       |

|        | BLD #xx:3, Rd     | B                   | 2  |      |           |              |     |            |      | ~(#xx:3 of Rd8)→C                  | - | - | - | ↑          | 2 | 2                  |     |       |

|        | BLD #xx:3, @ERd   | B                   | 4  |      |           |              |     |            |      | ~(#xx:3 of @ERd)→C                 | - | - | - | ↑          | 6 | 6                  |     |       |

|        | BLD #xx:3, @aa:8  | B                   |    |      |           |              | 4   |            |      | ~(#xx:3 of @aa:8)→C                | - | - | - | ↑          | 6 | 6                  |     |       |

表A. 1 命令セット一覧(9)

| 一一モニック |                    | アドレッシングモード/命令長(バイト) |      |           |             |     |          | オペレーション |                              |   |   |   |   | コンディションコード |   |      |       | 実行行数 |

|--------|--------------------|---------------------|------|-----------|-------------|-----|----------|---------|------------------------------|---|---|---|---|------------|---|------|-------|------|

| サイズ    | #xx                | Rn                  | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @@aa    | -                            | I | H | N | Z | V          | C | J-N# | JN#J! |      |

| BST    | BST #xx:3, Rd      | B                   | 2    |           |             |     |          |         | C->(#xx:3 of Rd8)            | - | - | - | - | -          | - | -    | 2     |      |

|        | BST #xx:3, @ERd    | B                   | 4    |           |             |     |          |         | C->(#xx:3 of @ERd24)         | - | - | - | - | -          | - | -    | 8     |      |

| BIST   | BIST #xx:3, @aa:8  | B                   |      |           |             | 4   |          |         | C->(#xx:3 of @aa:8)          | - | - | - | - | -          | - | -    | 8     |      |

|        | BIST #xx:3, Rd     | B                   | 2    |           |             |     |          |         | ~C->(#xx:3 of Rd8)           | - | - | - | - | -          | - | -    | 2     |      |

| BIST   | BIST #xx:3, @ERd   | B                   | 4    |           |             |     |          |         | ~C->(#xx:3 of @ERd24)        | - | - | - | - | -          | - | -    | 8     |      |

|        | BIST #xx:3, @aa:8  | B                   |      |           |             | 4   |          |         | ~C->(#xx:3 of @aa:8)         | - | - | - | - | -          | - | -    | 8     |      |

| BAND   | BAND #xx:3, Rd     | B                   | 2    |           |             |     |          |         | C\wedge(#xx:3 of Rd8)->C     | - | - | - | - | -          | - | -    | 2     |      |

|        | BAND #xx:3, @ERd   | B                   | 4    |           |             |     |          |         | C\wedge(#xx:3 of @ERd24)->C  | - | - | - | - | -          | - | -    | 6     |      |

| BAND   | BAND #xx:3, @aa:8  | B                   |      |           |             | 4   |          |         | C\wedge(#xx:3 of @aa:8)->C   | - | - | - | - | -          | - | -    | 6     |      |

|        | BAND #xx:3, Rd     | B                   | 2    |           |             |     |          |         | C\wedge~(#xx:3 of Rd8)->C    | - | - | - | - | -          | - | -    | 2     |      |

| BIAND  | BIAND #xx:3, @ERd  | B                   | 4    |           |             |     |          |         | C\wedge~(#xx:3 of @ERd24)->C | - | - | - | - | -          | - | -    | 6     |      |

|        | BIAND #xx:3, @aa:8 | B                   |      |           |             | 4   |          |         | C\wedge~(#xx:3 of @aa:8)->C  | - | - | - | - | -          | - | -    | 6     |      |

| BOR    | BOR #xx:3, Rd      | B                   | 2    |           |             |     |          |         | C\vee(#xx:3 of Rd8)->C       | - | - | - | - | -          | - | -    | 2     |      |

|        | BOR #xx:3, @ERd    | B                   | 4    |           |             |     |          |         | C\vee(#xx:3 of @ERd24)->C    | - | - | - | - | -          | - | -    | 6     |      |

| BOR    | BOR #xx:3, @aa:8   | B                   |      |           |             | 4   |          |         | C\vee~(#xx:3 of @aa:8)->C    | - | - | - | - | -          | - | -    | 6     |      |

|        | BOR #xx:3, Rd      | B                   | 2    |           |             |     |          |         | C\vee~(#xx:3 of Rd8)->C      | - | - | - | - | -          | - | -    | 2     |      |

| BIXOR  | BIXOR #xx:3, @aa:8 | B                   |      |           |             | 4   |          |         | C\oplus~(#xx:3 of @aa:8)->C  | - | - | - | - | -          | - | -    | 6     |      |

|        | BIXOR #xx:3, Rd    | B                   | 2    |           |             |     |          |         | C\oplus~(#xx:3 of Rd8)->C    | - | - | - | - | -          | - | -    | 2     |      |

| BIXOR  | BIXOR #xx:3, @ERd  | B                   | 4    |           |             |     |          |         | C\oplus~(#xx:3 of @ERd24)->C | - | - | - | - | -          | - | -    | 6     |      |

|        | BIXOR #xx:3, @aa:8 | B                   |      |           |             | 4   |          |         | C\oplus~(#xx:3 of @aa:8)->C  | - | - | - | - | -          | - | -    | 6     |      |

| BIXOR  | BIXOR #xx:3, Rd    | B                   | 2    |           |             |     |          |         | C\oplus~(#xx:3 of Rd8)->C    | - | - | - | - | -          | - | -    | 2     |      |

|        | BIXOR #xx:3, @aa:8 | B                   | 4    |           |             |     |          |         | C\oplus~(#xx:3 of @aa:8)->C  | - | - | - | - | -          | - | -    | 6     |      |

| BIXOR  | BIXOR #xx:3, @ERd  | B                   | 4    |           |             |     |          |         | C\oplus~(#xx:3 of @ERd24)->C | - | - | - | - | -          | - | -    | 2     |      |

|        | BIXOR #xx:3, @aa:8 | B                   |      |           |             | 4   |          |         | C\oplus~(#xx:3 of @aa:8)->C  | - | - | - | - | -          | - | -    | 6     |      |

| BIXOR  | BIXOR #xx:3, Rd    | B                   | 2    |           |             |     |          |         | C\oplus~(#xx:3 of Rd8)->C    | - | - | - | - | -          | - | -    | 2     |      |

表A. 1 命令セット一覧(II)

## (6) 分岐命令

| 二モニック |                   | アドレスングモード/命令長(バイト) |    |      |           |             |     |          |      |   |                      | オペレーション |   |   |   |   |   | コンディションコード |      |       |  |  |  | 実行行数 |  |

|-------|-------------------|--------------------|----|------|-----------|-------------|-----|----------|------|---|----------------------|---------|---|---|---|---|---|------------|------|-------|--|--|--|------|--|

|       | サイズ               | #xx                | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @@ea | - | if condition is true | 分岐条件    | I | H | N | Z | V | C          | J-ZW | TRW#t |  |  |  |      |  |

| Bcc   | BRA d:8(BT d:8)   | -                  |    |      |           |             | 2   |          |      | - | Always               | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

|       | BRA d:16(BT d:16) | -                  |    |      |           |             | 4   |          |      | - | then PC->PC+d        | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

|       | BRN d:8(BR d:8)   | -                  |    |      |           |             | 2   |          |      | - | else next;           | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

|       | BRN d:16(BR d:16) | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BHI   | d:8               | -                  |    |      |           |             | 2   |          |      | - | CVZ=0                | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BHI   | d:16              | -                  |    |      |           |             | 4   |          |      | - | CVZ=1                | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BLS   | d:8               | -                  |    |      |           |             | 2   |          |      | - | C=0                  | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BLS   | d:16              | -                  |    |      |           |             | 4   |          |      | - | C=1                  | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BCC   | d:8(BHS d:8)      | -                  |    |      |           |             | 2   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BCC   | d:16(BHS d:16)    | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BCS   | d:8(BLO d:8)      | -                  |    |      |           |             | 2   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BCS   | d:16(BLO d:16)    | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BNE   | d:8               | -                  |    |      |           |             | 2   |          |      | - | Z=0                  | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BNE   | d:16              | -                  |    |      |           |             | 4   |          |      | - | Z=1                  | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BBQ   | d:8               | -                  |    |      |           |             | 2   |          |      | - | V=0                  | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BBQ   | d:16              | -                  |    |      |           |             | 4   |          |      | - | V=1                  | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BVC   | d:8               | -                  |    |      |           |             | 2   |          |      | - | N=0                  | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BVC   | d:16              | -                  |    |      |           |             | 4   |          |      | - | N=1                  | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BVS   | d:8               | -                  |    |      |           |             | 2   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BVS   | d:16              | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BPL   | d:8               | -                  |    |      |           |             | 2   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BPL   | d:16              | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

| BMI   | d:8               | -                  |    |      |           |             | 2   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 4     |  |  |  |      |  |

| BMI   | d:16              | -                  |    |      |           |             | 4   |          |      | - |                      | -       | - | - | - | - | - | -          | -    | 6     |  |  |  |      |  |

表 A. 1 命令セット一覧(II)

| モード | サイン        | アドレッシングモード/命令長(バイト) |    |      |           | オペレーション     |     |          |      | コンディションコード           |           |   |   | 実行時間 |   |   |     |        |

|-----|------------|---------------------|----|------|-----------|-------------|-----|----------|------|----------------------|-----------|---|---|------|---|---|-----|--------|

|     |            | #xx                 | Rn | @ERn | @(d, ERn) | @-ERn/@ERn+ | @aa | @(d, PC) | @@aa | -                    | I         | H | N | Z    | V | C | J-W | TF/SAT |

| Bcc | BGE d:8    | -                   |    |      |           |             |     | 2        |      | if condition is true | N⊕W=0     | - | - | -    | - | - | -   | 4      |

|     | BGE d:16   | -                   |    |      |           |             |     | 4        |      | then PC←PCd          | -         | - | - | -    | - | - | -   | 6      |

|     | BLT d:8    | -                   |    |      |           |             |     | 2        |      | else next;           | N⊕W=1     | - | - | -    | - | - | -   | 4      |

|     | BLT d:16   | -                   |    |      |           |             |     | 4        |      |                      | -         | - | - | -    | - | - | -   | 6      |

|     | BGT d:8    | -                   |    |      |           |             |     | 2        |      |                      | Z∨(N⊕V)=0 | - | - | -    | - | - | -   | 4      |

|     | BGT d:16   | -                   |    |      |           |             |     | 4        |      |                      | -         | - | - | -    | - | - | -   | 6      |

|     | BLE d:8    | -                   |    |      |           |             |     | 2        |      |                      | Z∨(N⊕V)=1 | - | - | -    | - | - | -   | 4      |

|     | BLE d:16   | -                   |    |      |           |             |     | 4        |      |                      | -         | - | - | -    | - | - | -   | 6      |

| JMP | JMP @ERn   | -                   |    |      |           |             |     |          |      | PC←ERn               | -         | - | - | -    | - | - | -   | 4      |

|     | JMP @aa:24 | -                   |    |      |           |             |     | 4        |      | PC←aa:24             | -         | - | - | -    | - | - | -   | 6      |

|     | JMP @@aa:8 | -                   |    |      |           |             |     |          | 2    | PC←@aa:8             | -         | - | - | -    | - | - | 8   | 10     |

| BSR | BSR d:8    | -                   |    |      |           |             |     |          | 2    | PC→@-SP, PC←PCd:8    | -         | - | - | -    | - | - | 6   | 8      |

|     | BSR d:16   | -                   |    |      |           |             |     |          | 4    | PC→@-SP, PC←PCd:16   | -         | - | - | -    | - | - | 8   | 10     |

| JSR | JSR @ERn   | -                   |    |      |           |             |     |          | 2    | PC→@-SP, PC←@ERn     | -         | - | - | -    | - | - | 6   | 8      |

|     | JSR @aa:24 | -                   |    |      |           |             |     |          | 4    | PC→@-SP, PC←@aa:24   | -         | - | - | -    | - | - | 8   | 10     |

|     | JSR @@aa:8 | -                   |    |      |           |             |     |          | 2    | PC→@-SP, PC←@aa:8    | -         | - | - | -    | - | - | 8   | 12     |

| KTS | KTS        | -                   |    |      |           |             |     |          |      | 2 PC←@SP+            | -         | - | - | -    | - | - | 8   | 10     |

## (7) システム制御命令

表A. 1 命令セット一覧(7)

| 二モニック      | サイズ               | アドレッシングモード／命令長(バイト) |    |      |           |             |     |          |      |   |                               | オペレーション                  | コンディションコード               | 実行手段 <sup>1)</sup> |

|------------|-------------------|---------------------|----|------|-----------|-------------|-----|----------|------|---|-------------------------------|--------------------------|--------------------------|--------------------|

|            |                   | #xx                 | Mn | @Etn | @(d, Etn) | @-ERn/@ERnt | @aa | @(d, PC) | @@aa | - | PC->@-SP, CCR->@-SP, <(d)>-PC | I - H N Z V C J-Z# A&B&T |                          |                    |

| TRAPA #x:2 | -                 |                     |    |      |           |             |     |          |      |   | 2                             | CCR->@SP+, PC->@SP+      | 1 - H N Z V C J-Z# A&B&T |                    |

| KTE        | KTE               | -                   |    |      |           |             |     |          |      |   |                               | 低消費電力状態に遷移               | - - -                    | - - -              |

| SLEEP      | SLEEP             | -                   |    |      |           |             |     |          |      |   |                               |                          | - - -                    | - - -              |

| LDC        | LDC #xx:8, CCR    | B                   | 2  |      |           |             |     |          |      |   | #xx:8->CCR                    | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| LDC        | RS, CCR           | B                   | 2  |      |           |             |     |          |      |   | RS8->CCR                      | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 10                 |

| LDC        | @ERS, CCR         | W                   | 4  |      |           |             |     |          |      |   | @ERS->CCR                     | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| LDC        | @(d:16, ERS), CCR | W                   | 6  |      |           |             |     |          |      |   | @(d:16, ERS)->CCR             | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| LDC        | @(d:24, ERS), CCR | W                   | 10 |      |           |             |     |          |      |   | @(d:24, ERS)->CCR             | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 12                 |

| LDC        | @ERS+, CCR        | W                   | 4  |      |           |             |     |          |      |   | @ERS->CCR, ERS32+2->ERS32     | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 6                  |

| LDC        | @aa:16, CCR       | W                   | 6  |      |           |             |     |          |      |   | @aa:16->CCR                   | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 8                  |

| LDC        | @aa:24, CCR       | W                   | 8  |      |           |             |     |          |      |   | @aa:24->CCR                   | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 10                 |

| STC        | CCR, Rd           | B                   | 2  |      |           |             |     |          |      |   | CCR->Rd8                      | - - -                    | - - -                    | 2                  |

| STC        | CCR, @ERd         | W                   | 4  |      |           |             |     |          |      |   | CCR->@ERd                     | - - -                    | - - -                    | 6                  |

| STC        | CCR, @(d:16, ERd) | W                   | 6  |      |           |             |     |          |      |   | CCR->@(d:16, ERd)             | - - -                    | - - -                    | 8                  |

| STC        | CCR, @(d:24, ERd) | W                   | 10 |      |           |             |     |          |      |   | CCR->@(d:24, ERd)             | - - -                    | - - -                    | 12                 |

| STC        | CCR, @-Rd         | W                   | 4  |      |           |             |     |          |      |   | ERd32-2->ERd32, CCR->@ERd     | - - -                    | - - -                    | 8                  |

| STC        | CCR, @aa:16       | W                   | 6  |      |           |             |     |          |      |   | CCR->@aa:16                   | - - -                    | - - -                    | 8                  |

| STC        | CCR, @aa:24       | W                   | 8  |      |           |             |     |          |      |   | CCR->@aa:24                   | - - -                    | - - -                    | 10                 |

| ANDC       | ANDC #xx:8, CCR   | B                   | 2  |      |           |             |     |          |      |   | CCR ^ #xx:8->CCR              | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| ORC        | ORC #xx:8, CCR    | B                   | 2  |      |           |             |     |          |      |   | CCR V #xx:8->CCR              | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| XORC       | XORC #xx:8, CCR   | B                   | 2  |      |           |             |     |          |      |   | CCR⊕#xx:8->CCR                | 1 - H N Z V C J-Z# A&B&T | 1 - H N Z V C J-Z# A&B&T | 2                  |

| NOP        | NOP               | -                   |    |      |           |             |     |          |      |   | 2 PC->PC+2                    | - - -                    | - - -                    | 2                  |

(8) プロック転送命令

表 A. 1 命令セット一覧(II)

| 二モニック    | サイズ | アドレスシングモード／命令長(バイト) |    |      |           | オペレーション | コンディションコード |     |          |      | 実行ステート数* |                                                                                              |   |   |   |   |   |      |        |        |

|----------|-----|---------------------|----|------|-----------|---------|------------|-----|----------|------|----------|----------------------------------------------------------------------------------------------|---|---|---|---|---|------|--------|--------|

|          |     | #xx                 | Rn | @ERn | @(d, ERn) |         | @ERn/ERn+  | @aa | @(d, PC) | @@aa |          | I                                                                                            | H | N | Z | V | C | J-ZW | TMOVXt |        |

| EMOVY, B | -   |                     |    |      |           |         |            |     |          |      | 4        | if R4L ≠ 0<br>Repeat @R5→@R6<br>R5+1→R5<br>R6+1→R6<br>R4L-1→R4L<br>Until R4L=0<br>else next; | - | - | - | - | - | -    | -      | 8+4n*2 |

| EMOVY, W | -   |                     |    |      |           |         |            |     |          |      | 4        | if R4 ≠ 0<br>Repeat @R5→@R6<br>R5+1→R5<br>R6+1→R6<br>R4-1→R4<br>Until R4=0<br>else next;     | - | - | - | - | - | -    | -      | 8+4n*2 |

【注】\*: 実行ステート数は、オペコードおよびオペランドが内蔵メモリに存在する場合です。それ以外の場合は、「A.3 命令実行ステート数」を参照してください。

\*2 n は R4L または R4 の設定値です。

- ① ビット11から桁上がりが発生したとき“1”にセットされ、それ以外のとき“0”にクリアされます。

- ② ビット27から桁上がりが発生したとき“1”にセットされ、それ以外のとき“0”にクリアされます。

- ③ 演算結果がゼロのとき、演算前の値を保持し、それ以外のとき“0”にクリアされます。

- ④ 演算結果に桁上がりが発生したとき、“1”にセットされ、それ以外のとき演算前の値を保持します。

- ⑤ エクロック同期転送命令の実行ステート数は一定ではありません。

- ⑥ 商が負のとき“1”にセットされ、それ以外のとき“0”にクリアされます。

- ⑦ 商がゼロのとき“1”にセットされ、それ以外のとき“0”にクリアされます。

- ⑧ 商が負のとき“1”にセットされ、それ以外のとき“0”にクリアされます。

## A. 2 オペレーショントラップ

表A. 2 オペレーショントヨコードマップ(1)