スキルアップ・シリーズ

SKILL UP

# マイコン 技術者 スキルアップ事典

ハードに強いエンジニアになるためのデータバンク

長嶋洋一 著

あなたのプログラミング技術を支援する「Kernelシリーズ」/

好評発売中!

バッチ・ファイルの動作原理からEXE/COM/Cファイル変換ツールの製作まで

# DOSプログラマのための バッチ・ファイル研究

中島信行著 B5判 216頁 3.5" 2DD FD付き 定価2,600円 送料380円

バッチ・ファイルの起動・動作原理を解説しながら、バッチ・ファイルのEXEファイル化、COMファイル化の実現を考察していきます。また、バッチ・ファイルをプログラミング言語としてとらえた場合、プログラム記述に必要なコマンドを追加し、バッチ・ファイルをCプログラムへ変換する、バッチ・ファイル・コンパイラを作成しています。

第1章：バッチ・ファイルの起動原理／第2章：バッチ・ファイルをEXEファイルに変換／第3章：バッチ・ファイルをCOMファイルに変換／第4章：バッチ・ファイル・コンパイラ／第5章：バッチ・ファイル・ユーティリティ／第6章：バッチ・ファイルの問題点

ICE不要のソフト開発環境を構築する

# 68K/86系対応リモード・デバッガ

中島信行著 B5判 184頁 3.5" 2DD FD付き 定価3,700円 送料380円

FA関連のシステムを構築するとき、ソフトウェア・デバッグのためのツールが必要です。いままでは、ICE(In-Circuit Emulator)が多く使われてきました。本書では、このICEのかわりに簡単なSYMDEBレベルのデバッガを行うためのリモート・デバッガを、原理から、仕様、機能、使用法、プログラムの解説まで行います(ソース/実行形式ファイル付き：開発環境に合わせた移植も可能)。

第1章：リモート・デバッガの基礎／第2章：リモート・デバッガの使用法／第3章：リモート・デバッガのプログラム／第4章：ターゲット側のプログラム

パソコンによるソフト開発環境整備術

# 86系ROM化支援ソフトウェアの製作

中島信行著 B5判 144頁 5" 2HD FD付き 定価3,500円 送料310円

第1章：86系のROM化ツールEXE2HEX／第2章：プログラム・ダウンローダ／第3章：PC-9801でRS-232-Cの送受信割り込みを可能にする方法

C言語入門から実用プログラムの開発まで

# ためしながら学ぶCプログラミング

岡村延夫著 B5判 208頁 3.5" 2HD FD付き 定価2,800円 送料380円

第1章：ディスプレイに文字を出す／第2章：数と計算／第3章：判断と回数／第4章：関数と変数／第5章：配列とポインタ／第6章：文字列の扱い方／第7章：データをまとめる／第8章：ファイル／第9章：プログラムの考え方／第10章：大きなプログラムを作る

アセンブリ活用の考え方から応用事例まで

# MASM & DOSプログラミング

岡村延夫著 B5判 232頁 定価2,400円 送料380円

第1章：スタートの手がかり／第2章：使用する8086の機能／第3章：COMプログラムをつくる／第4章：バッチ・ファイルの活用／第5章：EXEプログラムをつくる／第6章：分割アセンブリと高水準言語との接続／第7章：マクロは役に立つか／第8章：ファイルを扱う／第9章：デバイス・ドライバと常駐プログラム／第10章：プログラムのデバッグと試験

MASMをC言語感覚で使うための前処理言語

# 構造化アセンブリPASMの製作

森川 治著 B5判 192頁 5" 2HD FD付き 定価3,000円 送料380円

第0章：PASMへの招待／第1章：PASMプログラミングの基礎／第2章：PASM文法解説／第3章：言語処理系PASMの作成

SKILL UP

# マイコン 技術者スキルアップ事典

ハードに強いエンジニアになるためのデータバンク

長嶋洋一 著

CQ出版社

# フレッシュマンへのエール

## ●新人の「技術不安」

本書は、エレクトロニクスに関するメーカーへの就職を考えている学生・技術者の卵の皆さん、メーカーに就職したばかりの新人エンジニアの皆さん、そして入社2~3年までの若手技術者の皆さんのために企画されました。エレクトロニクス技術・コンピュータ技術が激しく進歩するこの時代に、若手の皆さんのが体験する「技術不安」を解消して、自信をもってエンジニア人生に出帆してほしい、というのが本書の大きな目標です。

20世紀後半に人類史の表舞台に登場したコンピュータ技術は、現在では工業・商業ばかりでなく、人間のあらゆる活動になくてはならないものとなりました。その進歩のスピードと内容の複雑さ・巨大化は、すでに現場で活躍している先輩エンジニアですら、消化・吸収する前に新技術がどんどん登場してくる、と思うほどのプレッシャーとなっているものです。そしてこの世界にこれから飛び込もう、または飛び込んでみたばかり、というフレッシュマンにとっては、なおさら直面する技術の膨大さに圧倒されてしまうことでしょう。「技術不安」になるのもある意味で当然ですし、もちろん筆者も同じような不安を体験しました。

しかし、漠然とした不安というのは、相手の正体をよく見極めることで、あるいは全体の姿をやや高い視点から眺めてみると、自然に解消できるものだと思います。そこで本書では、

**「マイコン・システム技術者の仕事地図を示す」**

**「エンジニアとしての生き方を考える」**

という、ちょっと従来の技術書とは異なる視点を心がけてみました。具体的な「回路テクニック」とか「プログラム・リスト」はあまり多くありませんが、そういう技術情報を自分から効果的にアクセスしていく姿勢を身につけることを期待しているのです。さあ、つ

まらない「技術不安」にサヨナラして、前向きなエンジニアを目指そうではありませんか。

## ●専攻外・文系出身の意外な強み

ここ数年来の社会傾向として、慢性的なエンジニア不足が続いている。大企業から中小企業まで、あらゆる業種のあらゆる分野で、エレクトロニクス技術やコンピュータ技術が必須のものとなってきたために、たとえば大学や専門学校の電気・電子・情報系の学生だけでは不足しているからです。そのため、専攻を問わずに理系全体の学生を広く求めたり、さらには文系の学生であってもエンジニアとして採用し、社内研修によってプロとして再教育するケースも多く見られています。

しかし筆者の意見としては、「エンジニア=専門分野の出身」などという図式は、人材難の状況とは関係なく否定したいところです。エンジニアとしての適性というのは、もちろんある種の論理性や継続性、といった側面はありますが、「理系でないから向かない」などというのは誤解でしかないので、というより、むし

る専攻出身でないことがメリットとなる点もある、とさえ思います。これから時代、文系出身のコンピュータ技術者も当たり前になる、と確信をもって予言しておきましょう。

じつは筆者自身、大学での専攻は物理学(原子核物理)で、メーカに就職して電子関係のエンジニアとしてスタートした時点では、マイコンもディジタルもソフトもハードも、すべて白紙の状態でした。しかし物理屋というのは、「道具がなければまず道具を作ればいい」という、したたかな柔軟性(これを称して「物理する心」という)をもっています。知らない知識は臆せず先輩に聞き、知らないデバイス・装置は実験・分解して理解し、知らないコンピュータは触って覚え、知らない理論は文献から調べればいい、という「自由な感覚」ならもっているわけです。これは現在でも変わっていないらしく、コンピュータ言語はちょっと使わないを忘れてしまいますが、マニュアルさえ開けばすぐに現役バリバリにもどる、というぐあいで、「体得した一定の技術を後生大事に守る」よりも、「新しい技術の大海上を泳ぐことを楽しんでいる」のです。

ところが逆に、電気・電子・情報などの専攻の新入社員の中には、「ここは自分の専攻と違うのでわからない」というような、異分野への抵抗感をもつ人もいます。これは完全なマイナス面で、プロのエンジニアであれば、どんな新しい目標・新しい手法・新しい技術に直面していくかわからないのですから、自分のごく僅かな「過去の蓄積」など、忘れてしまったほうがいいのです。とくにコンピュータ技術などというのは日進月歩、どんどん新しくなっていきますから、むしろ「自分の専攻は役に立たないぞ」と自覚してスタートす

るぐらいのほうが、あとあとプラスになると思います。

### ●エンジニア冥利とは

まだ学生の皆さんにとって、プロの技術者の実際の姿がよく見えないかもしれません。たしかに、研究室や実験室の中で、黙々と毎日コンピュータや計測機器に囲まれて研究・開発・設計の作業に従事しているエンジニアの姿というのは、一般にわかりにくいものでしょう。技術者がいつも格闘している実験ボードや試作機というのは、最終的に完成されたスマートな製品とは似ても似つかない手作りのパラックであったり、製品の基板上にある切手サイズ程度のカスタムLSIが、開発段階では1枚四方の基板の3枚セットで、そのあちこちから修正の配線がわざわざと出ている「ジヤングル」であったりします。

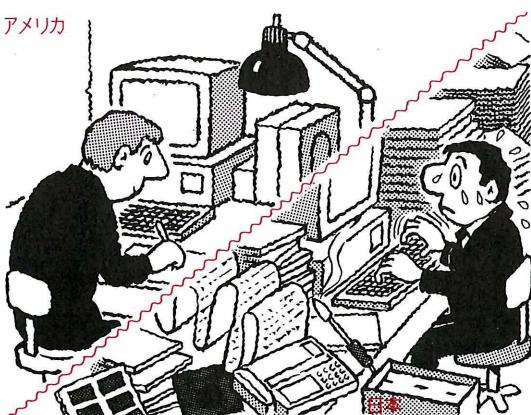

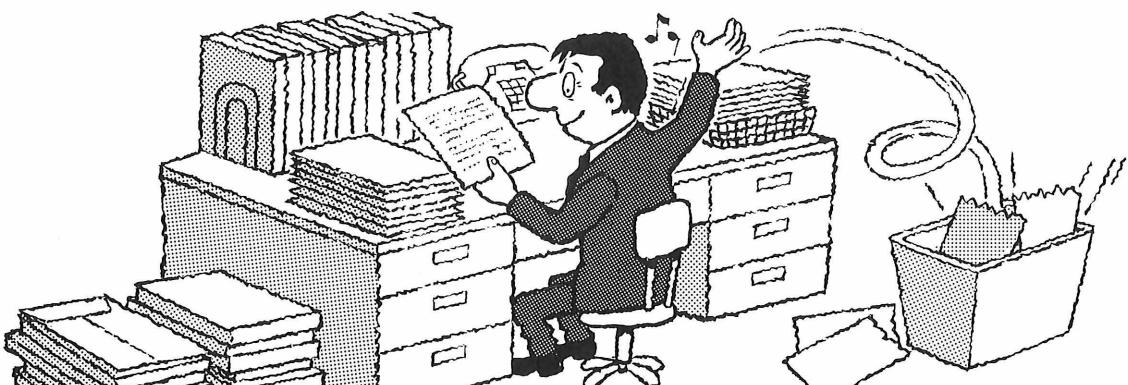

アメリカの研究者のスマートなオフィス(机の上に足を伸ばして、膝の上のキーボードを叩く)を想像するのも、たいていは大きな誤解です。実験室の地味な作業机には、多くの開発装置と実験ボードと部品が置かれ、ハンダごてやテスターが並んでいます。ソフト寄りの仕事場であれば、ファイルとプログラム・リストとフロッピが雑然と積み重なっている、という風景が普通のものでしょう。また、スケジュールに追われて残業が多いのも事実なのですが、「会社にいわれてやる」というよりも、「熱中するとつい残業しても続けてしまう」という傾向が、エンジニアの多くに共通したところのようです。

エレクトロニクスにしてもコンピュータにしても、正しい設計をすれば確実にその通りに動いてくれるから、人間味というか偶然性の面白味がないじゃないか、といわれたことがあります。たしかに理屈はそうなのですが、残念ながら実際には、なかなか新システムはうまく動いてくれません。ほとんど人間的とも思えるほど、開発途上のシステムのきまぐれなトラブルはいろいろと登場してきます。正しい「道具」であるはずの計測器や開発用コンピュータの欠陥を、トラブル追求の最中に発見することさえあります(筆者の場合、ついついこのトラブルとの格闘を楽しんでしまいます)。

やがて、システム全体が自分のモノとなり、なにより「製品」という具体的な形となって、世の中に送り出されることになります。これが、技術者としての手応えを感じる頂点といえるかもしれません。そして、

アメリカ

新システムが完成した時点で、それを開発した自分自身が、エンジニアとしてより成長している、というところも大切です。つまり、「同じ機能のシステムを開発しないで」というテーマがもう一度与えられたとすると、今度は1ステップ成長したその技術者によって、よりスマートで高性能でローコストな製品が、より短期間に美しく開発されることになるのです。開発対象とともに自分自身が成長していくところも、エンジニアという仕事の大いなる魅力だと思います。

### ●柔らかな頭と熱き心と

さて、それでは「エンジニアとして必要な姿勢」には、どんなものがあるでしょうか。なにしろ相手は深い深いエレクトロニクス技術・コンピュータ技術の世界ですから、膨大な技術情報を圧倒されずに、冷静に少しづつ理解していこう、という地道な姿勢はもちろん大切です。また、新しい概念には予備知識に頼らずに素直に接するとか、面倒がらずにマニュアルやデータブックを参照する、というのも、たとえば語学の初学者が「まめに辞書を引きなさい」といわれるのと同様の基本でしょう。電子回路とかコンピュータの動作というのは「規則通り」の世界ですから、理詰めで論理的に考える、という姿勢も大切です。

しかし、これら「当たり前の条件」以上に筆者が求めたいのが、「柔らかな頭と熱き心」という生き方です。いわゆる「工学系人間」というのは、上に述べたような真面目な点ではピカイチなのですが、いざというときやトラブルに直面したときの柔軟性とか、新しいシステムを検討する際の自由な発想とか、試行錯誤や新アイデアを楽しんで遊ぶ、といった余裕とかの面で、どうしても「固い」印象があります。理系アウトローの物理屋とか、文系出身(文学部の論理学専攻など)は、コンピュータのプロとして素質十分のエンジニアのほうが、そういう自由な発想の場では活躍した例も多く見かけています。この「柔らかな頭」を、フレッシュマンの誰にも期待したいところです。

そしてもう一つのポイントが「熱き心」です。毎日ほとんど無言でコンピュータに向かっている技術者、というと、なんだか暗くて、ロボットのような冷たさをイメージしてしまうかもしれません。たしかに、会社から給料をもらうと引き換えに自分の人生から一定の時間と労力を提供して、与えられた仕事を黙々とこなす「サラリーマン・エンジニア」もいるかもしれません

ません。しかし筆者は、これではあまりに淋しい、もっと前向きに、エンジニアとしての人生そのものを楽しんでしまおうではないか、と提案したいのです。

たとえばマイコン応用のシステムを新しく開発する、という「業務」は、仕事と考えるとプレッシャーもありますが、こんな楽しい「ゲーム」はちょっとない、という見方だってあるのです。技術者である自分自身がロールプレイング・ゲームの主人公となって、会社のカネで部品や開発機材をふんだんに駆使して、個人の趣味ではとても出来ないような費用と期間を集中してシステムを完成に導いていく、と考えると、こんな楽しいゲームは他にないでしょう。事実、多くの技術者が仕事に熱中する原動力は、会社のためでもカネのためでもなく、彼ら自身が、子供のようにその仕事で「遊んでいる」ところにあると思います。大きな声でこそさらいう必要はないかもしれません、仕事をゲームとして楽しんでもらいましょう。

### ●本書の構成について

コンピュータ技術・エレクトロニクス技術の世界のフレッシュマン技術者のために、という壮大な目標をもった本書ですが、実際にはエンジニアといっても、多くの業種・多くの職種に対応した、いろいろな仕事があります。そこで、ある意味で最大公約数となる対象として、本書では「マイコン・システム技術者」というポイントを設定してみました。これは、ハードからソフトまでをこなして、専用の組み込み機器を開発するシステムハウス(一品料理の特注システムを受託開発する技術者集団)の技術者というのが、まさにそのものズバリです。しかし本書の扱ういろいろな技術領

仕事をゲーム感覚で楽しもう!?

域は、ソフトハウスのプログラマであっても、システム設計のSEであっても、量産ベース民生機器のハード開発者であっても、いずれもこれから時代には必要となるものです。「自分の技術フィールドを限定することが、エンジニアとしての可能性の芽をつむことになる」という重要な視点を忘れずに、広い視野をもつための「事典」として活用していただければ、と思います。

全体の構成としては、まず<イントロダクション>として、「マイコン・システム」と「マイコン技術者」の定義からスタートし、概論として、その「仕事地図」をざっと眺めてみます。個々の技術的な内容については、最初はピンとこない部分もあるかもしれません、まずは「エンジニアの仕事」の全体像をつかんでみる、という作戦です。そして、つぎにマイコン技術者として必要ないろいろな技術項目について、「技術レベルのステップアップ」として、これもざっとチェックしていきます。個々の具体的な技術内容は<事典>のなかで取り上げられていますから、これら個々の技術(縦糸)を別の視点からくくった横糸、と考えてみましょう。

そして本編である<事典>とは、マイコン技術者がいろいろな局面で必要になる技術として、まず最初に

- (1) マイコン技術者のための基礎概論

- という項目で予備的な基本技術をまとめ、ついで

- (2) パソコン活用関連技術

- (3) マイコン・システム実戦テクニック

- (4) チップ関連技術

- (5) 信号と信頼性の技術

- (6) 情報収集テクニックとドキュメント技術

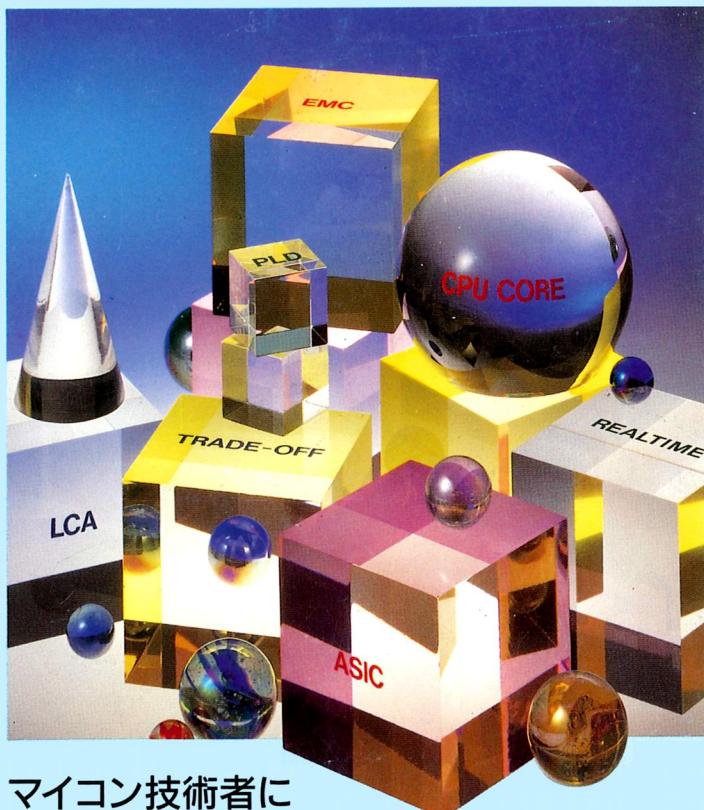

- (7) ASIC 技術

- (8) 並列処理・分散処理とネットワーク

の8項目に分類して、それぞれ関連する技術ポイントを集めてみました。これらの項目はそれぞれ独立したオムニバス構成となっていますから、本書のどこから読んでも(つまり食いでも)、それなりに役立つようになっています。

また<教科書>でなく<事典>としたのは、フレッシュマンにとって技術の全体に触れてみる材料として、さらに実務の現場においても参考になるように、という目標のためです。そこで、個々の内容が理論的に整

然と網羅されている、というよりも、現場で役立つテクニックとか、あまり理論書には書かれない実際的な視点、といったものが多くなるように心がけています。中堅エンジニアにとっても、なにかの折りに本書をバラバラと眺めてみれば、その時点での自分の技術レベルの確認に利用していただけるでしょう。

### ● 「エンジニア万歳！」に向かって

まだフレッシュマンの皆さんにとって、「エンジニアとしての人生目標」など想像がつかないかもしれません。エレクトロニクス技術やコンピュータ技術の歴史が若いために、お手本となるべき先輩技術者もまだ現役の人ばかりで、それら先輩エンジニアが、これからどういった「理想」の姿をわれわれに見せてくれるのかわからないのも事実でしょう。

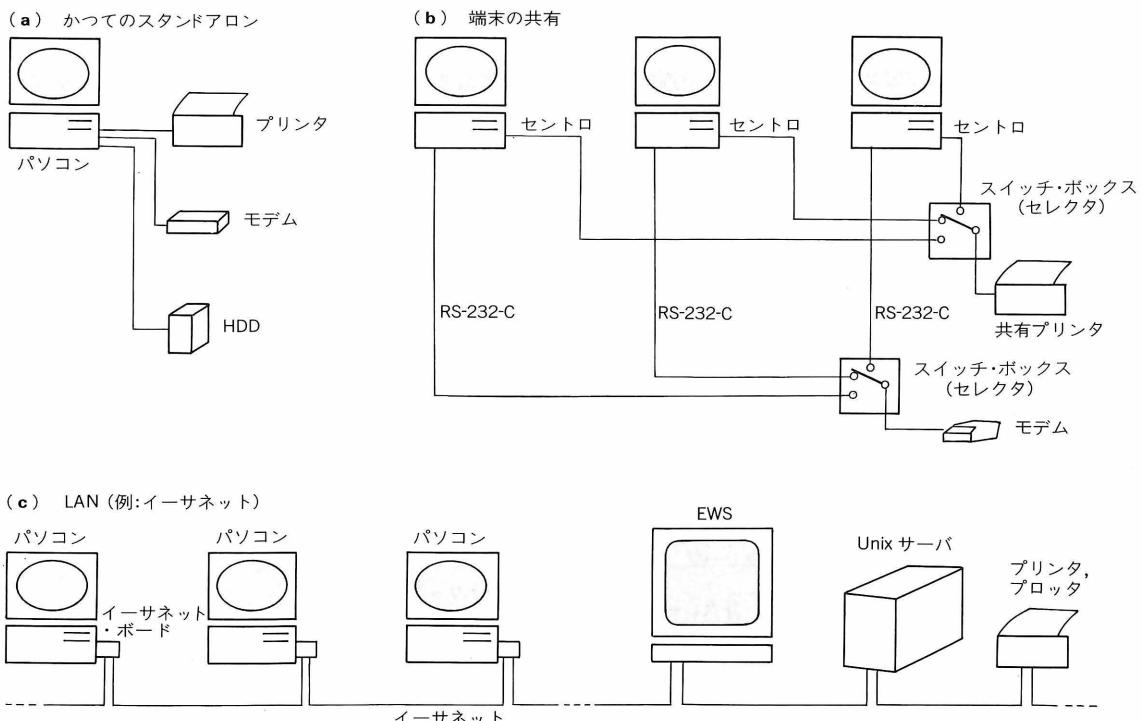

ただ、次第に充実してきている「技術者のための支援環境」によって、これからエンジニアの日常がより快適に、本人の能力をより効果的に引き出す方向に向かうことだけはたしかなようです。技術者がEWS(エンジニアリング・ワークステーション)ネットワークの環境によって周囲の世界と結びつき、知的なコンピュータ支援によって効率的に高度なシステムを開発していく…こんなシーンが未来予測として語られています。筆者などはこれに対して、実現されていく際にまだかなりの曲折があるだろう、などと多少の経験から意地悪に見てしまいますが、基本的な傾向としては、技術者の環境の未来は明るいと思います。フレッシュマン技術者は、これまでの先輩技術者が望んでも得られなかった、高度で快適な開発環境を約束されているわけです。

さて、エンジニアとしてのスタート付近にいる皆さんのための<プロローグ>は、これでおしまいです。勇気と元気が湧いてきたでしょうか。ここからこの世界に飛び込んで、自分なりの「エンジニアの理想像」を模索しながら頑張るのは、あとは皆さん次第ということになります。10年選手として「エンジニア万歳！」と実感するようになった筆者からの、スタート時点でのエールは十分に贈ったつもりです。皆さんのこれからに期待し、先輩としてライバルとして、心から応援したいと思います。

|                           |    |

|---------------------------|----|

| <プロローグ>                   |    |

| フレッシュマンへのエール              | 3  |

| <イントロダクション>               |    |

| マイコン・システム技術者の世界           | 11 |

| マイコン技術者の仕事地図              | 11 |

| 目標技術のステップアップ              | 16 |

| <コラム> マイコン技術者の徒弟制度        | 18 |

| <飛び石コラム> おすすめ BOOKS ①     | 21 |

| <Appendix> ある「技術勉強会」のメニュー | 22 |

## 事典編

|                       |    |

|-----------------------|----|

| 1. マイコン技術者のための【基礎】概論  | 32 |

| ディジタル技術の基本            | 32 |

| <コラム> 解答1 符号付き乗算回路の例  | 38 |

| <飛び石コラム> おすすめ BOOKS ② | 39 |

| アナログ技術の基本             | 41 |

| マイコン・システムの3形態とトレードオフ  | 46 |

| ヒューマン・インターフェース考       | 53 |

| 2. パソコン活用システム関連技術     | 58 |

| ハードウェア技術の基本           | 58 |

| ソフトウェア技術の基本           | 60 |

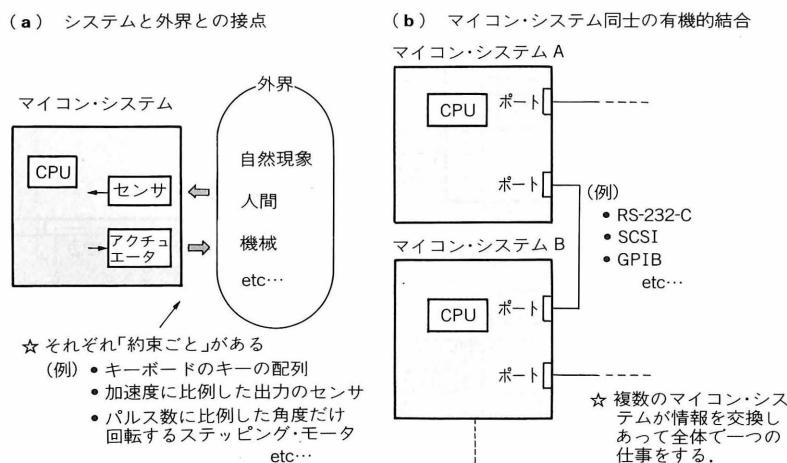

| 外部システムとのインターフェース技術    | 67 |

| <コラム> リアルタイム・システム     | 70 |

| <飛び石コラム> おすすめ BOOKS ③ | 71 |

### 3. マイコン・システム実戦テクニック集 ..... 72

|                    |    |

|--------------------|----|

| システム設計の実例          | 72 |

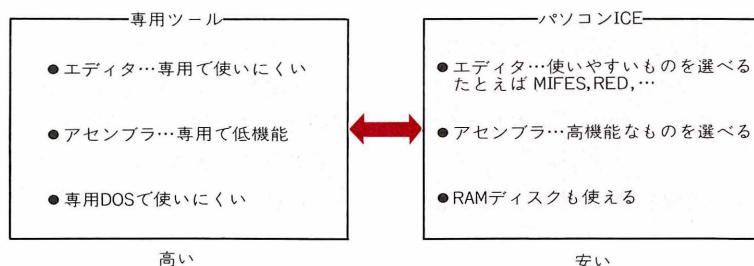

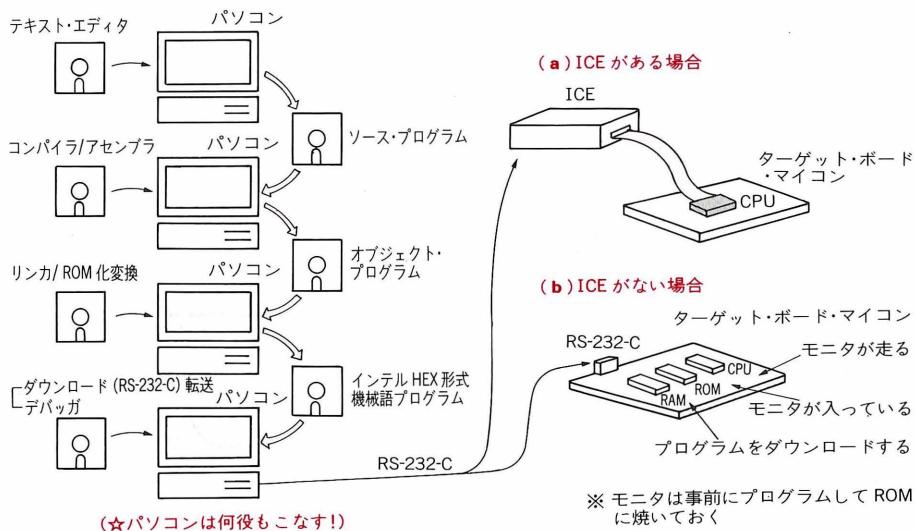

| 開発環境：ICE           | 77 |

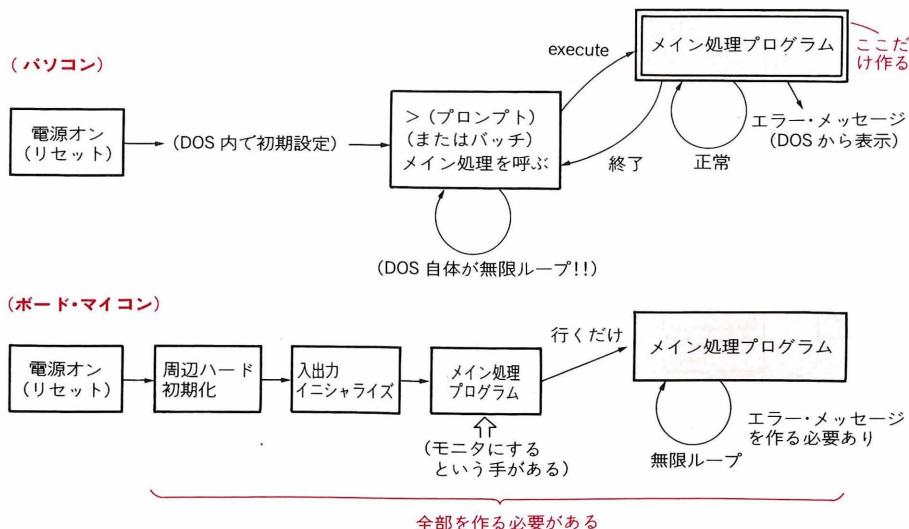

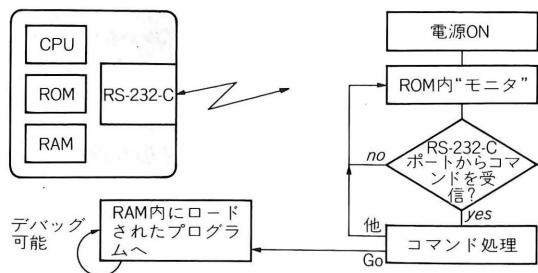

| 開発環境：モニタ           | 79 |

| ソフト・テクニック：ワンパターン処理 | 81 |

| ソフト・テクニック：FIFO 処理  | 85 |

### 4. すべてはチップから：「チップ」関連技術 ..... 88

|                        |    |

|------------------------|----|

| 周辺LSI                  | 88 |

| <コラム> 解答2 可変クロック発生回路の例 | 90 |

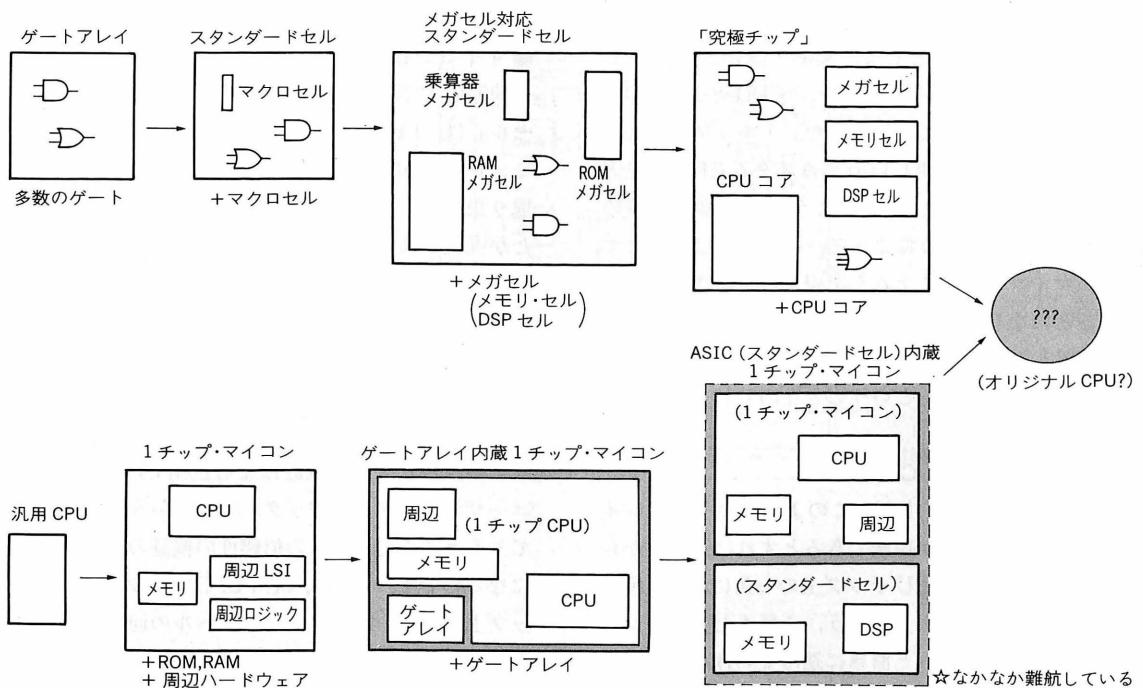

| メモリ                    | 95 |

| Iチップ・マイコン              | 96 |

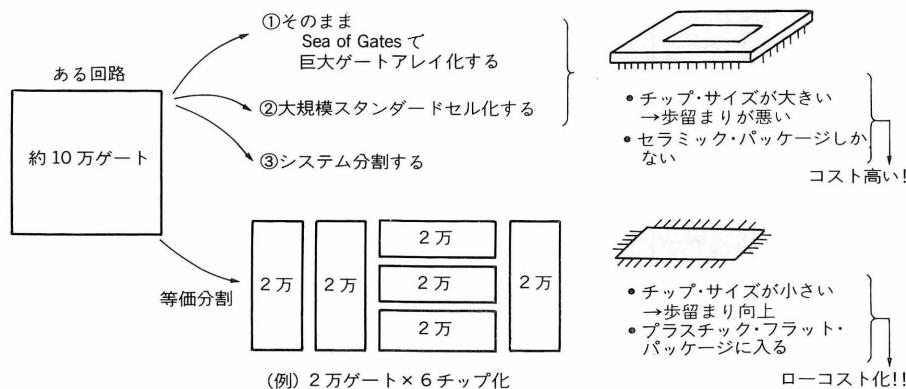

| セミカスタムIC               | 98 |

### 5. 「信号」技術から「信頼性」技術へ ..... 105

|                |     |

|----------------|-----|

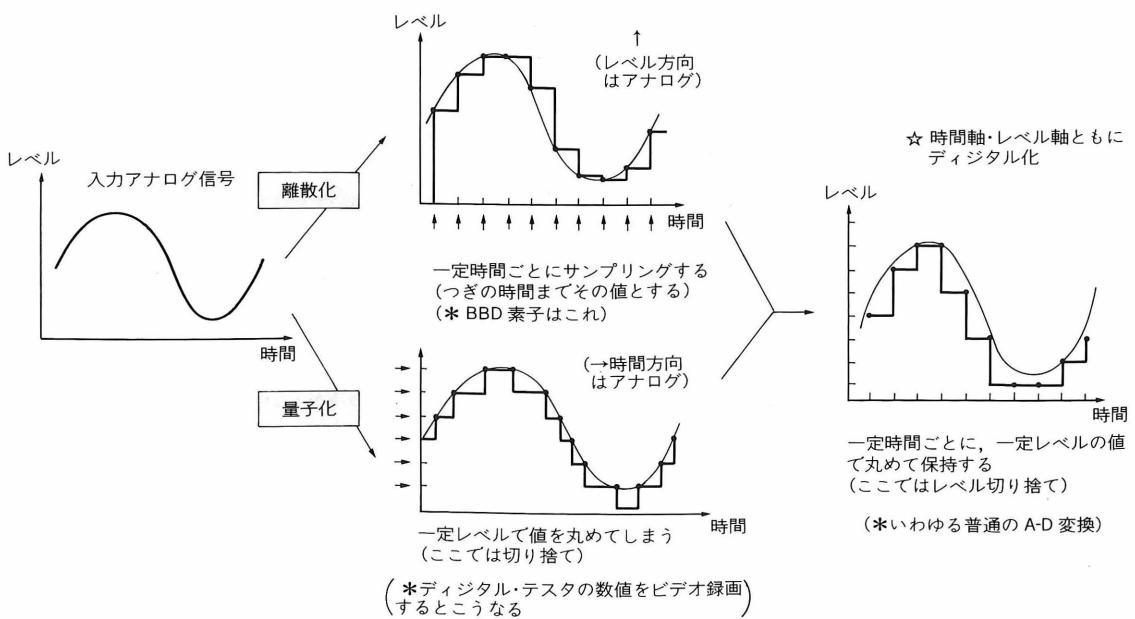

| アナログ→デジタル変換の考察 | 105 |

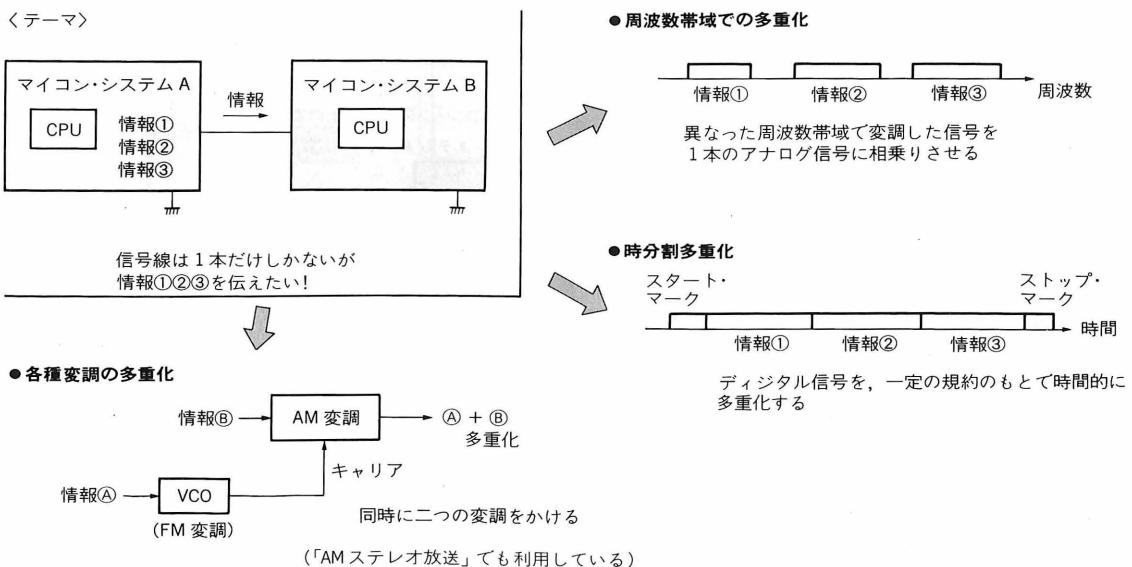

| インターフェース信号の検討  | 108 |

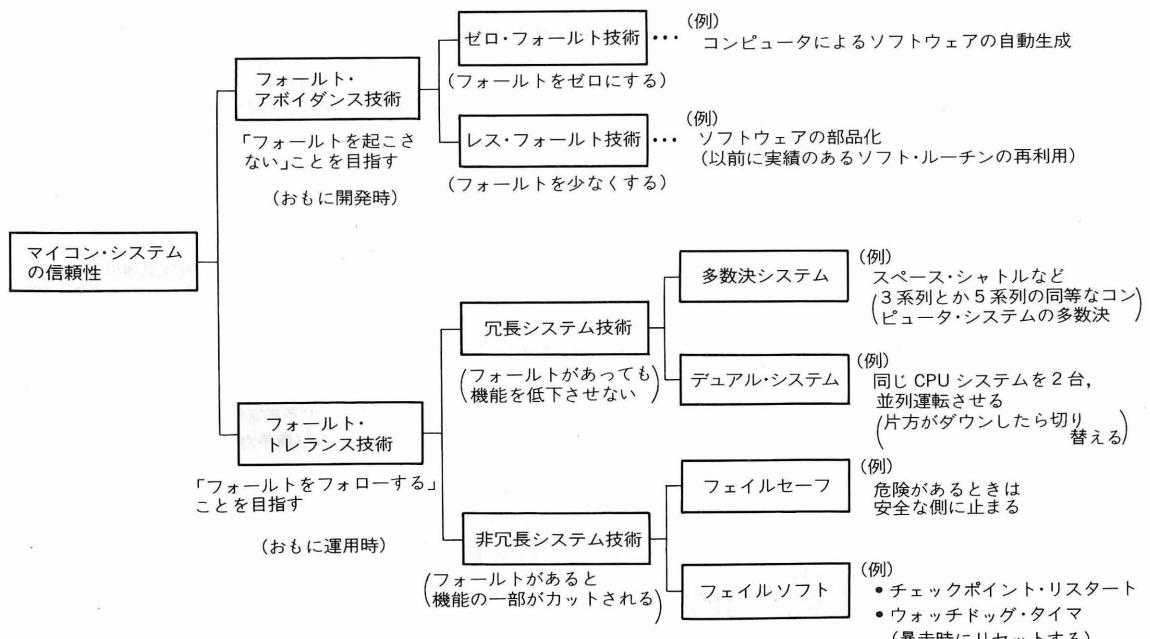

| 信頼性の技術         | 110 |

| <コラム> 境界値分析    | 112 |

| EMC技術          | 113 |

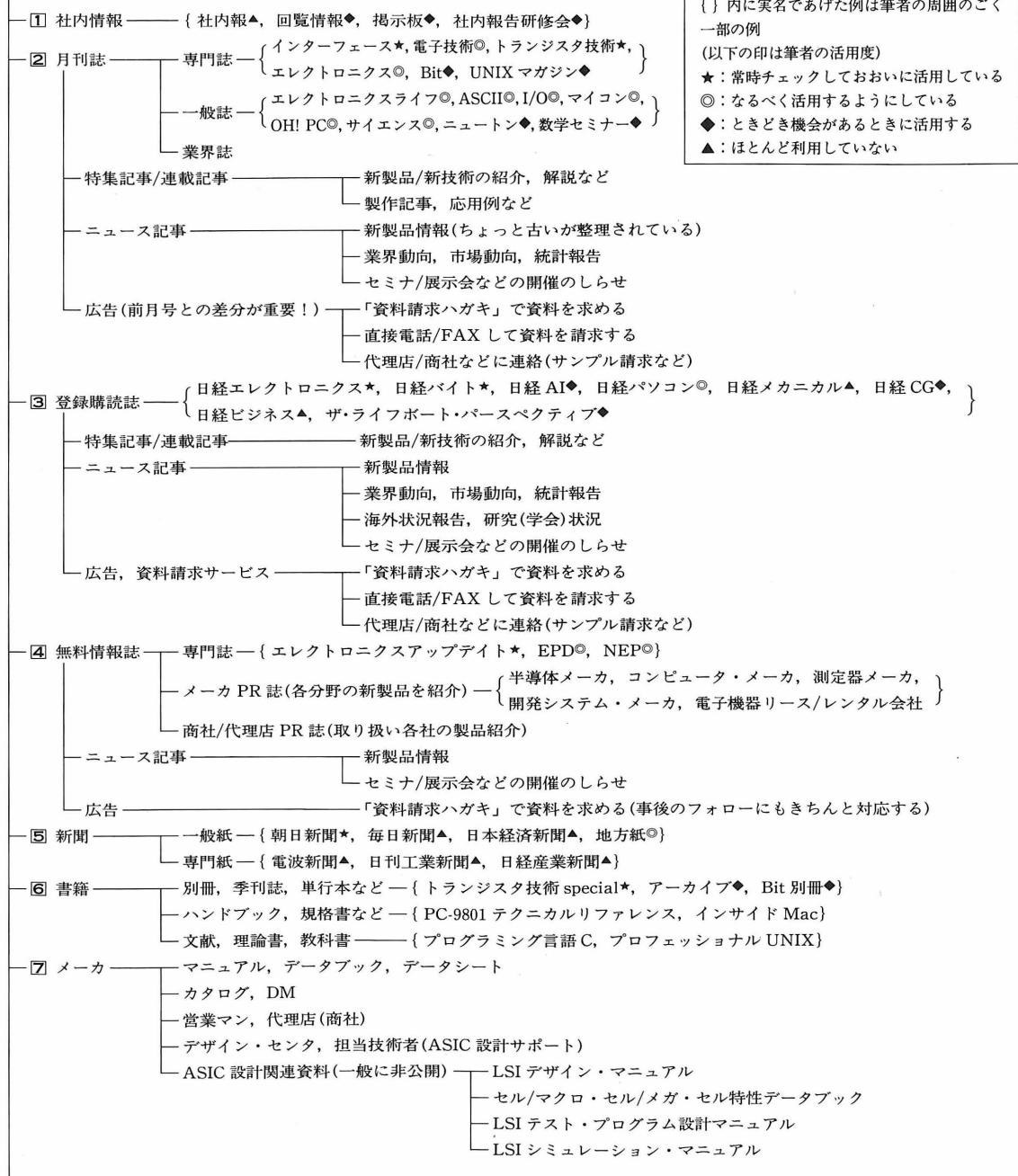

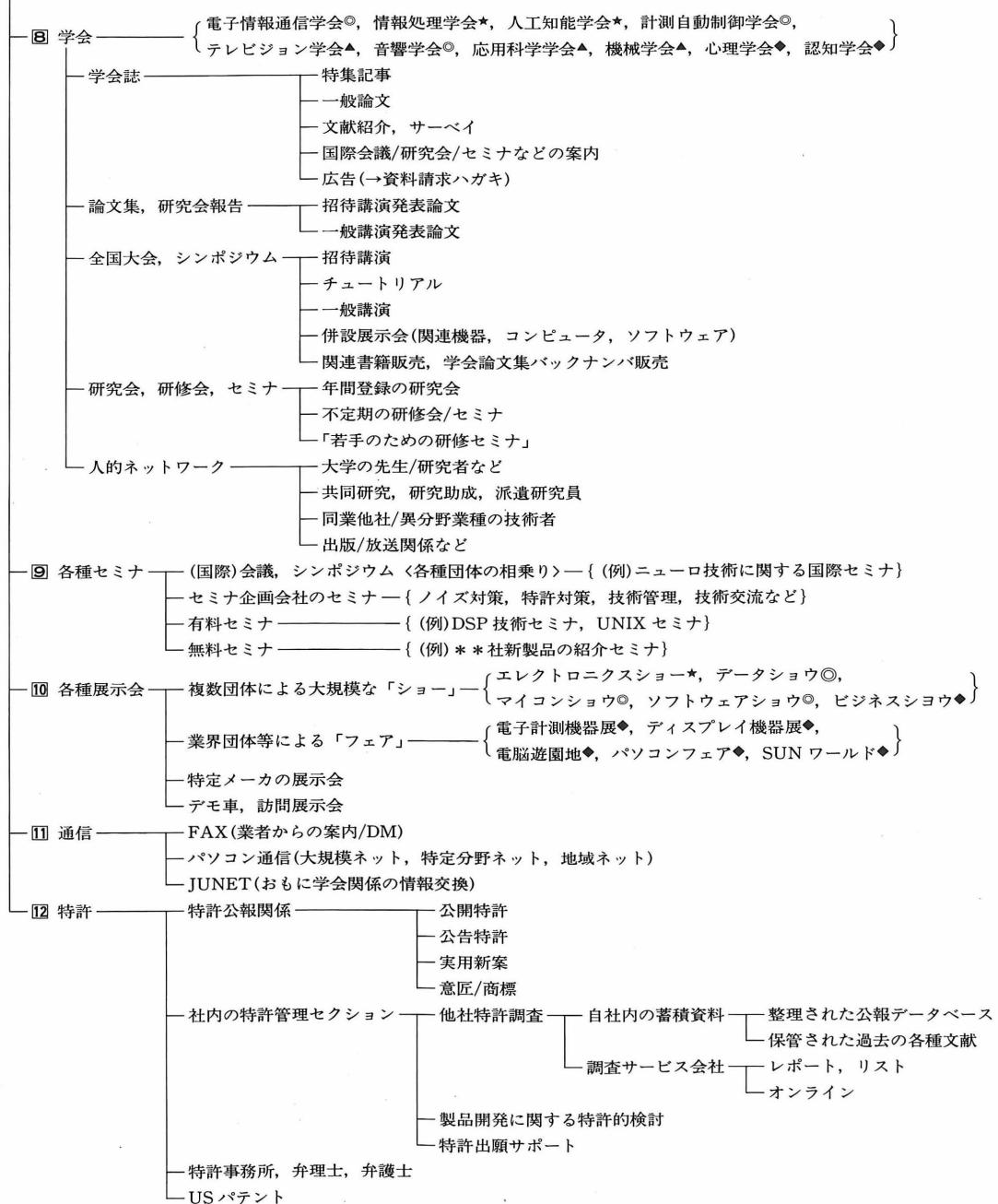

### 6. 情報収集テクニックとドキュメント技術 ..... 116

|                      |     |

|----------------------|-----|

| あるエンジニアの情報収集の例       | 116 |

| 技術情報の活用テクニック         | 121 |

| エンジニアのドキュメンテーション技術論  | 123 |

| <コラム> プロジェクト管理も重要な技術 | 127 |

| <飛び石コラム> おすすめBOOKS④  | 128 |

|                                   |     |

|-----------------------------------|-----|

| <b>7. 上級システム：ASIC 技術</b>          | 129 |

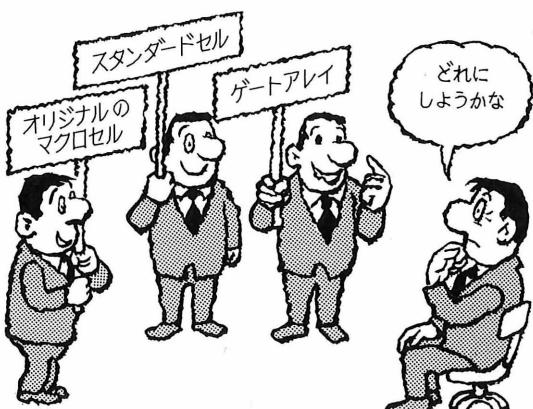

| ゲートアレイからスタンダードセルへ                 | 129 |

| <コラム> ビットスライス CPU                 | 134 |

| CPU コア内蔵「究極チップ」へ                  | 136 |

| 「究極チップ」の技術ポイント                    | 139 |

| セミカスタム CPU からのアプローチ               | 143 |

| カスタム CPU への道                      | 148 |

| <br>                              |     |

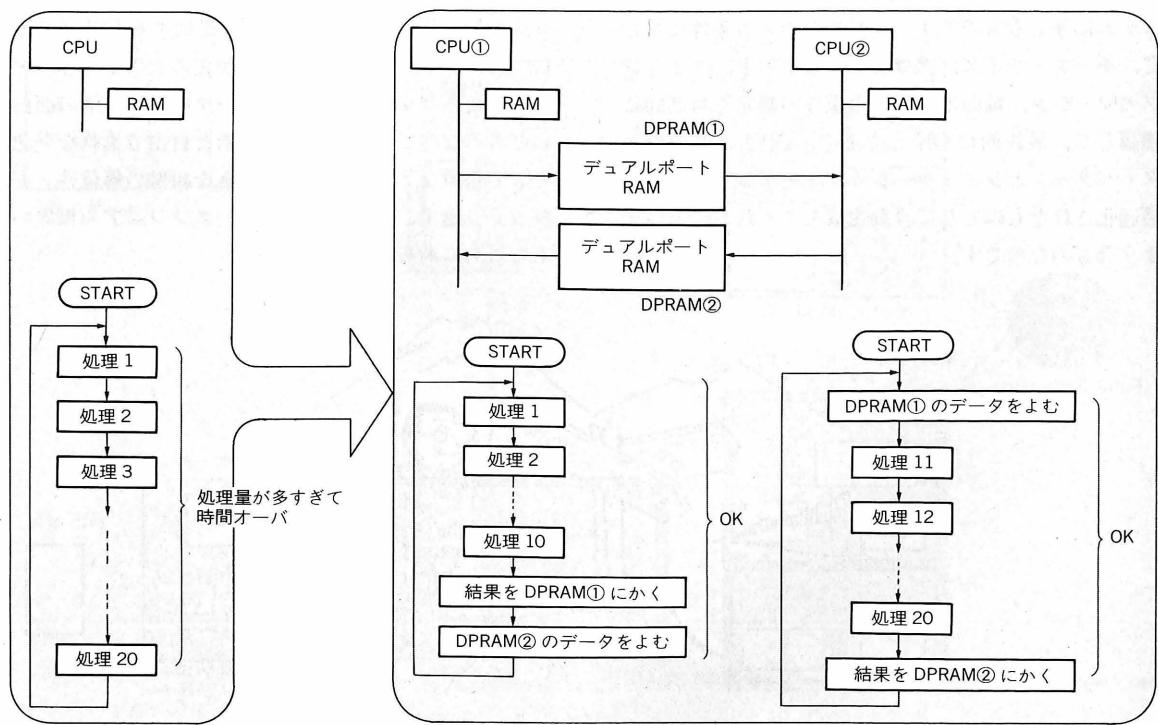

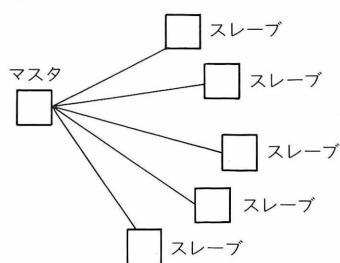

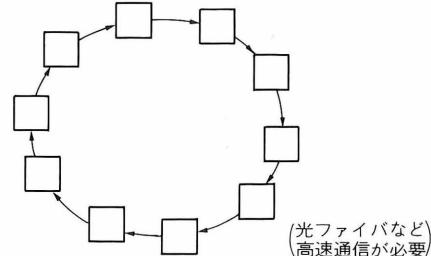

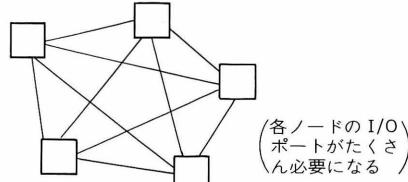

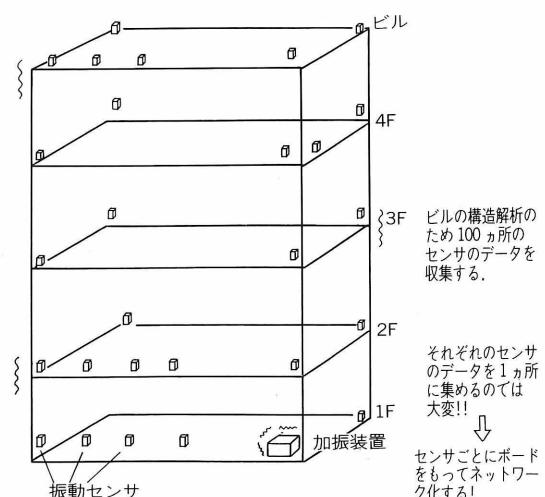

| <b>8. 並列処理・分散処理とネットワーク</b>        | 150 |

| ネットワーク化によるシステム性能向上                | 150 |

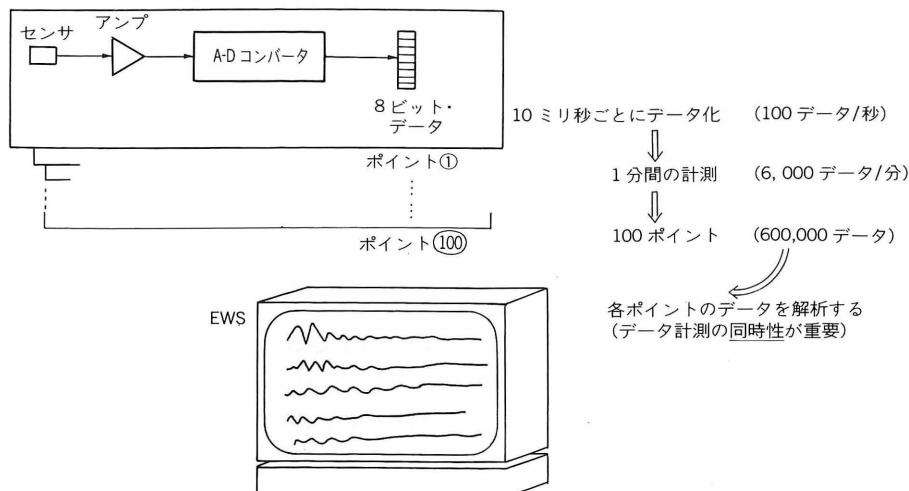

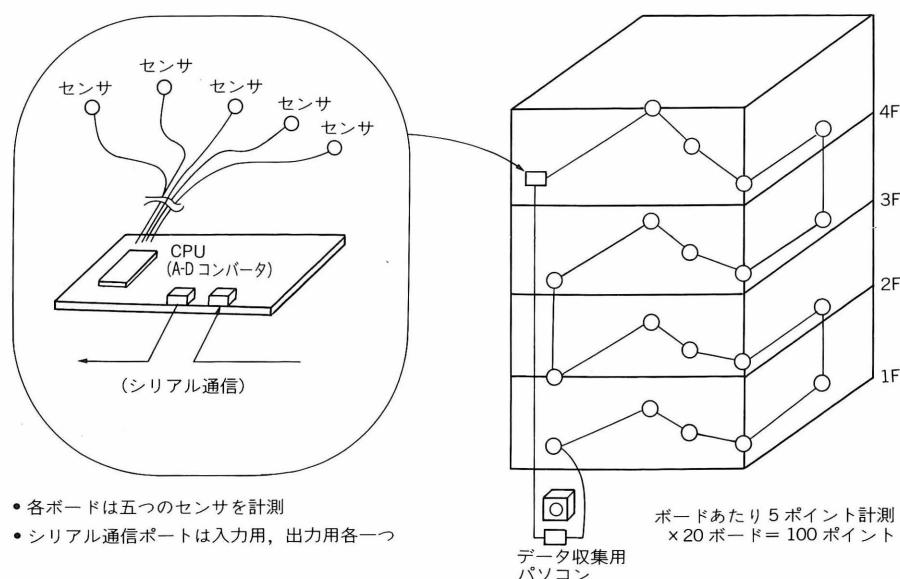

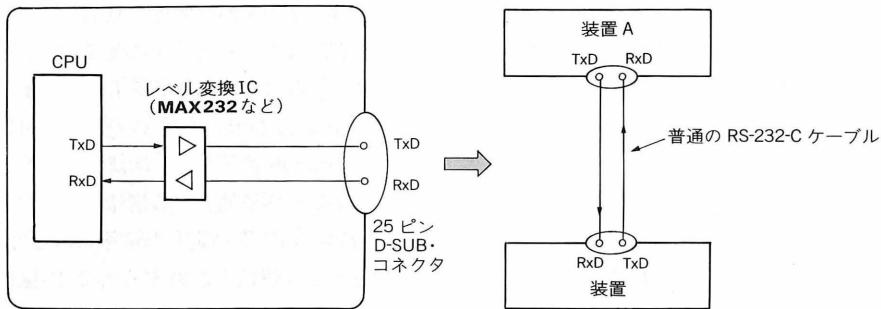

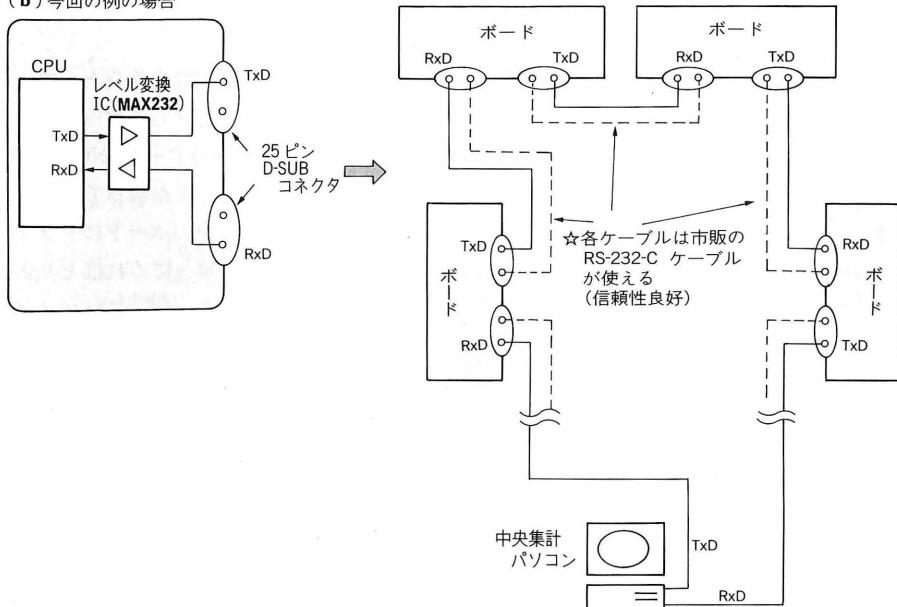

| ボード・マイコンによる分散処理の例                 | 153 |

| チップによる並列・分散処理の例                   | 158 |

| ASIC 化による分散処理                     | 162 |

| <Appendix> 体験的 ASIC 開発入門          | 165 |

| <br>                              |     |

| <b>&lt;エピローグ&gt;<br/>エンジニア万歳！</b> | 171 |

| <br>                              |     |

| <b>INDEX</b>                      | 175 |

# マイコン・システム技術者の世界

## マイコン技術者の仕事地図

### ●マイコン・システムとは

本書では「マイコン・システム技術者」を対象としていきますから、まず最初に「マイコン・システムとは」という定義について述べることにしましょう。

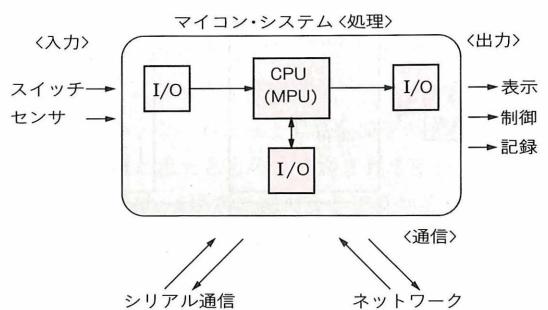

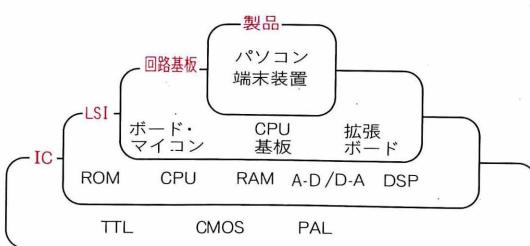

ひとことで定義すれば、ここで取り上げるマイコン・システムとは、一般にCPUとかMPUと呼ばれる、マイクロプロセッサ(またはマイクロコンピュータ)を使用したシステム、ということになります(図0.1)。

たとえば、パソコン(パーソナル・コンピュータ)は立派なマイコン・システムですが、エアコン・炊飯器・洗濯機などの家電製品やカメラ・自動車・電話機などでも、機能強化のためにマイコンを内蔵するのは常識となっています。そしてもちろん、事務処理、工場の自動化、通信機、ゲーム機などもマイコン技術の結晶です。「コンピュータ」=「電子計算機」という名前の神通力はもはや過去のもので、現在ではあらゆるエレクトロニクス機器のたんなる「部品」として、マイクロプロセッサをふんだんに使うのが当たり前になっています。

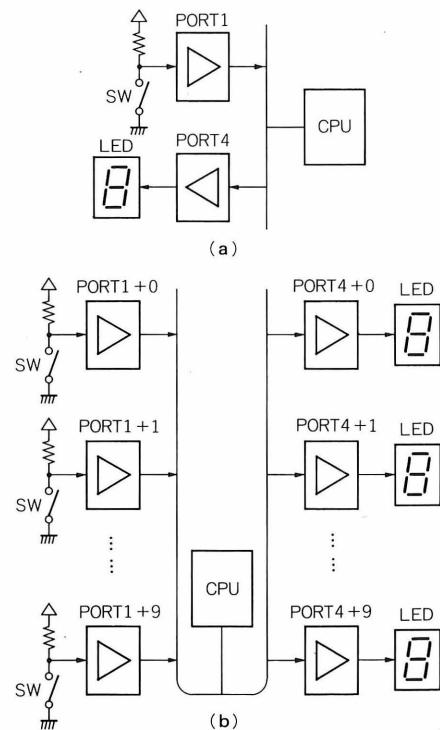

そして、CPUを使うという内部の条件とともに、「システム」として外から見る視点も重要です。マイコン・システムとは図0.1のように、全体の動作を制御する中央のCPUとともに、システムの外部(外界)とCPUとが情報交換するためのI/O(インターフェース)処理部分があり、システムとして「外界となんらかのやりとりをする」性質があります。パソコンのキーボードから入力するとか、CRTディスプレイから表示出力するとか、通信ポートを介して外部と通信する、といった

動作が、ここでの外部インターフェースの典型的な例です。

また、簡単なマイコン・システムでは図0.1のように1個のCPUからなりますが、2個とか3個以上のCPUが分業・協力しながら、全体として一つのシステムを構成するような「マルチプロセッサ・システム」も多く、たとえば自動車では数個から十数個のマイコンが搭載されています。また、マイコンには荷が重い複雑・高速な処理を担当する専用のハードウェア(チップ)をもつもの、複数の独立したマイコン・システム同士が通信ネットワークを介して共同作業(分散処理)をするシステム、反対にたった1個のチップにすべての回路機能を盛り込んだ電卓のようなシステムもあります。なお、ここでの定義によれば、ワークステーションのような大規模システムまで含まれることになりますが、本書では、一人の技術者が相手にできるぐらいの規模を考えしていくことにします。

### ●マイコン技術者の守備範囲

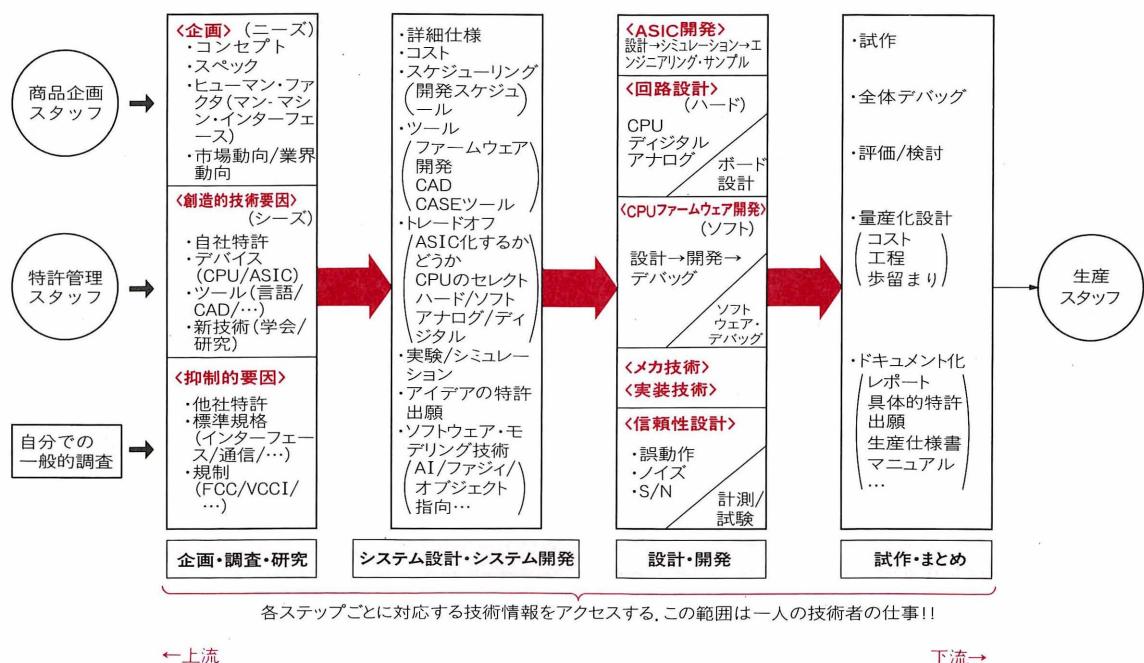

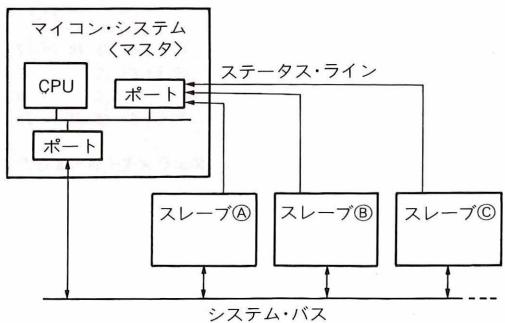

マイコン技術者の仕事の領域を具体的に考えてみるために、図0.2の例について見ていくことにしましょ

[図0.1] マイコン・システムとは

う。この例では、調査・研究からはじまって、システム全体の設計・開発段階、さらにシステムの各部分の具体的な設計・開発段階、そして製品の生産につながっていく試作・まとめの段階まで、時間とともにステップが推移していくものとしています。また、各ステップの中でも、いろいろな分野での作業が横に広がり、平行して進められることがわかると思います。

もちろんフレッシュマンが、いきなりこの仕事を全部任される、ということはありません。現役の技術者の大部分が、この領域のどこかの専門家として活躍しているわけです。また、どちらかというと大きな企業ほど、これらの仕事領域の細分化・専門化が徹底しているために、図0.2の全部の領域を一人のエンジニアが担当する、などということは希であるかもしれません。この意味で、「小さなシステムハウスの技術者のはうが、全体を見渡す仕事をすべてカバーすることになるために、むしろ技術的には面白いものだ」という意見もあります。

設計・開発の段階については、

- (1) システム全体の設計・開発段階

- (2) システムの各部分の具体的な設計・開発段階と2段階に分けてありますが、図の左側の部分とい

るのは、ソフトウェアであれば「上級SE」の仕事に対応する、という見方によるものです。もちろん、この部分を担当するためには、具体的な設計・開発技術が十分に身についている必要がありますから、ここは中堅・ベテラン技術者の世界と考えられます。若手技術者の皆さんには、基礎的な技術力をアップしながら、この領域の仕事に進出していけるように、先輩のテクニックを吸収していくことになるでしょう。

また、最終段階として「試作・まとめ」という呼び方をしていますが、これは前段の具体的な設計・開発作業と明確に区分されるものではありません。しかし、ここでは実際の製品として完成させる作業とともに、この開発によって得られた技術的な収穫を、つぎのステップでの活用に向けてまとめる、という重要な性格があるために、あえて独立のものとしてみました。

それでは、図0.2の仕事の流れについて検討していきます。

### ●企画・調査・研究

図0.2のステップのいちばん上流にあるのは、「企画・調査・研究」という仕事です。ここでは、具体的なシステム開発のテーマとは一見関係ないような、一

[図0.2] マイコン・システム技術者の仕事(守備範囲)は?

各ステップごとに対応する技術情報をアクセスする。この範囲は一人の技術者の仕事!!

←上流

下流→

一般的な技術情報(学会の論文集・研究報告とか特許公報のような技術情報)を扱います。経験のあまりないフレッシュマンにとっては親しみのない、どこか縁のない世界のもののように思えるかもしれません、ベテラン技術者にとっては、直接は関係のない特許資料や学会発表の中から、将来の具体的実現のためのヒントをかぎつけるきっかけにもなるのです。

新聞や雑誌に「新技術」などと取り上げられる話題は多くありますが、たとえばあまりに高価で非現実的だったり、信頼性や精度の点で実用的でないような、「アイデア先行」の技術も多くあります。ところがプロの技術者は、マスメディアよりもかなり前から、これらの新技術の情報を入手して、さらにそれを現実的なシステムとするための実験・開発を進めることさえあるのです。

たとえば、「A大学で基礎実験に成功した光センサが、1年後にBメーカの新製品コピー機のスキャナに応用されていた」というように、一般の目には見えない水面下で進むことになりますから、現代の企業戦略としても重要なものです。この「企画・調査・研究」活動は、新しい技術を前向きに取り入れていく技術者にとって、必須の業務といえるでしょう。

また、フレッシュマンが現場で直面するものの中に、各種の「規格」があります。これは、複数のメーカーがそれぞれ勝手に独自のインターフェースやフォーマットを用いると、ユーザが混乱してしまうために、協定のもとに共通規格として、お互いに規定しているものです。メーカーの技術者とすれば、新システムを開発する場合には、この規格というのは開発の自由度を制限する、抑制的な要因として関与していくことになります。しかし一方で、「規格」の適切な活用は、開発の効率化と信頼性の向上を同時に得ることにもつながります。たとえば、「まったく新しいアイデアの事務機器を開発する」という場合でも、入力装置や表示・印刷装置、あるいは外部との通信ケーブルや信号フォーマットをまったく独自のものにしたら、全体の設計・開発コストが巨大になってしまうだけでなく、すでに一般に出回っている機器が使えませんから、おそらくそんな「新製品」は市場に受け入れられないでしょう。この意味で、各種の規格をよく理解して活用していくことは、コンセプトのオリジナリティとは別の次元の問題として、重要なことなのです。

## ●ニーズ指向とシーズ指向

新しいシステムを生み出すための企画・調査という領域の仕事では、二つの方向性があります。

ひとつは、市場やユーザの希望・要望、つまり「新システムに求められるもの」という「ニーズ」を調査・分析して、それを満足するための新製品を企画・開発していく、という手法です。このためには、たとえば営業セクションを担当するスタッフとの情報交換の中から、自社の得意な技術によって実現可能なものを探っていく、というような視点が重要となります。やはり、これもベテラン技術者の仕事でしょう。

もうひとつは、日頃から研究・開発している新しい技術(基礎技術を含む)の中から、そのユニークな技術をうまく応用することで、独自の付加価値をもった新製品の企画・開発を提唱していく、という自社開発技術(シーズ)からの発想もあります。このためには、目先の製品開発にふり回されずに、もっと長いスケールでじっくりと研究・開発に取り組む姿勢も必要となります。特許・ソフトなどの知的所有権意識の高揚している現代では、シーズ指向というのはかなり手堅い戦略であるともいえます。

エンジニアのシーズ指向のためには、つねに世の中の進歩をチェックするとともに、大学や研究機関の研究の先端状況を把握することが重要です。また、たとえば従来は1チップに入りきらない規模のためメリットの少なかったユニークな回路が、LSIメーカーの微細化の進展によって実現されるといった、他社・他業界との関係によても、状況はつねに変化していきます。技術者は実験室にこもるばかりが能ではなくて、このような情報収集のために、セミナーや研究会などをチェックして歩き回ることも重要なことです。

## ●システム設計・開発

設計・開発のステップは、開発プロジェクトであればプロジェクト・リーダーの仕事に相当するものです。その中には、開発作業のスケジューリングやコスト検討のようなプロジェクト管理とか、アイデア段階での特許出願のような、ちょっと製品開発そのものの技術要因とは別種と思えるものまで含まれます(これらの技術については、<事典>編のなかで具体的にふれてています)。

そしてこの段階で一番重要なのが、後述する「トレードオフ技術」を活用した、システムを大きく切り分

けて構成していく作業になります。たとえば、ある仕様をもった製品システムは、ベテラン技術者にとって、何通りも実現の方法が考えられる、というのが普通です。その中から、ソフトとハードをどう組み合わせ、どんなデバイスとどんなソフトウェア技術とを使って、さらにどんな開発手法で試作から生産まで進めていくか、という全体構想を、バランスよく構築していくものです。簡単な例でいえば、ある処理をソフトで行うのか専用ハードを設計するのか、という選択にしても、

- 性能・処理速度

- コスト(開発コスト・量産コスト)

- 開発期間

- 信頼性・規格

などの種々の要因が関係していますから、なかなか判断が難しいものなのです。そして、ここでのシステム構想が決定されてしまえば、もうあとでは変更がきかない場合が多いだけに、決定の際の責任も重大です。

また、「開発環境」とまとめていますが、開発ツール、開発支援装置、開発言語、デバッグ手法などの構想を決定することも、この上流ステップでの重要なポイントとなります。もし開発環境の選択を間違うことになれば、ある意味でほとんどプロジェクトの失敗につながってしまいます。いくら各技術者が頑張っても、適切でない開発環境では、時間も労力も能力も、文字通り無駄使いになってしまいます。開発環境は日々進歩していますから、この状況にアンテナを立てるのも、技術者の重要な仕事なのです。

## ●具体的設計・開発

一般的に「技術者」といえば、この具体的な設計・開発ステップの仕事が想像されるものようです。いわゆるハード屋であれば、試作基板に部品をハンダ付けしてはシンクロのプローブを当てる、あるいはソフト屋であれば、毎日コンピュータの画面を眺め続けている、というようなイメージではないでしょうか。しかし、**最近のマイコン・システムというのは、どうもハードとソフトの境界があいまいになって、ハードだけのハード屋もソフトだけのソフト屋も少なくなってきた**。つまり、あらゆる技術者が、電子回路技術からソフト開発までをカバーしてしまう、逆にいえばハードからソフトまでを守備範囲としないと、満足な仕事ができないようなレベルになっている、という状

況を理解しておく必要があります。

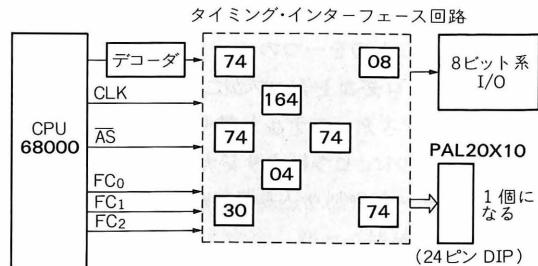

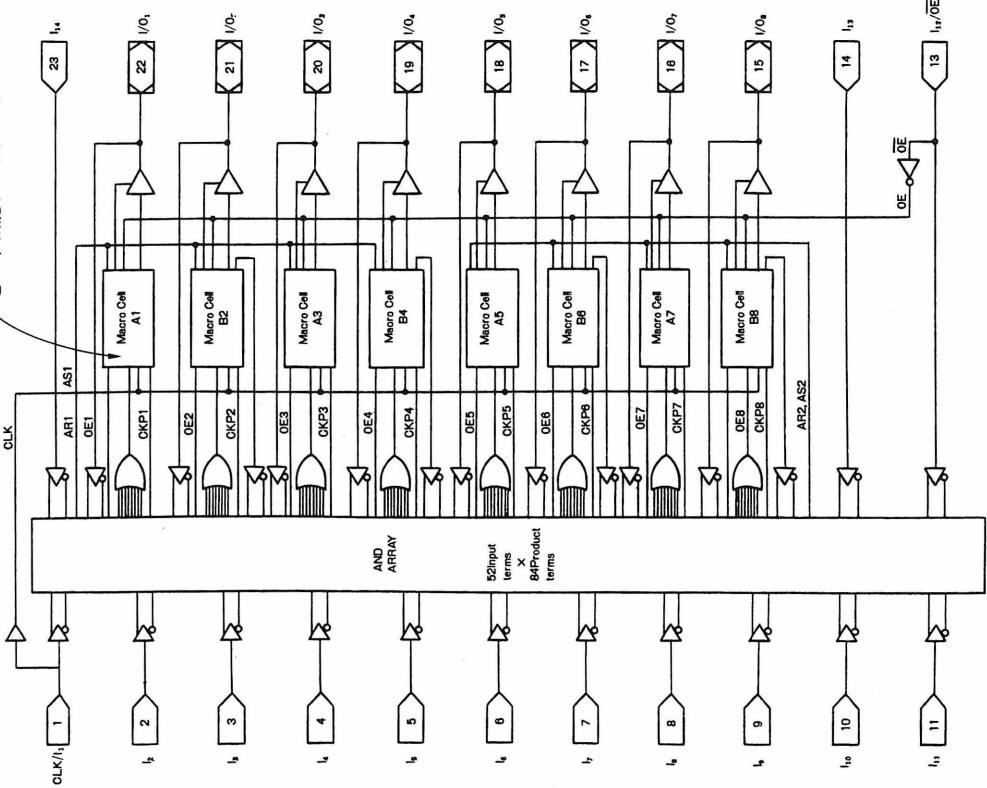

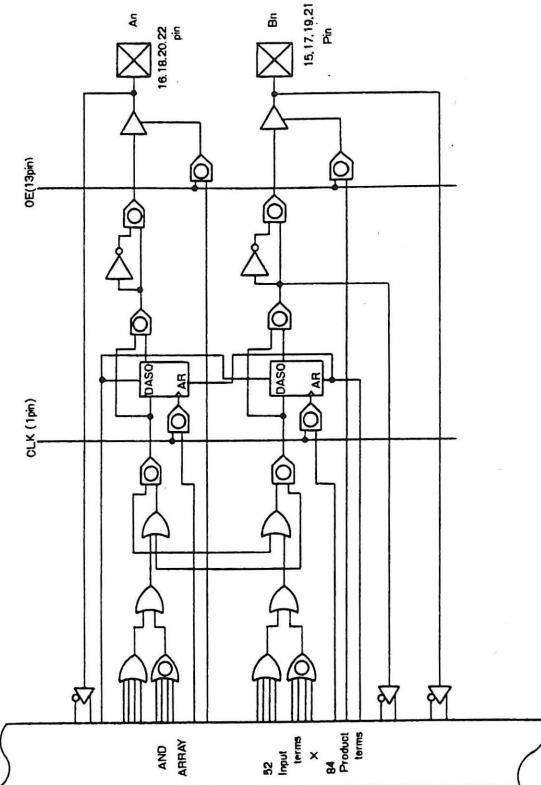

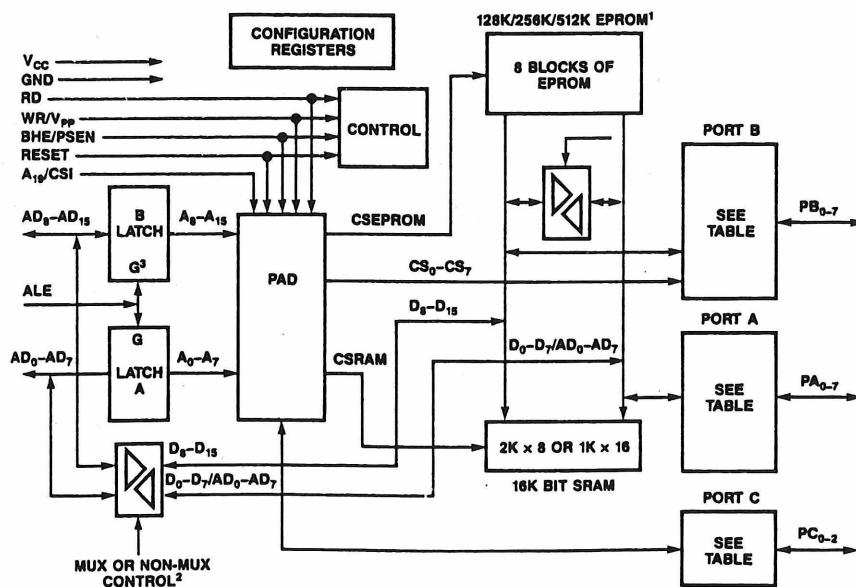

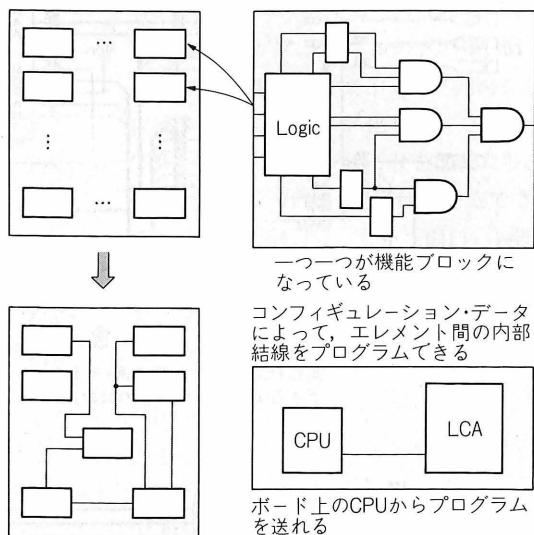

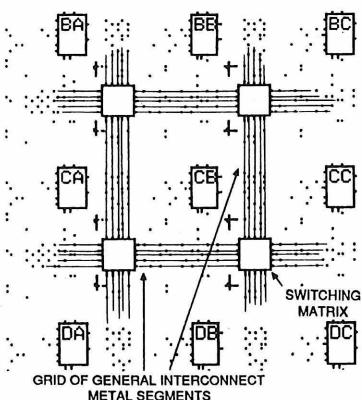

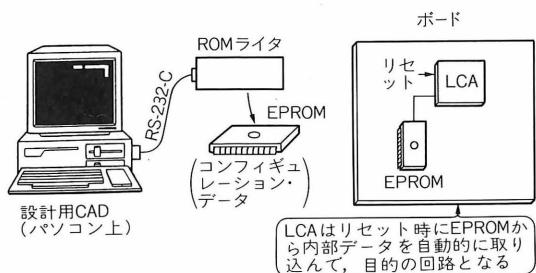

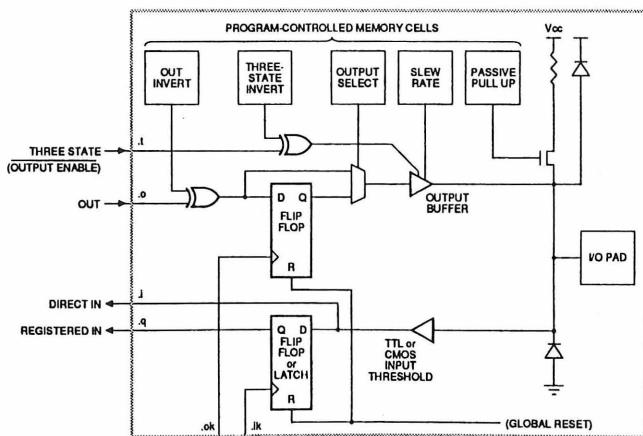

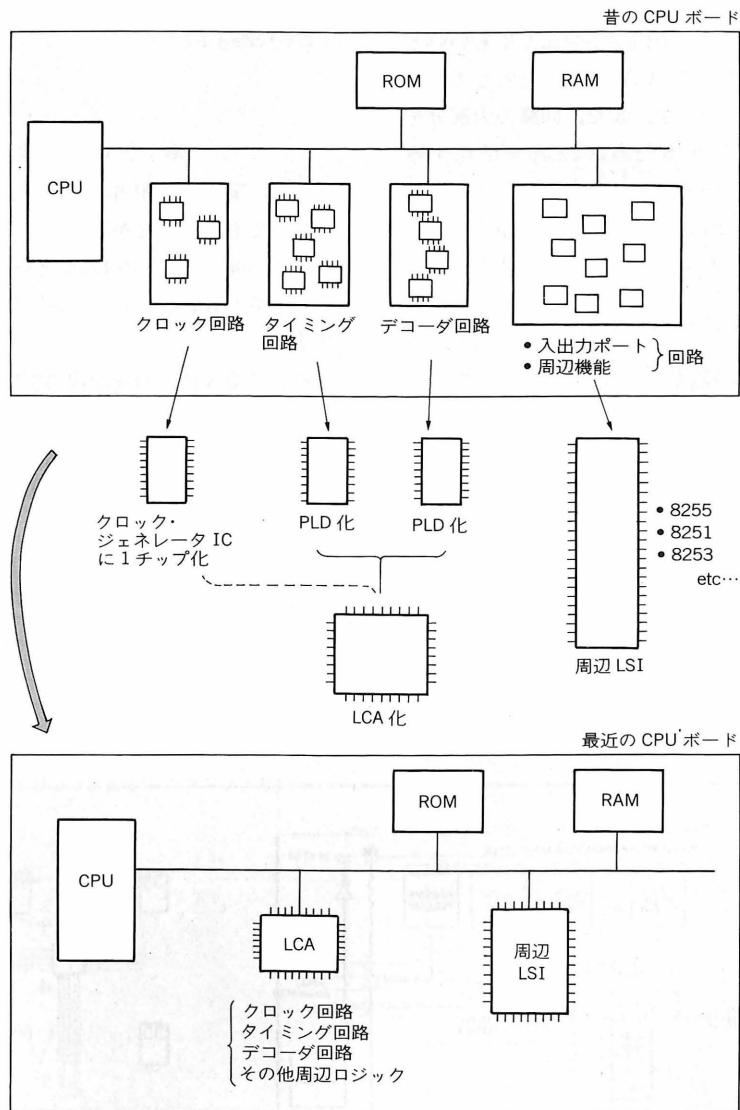

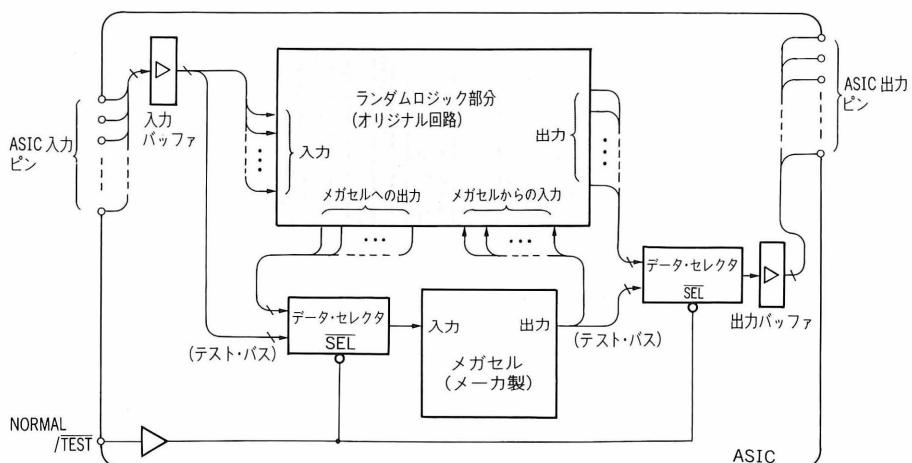

そして、最近のトレンドである **ASIC**(あるいはその前段の **PLD** や **LCA**)。それぞれ<事典>編で詳しく解説があります)に関する技術の場合、ある機能を特定のハードウェアとして実現するために、システム開発者が「ソフト的にハードを設計する」という仕事がメインとなります。たとえば、ちょっとした事務機器の簡単なシステム開発でも、試作ボードに3台のパソコンと1台のICEを接続して、ASIC搭載ボード設計のために数種類のソフトを同時に駆使して作業を進める、といった風景になります。筆者は英語も満足に使いこなせない典型的日本人(?)ですが、ASICがらみのシステム開発のピーク時には、同時に数種類の言語を駆使するバイリンガル技術者に変身します。このメリハリは、初めて見た新人には驚異でしょうが、これから時代、やがて誰もが体験していくことになるでしょう。

また、開発という仕事に対して、たんに目的とされる機能を設計して試作すればおしまい、というイメージしかもっていないとしたら、フレッシュマンの皆さんには考え方を変える必要があります。

一人の人間の頭が同時に考えられる物事の数には限りがありますが、マイコン・システムの場合、もっともシンプルなものでも、部品点数で数10個、LSIの内部に置かれたトランジスタに換算すれば数10万個分の複雑なシステムなのです。ソフトウェアにしても、ちょっとした処理でも何千~何万バイトの機械語の集まりであり、それらのすべてが完璧に「正しく」設計されることは、残念ながらあまり期待できません。そこで、試作段階ではこのミスを追求していくデバッグ作業がつきものとなるのです。つまり、**デバッグをいかにうまく行えるか**、がエンジニアの仕事のひとつのポイント(製品の開発スケジュールや品質を左右する要因)であり、**デバッグとはまさに技術者の腕の見せどころ**、あるいは先輩技術者からあらゆる**ノウハウを吸収する格好の機会**ともなります。

また、これも本来の設計・開発作業としては目立たないものですが、システムの完成度を高めるためのいくつかの重要な技術があります。たとえば、信号線や電源ラインに乗ったノイズによって誤動作しないようにする、あるいは他の電子機器に悪影響を与えないように、所定の電磁放射規制条件をクリアする(一定範囲内に抑える)といった設計技術では、実験のための**データ**

**タ計測技術**も必要となってきます。さらに基板サイズをコンパクト化する実装技術、故障を極力避ける(場合によっては回復する)ための**信頼性技術**なども、一見すると気づかないものですが、プロの仕事としては重要なものです。

### ●試作・まとめ

さて、設計・開発の最終段階を受けて、いよいよ「まとめ」のステップに到達します。ここではまず、ミスを検出する「デバッグ」よりも難しい、正しく動作することを確認するための「**検証**」作業があります。デバッグではエラーを出させてそれを修正していきますが、検証というのは当たり前のはずの動作をチェックするので、ややもすると「完全な検証」の追求が甘くなる可能性があり、デバッグ以上に論理的な作戦を立てる必要があります。

また、開発したシステムがある程度の数量の量産工程にバトンタッチされる場合には、コスト面や量産技術的な検討を加える必要もあります。生産部門への完全な仕様書を用意することや、生産スケジュールの検討・出荷検査仕様書などにも、開発部門がかなり関与します。さらに、ユーザのためのマニュアルの原稿も、小さなプロジェクトの場合には開発スタッフ自身が書くこともあります。この場合、開発の過程でいかにしっかりとメモをまとめておくか、で出来映えも内容も大きく変わってしまいますが、なかなか時間に追われ

た開発の修羅場では、その余裕がないのが実状のようです。

そして最後に、この「まとめ」の段階で重要なのが、設計・開発の途中で得られた技術・ノウハウを、その後の新たなテーマのための財産として整理することです。たとえば、新たに得られた技術は特許の出願という形で将来に備えたり、技術的なノウハウを研究開発レポートとしてまとめることなどです。また、新規に開発したPLDやASICなどのハード、基板やケースなどの技術資料、CPUソフトなどの「ドキュメント」をしっかりと残しておきます。というのも、開発終了後にバグが出た場合とか、将来モデル・チェンジやバージョンアップを検討するような場合には、開発担当者自身であっても「忘れてしまう」ことがほとんどだからです。

「立つ鳥あとを濁さず」といいますが、この「まとめ」段階をしっかりと行う技術者が、長い目で見ると着実に成長するといわれます。終盤のドタバタの中でいつのまにかプロジェクトが終わる、というのがつねですが、若手技術者の皆さんには、ぜひ先輩のお手並みをチェックしてみてください。

このように、「技術者の仕事地図」と簡単にいってもかなりの広がりがあるものです。少しづつ、自分の足元を固めるとともに、ぜひ積極的に自分のフィールドを広げていってほしいと思います。

足を使うことが企画力や技術力を育てる

## 目標技術のステップアップ

### ●目標「技術レベル」のいろいろ

前節の「エンジニアの仕事地図」では、マイコン技術者のいろいろな業務のすがたを眺めるなかで、フレッシュマンが身につけていきたい各種の技術フィールドがあることに触れてきました。そして本節では、イントロダクションのもう一つの試みとして、エンジニアとして獲得していきたい技術(の段階)を、全体として別の視点からまとめてみたいと思います。

まず最初には、本書の全体にわたって重要なポイントとなっている「トレードオフ」技術のなかで、もっとも基本的な三つのトレードオフについて考えます。そしてつぎに、とくにフレッシュマンが基礎として身に付けていく「ハードウェア技術」、「ソフトウェア技術」のステップアップについて概観して、*<事典>*編の「基礎技術」の解説へつながっていきます。さらに、プロのエンジニアとなっていくためのポイント技術として、

- (1) 開発ツールの活用技術

- (2) デバッグ技術

- (3) モデリング技術

- (4) スケジューリング技術

という四つの技術について、「マイコン技術者のステップアップ」という視点から考えていきます。

もちろん、まだまだ他にも重要な技術はありますが、これらはエンジニアとしての経験からしだいに身に付いてくる(スキルアップしていく)，総合的な技術力の

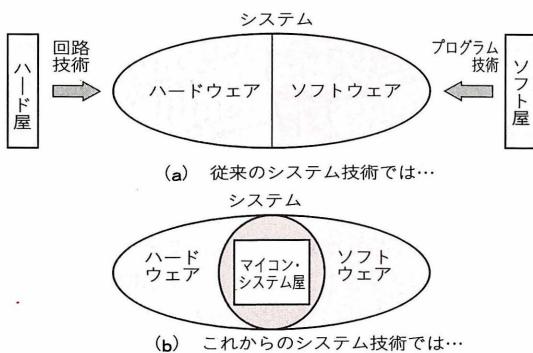

〔図0.3〕 ハードとソフトのトレードオフ

いろいろな側面なのです。したがって、いきなり全部を理解しようとする必要はありません。フレッシュマンが技術レベルをステップアップしていくにあたって、ポイントとなる「柔軟な視点」を紹介していると理解してください。

### ●ソフトとハードのトレードオフ

それでは、マイコン技術者にとっての重要なポイントとして、筆者の持論である「三つのトレードオフ技術」をあげていきましょう。これは、フレッシュマンの皆さんのが今後マイコン・システムについて考えていく上で、ときどき頭に置いて周囲を見なおしてほしい視点、ということになります。キーワードは「トレードオフ」、つまり技術者があらゆる場面で遭遇する、政策的・技術的な判断に関するものです。

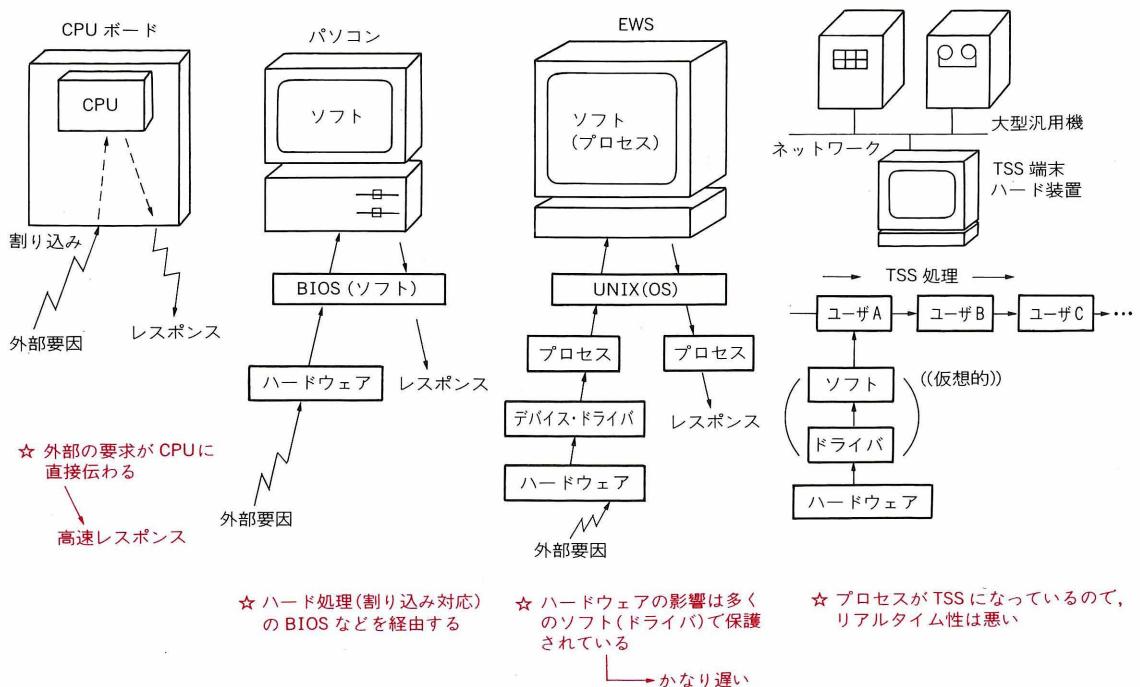

第1のトレードオフは、「**ソフトとハードのトレードオフ**」です。図0.3のように、エレクトロニクスに関するシステムでは、昔は「回路を設計するハード屋」と「プログラムを作るソフト屋」という、二つの人種がありました。ところが、マイコン・システムの一般化と、システム開発を支援する環境の進歩から、ハードもソフトもカバーするような、いわば「マイコン・システム屋」という技術者が中心となって活躍する時代になりました。つまり、この部分はハード屋の仕事だとか、この問題はソフト屋の領分だ、というような考え方が通用しなくなってきたのです。そこで、システムを設計・開発していくエンジニアの重要なセンスとして、システムの機能のどの部分をハード化し、どの部分をソフトとして実現するか、という判断が大切になってきたのです。このトレードオフはクイズではありませんから、正解が一つとはかぎりません。技術者ごとに、ノウハウのレベルごとに判断が異なりうるので、それだけに「技術者の腕の見せどころ」ともなるのです。

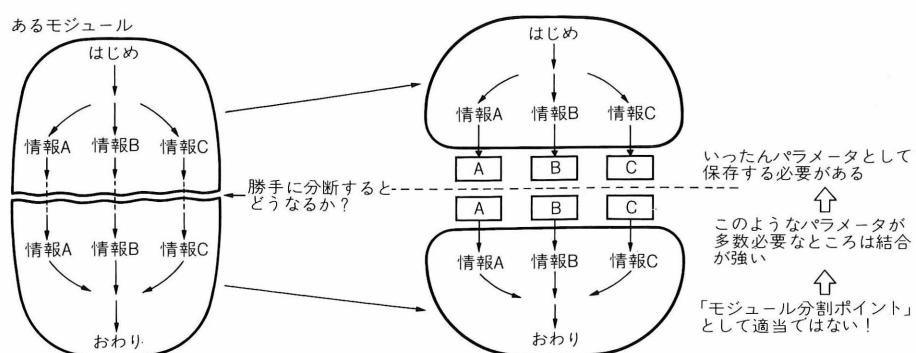

### ●階層化のトレードオフ

第2のトレードオフは、「**階層化のトレードオフ**」です。半導体の集積度の進歩、あるいはコンピュータ・パワーの向上によって、現代のマイコン・システムというものは、細部まで眺めていると全体を把握しきれないほど、複雑・巨大なシステムとなっています。そこで必要となるのが、システムをいくつかの階層に分割して考える、という階層化の発想です。図0.4や図0.5のように、ハードにしてもソフトにしても、ある階層

から下はブラックボックスとして簡略化(部品化)する、という階層化によって、システムがわかりやすくなり、開発効率や信頼性も高くなるのです。ただし、この階層化の判断を誤ると、かえって複雑になって逆効果となったりします。階層の分割は「分割された階層間の適切な情報交換」の設計が必要ですから、ここでもノウハウ的な経験の蓄積が重要になります。

### ●コスト/スペック/スケジュール

第3のトレードオフは、「コスト/スペック/スケジュールのトレードオフ」です。二つでなく三つの要因がからんでいるために、おそらく世の中の大部分の技術者がこの点で悩んでいる、と筆者も確信をもっているポイントです。

コストはもちろん費用ですが、これは製造コスト・部品原価だけでなく、開発(イニシャル)コストや人的(ランニング)コスト、あるいは知的所有権の将来的コスト、といった面もあります。もちろん基本的には「安いほどいい」のですが、残り2点とは相反する要因です。

スペックとは「仕様」のこと、システムの機能・能力・性能などと考えることができます。あきらかに、スペックを追求することはコストとスケジュールを圧迫することになります。

そしてスケジュールとは文字通りのものですが、技術者が一人で何もかも担当しているのでなければ、「他の関係の調整」という、なかなかやっかいな要因となります。当然、スケジュールの制限は他の二つの要因を制限してしまいます。このトレードオフをうまく解決できるようになることこそ、ベテラン技術者への登龍門だと思います。

### ●ハードウェア技術の基礎ステップ

ここでは、マイコン・システムのハードウェア技術について、フレッシュマンがステップアップしていくための指針を考えていくことにします。なお、具体的な技術項目や具体的な課題例については、このあとのがく事典>編で詳しく述べていますから、ここでは「概論」ということになります。まったくの新人でもなければ当然すぎることばかりですが、たとえば「新人研修のときにこのポイントを確認させよう」というような使い方にも役立つものとして、あえて基礎の基礎から列記してあります。

まず最初のステップは、「基礎的な技術情報を身につける」ことです。算数から数学に進むためには九九や加減乗除を知らなければならないように、基本的な用語、各種部品の知識、ハンダ付けの技能(ソフト屋でも必須)、データブックの引き方(「このICはあの本で調べる」という情報)、回路図の約束事、カラー・コードやテストの使い方、などは最低限身につけたいことです。

つぎのステップは、たとえば先輩から与えられた実験回路とか、製品の回路図、本に載っている回路図などを「読める」ようになることをめざしましょう。個々の部品の名前を当てるのではなくて、全体としてどこで何をやっているか(おおよその動作)が感覚としてわかる、ということです。これには、周囲の先輩をつかまえて質問攻めにするのが最適の方法です。

そのつぎには、正しく動くかどうかは別として、「自分で回路を設計してみる」ことです。ディジタル回路の実験というのは、間違えてもICから火や煙が出るくらいで、それほど人命に関わるような事故にはなりません。とにかくある機能(時計でもチャイムでも)を

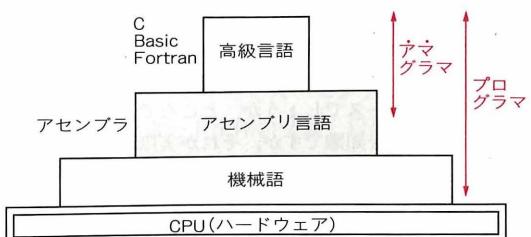

〔図0.4〕 ハードウェアの階層

〔図0.5〕 プログラム言語の階層

自分の頭で実現しようと努力してみると、欠けている知識を痛感できます。そして、設計した回路を実際に手で作って、テストやオシロなどを使いながら、動くところまで追求することが大切です。これによって「デバッグ」という技術の意味を理解することができます。

そして、この先にあるのは、もう実戦の世界となります。いきなり本番の仕事を全部任されるというよりは、たとえばチーム・リーダーから一部の仕事をアシスタントとして与えられるわけですが、それでも立派なプロの仕事です。自分なりに精一杯工夫して、限られた条件の中で最高の性能をめざしてみましょう。実戦での試行錯誤の繰り返しそそ、スキルアップの最大の教師です。失敗を恐れることはできません。若手の失

敗の可能性をちゃんとカバーしてくれているのが、先輩の技量だと思いましょう。

### ●ソフトウェア技術

つぎに、ソフトウェア技術のポイントについて考えてみましょう。すでに述べたように、ソフトとハードの両方について「自分のものにする」のがマイコン技術者にとっての基本的な目的ですから、どちらか一方でなく、ともに積極的にアプローチします。

まず最初のステップは、とにかく「コンピュータに慣れる」ことです(ファミコン世代のフレッシュマンにとって、「コンピュータ・アレルギー」の心配は不要でしょうか)。いろいろな理屈とか知識はさておいて、と

## [コラム]

# マイコン技術者の徒弟制度

「職人」が製品を生み出していた昔、若者は親方のところに弟子入りして、手とり足とりに技術を教えてもらいました。もっとも親方衆も頑固親父が多くて、「師匠の技を盗む」のがふつうでした。デザイン・道具・材料・製作技法などのあらゆるノウハウは、親方から弟子に無形のものとして継承され、この徒弟制度は日本ばかりではなく、たとえばヨーロッパの優れた工芸技術などでもまだ基本となっているようです。

さて、ところでエレクトロニクス技術とかコンピュータ技術の世界ではどうでしょうか。テクノロジーの進歩があまりにすさまじく、親方の技術レベルは弟子の世代の技術としては「過去の遺物」になってしまう世界のことです。徒弟制度などという言葉は無縁のものだ、と思われるでしょうか。筆者の感想ですが、なかなかどうして、この世界でも先輩の存在は非常に重要なものだ、とつくづく思うことばかりなのです。マイコン時代の徒弟制度、というのも、けっこう大切な視点のように思います。

### ●新人の伸びを左右する OJT と上司

まず、誰でも「新人」のときがあり、はじめてこの世界に触れる時期があります。新入社員研修とか、新人研修講座、さらにOJT(On the Job Training)と続くのが一般的なコースでしょうか。ところで、「研修」で習うのはいろいろな知識ですが、それが実際にフレッシュマンの技術として理解され、さらに利用できるように身についてくるのは、明らかにOJT以降のことでしょう。そ

の際に先生となるのはそれぞれの職場の先輩で、まさにこの「師匠」のデキ次第で、その新人の伸びが左右されてしまうのです。

\*

筆者の経験でも、新人のときのチームの先輩には大変に感謝しています。些細なこと、同じこと、単純なこと、とんでもないこと、とにかく「臆せず質問する」ウルサイ新人だったあのころ、よく付き合っていただいたものだ、と思い出すだけで恥ずかしくなります。相当に先輩の仕事の邪魔をしていたのだと、やっと分かってくる頃には、やがて自分が新人の面倒を見るようになります。筆者にとって、あのころの先輩はまさに「一生の師匠」のように思えます。

\*

また、職場の上司も大切な「師匠」でした。技術の現場から次第に離れてマネジメント中心の中間管理職となつても、新しいツールを買ってくれとか、勉強のために学会に行きたいとか、この書籍は面白そうだから参考に買いたいとか、仕事に直結しない要求をいろいろ叶えてくれました。実際のコンピュータ技術としては時代から遅れてしまがちなため、オフタイムに解説本を一生懸命に読んで話題を理解しようとしている努力の姿勢も、若手への刺激となりました。

\*

そして実際に仕事を始めてみると、自分のチームの先輩だけでなく、他のセクションの技術者もまた、いろいろなヒントや知恵を与えてくれました。バグに悩まされ

にかくソフトウェアという概念に慣れてしまうのが、なんといっても先決なのです。「文系」の人であっても、ソフトについてはハンデはありませんから、自信をもってアタックしてください。たとえば、言語はBasicでテーマは「3日で何かゲーム1本を作ること」というと、なんだか遊んでいるみたいですが、これが立派な新人研修になります(実績は保証済みです)。

先輩技術者が特定のプログラミング言語のプロであると、その言語ばかりに限定されてしまうかもしれません、できればいろいろな種類の言語、いろいろな種類のソフトウェア環境を(つまり食いでも)体験したいところです。インターフェースで遊んだらつぎはコンパイラ、そのつぎにはアセンブラー…という貪欲さを期待

ている本人が気付かない単純なミスを、通りかかって一瞥するだけで指摘して立ち去ってしまう先輩が神様のように思えたり、ノイズ対策で悩んでいると、アナログに強い古参の先輩が画期的な解決策を授けてくれたり、といった経験は数多くありました。教科書に書かれていらないこれらのノウハウを先輩から吸収すること、これはまさに徒弟制度そのもののプラス面だったと思います。

### ●「態度で示す」のが最高の教育

そして、新人もやがて中堅技術者に、さらに新人を教育する立場の「先輩」になっていきます。とても自分にはあの先輩のような立派な教育はできそうもない、とは思いながら、それでもメニューを作って実習させて、質問があれば仕事の手を休めてなるべく答え、そして何より、「態度で示す」雰囲気を自分にいい聞かせることに努める日々となるのです。先輩である自分自身が、本当に心からエンジニア生活をエンジョイしていれば、それが最大の教育であるように思います。技術者として自分を向上させることの喜び、新しい技術を自分のモノにして、さらにそれを具体的に世に出すことの面白さと手応え、そういう楽しさを、なるべく言葉に出さずに伝えたい、と思うようになりました。

\*

技術者というと、エンジニアとしての自分の腕次第とか、実力の勝負というクールな面ばかりが強調されてしまいますが。しかし、エンジニアとしての自分が現在あるのは、多くの先輩(師匠)のお陰なのだ、と理解するところまでは、ようやく分かってきたところです。会社との関係はある意味でギブ・アンド・テイクですが、先輩からはテイクばかりの日々でした。このノウハウなり喜びを若手に惜しみなくギブしていくことで、やっと先輩への感謝をはたせるのだろう、と思っています。

したいのです。まずは実際にソフトを体験するうちに、プログラミングのテクニックとか、ソフトウェア工学の理論的な勉強、というのも次第に気になってくることでしょう。

ソフトそのものに慣れるには、ハードウェアの心配のいらない(環境として提供される)パソコン上で実験するのがいちばんです。そしてたんなるプログラマのパソコン少年で終わらないためには、拡張スロットのボードで積極的に外界とインターフェースしてみたり、さらにはボード・マイコンという製品を使って、ボード上のCPUプログラムを作る実験に進みます。その先になると、ハードとの両輪になりますが、自作のCPU基板に自分のソフトを走らせる、という目標に向かってトライすることになります。たとえばLEDが1秒ごとに点滅する、というだけの簡単な動作であっても、それがオリジナルのCPUボードでコントロールできたとすれば、かなりのレベルといえます。

そしてプロのマイコン技術者と、アマチュアが一線を画すのが、「厳しい条件をソフトで解決する」、「信頼性の高いソフトウェア」といった点です。求められる機能仕様をハードを追加せずに、割り込みとかマルチタスクとか自作モニタによって、なんとかソフト的に実現したり、あるいはソフト的な誤動作対策の追求に悩まされるといった経験が、結果として新人を大きく成長させるのです。

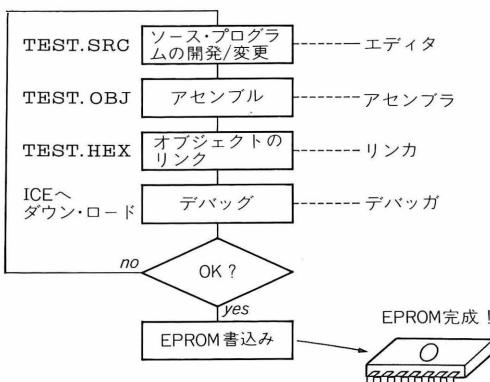

### ●開発ツールの活用技術

技術者に「ツール」はつきものですが、マイコン技術者の場合には、仕事がハードからソフトまで、あるいはデジタルからアナログまで(時間スケールでいえばナノ秒オーダーからマイクロ秒、ミリ秒を経て秒、分、時間のオーダーまで)の領域にわたっていますから、関連するツールも多種多様です。ステップアップの指標としては、「**各種ツールを理解して、適切に活用できる**」という状態が明確な目標となります。

昔の「街の電気屋さん」というのは、テスタとハンダごてがあれば、たいていの家電製品を修理できたのですが、これは完全に過去の話となりました。現在では大手電気メーカーのサービス・センタであっても、修理とは「CPUボード全体の交換」以外に方法がない、という状態になっています。テスタどころかシンクロスコープがあっても、動作がデジタルであれば見当がつかないわけです。各種の計測器を含めて、高価な

開発ツールをいろいろ使うことは、プロの技術者のスタート・ラインとなります。

ハードウェアでは、**テスタ**で直流的(静的)に計測できるのは「ショートのチェック」程度で、**オシロやシンクロ**、または**ロジック・アナライザ**によるデジタルの計測は常識となります。扱う信号によっては、**ストレージ・スコープ**とか**FFT アナライザ**といった装置も必要になりますが、機器の使い方の背景にある、信号そのものの物理的な理論を理解することも重要です。

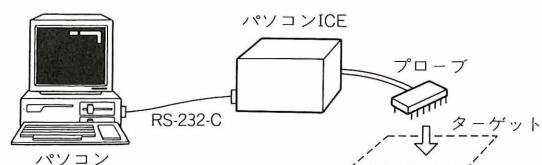

CPU 関係ツールの本命は**ICE**(イン・サーキット・エミュレータ)，通信関係のツールならば**プロトコル・アナライザ**、ということになるのですが、場合によっては「使い慣れた CPU ボードを使って、必要な計測装置を作ってしまう」という姿勢が重要です。

ソフトウェア開発のツールは、なんといってもパソコンの機動力です。ソフト開発の場合には、パソコン→ICE というレールが決まっていますが、同じ開発環境を使っても、ベテランと新人とではツールの活用度が違いますから、フレッシュマンは先輩の「技」をよくチェックしましょう。また、ハードのツールを自作することが重要な経験となるように、いつも ICE に頼るばかりでなくして、対象の程度によってはあえて ICE を使わずに、**デバッグ・モニタ**を自作してシステムに内蔵し、その環境でソフト開発を行ってみる、というような挑戦もいいことです。

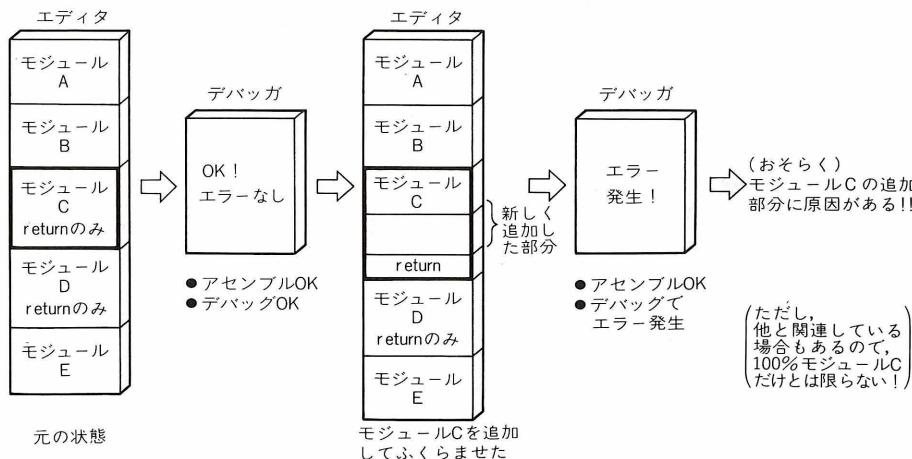

## ●デバッグ技術

デバッグとは、システムのバグ(問題点)を追求し解決する、地味な作業です。当然のことですが、最初から原因の明らかなバグなどありません(わかっていないれば対策する!)から、フレッシュマンにとっては困惑するばかりかもしれません。正しく設計して正しく試作したはずの基板が、どうして動かないのか、という気持ちです。

しかし、ちょっと慣れてくると、「**バグは必ずあるもの**」という真理を納得するようになります。中堅エンジニアともなると、試作基板にいきなり電源を入れたりはしませんが、その背景にはこんな悟りの境地があるのです。そして、いざバグに遭遇したら、過去の経験を総動員して、あらゆる視点から原因の可能性を追求します。適切なツールを活用したり、デバッグ用のハードやデバッグ用のルーチンを、(場合によっては設

計の当初から)わざわざ作ることで「急がば回れ」を実践します。

実際の対象によって千差万別なため、なかなか図式的な「デバッグ技術」という教科書がない(工学的な理論は議論されている)のですが、ある意味でデバッグというのは、技術者の能力をフルに發揮する場です。ひとことでいえば「**経験とともに成長するのがデバッグ技術**」ということになります。筆者の場合は、バグやトラブルに直面すると、自分の力を試すいいチャンスだと思って楽しんでしまうこともあります。

## ●モデリング技術

マイコン・システムを設計・開発する際に、情報の解釈・データの形式・ソフトの動作などに、なんらかの「数学的」、「物理的」モデルを使うことがあります。たとえば、地上の重力の影響をプログラムで考慮するとか、2次元の平面ディスプレイで3次元的な立体図形を表示するための座標変換処理、最近の流行ではバーチャル・リアリティ(仮想現実感)中の「世界モデル」などです。

この「モデリング技術」のようなテクニックは、マイコン・システムのハードやソフトの技術の獲得とはすこし異なるものです。つまり、自然界とか人間の感覚をシステム上でいかにモデリングするか、という技術は、着目するアイデアの部分は本人次第ですが、正しく表現するためには、しっかりととした理論的手法にしたがう必要があるのです。たいていのモデルは高校の数学程度の範囲で記述できるもので、筆者もよく物理や数学の教科書を開いて調べたことがあります。

モデリング技術を向上させるためには、日頃から周囲の現象を「マイコン・システムで表現するにはどうしたらいいか」といった視点で眺める、という姿勢が大切です。また、モデリングの実例を、いろいろな文献や論文で調べたり、実際にパソコンのソフトなどで実験してみることも有効です。

モデリングを考えているうちに、高校の授業で習った物理法則や数学公式の意味があらためて理解できた、などという経験はけっこう楽しいものです。

ここでモデリングのコツというか、ヒントを指摘しておくとすれば、自然界は「線形性」に支配されている、という物理学の大原則が大切な視点です。線形性、つまり比例関係によって力学的な微分方程式を記述すると、そこから自然に「重力加速度」、「単振動」、「時

定数の指数関数的特性(→共振回路の減衰振動)」などが出てくるわけで、これらの関数というのはけして数学のための作的なものではないのです。興味のある人は、ちょっと考えてみてください。

### ●スケジューリング技術

トレードオフの話題のところでも述べましたが、マイコン技術とはちょっと異質のポイントとして、「**開発作業の進め方**」に関する、スケジュールとかチームプレイ、といった視点があります。スケジューリング技術、あるいは進んでいくと「**プロジェクト管理**」の技術として重要なノウハウです。この章は「概論」ということで、これ以上の深入りはしませんが、スキルアップの後半戦では主役となる技術なので、頭の片隅に置いてみてください。職場の上司がたんに「管理職(マネジメント)」として技術の現場から離れているようでも、じつはこのスケジューリング技術を駆使している、その裏には、しっかりとした技術が存在していることに気づくかもしれません(p.127のコラム参照)。

### ●「技術者の創造性」とは

さて、ここまで技術というのは、どちらかというと「与えられる」スキルアップについてのものでした。

ところでマイコン技術者は、世の中に新しいシステムを送り出すのですから、そこにはオリジナリティ、つまり「**独創性**」「**創造性**」が求められていくことになります。まったく同じテーマを与えられても、エンジニアごとに生み出すシステムは異なりますし、同じ技術者でも成長していくにつれて、以前とは違う(より美しい)システムを思いつくはずです。

この技術者の創造性というのは、いつまでも尽きない課題なのですが、残念ながら筆者もここで系統的に意見を述べることはできません。まだ現在進行形で模索しているところで、これからも皆さんと共有する「宿題」ということになるようです。フレッシュマンがスキルアップを考えるときには、最後にはこの創造性の勝負となる、つまり先輩から「与えられる」技術でなく、自分自身の技術としてどこかで一人立ちしていくのだ、ということをしっかりと心がけていってほしいと思います。

エレクトロニクスとかコンピュータといえば、ハイテクが際限なく進んでいる世界のようですが、逆にいえば**自分の技術を自由に展開できる空間が広がっている**、という楽しみのある世界なのです。自分の可能性を信じて、少しずつ着実に、そしてときには大胆にチャレンジしていきましょう。

## 【飛び石コラム】 おすすめ BOOKS ①

### ●心の社会

M. ミンスキー 著 安西祐一郎 訳

産業図書

人工知能・認知科学の分野で世界中に翻訳され、古典的名著になろうとしている本です。人間の脳の中での働きについて、非常に多数の処理単位(エージェント)が別個に、かつ共同して複雑な仕事を実現している、というような考え方で、現在のニューラル・ネットワークとか、超並列コンピュータを考える際のヒントを与えてくれます。

### ●超マシン誕生——コンピュータ野郎たちの540日

トレイシー・キダー 著 風間禎三郎 訳

ダイヤモンド社

コンピュータ黎明期の、夢とパワーあふれる若者たち

のチャレンジ物語として、一気に読ませてしまう本です。内容はデータゼネラル社のスーパーミニコン開発という、ちょっと前の時代ですが、エンジニア・スピリットを見事に伝えています。日本のこの手の「成功物語」が、なぜか企業の提灯持ち記事になる場合が多いのとは対照的です。

### ●aha! —ひらめき思考(別冊サイエンス)

マーチン・ガードナー 著 島田一男 訳

日本経済新聞社

世の中にパズルの本は数多くありますが、そんな中でもとびきりのパズル集として楽しめ、さらにコンピュータ技術者の「発想法トレーニング」としても重宝できる本です。著者が指摘するように、コンピュータ時代になると、問題を「計算して解く」部分は機械に任せて、人間の思考(ひらめき)がより重要になってくるのです。

# [Appendix] ある「技術勉強会」のメニュー

以下のメモは、ある中堅エンジニアが何年か前に、若手技術者を対象に開催した技術「勉強会」での、「概論」の講演のための資料です。

いわゆる「研修会」というのは、上司から指示されて「仕事」として参加するものですが、この勉強会では、本人の自発的な参加希望を条件としました。そのため、ただ受け身で聞くばかりではなく、全員に事前に課題を与えて、毎回の冒頭に交代で発表させ、さらに最終レポート(または新規の特許出願)の提出を全員に義務づけました。具体的な実務に関するテーマでは、講師として中堅の技術者がそれぞれ各技術分野を深く解説ましたが、これは「講師」自身のプレゼンテーション研修でもありました。

ここに紹介するのは、冒頭3回分の一般的「概論」の一部(業界の具体的な事項に関する部分は<省略>扱い)ですが、エンジニアの姿勢、ハードウェアの概要、ソフトウェアの概要などを広く展望しています。

## -----[勉強会・総論] -----

### (1) イントロダクション

#### A. この勉強会の目的について

- 若手の実力アップが求められている

当社の開発部門の歴史：結果を待ちきれない体质

年寄りの発想とは技術レベルが別になりつつある

- 「講習会」でなく「勉強会」であることの重要性

受け身では成長しない

自分を変えられるか？

自分の意見を持ち・主張すること

- たんなる専門馬鹿ではダメになる

ハード屋もソフト屋も長続きしない

(技術とは進歩するもの：個々の人間の進歩のほう

が遅い)

当社の客観的な技術レベルは低いという認識

当社は社員を成長させるのは下手→自分でやる！

(アメリカ：「引き抜き」されない技術者に問題あり)

- 一点豪華主義のプロとなるためのネタを捜す

研究者・学者を越えてもよい

「この分野ならおまかせ」は武器となる

趣味嗜好の多様化時代：自分の趣味に仕事を引き込む

- 特許を書くのは技術者の仕事

ワープロの活用：活字・コピー・書き直し

論理思考のトレーニング

アイデアだけでよい

出願補助金は給料が安い技術職の合法的アルバイト

レポート・報告書・図面も手書きの時代ではない

#### B. 「いまやってみること——いくらでもある！」という話

- コンピュータを知らないで平気な技術者は去るべし

パソコン・アレルギーは論外

Basic でゲームを作る

C に触ってみる

Prolog/Lisp/Smalltalk とか…

アセンブラーでツールを作る

パソコン・EWSなどの一般情報を知っているか

ミニコン・Unix

- 日常業務の間隙を活用する

実験室は部品の宝庫：こつこつと電子工作

ソフトが走る合間の読書：会社の書籍をフル活用する

(定期購読誌・バックナンバー・書庫の文献)

暇を見つけてゲーム・ソフトを作る

こつこつとオリジナル装置を製作する

他社製品の分解・解析

メーカである会社の名前は案外に重い→活用するべき

(資料請求・サンプル評価)

- 会社は向上への投資を惜しまない

(日々向上しないのは技術者が無能である証明)

英会話の能力があればバリバリ海外へ行ける

アンテナを立てて学会・展示会・ショーなどへ出張

勉強のための書籍は会社に買わせる

去年と同じ仕事をしているのは能がない：環境の改善

を考える

(必要性を証明して最新のツールを導入できないか)

大学との共同研究のネタがないか

フェア・市場調査に行きまくる

特別な行動には十分な報告・レポートが条件→やりがいあり！

### (2) <省略>

### (3) [コンピュータ] 側からのアプローチ

#### G. コンピュータとは何なのか

- コンピュータの歴史：本を読めばわかるので省略

ノイマン博士・ENIAC

- PDP・VAX・Sun・NEWS・NeXT

- アップル・IBM PC・Mac・ATARI・NES

- PC80/98・MSX・ファミコン・TOWNS・AX

- ・コンピュータ技術：ハードとソフトの両面からなる

デバイス：真空管・TR・IC・LSI・DSP

大型機・ミニコン・TSS・パソコン・EWS・LAN

ノイマン方式・バッチ・TSS・OS

Fortran・Basic・C・Lisp

構造化・マルチタスク・ウィンドウ・ネットワーク

#### H. <省略>

- I. コンピュータ科学・コンピュータ技術の進歩

- ・パーソナル化・マシンパワーの向上

パソコン→機能強化→かつてのミニコンを凌駕

ソフトの一部をハード化する

(DSP・FFT・ニューロ・ファジイ)

- CPU の機能向上(CISC vs RISC)

- ・通信・ネットワーク化

LAN・ISDN・LA の分散処理化

情報の国際ネットワーク化

- ・マルチメディア化・マン-マシン・インターフェースの向上

AV・双方向・ウィンドウ・マウス・トラックボール

脳波バンドによる入力装置

- ・知識工学・人間工学のはてにあるものは何か

コンピュータ技術も結局は人間に回帰する

#### (4) <省略>

### -----[勉強会・ハードウェア概論] -----

- (1) 当業界の回路方式の歴史=電子回路技術の歴史

<省略>

#### (2) ハードウェア技術のおさらい

#### F. 電子回路の特徴とポイント

- ・受動素子と能動素子

抵抗/コンデンサ/コイル

ダイオード/TR

AC/電池/水晶/LED/LCD

- ・アナログ回路

オペアンプ/コンパレータ

パッシブ・フィルタ/アクティブ・フィルタ

アナログ乗算器

- ・デジタル回路

TTL/CMOS/HS-CMOS

ロジック IC/順序回路→乗算器を設計してみる

ROM/RAM/PAL/LCA

- ・CPU 回路

ソフトウェアで回路を実現する

・アナログ・ディジタルの接点領域

S&H A-D D-A

#### G. さらにプロならば必要な視点

- ・システム設計技術の三つのポイント

ハードウェアとソフトウェアのトレードオフ

階層化の思想

時間スケールに関する視点

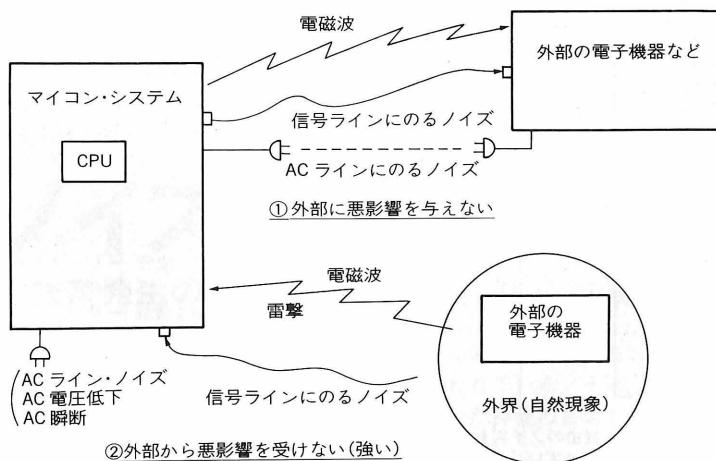

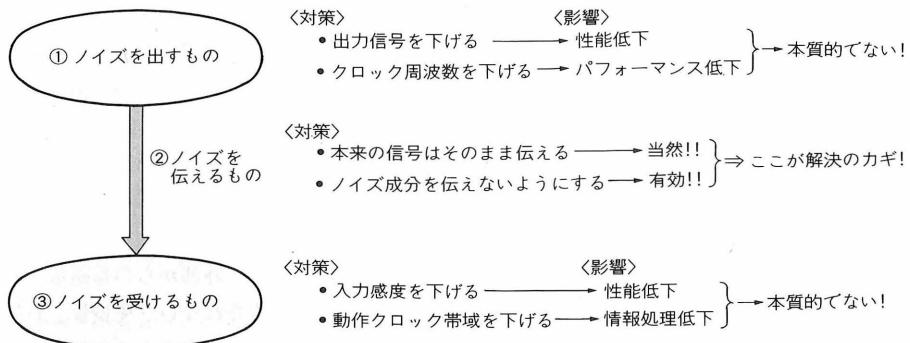

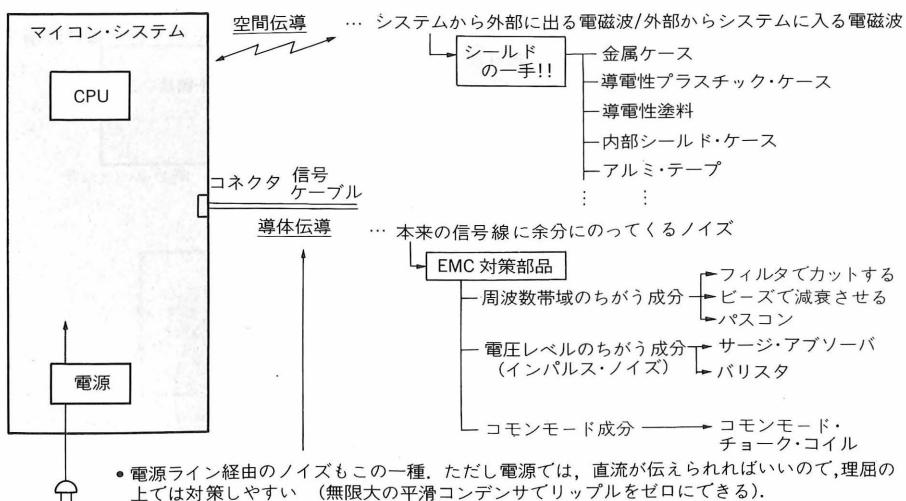

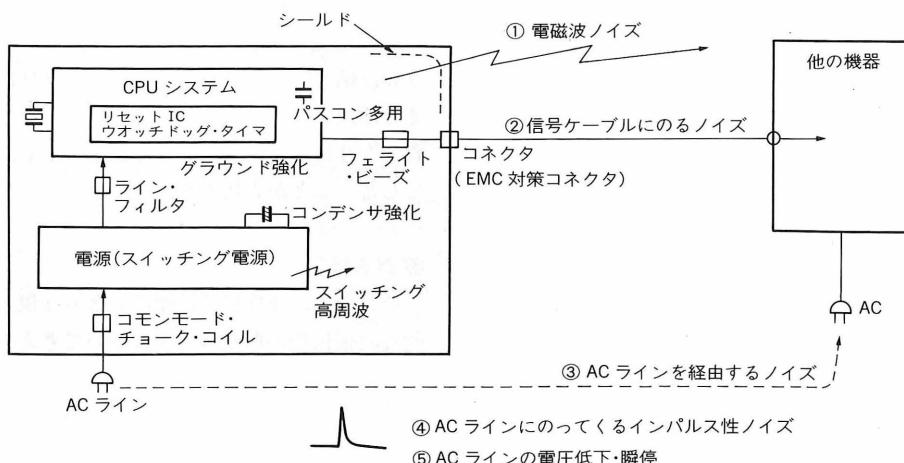

#### ・ノイズ/EMC

停電/電源電圧低下

瞬間停電

AC ライン・ノイズ

静電気

誘導高周波信号

電磁放射

用語: EMC/FCC/マージン

「ノイズを出さないシステムは外からのノイズにも強い」

#### ・信頼性設計

フェイルセーフ

ウォッチドッグ・タイマ

フォールトトレラント・システム

誤動作対策

(ハード・マージン向上/ソフト対策)

修復/対策技術

#### ・テストビリティ/デバッグビリティ

3種類のバグをいかに検出して退治するか

(仕様の不備/開発途上のミス/本当のバグ)

ハードウェアのバグ検出テクニック

(測定器/視点/ソフトがらみ)

デバッグ環境を作り込んでおくのがプロの技

(テスト・ピン/テスト・モード/テスト治具)

#### ・開発のドキュメンテーション技術

企画検討

機能仕様書

基本システム構想

回路設計

ソフト開発

部品表/原価表

テスト/デバッグ記録

特許調査

詳細仕様書

ユーザーズ・マニュアル

サービス・マニュアル

開発レポート

#### ・コスト/スケジュール/特許

仕様 vs コスト

仕様 vs 開発スケジュール(vs コスト)

仕様 vs 特許対策→方式変更もありうる

「全体として最適な方法は何か」という視点

スケジュールは与えられるものではない

### (3) 具体的な回路の設計方法

#### H. アナログ方式

<省略>

#### I. ハイブリッド方式

<省略>

#### J. デジタル方式

<省略>

#### K. システムとしての視点

<省略>

### (4) 専用 LSI の設計方法

#### L. LSI 設計の基礎知識

- ・ディジタル時分割方式

- タイムスライス

- 状態保持レジスタ群

- タイミング設計

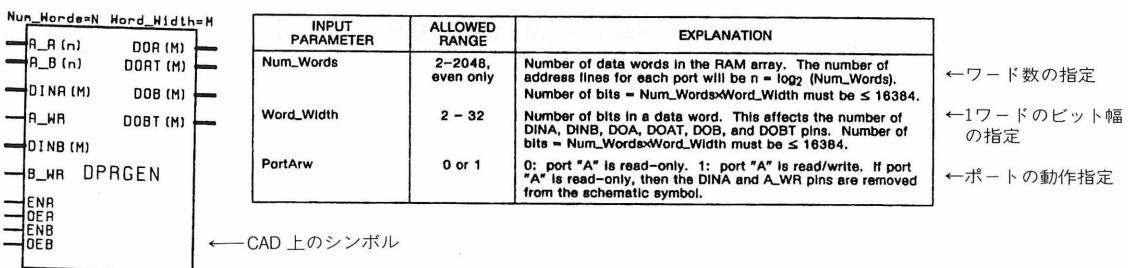

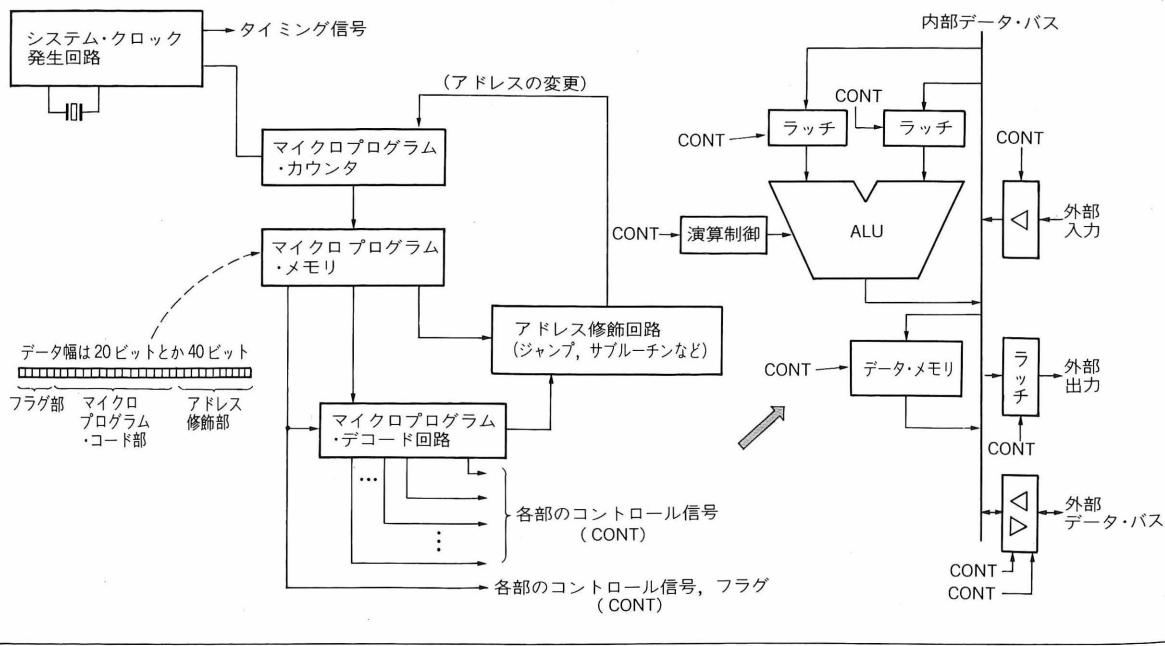

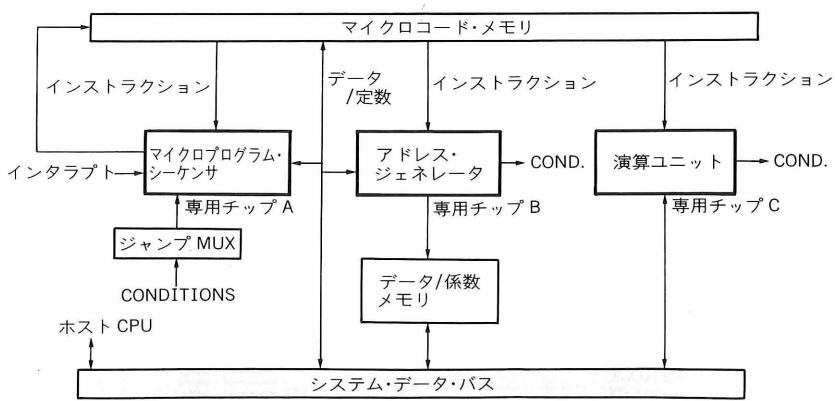

- ・マイクロプログラム方式

- DSP

- 処理制御信号の作り方

- マイクロプログラム・メモリ

- ・LSI の分類

- フルカスタム LSI

- セミカスタム LSI

- (ゲートアレイ/スタンダードセル)

- ユーザ・プログラマブル LSI

- (LCA/大規模 PLD)

- マクロセル/メガセルの登場

- DSP セル/コア CPU の登場: システム・オンチップ

- 重要な視点: 開発費用/開発期間/開発手法

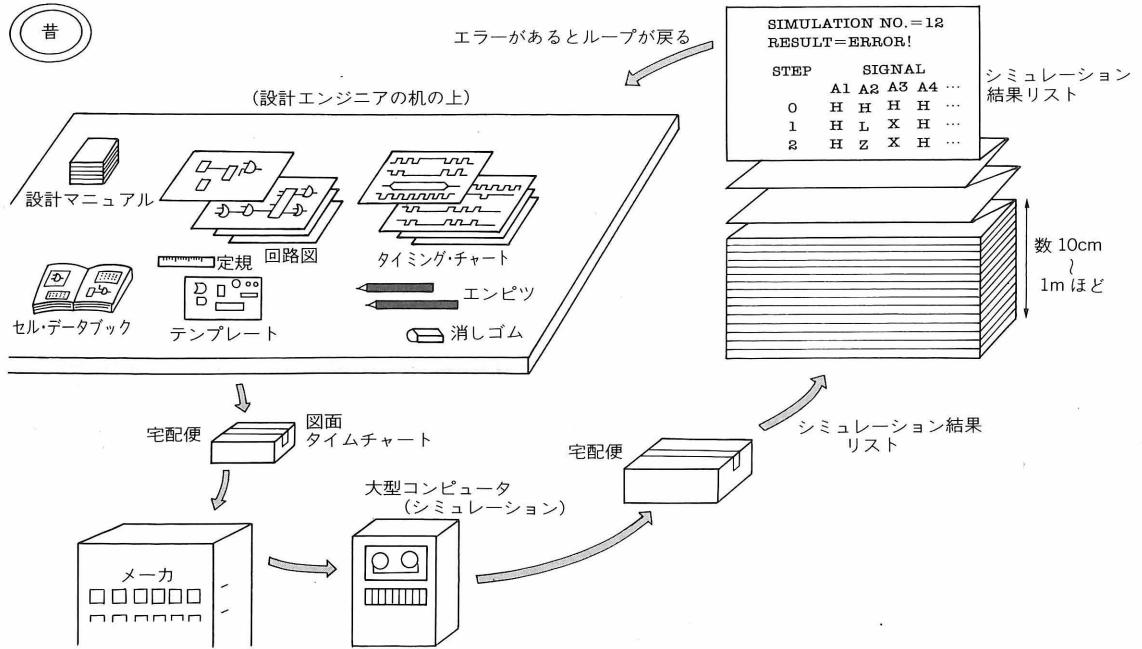

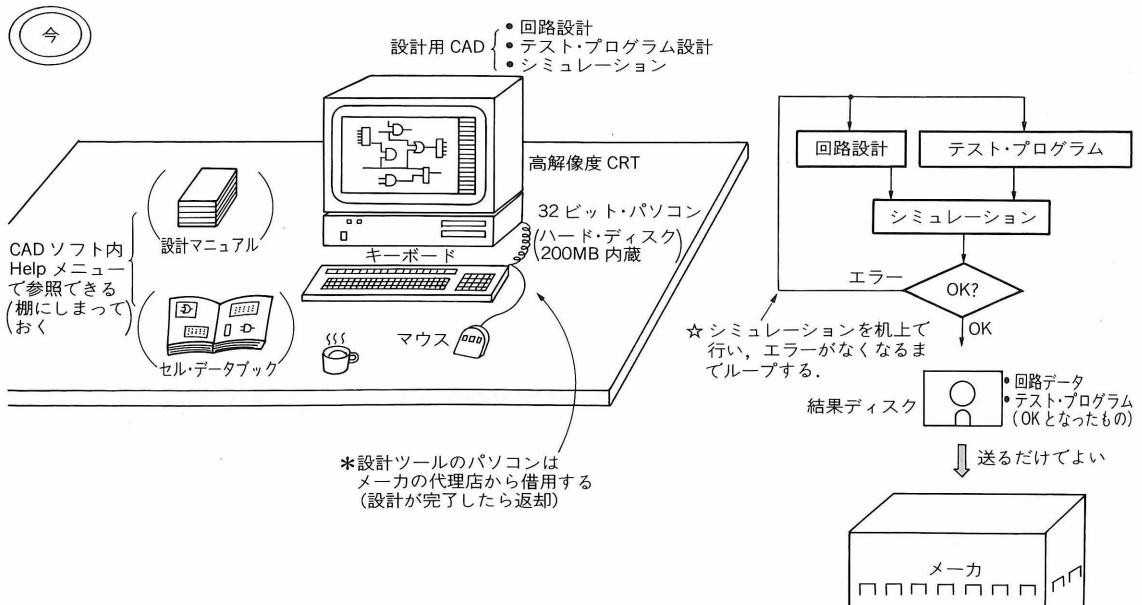

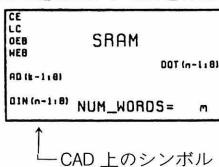

#### M. LSI の設計風景

- ・いにしえの設計手法

- [図面/タイミング・チャート] インターフェース

- 儲かるのは→ NTT と宅急便

- 代理店のデザイン・サポート部隊

- ・回路設計

- システム設計/ブロック分割

- タイミング設計

- CAD ツール

- データ変換/転送

- 重要ポイント: テストを意識した回路設計

- ・テスト・プログラム設計

- テスト・プログラムの意味

- (論理検証/タイミング検証/品質保証)

- テスト・プログラムの諸形式

- (Wave/Vector/Graphic)

- データ変換/転送

- ・シミュレーション

- LSI シミュレーションの種類

- (論理 Sim/仮 Sim/実 Sim)

#### LSI シミュレーションの意味

(ブレッドボード(BB)の代行/回路の検証/テストの検証)

#### N. これからの専用システム開発について

- ・シリコン・コンパイラ化

- LSI 開発環境の統一→製造メーカを自由に選べる

- (デザインハウス/シリコン・ファウンドリの分化)

- 仕様記述のみで LSI 化: シリコン・コンパイラ

- ・評価システム/ソフト開発システム

- ES 評価システムの必要性

- コア CPU: ソフトの同時開発環境が重要

- BB の位置づけ: LCA 化がカギ?

- ・統合シミュレーション・システム

- 今後のツールは EWS!

- 仕様/条件の高級言語による記述

- ハード/ソフトの統合シミュレータ

- 基板 CAD + 3 次元メカ CAD → 自動試作システム

- CASE ツールとの統合

-----[勉強会・ソフトウェア概論] -----

#### (1) コンピュータ/CPU のおさらい

#### A. コンピュータの種類と歴史

- ・メカ式コンピュータ

- 歯車を組み合わせた計算器

- コンピュータは戦争とともに発展(弾道計算)

- ・アナログ・コンピュータ

- 乗算→アナログに向いている(自然界は線形)

- 非線形要素→指数/対数演算器

- ・ワイヤード・ロジック方式コンピュータ

- 膨大な数のリレーによってデジタルを実現

- 速度/信頼性が問題

- ・ノイマン方式コンピュータ

- ストアード・プログラム方式

- 真空管→ TR → IC → LSI → VLSI → ULSI

- 記憶装置の階層化: キャッシュ/バッファ/連想記憶

- ・並列コンピュータ

- CPU を複数並べる: 1 次元/2 次元/3 次元

- 並列処理のための記述言語

- CPU レベル→トランスピュータ

- ・データフロー方式コンピュータ

- 非ノイマン型コンピュータ

- データ駆動方式とは

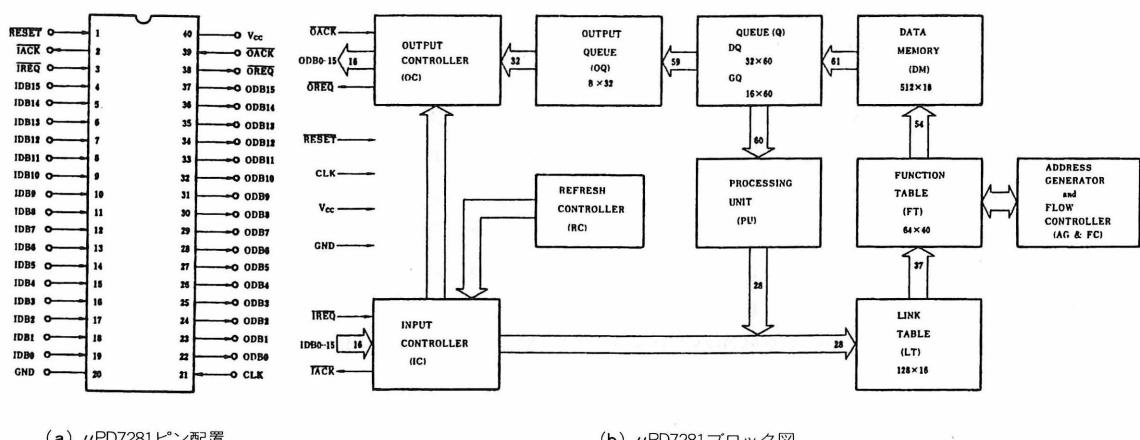

- NEC 画像処理用プロセッサ

- カシオ事務計算用コンピュータ

- ・ニューロ・コンピュータ

- コンピュータと人間の脳

- ニューロの実現方法: ソフト/ハード/バイオ

- ・ファジィ・コンピュータ

- ファジィの実現方法

- (ソフト/メモリ/ハード/バイオ)

- ・光コンピュータ

- 光ファイバの能力

- 光LSIによる光コンピュータ(ニューロも含む)

- ・汎用コンピュータ

- IBMの大型機のような「メインフレーム」

- CPUの能力は巨大→TSS

- 階層性/互換性/信頼性

- (走行を止めずに保守/増設)

- ・スーパ・コンピュータ

- 科学技術計算/シミュレーション

- ベクトル演算/高精度浮動小数点演算

- 専用の言語による最適化

- ・ミニコンピュータ

- DECのPDP→VAX

- LA/FAからCAD/CAM分野

- EWSに押されて消滅の危機

- ・パーソナル・コンピュータ

- 8ビット/16ビット/32ビット

- 本当にパーソナルに普及する仕様とは?

- ・ワークステーション

- 32ビット/64ビットCPU/RISCの活用

- ミニコンの複数端末→1人1台の時代!

- CAD/ソフト開発/CG

- Sun/NEWS/VAX/各社

- ・オフィス・コンピュータ

- IBMは本当に使いやすいのか?

- 「オフコン」→パソコンOA

- ネットワーク化:個々の端末をLANで結ぶ

- ・ファクトリ・コンピュータ

- FAとは(NC→FA)

- 信頼性の条件

- ・ラボラトリ・コンピュータ

- 実験装置の自動制御

- データ収集/処理

- ・ゲーム・コンピュータ

- ゲームウォッチ/LCDゲーム

- ピュウ太/セガ/ファミコン/アタリ

- メガ・ドライブ/PCエンジン/ゲームボーイ

- PC8801/X68000/FMタウンズ

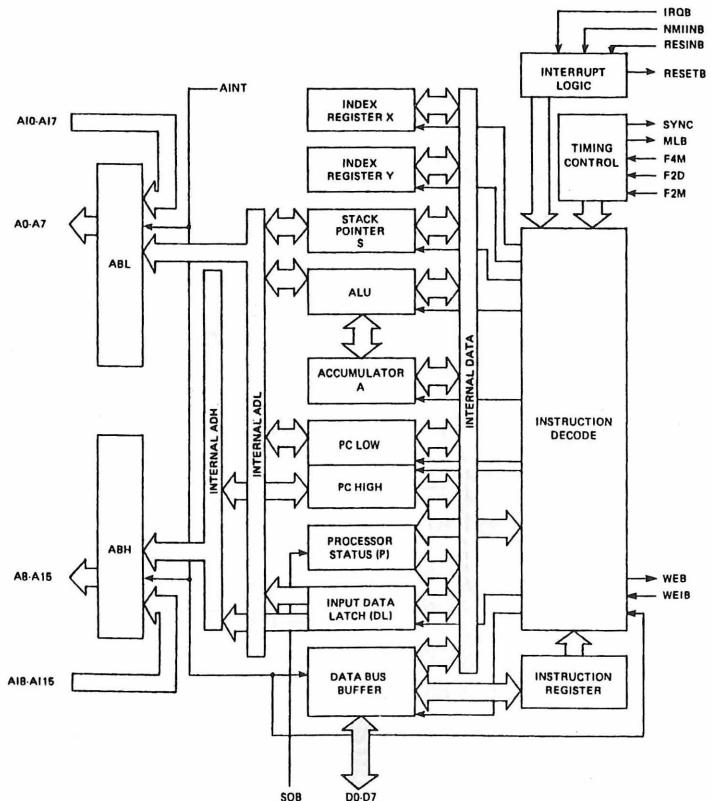

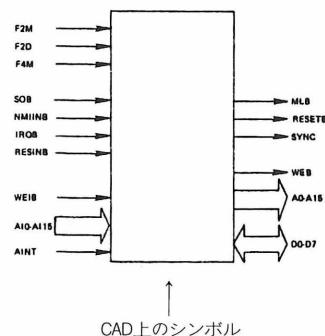

- B. おもなCPUの歴史**

- ・電卓用専用回路→CPUの発想

- 最初のCPUはなんと日本人が作った!

- ・インテル:8080/8085

- 数値計算/データ処理向け

- あまり美しくないアーキテクチャ

- 市場に先に参入してシェアを押さえる

- ・モトローラ:6800/6809

- 制御系に向く

- エンジニア受けする美しいアーキテクチャ

- 6809のOS-9は8ビットなのにマルチタスク

- 後発に泣いた:モトローラの体質

- 「ビッグ・マイナー」CPU

- ・ザイログ:Z80

- 8080のソフト上位互換/改良版

- 8ビットの帝王として君臨

- CP/Mがディスク時代とマッチした

- 「リトル・ジャー」CPU

- 周辺LSIファミリは不振

- ・ロックウェル:6502

- アップル・コンピュータのオープン・アーキテクチャに

- のる

- ファミコンの心臓部

- 小さいチップ/簡潔な命令セット/高パフォーマンス

- プリフェッヂ機能/サイクル・スチール機能

- ・ピットストライス:2900

- コンピュータ機能を複数チップで最適に実現

- 高速用途/専用機能向き

- 高機能CPU/ASICに押されてイマイチ

- ・国内メーカーの戦略と栄枯盛衰

- 日電 日立 東芝 富士通 松下

- 三菱 沖 三洋 シャープ ソニー

- エプソン リコー ローム

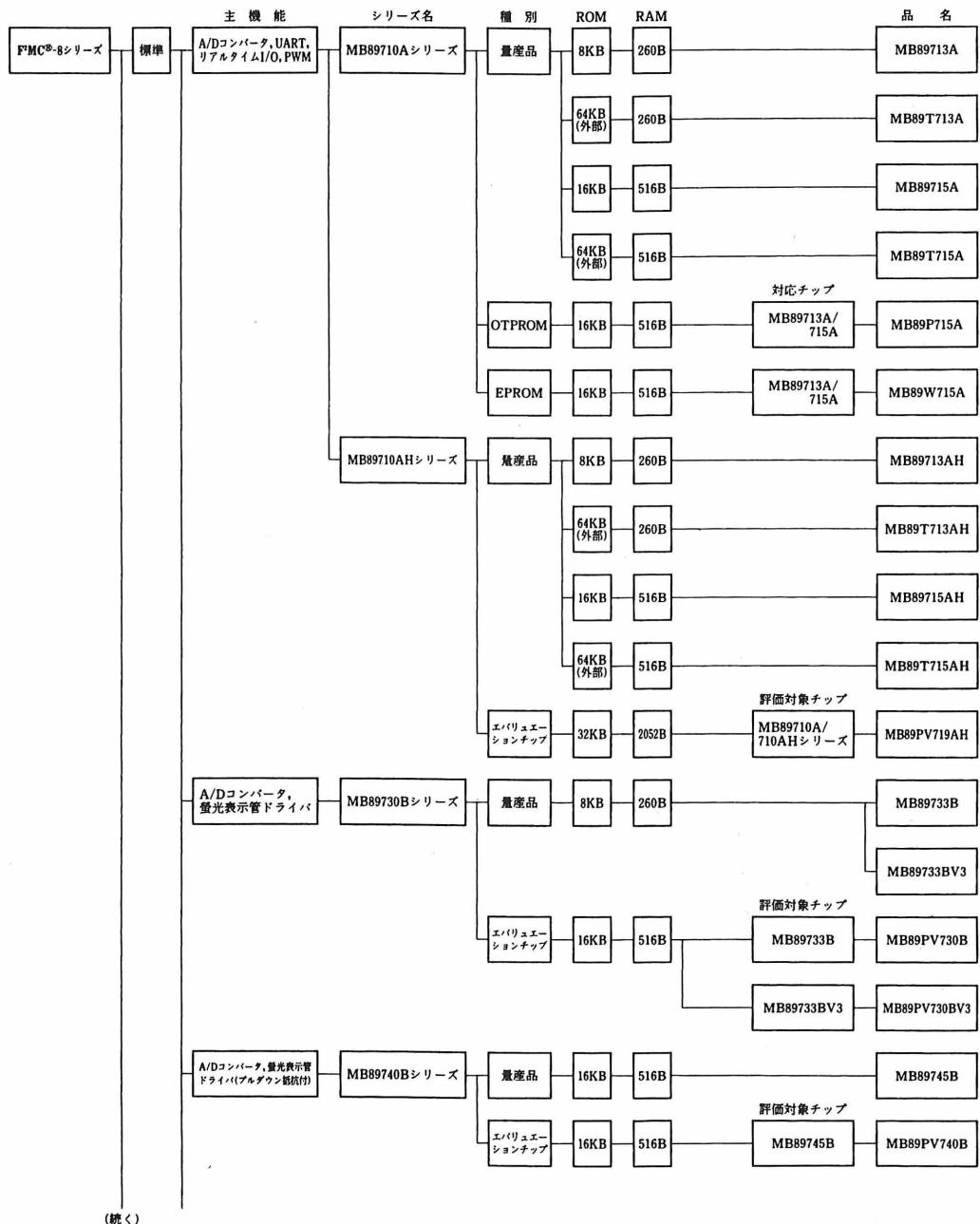

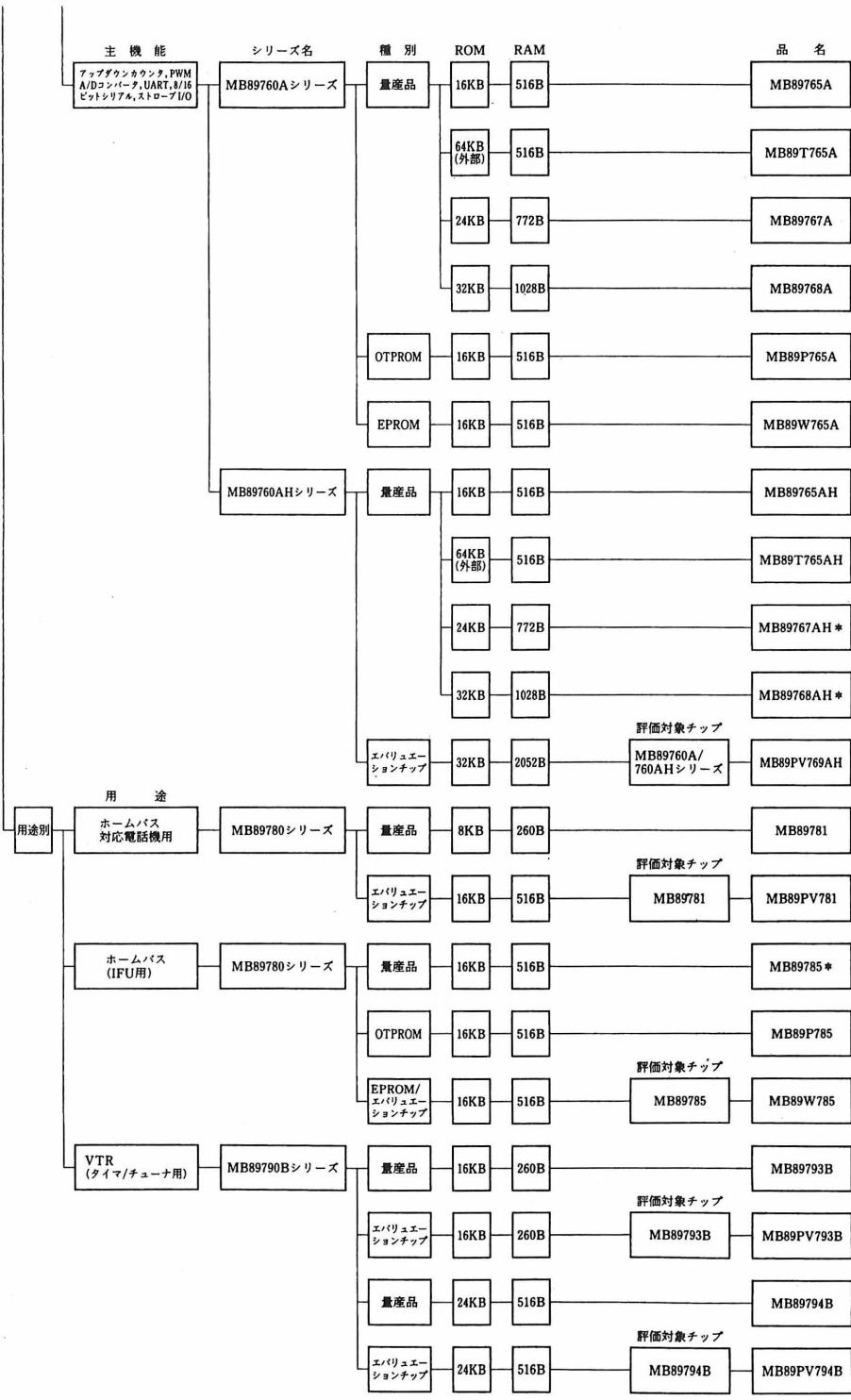

- ・1チップ・マイコン群

- 4ビットCPU:日本の得意分野

(機器組み込み/スレーブCPU)

- 8ビットCPU:1チップの主戦場

(6801/Z8/8049/8051)

(7801/6301/50740)

(16ビット処理コア:日電/富士通/東芝/日立)

- 16ビットCPU:いよいよ本格化

(V25/68008/8096)

- ・16ビット化/32ビット化/64ビット化

- インテル:8086/286/386/486

- モトローラ:68000/68020/68030

- NEC:独自のVシリーズ:V60/V70/V80

- 国内各社:TRONチップで付和雷同

- ・高級言語対応:CISC vs RISC

- CISCの限界

- RISCの問題点

- SPARC/R3000/88000/80860

- 日本のメーカー:独自にやらない(やれない)

- ・ASIC/コアCPU

- システム・オンチップの発想

- 1チップ・マイコン上にゲートアレイを

- スタンダードセル上にCPUコアを

- 東芝の失敗例:スーパ・インテグレーション

リコーの成功例：ファミコン専用チップ

エプソンのアプローチ

モトローラの情けない対応例

国内大手電気メーカの重い腰

### C. CPU の使われ方の例

・データの処理/計算/保管：電子手帳

2進化10進数データ/10進数命令

ストリング・サーチ命令/ブロック転送命令

・自動制御：FA

割り込み命令/タイマ割り込み/ポーリング

・センシング技術：自動車

センサのいろいろ/A-Dコンバータ

アンチロック・ブレーキの例：8096

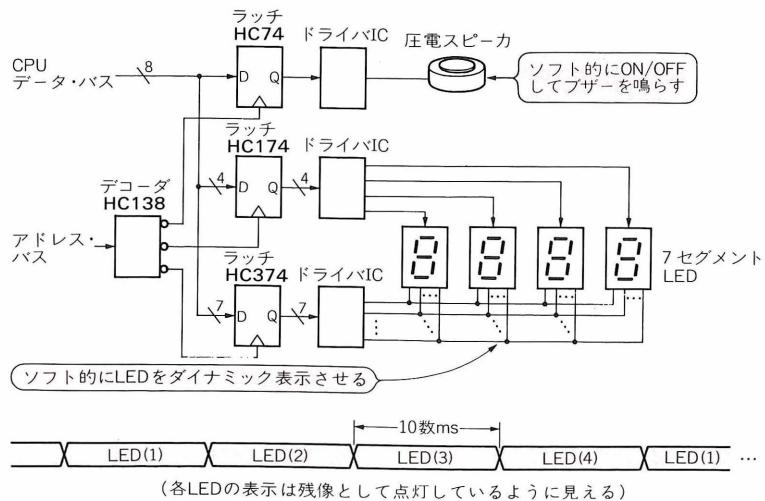

・情報の出力手段：LCDパネル

LEDダイナミック点灯/7セグメントLED

LCDパネルの構成

・通信：FAX

イメージ・センサ/画像データ処理の特性

電話回線との接続/プロトコル/ネットワーク・リンク

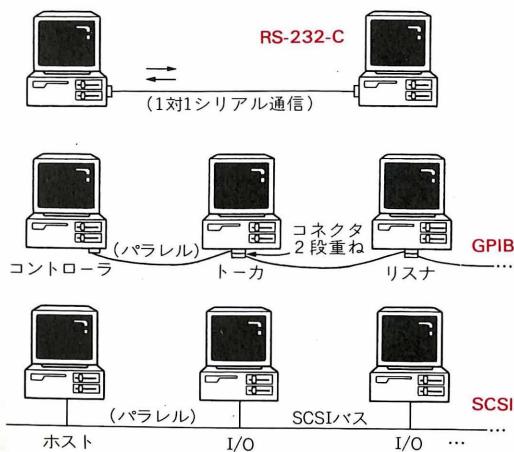

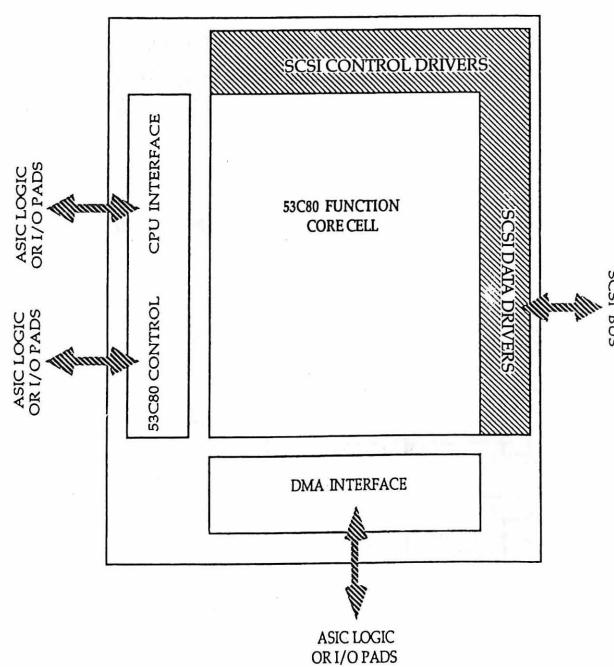

・ネットワーク：SCSI/イーサネット

パソコンの外部信号バス

(GPIB/RS-232-C/SCSI)

EWS/ミニコンのLAN

・パソコン vs 機能特化製品群

ワープロ/電子手帳

多機能電話

ファミコン

・家電機器への組み込み

センサ入力に対する処理(エアコン/炊飯器/ガス警報器)

時間管理処理(タイマ・セット/周期的動作)

情報出力処理(メッセージを話す家電製品)

### (2) ソフトウェアとは

#### D. ソフトウェアの種類と基本概念

・ハードウェア/ファームウェア/ソフトウェア

ファームウェアとは

組み込み機器のプログラムはファームウェア

・「ソフトが走る」とはどういうことか？

CPUが走る

プログラムが走る

ソフトとは無限ループのこと

・階層化→システム・ソフトウェア

階層化の必要性/システム・ソフトウェアとは

ブラックボックスとのインターフェース

・OS/DOS/BIOS

OSとは/DOSとは

BIOSとは

DOSコール/BIOSコール

・プログラム/タスク

プログラムとは/タスクとは

・ユーティリティ/ツール/ファイル

ユーティリティとは

ハードのツール/ソフトのツール

ソフトは「ファイル」という概念から

・モジュール/ルーチン/ライブラリ

ソフトのモジュール化

メイン・ルーチン/サブルーチン

ソフトのライブラリ化/ライブラリアン

・アルゴリズム/チューリング・マシンとは

フローチャート/アルゴリズム

コンピュータ理論の世界

・マルチタスク・システム

マルチタスクとは

当業界はマルチタスクの好例

・バッチ/TSS/リアルタイム

マルチユーザとは

バッチ・システム/TSSシステム

コンピュータのリアルタイム性

#### E. OSのいろいろ

・OS/DOSの必要性

OSの歴史

CPUシステムでのDOSの条件

・Unix

ミニコンの世界の標準

ファイル/ディレクトリの階層性

文字形式ファイルによる統一

2派の対立と統合への展望

・DISC-Basic

DOSを意識させないDOS

Basicからの制御の限界

・CP/M

Z80をメジャーにしたDOS

ツールのいろいろ

・MS-DOS

パソコンの世界を制覇したDOS

CP/Mがベースの8086用DOS

途中のバージョンからUnix風ファイル管理をサポート

MS-DOSの問題点

・OS-9

究極の8ビットCPU:6809用の究極のOS

マルチタスク/オープン・システム

OS-9/68000の人気

・OS/2

IBMの他社いじめ戦略:マイクロチャネル

80286の問題点

- Windows

マッキントッシュの先進性：マン・マシン・インターフェース

オブジェクト指向の環境とは：各種ウィンドウ・システム

- TRON

日の丸 OS=TRON の目新しさ(無い)

TRON の明日/CEC との関係

- ファミコン/Macintosh/FM タウンズ

ファミコン：クイック・ディスク用 DOS

FM タウンズ：CD-ROM だけが頼り

- F. プログラム言語のいろいろ**

- プログラム言語の分類

インタプリタ言語/アセンブラー言語/コンパイラ言語

クロス・アセンブラー/クロス・コンパイラ

AI 言語

- 機械語

CPU が読むのは機械語

インテル HEX フォーマット

- ASSEMBLER

CPU ソフト開発の主流

ニモニック記号

マクロ・アセンブラー

- Fortran

初代汎用言語

- Cobol

事務/経理関係のプログラム言語

- PL/I

事務/経理関係のプログラム言語

- Pascal

計算用言語：(C に押され気味？)

- Basic

ビギナー向け/インタプリタのメリット

Basic コンパイラ

- FORTH

制御向け言語/非常にコンパクト

- C

Unix を記述/各種入り乱れて激戦

C の問題点/欠点

- Lisp

リスト処理向け言語

- Prolog

AI 言語?

知識表現/知識処理に向く

- Ada

アメリカの軍用規格言語(ブームはほんの一時だけ)

- Smalltalk

言語というより環境

オブジェクト指向/ウィンドウ

- C++

C の欠点に対応して拡張

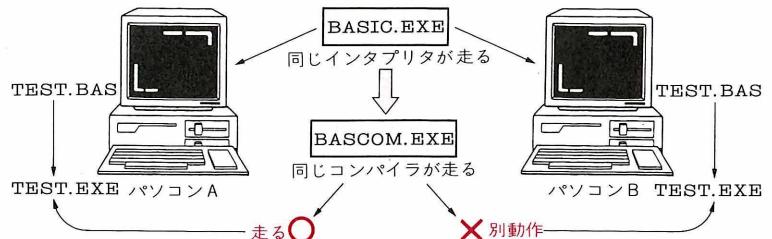

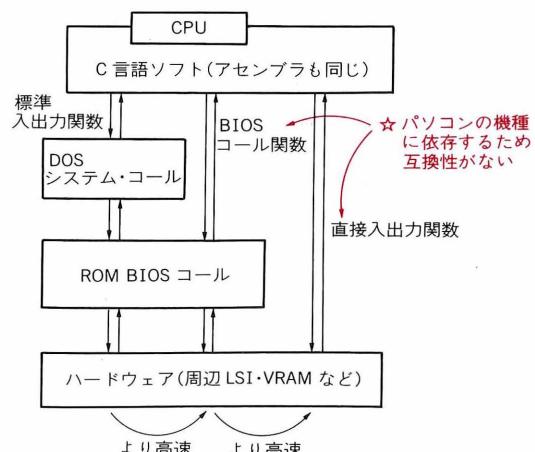

- G. ソフトウェアの走行環境**

- バッチ/TSS

結果が欲しいような処理

負荷に依存する処理速度：LSI 設計の実例

- パソコン

通常のシステム：DOS からアプリケーションを呼ぶ

コピー・プロテクト：独自 OS

パソコンの暴走→プロテクト・モード/スーパーバイザ・モード

- 組み込み機器

ファームウェアの走行環境

リセットから CPU が ROM プログラムに従う

- エミュレーション

機種の互換性とは

ハードウェア互換性/ソフトウェア互換性

エミュレーション・モード

AX パソコンの失敗

- リモート・プロセシング

CPU システムとの通信

リモート・デバッグの例

- オンライン

銀行のオンライン処理の例

オンラインの注意点：信頼性/回復対策

- 分散処理

EWS/パソコンの LAN

リアルタイム処理の分散化は可能か? → NTT の例

- H. プロのためのソフトウェア技術**

- 階層化/モジュール化：「ソフト部品」

ソフト部品のメリット/注意点

- 信頼性

暴走しないシステム

周囲を暴走させないシステム

暴走からの復帰方法

CPU が自分の発狂を知るには

フォールトレント・システム

- フレキシビリティ

製品の仕様変更に対応できるソフトとは

多機種展開に対応したソフト開発

組み込み機器の制御ソフトなんてみな同じ?

- 保守性

製品の寿命/何年もソフトを覚えていられるか

ドキュメント化によるサポート

- ソフトウェアのライフサイクル

企画フェーズ/システム設計フェーズ

開発フェーズ/デバッグ/ROM 化

市場デバッグ/バージョンアップ

- ・ソフトのコストとは

製品コストとソフトの比率

外注の危険性

(ノウハウのレベル/トシズラハウス/安いな変更)

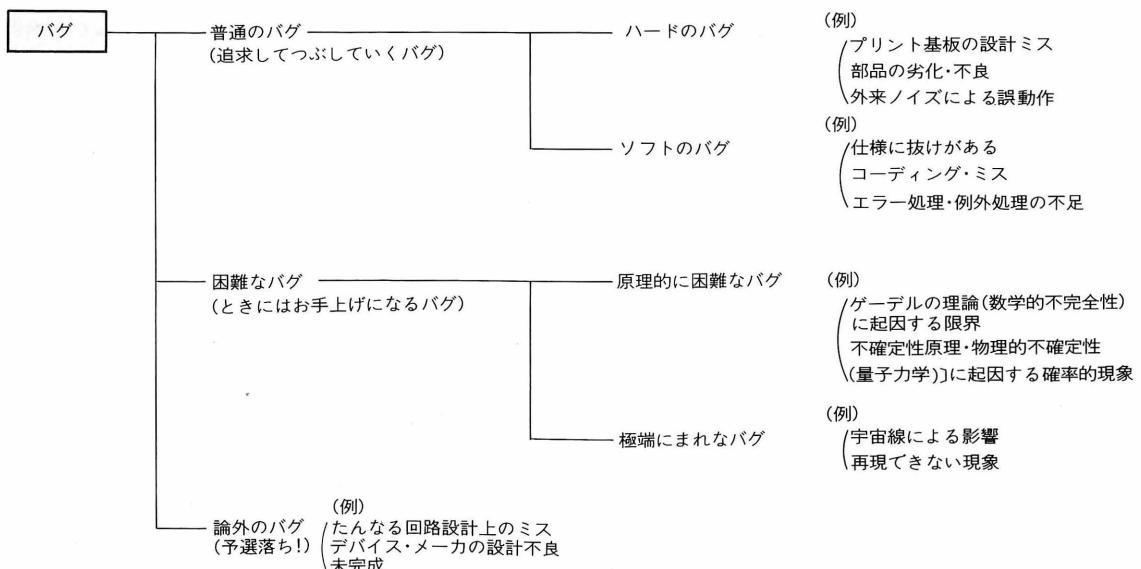

- ・バグとは

仕様の本質的なバグ

プログラム上のミスによるバグ

(アルゴリズム/ミスマッチ/レジスタ共有)

ソフトのインターフェースのバグ

非常に頻度の低いバグ

致命的バグ/許せるバグ

- ・デバッグとは

デバッグ曲線

あからさまなバグを検出するデバッグ

想像を越えるバグを出現させるデバッグ

市場デバッグ: 最大のデバッグ

- ・ソフトウェア開発手法→ CASE

効率的なソフト開発環境とは

専用言語を作ってしまう

専用コンパイラーを作ってしまう

CASEツールとは

アセンブラー<高級言語<自然言語=仕様書

CASE+フル CAD システムの美しい世界

- ・アドレッシング・モード

インプライド・アドレッシング

レジスタ・アドレッシング

イミディエート・アドレッシング

ダイレクト・アドレッシング

レラティブ・アドレッシング

ゼロページ・アドレッシング

インデックス・アドレッシング

レジスタ・インダイレクト・アドレッシング

メモリ・インダイレクト・アドレッシング

レジスタ・インデックス・アドレッシング

インデクスト・インダイレクト・アドレッシング

インダイレクト・レジスタ・インデクスト・アドレッシング

エクステンデッド・アドレッシング

- ・命令: オペコード/オペランド

オペコードの例/オペランドの例

- ・フラグ/分岐

フラグ・レジスタ

フラグ・ビットによる分岐命令

- ・リセット/ベクトル・アドレス

CPUをリセットすると…

リセット・ベクタ方式 CPU

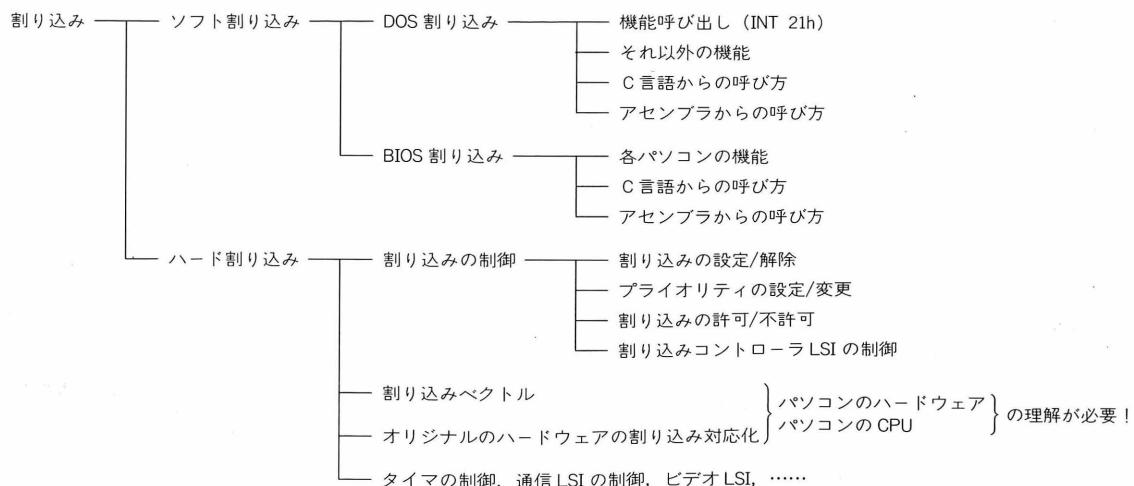

- ・割り込み(ハード/ソフト)

ハードウェア割り込み

ソフトウェア割り込み

- ・スタック/スタック・ポインタ

スタックとは/スタック・ポインタとは

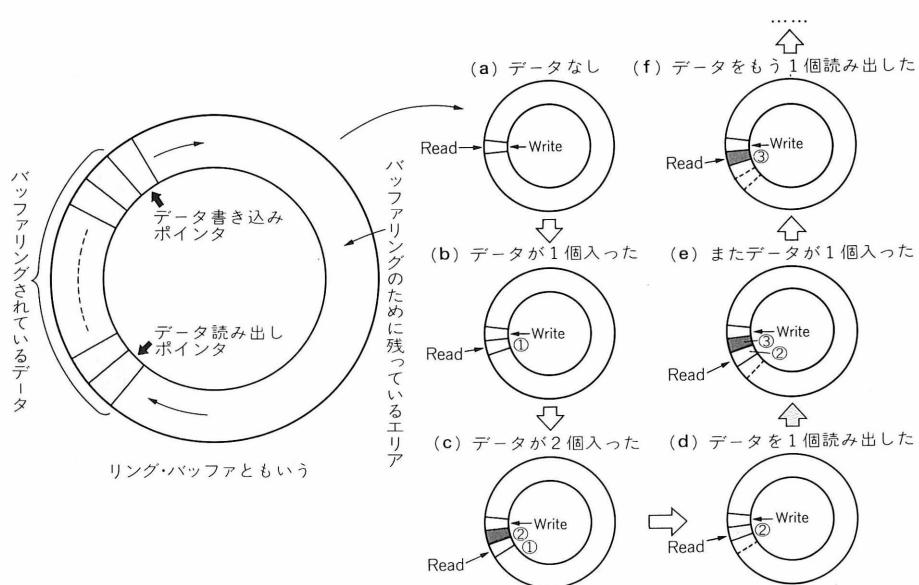

FILO/FIFO: リング・バッファ

- ・入出力動作とは

入出力命令

I/Oマップド I/O

メモリ・マップド I/O

- ・パイプライン/プリフェッチ/キャッシュ

CPUの高速化の要請

命令パイプライン

命令のプリフェッチ

キャッシュ・メモリの搭載

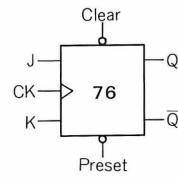

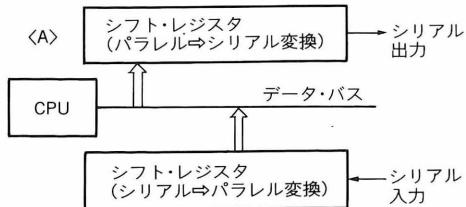

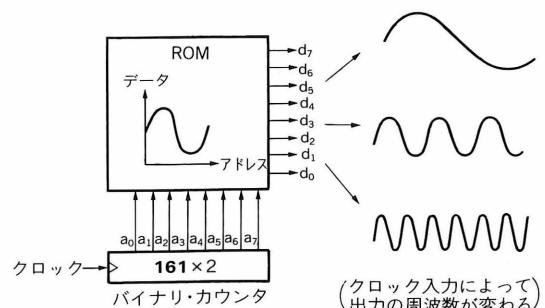

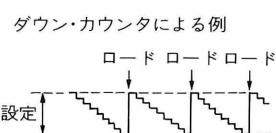

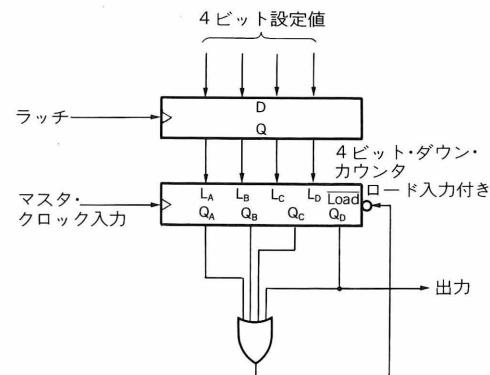

- J. 周辺回路/周辺 LSI

- ・バス・バッファ

245: 双方向 3 ステート・バッファ

374: 3 ステート・ラッチ・バッファ

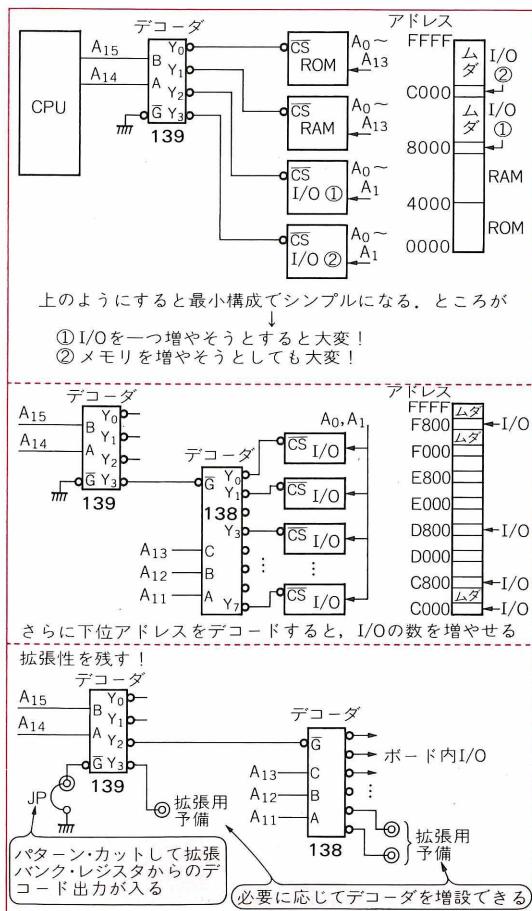

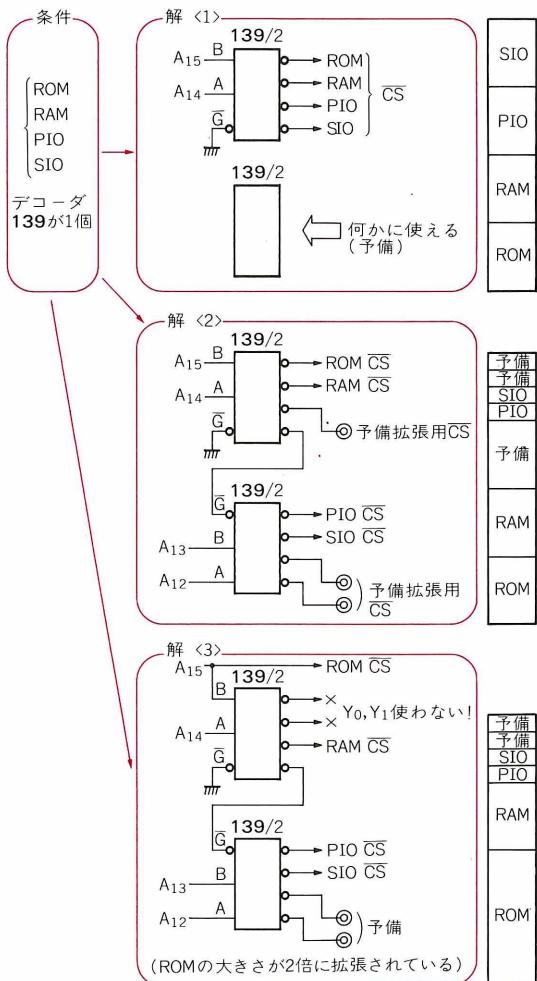

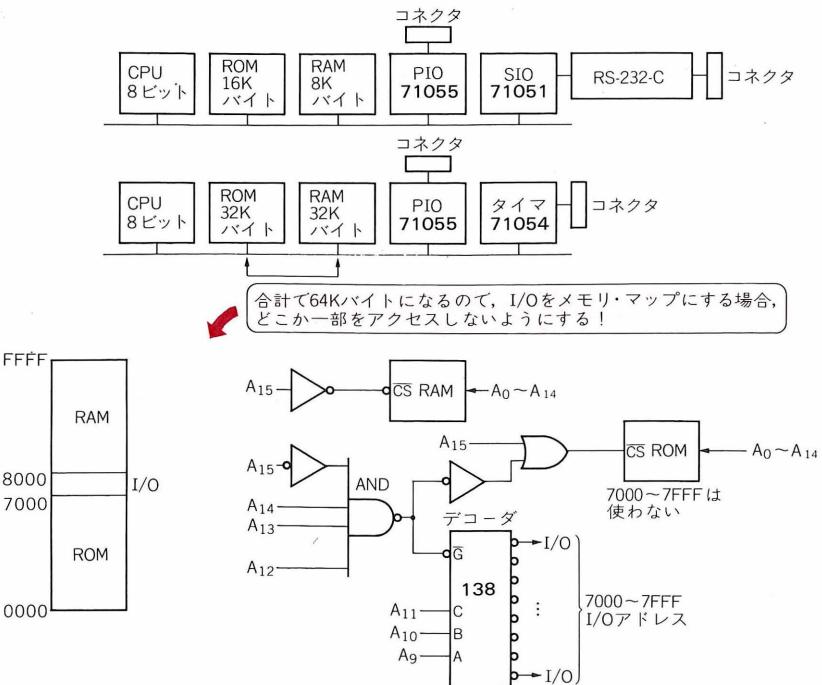

- ・デコーダ

アドレス・デコードとは/負論理のチップ・セレクト信号

138: 3+3 入力 8 出力

139: (2+1 入力 4 出力)2 系列

PAL によるアドレス・デコード

ゴースト(シャドウ)エリア

- ・タイマ

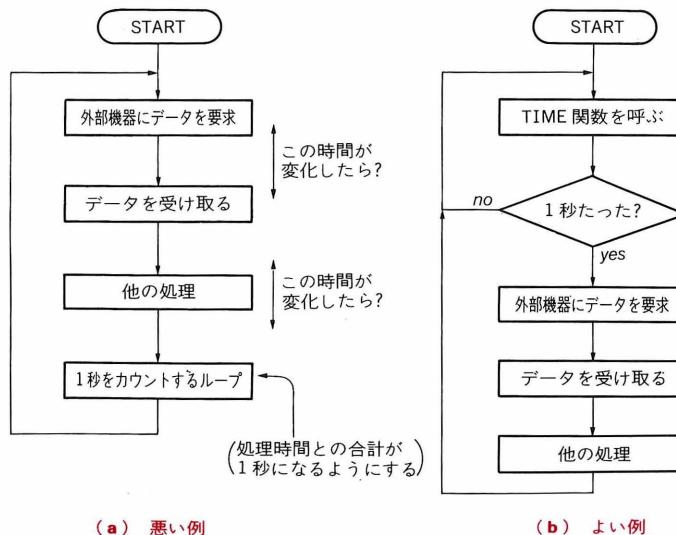

- CPU のソフトによる時間管理はデータマ

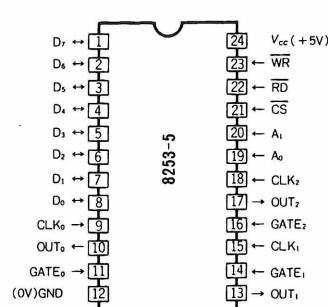

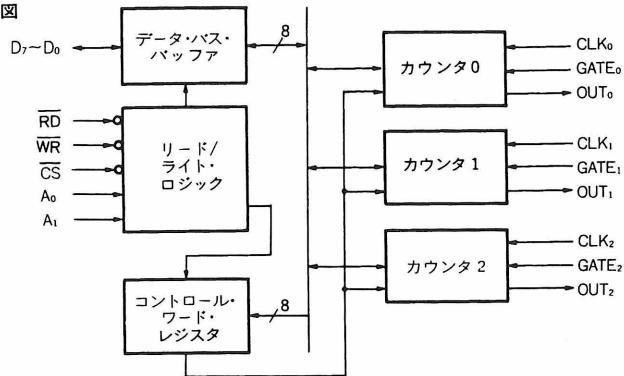

8253：古典的タイマ

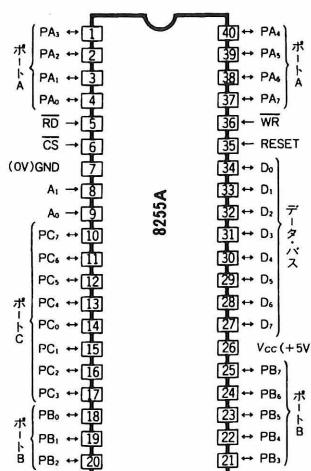

- ・パラレル I/O

- データ・バスから信号を出力するには

データ・バスに信号を取り込むには

8255：古典的 PIA

瞬間的バス・ファイトの問題

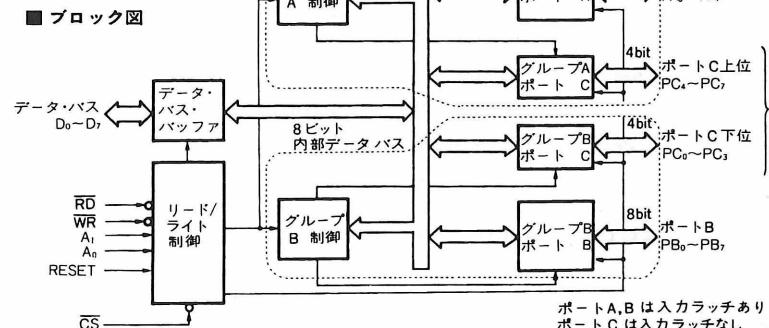

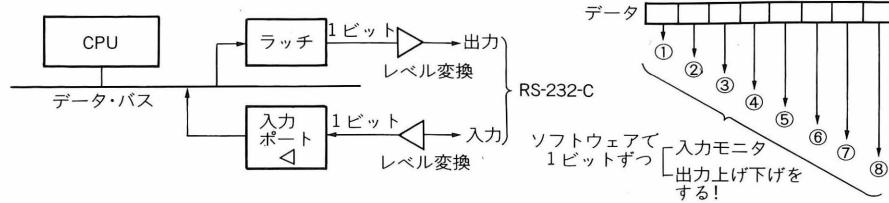

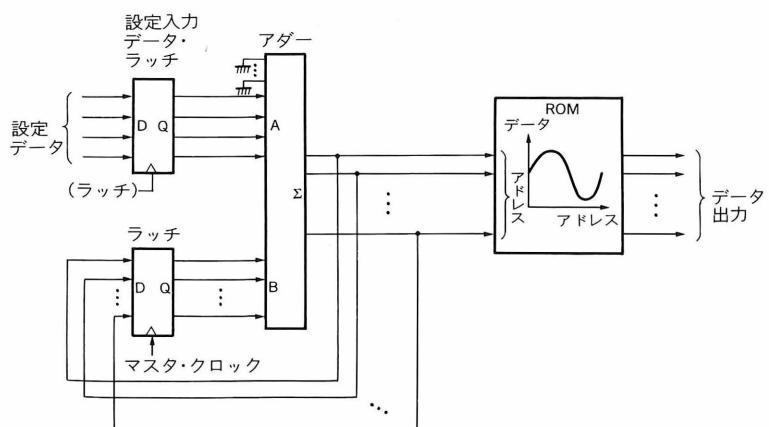

- ・シリアル I/O

- シリアル通信の種類

シリアル信号を CPU のソフトで実現すると

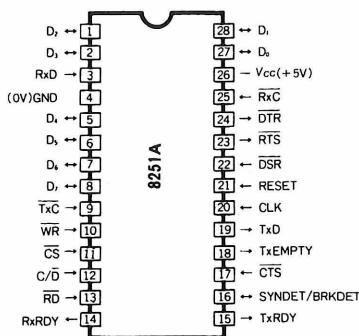

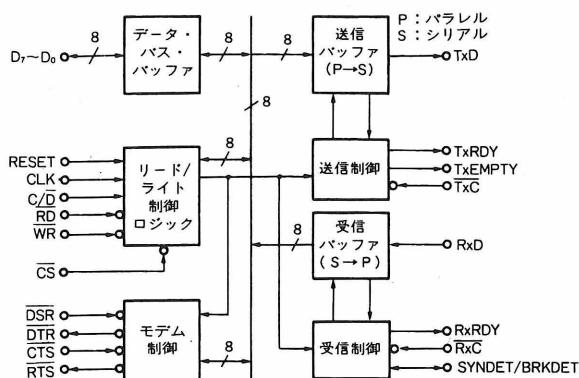

8251：古典的 UART → RS-232-C

- ・MMU

- メモリ空間を拡張するには

パンク・レジスタ

ページング/セグメント方式

- ・割り込みコントローラ

- 多重割り込みの必要性/プライオリティ

Z80 ファミリ：デイジ・チェーン

モトローラ系：ベクタ処理が簡単

8259：プライオリティ可変コントローラ

- ・DMAC

- CPU による単純転送の非効率さ

DMA とは/DMAC の仕事

DMA の欠点→分散処理へ

- ・FDC

- FDD の制御処理

765/8877：古典的 FDC

- ・A-D・D-A

- S&H

変換時間の考え方

必要なビット精度/変換時間を見極めること

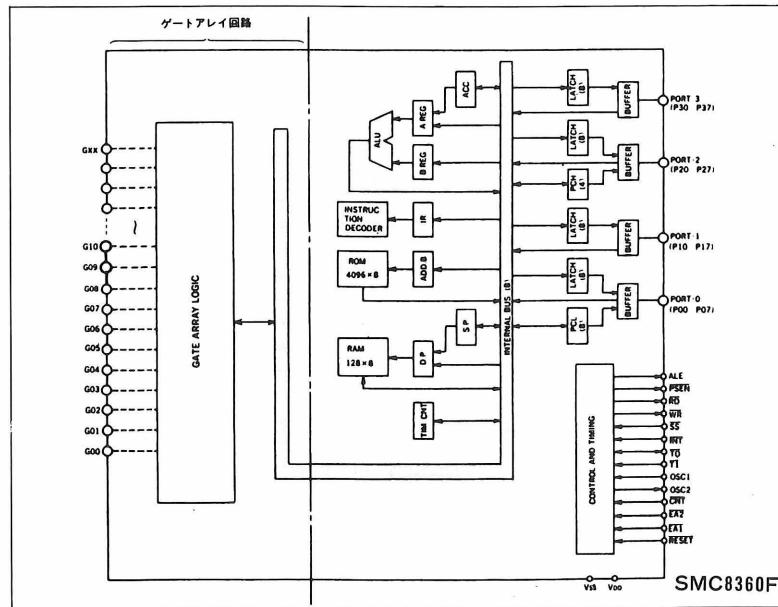

- ・1チップ・マイコン

- マルチチップ CPU/1 チップ CPU

チップ上のマスク ROM の使い方

- ・リセット IC

- リセット IC の機能/使い方

(パワーオン/電圧低下/レギュレータ)

- ・ウォッチドッグ・タイマ IC

- ウォッチドッグ・タイマとは

ハードによる構成/専用 IC による構成

- 開発ツール

- オールインワン型/パソコン・ホスト型

これからは EWS の時代

- エディタ

- エディタと英文ワープロとの違いは？

エディタに要求されるもの

「ソフトとは本質的にはエディタである」

- アセンブラー

- アセンブリ言語/アセンブラーというツール

マクロ機能/クロス・アセンブラー

- コンパイラ

- 高級言語のメリット

コンパイラのデメリット

- リンカ

- リロケータブル・オブジェクト・ファイル

リンクとは/リンクを活用する

- ライブラリ

- モジュールのライブラリ化のメリット

ライブラリの機能

- ダウンローダ

- オブジェクト・フォーマット

(インテル HEX/拡張インテル/モトローラ)

- デバッガ

- パソコンのデバッガ/ハードウェアのデバッガ

- ICE

- ICE の機能

ICE によるリモート・デバッグ

- モニタ

- モニタの機能/モニタによるデバッグ

モニタを自作する

- ROM ライタ

- EPROM のプログラム/ROM ライタの活用

- OTPROM/ピギーバック

- ワンタイム EPROM

ピギーバック型 CPU

- ブレッド・ボード(BB)

- ブレッド・ボードとは/BB 開発のコスト

BB による開発のメリットは

コア CPU の BB による開発

- シミュレータ

- シミュレータによる開発のメリット

これからの開発の姿

- K. CPU プログラムの開発環境と開発手順**

- ・機能仕様→システム検討

- トップダウン設計/ボトムアップ設計

ニーズ指向/シーズ指向

- ・モジュール分割→フローチャート

- モジュールの切り分け方/モジュール結合

モジュール間のインターフェース

- (4) 具体的な CPU プログラムでの実戦的検討

- L. <省略>

- M. <省略>

## N. 各種ルーチンの考え方/組み方

- ・全体の構成

- 見やすいソフト構造とは

- 作りやすい/修正しやすい構造

- 2次災害を生まない構造

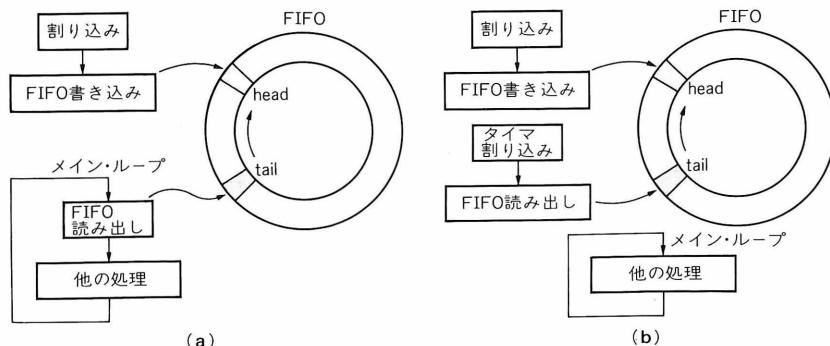

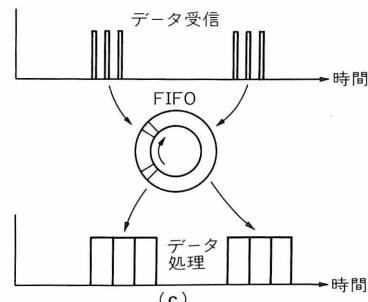

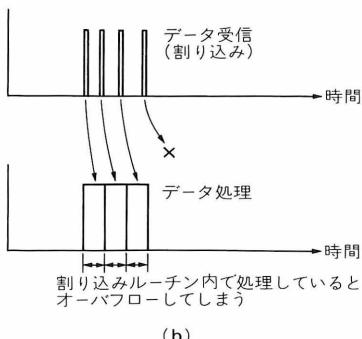

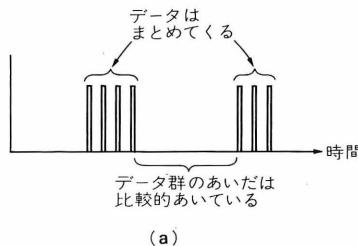

- ・ソフト処理とハードウェア割り込みとの関係

- ソフト処理で済むもの/割り込みを使用するもの

- ・初期化ルーチン

- 最優先の処理は何か

- リセット時の処理のいろいろ

- ・メイン・ルーチン

- できれば単純ループがよい

- 検査ルーチンとの2重化

- ・割り込みルーチン

- 割り込みルーチンの位置付け

- 非同期処理の注意点

- 割り込み処理の鉄則

- 通常ルーチンとのインターフェースのポイント

- ・処理プライオリティの付け方

- 割り込みコントローラ

- ベクタ配置による自動的処理

- ソフトによる簡単な方法

- プライオリティの変更

- ・デバッグのための処理

- エラー・トラップ/エラー・メッセージ

- RS-232-C の活用

- テスト・モード/隠しモード/裏モード

- ・暴走対策

- ノイズ関係→ハード屋と共同で

- ソフトは基本的に暴走に弱い

- 冗長さによる対策

- ・ソフトを外注に出す場合の注意点

- ソフトハウスは当業界ソフトのノウハウを知らない

- 自分でソフトを書けなければ外注管理能力はなし！

- 時間をカネで買うことの認識

- . プログラム・テクニック/バグ出しテクニック

- ・ラベルの活用

- 絶対アドレスは絶対に使わない

- アセンブラーのラベル制限に注目

- コメント代わりにラベルを使う

- ・メモリ/レジスタの参照

- データは圧縮できる←スピードは落ちる

- 共通メモリ・アクセスの罠

- レジスタのスタックの注意点

- ・フラグ・ビットの活用

- ビット操作命令の活用

- CPU アーキテクチャに対応したワザがある

- ・間接アドレッシング

- Z80 の間接は最悪

- マニュアルをよく読む/CPU の個性をフルに活用する

- ・パラメータ・テーブル

- パラメータ比較の悪い例/良い例/もっと良い例

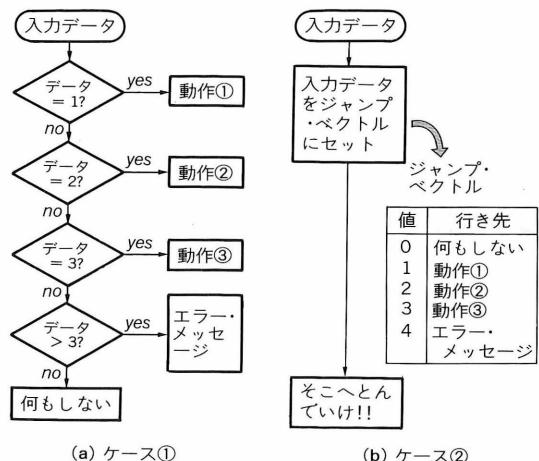

- ・ディシジョン・テーブル

- 制御ソフトは場合分けのカタマリ

- テーブル・ジャンプの美しさ

- 最後の処理を忘れずに

- ・マクロ/サブルーチンの活用

- 似たような処理を並べない

- マクロのメリット/デメリット

- サブルーチンのメリット/デメリット

- パラメータの受け渡し

- ・BIOS を作る

- パソコンのグラフィック BIOS

- BIOS コールによるプログラム製作

- ・デバッグ・ルーチン

- ジョブ・モニタ/履歴記録

- 条件アセンブル

- ステータスのディスプレイ

- ・他社に解読させないための方法

- パソコンのコピー・プロジェクト/高額ソフトのプロジェクト

- データ/パラメータの暗号化

- データ埋め込み

- 逆アセンブル・トラップ

- バス信号線の暗号化

- ROM 内蔵コア CPU 化

- 解読されて困るようなことはしない！(特許)

- ・自己診断機能

- メモリの検査(ROM/RAM)

- バージョン・チェック/周辺 LSI の初期確認

- ソフト的ランタイム・カウンタ/イベント・カウンタ

- ・工場出荷検査機能

- 特定の操作+電源 ON

- 信号ループ

- LED 点灯/SW スキャン

- ・隠し機能:リモート・デバッグ

- RS-232-C の活用

- RAM エリアが大きいものは実現可能

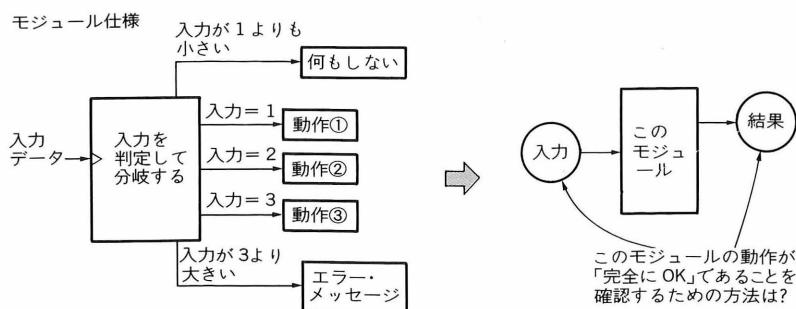

- ・バグの出し方:境界値分析

- 開発担当者のバグ出しはザル

- めくらめっぽう方式の欠点

- 境界値分析の手法

- 人間の手は2本という盲点

- ・パネル・スイッチ関係のバグ

- 「考えられない組み合わせ」を考える

- 導電ゴム接点の注意点

- ・誤動作対策関係のバグ

- ノイズで完全にリセットしていいのか

- UNDO/レジューム機能

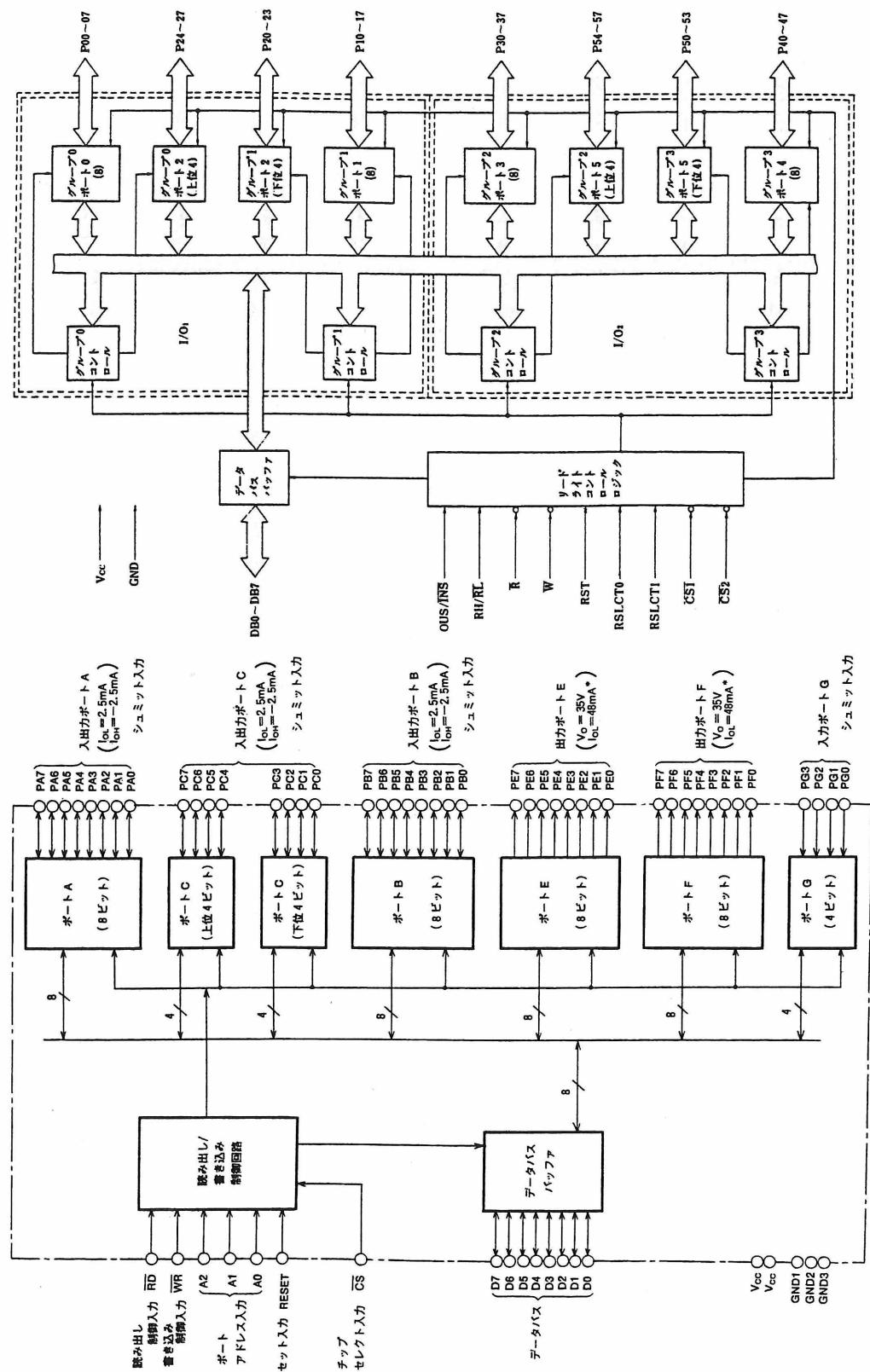

事 典 編

# マイコン技術者のための【基礎】概論

## ディジタル技術の基本

### ●論理回路

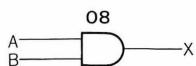

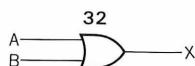

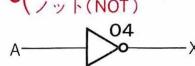

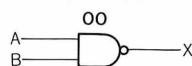

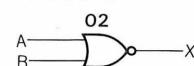

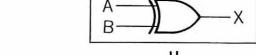

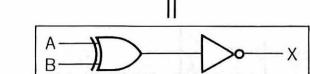

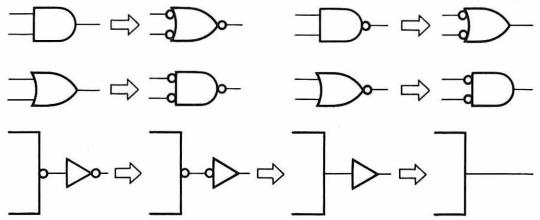

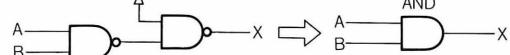

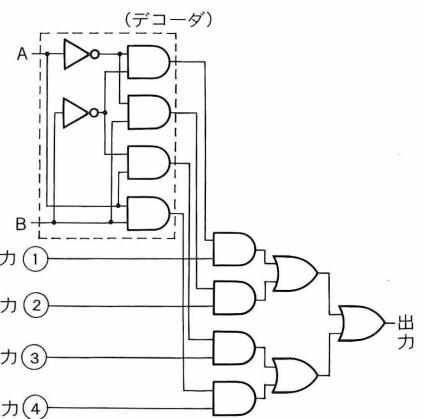

ディジタル回路技術の基本となる「論理回路」は、何種類かの「ゲート」(図1.1)で構成されます。つまり、

- 1本の信号の反転(否定)であるインバータ

- 2入力1出力の論理積(アンド)

- 2入力1出力の論理和(オア)

の3種類を知っていれば、原理的にはあらゆる論理回路を構成できることになります。

また、これとは別に、ゲートアレイを設計する際によく使われる方法として、

- [アンド+インバータ]と等価なNAND( NAND )

- [オア+インバータ]と等価なNOR( NOR )

- のいずれか1種類だけを組み合わせることによっても、他の論理ゲートはすべて実現できます。

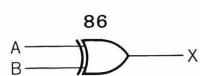

「排他的論理和」(エクスクルーシブ・オア)というゲートも基本的なものですが、この機能としては、

- 二つの入力の一一致・不一致を検出する

- 一方の入力を他方の信号を反転するための制御信号とする

というような性質があり、演算回路などを構成する上でいろいろに活用されます。

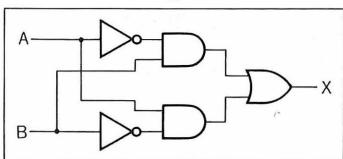

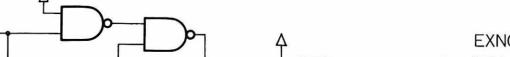

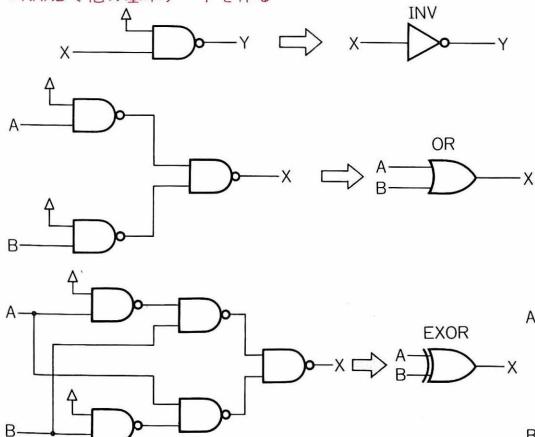

そこで、図1.2のように、基本ゲートの組み合わせで、いろいろな機能のディジタル回路を設計してみましょう。TTLデータブックには、各ICの等価回路も掲載されていますから、真理値表から等価回路を設計して確認してみる、というのは最高の勉強となります。

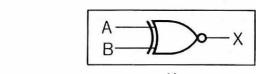

### ●順序回路(同期回路)

論理回路が「入力が揃うと出力が決まる」という静的な回路であるのに対して、順序回路(同期回路)とは、

▷動作の基準となる時間信号(基準クロック・パルス)が存在して、

▷その1クロックごとに同期して状態が変化する「動的」な回路

と特徴づけることができます。CPUそのものを含めて、ディジタル回路としてなんらかの時間的動作を行うものは、すべて順序回路をもっていることになります。

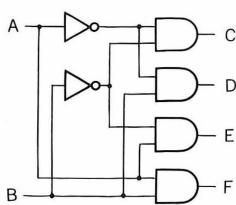

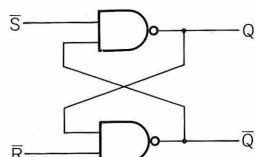

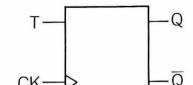

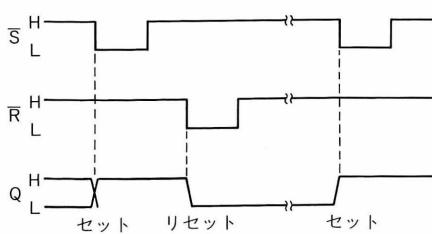

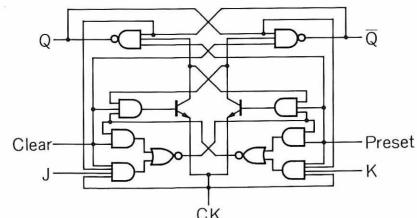

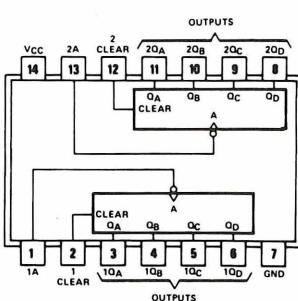

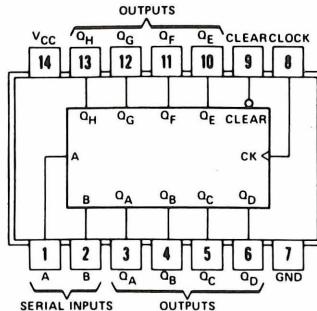

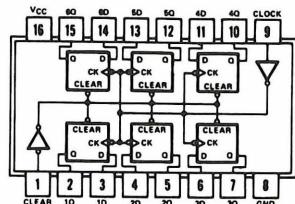

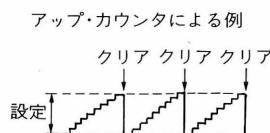

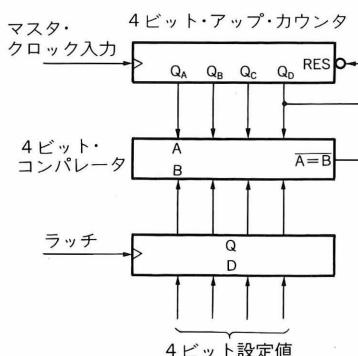

順序回路の基本は、フリップフロップ(F/F)によるトグル動作にあります。図1.3にあるような、もっとも単純なSRフリップフロップや、実用的なJKフリップフロップとかTフリップフロップについては、回路図の上で動作を追ってみたり、実際にTTLの動作をテスターで確認してみましょう。この延長には、図1.4のような、F/Fを多段に重ねたカウンタ回路やシフト・レジスタ回路、あるいは複数個を並べたラッチ回路などがあります。全体のゲート規模は大きくなります、これらの回路の基本的な動作原理は個々のF/Fに分解して理解することができます。

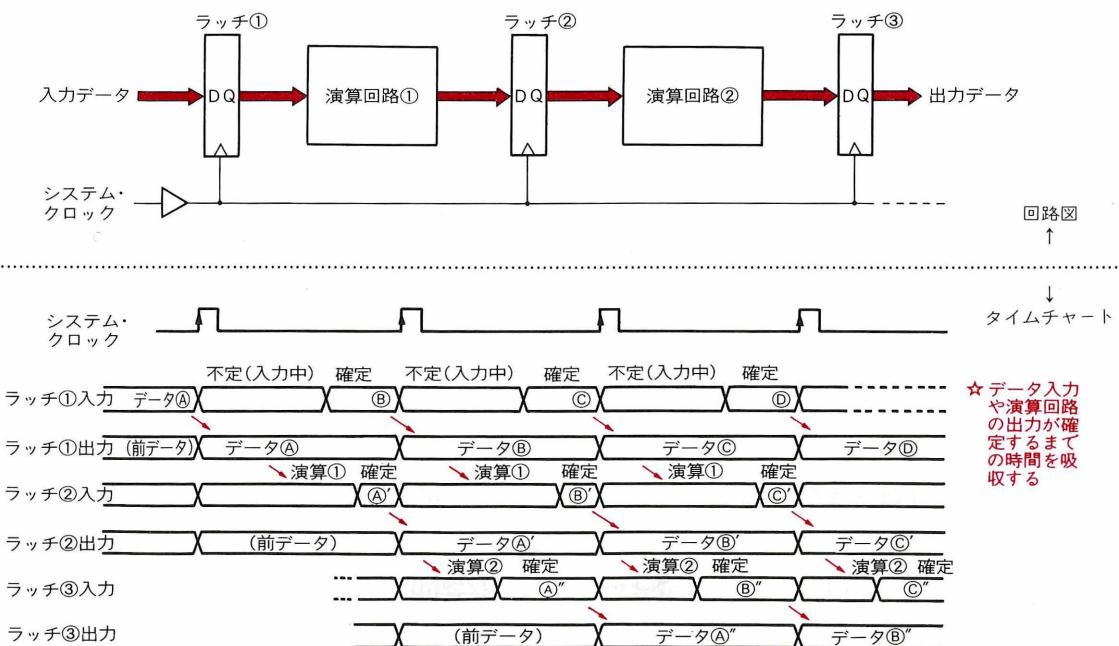

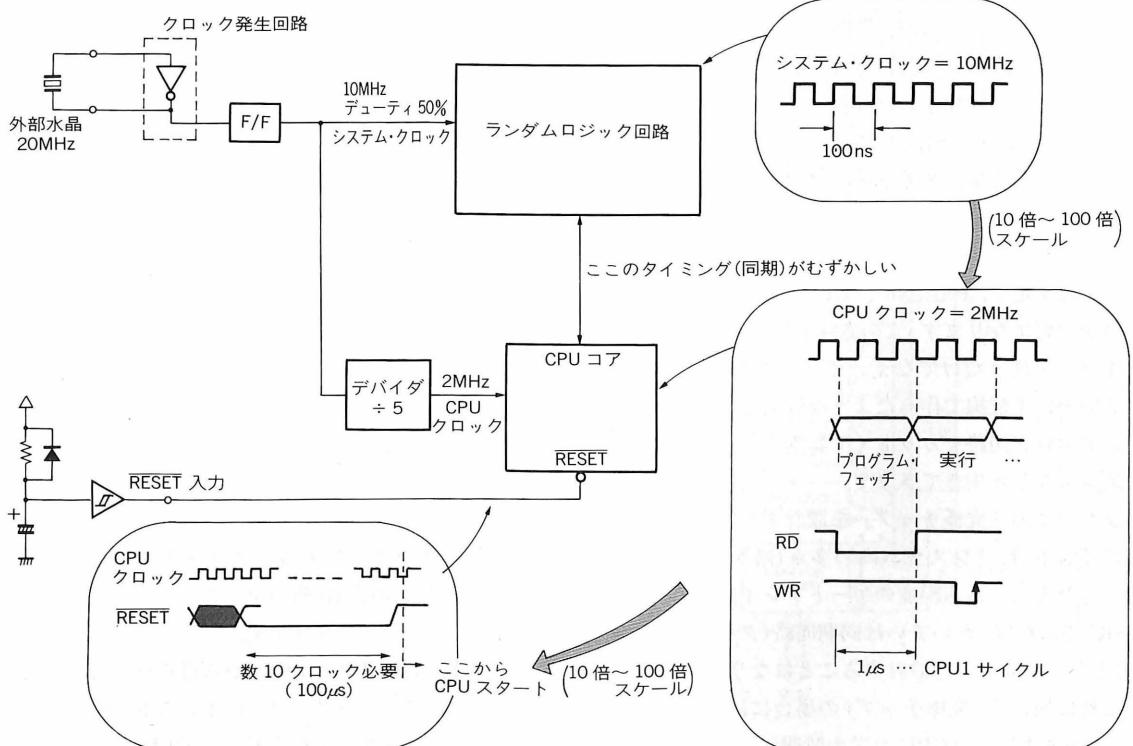

同期回路の考え方をさらに進めると、図1.5のように、クロック信号のタイミングに同期してシステムの各部分を動作させて、クロックとクロックの間(図では立ち上がりエッジ同士の間)での回路状態の遅延を吸収してしまう、という発想が重要になります。これは、ASICのような大規模な回路を設計する場合の定石的テクニックで、マージンを十分に確保した回路設計の秘訣ともいえるものです。

## (図I.1) ゲート — 基礎の基礎 —

ゲートとは、デジタル論理回路を構成する基本的な論理単位のこと。通常は図のようなものをいう。論理演算の基本は2入力1出力(と反転)であり、これらのゲートを組み合わせることで、あらゆる回路を構成するこ

とができる。また、トランジスタ回路の動作はNANDそのものなので、TTLの最初の番号である00によって、他の基本ゲートもすべて作ることができる。

## &lt;各種ゲート&gt;

## ●アンド(AND)

| IN |   | OUT |

|----|---|-----|

| A  | B | X   |

| L  | L | L   |

| H  | L | L   |

| L  | H | L   |

| H  | H | H   |

- ともに“H”入力のときのみ出力は“H”

$$X = A \cap B$$

## ●オア(OR)

| IN |   | OUT |

|----|---|-----|

| A  | B | X   |

| L  | L | L   |

| L  | H | H   |

| H  | L | H   |

| H  | H | H   |

- いずれかが“H”入力ならば出力は“H”

- (ともに“L”入力のときのみ出力は“L”)

$$X = A \cup B$$

## ●インバータ(INV)ノット(NOT)

| IN |  | OUT |

|----|--|-----|

| A  |  | X   |

| L  |  | H   |

| H  |  | L   |

出力は入力の反対

## ● NAND(NAND)

| IN |   | OUT |

|----|---|-----|

| A  | B | X   |

| L  | L | H   |

| H  | L | H   |

| L  | H | H   |

| H  | H | L   |

- ともに“H”入力のときのみ出力は“L”

$$X = \overline{A \cap B}$$

$$X = \overline{A} \cup \overline{B}$$

## ●ノア(NOR)

| IN |   | OUT |

|----|---|-----|

| A  | B | X   |

| L  | L | H   |

| H  | L | L   |

| L  | H | L   |

| H  | H | L   |

- いずれかが“H”入力ならば出力は“L”

- (ともに“L”入力のときのみ出力は“H”)

$$X = \overline{A \cup B}$$

$$X = \overline{A} \cap \overline{B}$$

## ●エクスクルーシブ・オア(EXOR)

| IN |   | OUT |

|----|---|-----|

| A  | B | X   |

| L  | L | L   |

| H  | L | H   |

| L  | H | H   |

| H  | H | L   |

- 入力が異なるときは出力は“H”，入力が等しいときは出力は“L”

## ●エクスクルーシブ・オア(EXOR)

## ●エクスクルーシブ・ノア(EXNOR)

## ●多入力ゲート

## ●正論理↔負論理の等価回路

## ●NANDで他の基本ゲートを作る

〔図1.2〕 基本ゲートによる等価回路の設計例

・デコーダ回路

| 入力 | 出力 |         |

|----|----|---------|

| A  | B  | C D E F |

| L  | L  | H L L L |

| L  | H  | L H L L |

| H  | L  | L L H L |

| H  | H  | L L L H |

・ゲート付きデコーダ回路

| 入力 | 出力 |             |

|----|----|-------------|

| A  | B  | C D E F     |

| L  | L  | (データ) L L L |

| L  | H  | L (データ) L L |

| H  | L  | L L (データ) L |

| H  | H  | L L L (データ) |

信号入力が出力に出る

データ

入力

ゲート信号とも考えられる

・データ・セレクタ回路

| 入力  | 出力 |   |     |

|-----|----|---|-----|

| 信号  | A  | B |     |

| 入力① | L  | L | 入力① |

| 入力② | L  | H | 入力② |

| 入力③ | H  | L | 入力③ |

| 入力④ | H  | H | 入力④ |

四つの入力から一つを選ぶ

〔図1.3〕 フリップフロップ(F/F)

(a) S-Rフリップフロップ

(c) Tフリップフロップ

(b) J-Kフリップフロップ

〔図1.4〕 フリップフロップを多数ならべた機能回路の例

393

164

174

(通常、74393, 74164…の74は省略することが多い。本書でもその流儀にしたがう)

〔図1.5〕 同期的なデジタル回路設計とは…

## ●演算回路

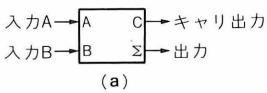

演算回路は、基本ゲートに分解すれば「高度に複雑な論理回路」ですが、加減乗除などの代表的な回路については、出会ったところでマスターしてしまいましょう。なお、図1.6のような2進数・8進数・16進数などの数値表現とか、図1.7のような、数値データの符号と補数の表現も確認しておきましょう。

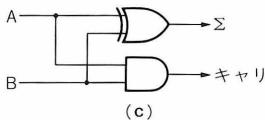

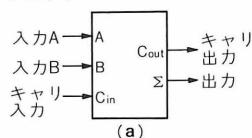

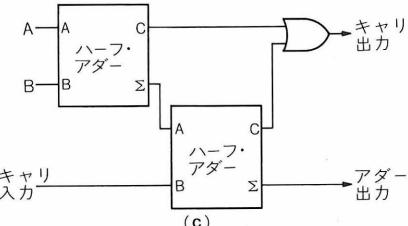

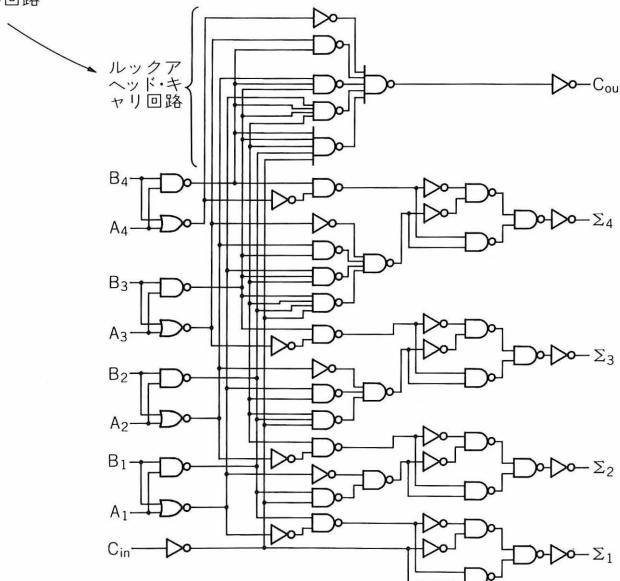

演算回路の基本的要素である加算器は、図1.8の1ビットのハーフ・アダーデ、二つをまとめてフル・アダーデが構成できます。これを多段にわたって(キャリ信号をつぎつぎに繰り上げて)重ねていけば、原理的には任

意のビット幅の加算器ができます。実際のASICやDSP回路では、キャリ信号が繰り上がる遅延時間が問題となるために、ルックアヘッド・キャリ回路によってスピードを稼ぎます。

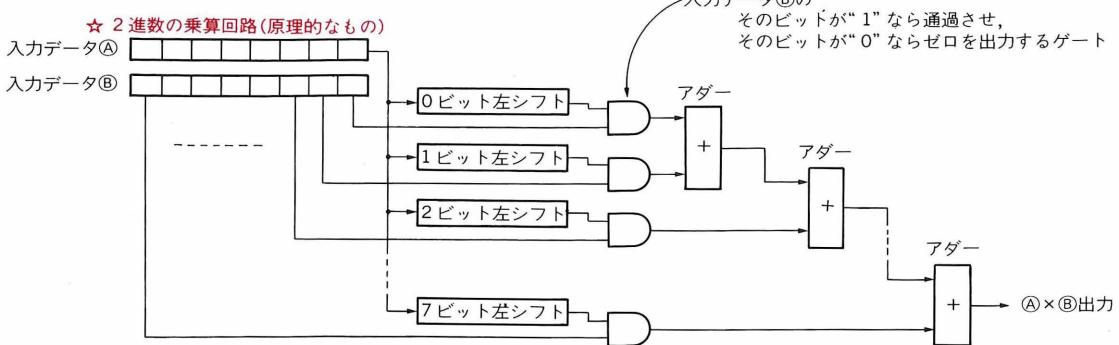

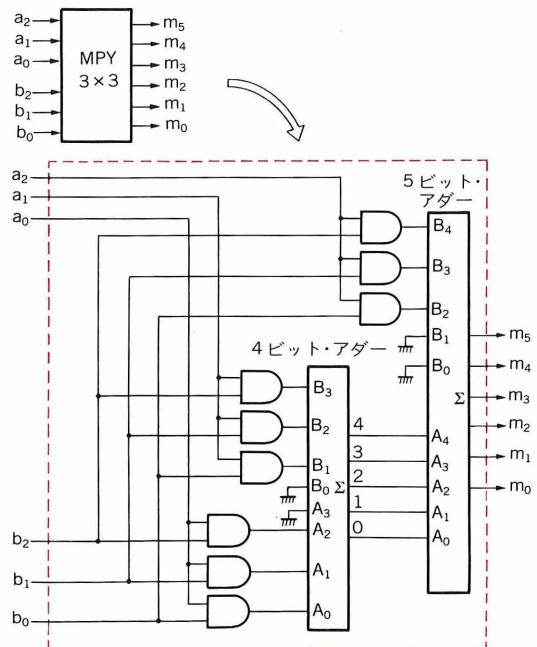

また図1.9のように、2進数ではデータの2倍は1ビット・シフトに相当しますから、シフト・レジスタと加算器の組み合わせによって、乗算回路が実現できます。ここに補数変換のための符号反転回路(エクスクルーシブ・オア群)を加えると、「符号付き乗算回路」が構成できます。ちょっと課題として考えてみてください(コラム 解答1 参照)。

〔図1.6〕いろいろなデータ表現

(例)

$$10\text{進法} \cdots 100_{10} = \underline{1} \times 10^2 + \underline{0} \times 10^1 + \underline{0} \times 10^0$$

$$2\text{進法} \cdots 100_{10} = \underline{1} \times 2^6 + \underline{1} \times 2^5 + \underline{0} \times 2^4 + \underline{0} \times 2^3 + \underline{1} \times 2^2 + \underline{0} \times 2^1 + \underline{0} \times 2^0 = 1100100_2$$

$$8\text{進法} \cdots 100_{10} = \underline{1} \times 8^2 + \underline{4} \times 8^1 + \underline{4} \times 8^0 = 144_8$$

$$16\text{進法} \cdots 100_{10} = \underline{6} \times 16^1 + \underline{4} \times 16^0 = 64_{16}$$

$$\begin{array}{l} \text{2進数 } 1100100_2 \text{ を8進数として見るには} \\ \rightarrow \begin{array}{c} 1100100 \\ \frown \frown \frown \\ 1 \quad 4 \quad 4 \end{array} \rightarrow 144_8 \end{array}$$

$$\begin{array}{l} \text{2進数 } 1100100_2 \text{ を16進数として見るには} \\ \rightarrow \begin{array}{c} 1100100 \\ \frown \frown \\ 6 \quad 4 \end{array} \rightarrow 64_{16} \end{array}$$

〔図1.7〕符号のついた整数の表現

### ① リニア(絶対値)表現

|     |          |    |

|-----|----------|----|

| 255 | 11111111 | FF |

| ↓   | ↓        | ↓  |

| 0   | 00000000 | 00 |

(10進) (2進) (16進)

### ② 2の補数

|     |          |    |

|-----|----------|----|

| 127 | 01111111 | 7F |

| ↓   | ↓        | ↓  |

| 1   | 00000001 | 01 |

| 0   | 00000000 | 00 |

-1 11111111 FF

↓ ↓ ↓

-128 10000000 80

### ③ 1の補数

|     |          |    |

|-----|----------|----|

| 127 | 01111111 | 7F |

| ↓   | ↓        | ↓  |

| 0   | 00000000 | 00 |

| -1  | 11111110 | FE |

↓ ↓ ↓

-127 10000000 80

☆「ゼロ」が00hとFFhの2通りに表現されてしまう。

### ④ 符号(サイン)+絶対値

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ↑ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ | ↓ |

サイン、ここは7ビットの

ビット 絶対値

(0…+

1…-)

|     |          |    |

|-----|----------|----|

| 127 | 01111111 | 7F |

| ↓   | ↓        | ↓  |

| 0   | 00000000 | 00 |

| -1  | 10000001 | 81 |

↓ ↓ ↓

-127 11111111 FF

☆「ゼロ」が00hと80hの2通りに表現されてしまう。

(255段階になってしまう)

[図1.8] 加算器(アダ)の構成

## &lt;ハーフ・アダ&gt;

| 入力 |   | 出力       |     |

|----|---|----------|-----|

| A  | B | $\Sigma$ | キャリ |

| L  | L | L        | L   |

| L  | H | H        | L   |

| H  | L | H        | L   |

| H  | H | L        | H   |

(b)

EXORと

一致

ANDと

一致

ハーフ・アダ(半加算器)の機能は(a)のようになる。真理値表は(b)のようになる。ここで出力 $\Sigma$ はAとBのEXOR(排他的論理和),

キャリ出力は

AとBのAND(論理積)

になっている。したがって、ハーフ・アダの回路としては(c)のようになる。

## ● 1ビットのフル・アダ

| 入力 |   |     | 出力       |      |

|----|---|-----|----------|------|

| A  | B | Cin | $\Sigma$ | Cout |

| L  | L | L   | L        | L    |

| L  | L | H   | H        | L    |

| L  | H | L   | H        | L    |

| L  | H | H   | L        | H    |

| H  | L | L   | H        | L    |

| H  | L | H   | L        | H    |

| H  | H | L   | L        | H    |

| H  | H | H   | H        | H    |

(b)

フル・アダ(全加算器)の機能は(a)のようになり、真理値表は(b)のようになる。つまり入力のA, B, キャリ入力という三つが対等の関係になる。フル・アダは二つのハーフ・アダとORゲートにより(c)のように構成できる。

## &lt;ルックアヘッド・キャリ&gt;

入力の組み合わせから、各ビットの $\Sigma$ の計算と同時に $C_{out}$ を出力してしまうための回路

(4ビット・フル・アダ 283の等価回路)

[図1.9] 乗算器(マルチプライヤ)の構成

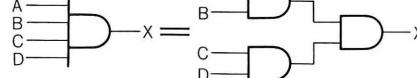

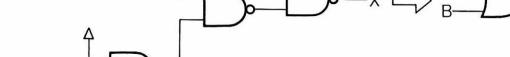

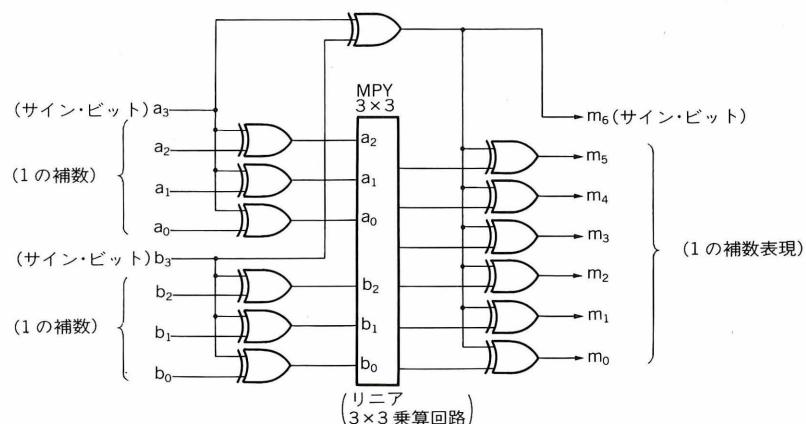

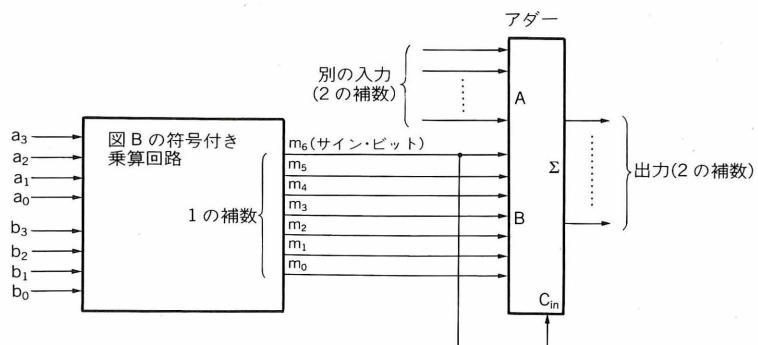

## [コラム] 解答 1

## 符号付き乗算回路の例

図Aは、リニア表現の3ビット・データ同士を乗算する回路を、加算器によって構成した例です。それぞれ(0 ~ 7)の値をとる入力データの乗算結果(0 ~ 49)が、6ビット・データとして出力されます。

つぎに、このリニア乗算回路を使って、「1の補数」表現の4ビット・データ同士を乗算する回路を構成した例が、図Bです。最上位ビットは「サイン・ビット」ですから、それ以下のビットのデータをサイン・ビットによって反転することで、符号以外の部分をリニア乗算します。符号部分の乗算というのは、ちょうどエクスクルーシブ・オア演算に相当します。そして乗算結果を、再び符号変換によって「1の補数」に戻しています。ここでは、ずらりと並んだエクスクルーシブ・オア・ゲート群が、「制御信号によってデータを反転するゲート」として活用されています。

コンピュータでよく使われる「2の補数」にするには、このデータにさらに、「結果が負の場合のみ、1を加える」という操作が必要になります。ところが、一般にこのような乗算回路の出力というのは、他のデータとさらに加算(累算)される場合が非常に多いために、図Cのように、次段の加算器のキャリ入力として、この出力のMSB(サイン・ビット)を与えることで、そのまま2の補数形式に変換してしまいます。

[図A] リニア表現の乗算回路(例: 3ビット×3ビット)

## [飛び石コラム] おすすめ BOOKS ②

### ● SE スキルアップ NOTE —上級ソフトウェア技術者になるための実践計画

小暮裕明 著 CQ 出版社

この本は、若手のソフトウェア技術者が、SE(システム・エンジニア)としてスキルアップしていくための指針として、10年計画で各種のSE技術を体得していく段階について解説しているものです。じつは、本書はこの本のハードウェア版として企画されたものなのですが、両方を読み比べてみるのも面白いかもしれません。

### ●情報と文化

情報文化フォーラム 編 NTT 出版

情報、生命、進化、文化、芸術、真理、哲学といった

種々雑多なテーマを横断的に網羅してしまおう、という大胆・壮大な試みの本です。個々の分野では掘り下げる不足している不満もあるのですが、自然科学から情報科学、そして美学・哲学・論理学から文明論までを意欲的に追求する姿勢は、優れた読み物として称賛できます。

### ●人間工学 —— 装置設計者のための —

W.E. ウドソン 著 青木和彦・野本明 共訳

コロナ社

マン・マシン・インターフェースとか、ヒューマン・インターフェースといった視点の歴史は非常に長いものです。この本はかなり古い(古書店で入手しました)ので、あるいは現在ではこの分野の別の本を捜す必要があるかもしれません、いずれにしても「人間工学」について知ってみると、とても勉強になると思います。

[図B]

符号付き乗算回路

(1の補数、4ビット×4ビット)

[図C]

図Bの符号付き乗算回路

の利用法

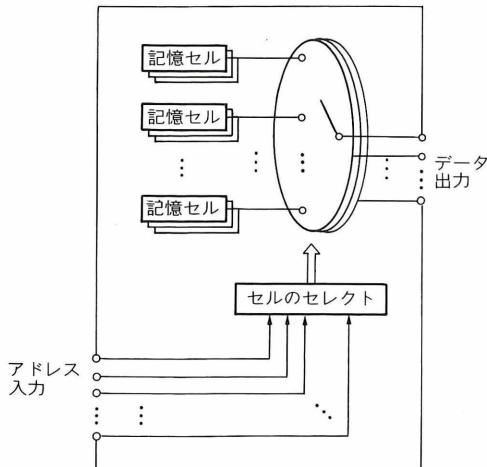

## ●記憶回路

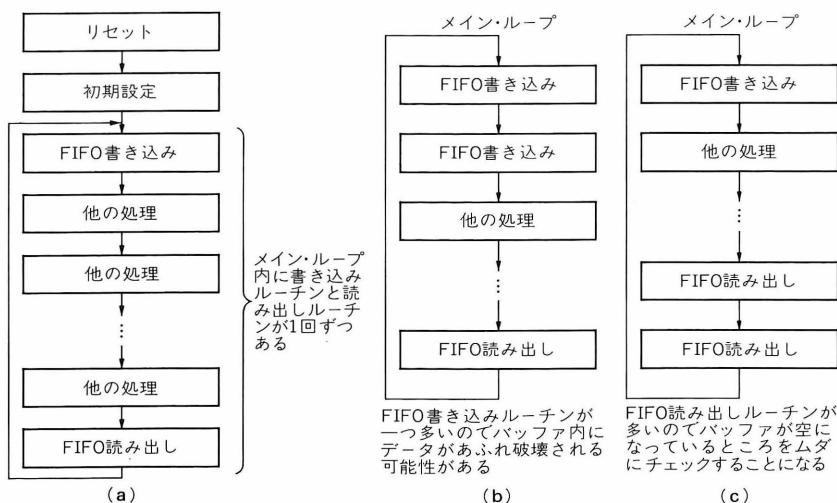

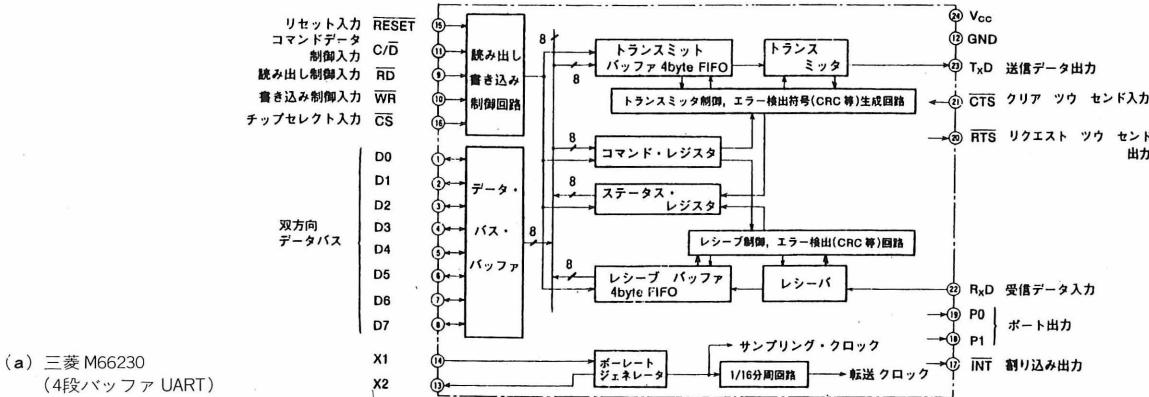

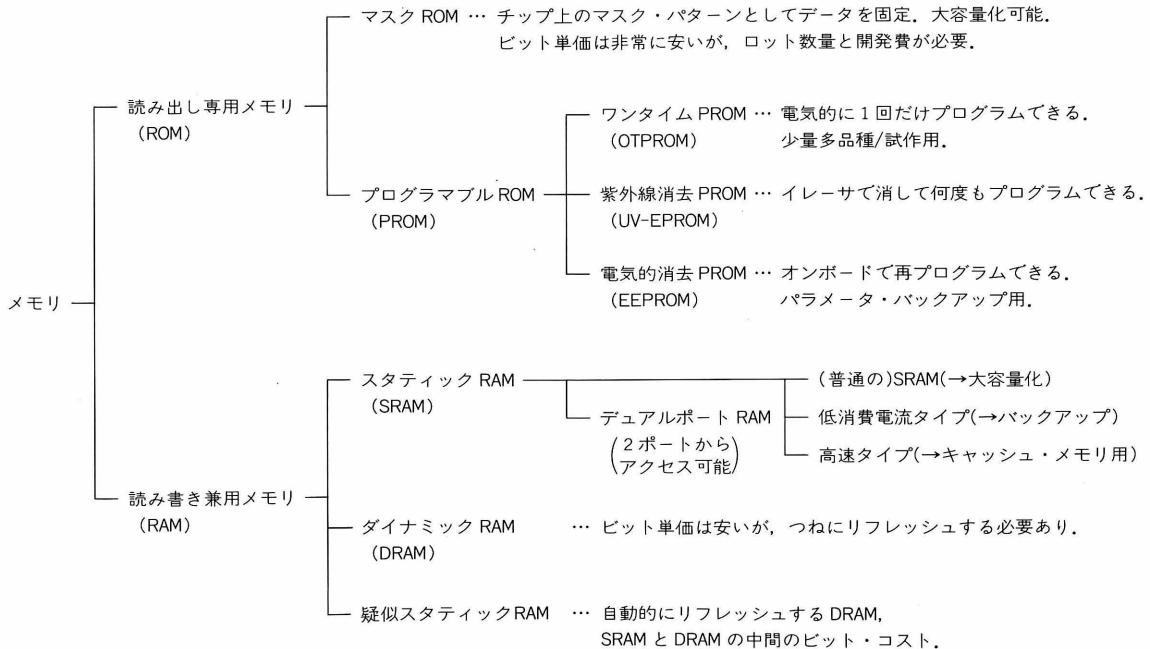

先にふれたフリップフロップ回路は、入力データをクロックで確定させてつぎのクロックまで保持する、という意味では、もっとも基本的なメモリ(記憶)回路です。そして F/F を複数個並べたラッチ回路は、まさに 1 アドレスのメモリ回路そのものです。また、シフト・レジスタを複数ビット並べた、あるいはラッチを多段重ねたと見ることができる FIFO 回路もメモリ回路の一種です。

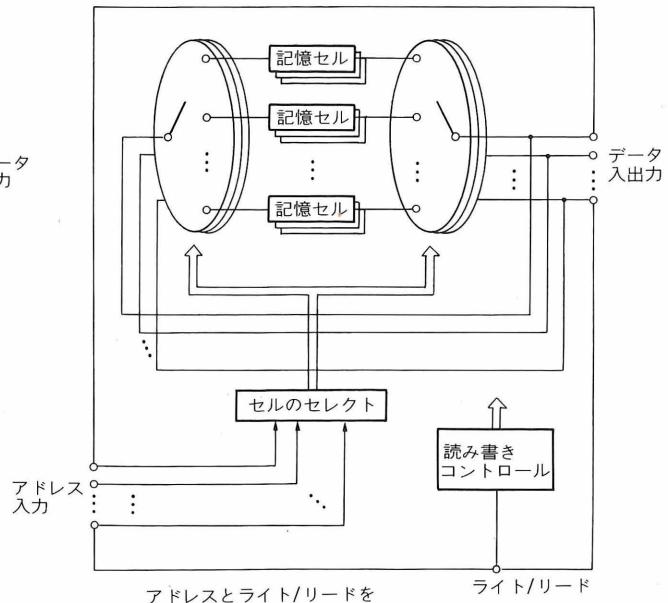

マイコン・システムでは、図1.10のように、内部の記憶セルをブラックボックス(F/F であるとは限らない!)にした LSI として、メモリ(RAM や ROM)が中

心的な活躍をします。ここではメモリの理解のために、やや意外な方法ですが、「ROM や RAM を単独で(CPU 回路以外に)使う」ことを考えてみましょう。

非 CPU 回路にメモリ IC を使ってみようすると、その情報容量の膨大さに驚かされます。たとえば 8464 という RAM は、374 というラッチにして 8192 個分のデータを読み書きすることができ、27256 という PROM は、8 ビットの DIP スイッチを 32768 個を並べたことに相当します。もちろん、これらの情報は厳密に「同時に」扱うことはできませんが、「順序回路」のテクニックの応用課題としては格好のものです。

[図1.10] 「メモリ」の考え方(ブラックボックス)

アドレスを与えると、内部の記憶セルのデータがoutputから出てくるブラックボックス

(a) ROM

アドレスとライト/リードを与えるブラックボックス

(b) RAM

## アナログ技術の基本

### ●アナログ技術の奥はとても深い

ここではアナログ回路技術の「ごく一部」について、基本技術のチェックポイントを考えましょう。「一部」と強調したのは、アナログ技術というのはデジタルよりも奥が深く、限られた誌面では十分に掘り下げきれないからです。エレクトロニクスの技術者にとって、アナログ技術のセンスというのは永遠の課題であり、ベテランのアナログのノウハウこそ、フレッシュマンにとって最大の目標であると思います。

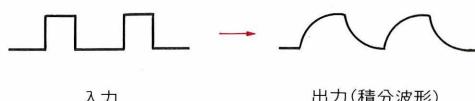

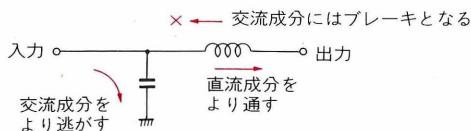

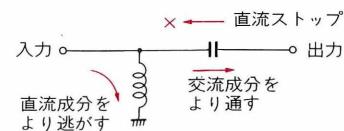

### ●受動回路・能動回路

最初に必要なのは、アナログの基本となる「受動回路」の理解です。これは、抵抗とコンデンサとコイルの組み合わせに対して、電気信号がどういう振る舞いをするか、という「定性的な理解」のことです。いきなり電気系学科のような複素ベクトルや偏微分方程式などは不要で、まず最低限のアナログのセンスとしては、図1.11のような、アマチュア無線の試験用に小学生が覚える程度で十分です。

また、トランジスタによる「能動回路」のノウハウ

は、これまでのエレクトロニクス技術者の領域では中心的なものでした。しかし筆者は、マイコン・システム技術のフレッシュマンにとって、この知識は「あと回しで結構」とあえていしまいましょう。なぜなら、

●技術的に獲得すべき、プライオリティのより高いものが他にも多い

ということが第一ですが、

●知らなくても、とりあえずは何とかなる

という第二の理由もあるからです。というのも、後述するOPアンプやアナログICの普及(高性能・ローコスト・多種化)によって、マイコン・システムでは、ディスクリートのトランジスタ回路を具体的に設計しなくても、まず当面はほとんど困らない、という状況になりつつあるからなのです。

デジタル回路で進んでいる「回路のブラックボックス化」という流れは、アナログ回路でも本流となっています。かつての「トランジスタ回路テクニック」を知らないとも、それぞれに要求される機能を1チップで実現してしまう、安くて高機能なアナログICがたくさんあります。たんなるバッファ・アンプ、たんなる電圧変換、たんなるインピーダンス変換回路であっても、理想特性のOPアンプを使えば、バイアス回路とかの余計な心配も不要で、全体の部品点数も減って

[図1.11] アナログ能動回路の基本

#### • 基本部品

|  |       |                         |                                                 |                           |

|--|-------|-------------------------|-------------------------------------------------|---------------------------|

|  | 抵抗    | → オームの法則                | $I = \frac{E}{R}$                               | (抵抗成分は交流でも直流でもかわらない)      |

|  | コンデンサ | → 容量リアクタンス<br>(交流成分の抵抗) | $X_C = \frac{1}{\omega C} = \frac{1}{2\pi f C}$ | (直流は通さない、周波数が上がると抵抗成分が減る) |

|  | コイル   | → 誘導リアクタンス<br>(交流成分の抵抗) | $X_L = \omega L = 2\pi f L$                     | (周波数が上がると抵抗成分が増加する)       |

#### • 組み合わせの例

##### 〈ローパス・フィルタ〉

##### 〈ハイパス・フィルタ〉

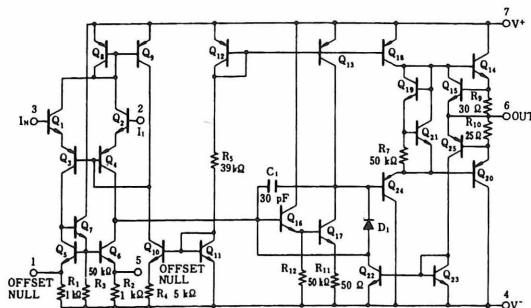

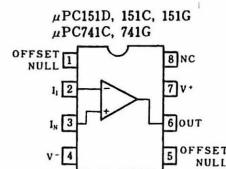

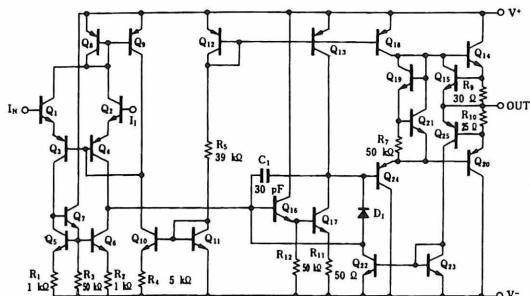

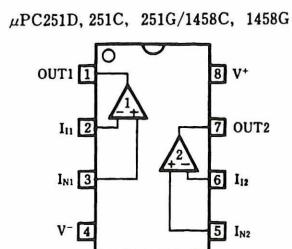

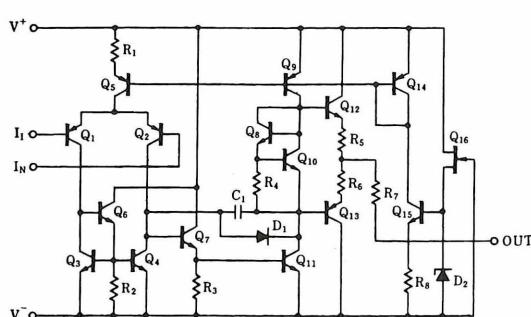

[図1.12] OPアンプの例(日本電気データブックより)

等価回路

(a) 741(シングル)

端子接続 (Top View)

等価回路 (1/2回路)

(b) 1458(デュアル)

端子接続 (Top View)

等価回路 (1/4回路)

(c) 458(クワッド)

端子接続 (Top View)

くれます。

誤解のないようにいいますが、もちろん「トランジスタ技術は不要」ということではありません。しかし、デジタル技術よりもファジーなこの世界に不安をもつことなく、いずれあとでわかつてくれればいい、というぐらいの気持ちでいきましょう。

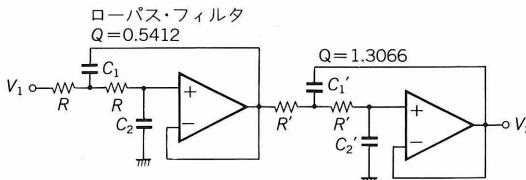

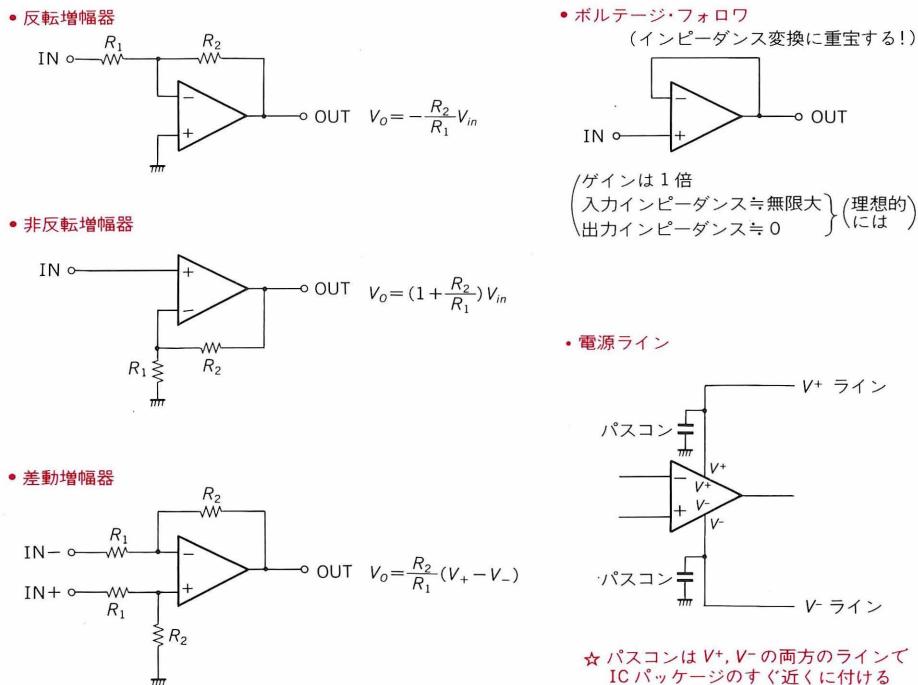

### ● OP アンプ回路

現在のアナログ回路の主役は、間違いなく各種のOPアンプICです。図1.12の等価回路のように、単一のトランジスタ増幅器の電気的特性の欠点を補うために、1個のOPアンプの中には多数のトランジスタが入っていて、いわゆる「増幅器の理想特性」をほぼ実現しています。1パッケージに2個とか4個のアンプがあったり、単一電源・低電圧電源・省電力タイプ・超高速タイプのものなど、種類もとても多くあります。これらのOPアンプを、まずは「完全にブラックボックスの便利なIC」として使ってしまえる、というのが重要なところでしょう。

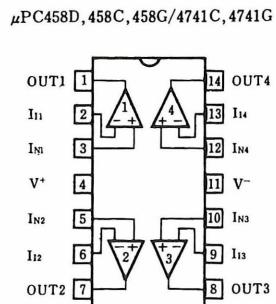

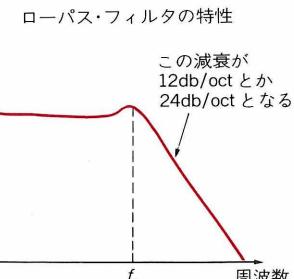

### ● フィルタ回路での例

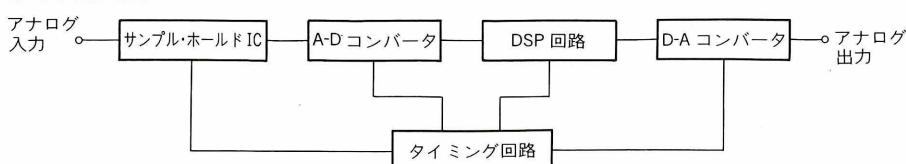

- マイコン・システム技術の視点からすると、従来はOPアンプを複雑に組み合わせて構成していた回路機能が、デジタル化によってかなりシンプルに実現されていきます。たとえば図1.13のように、

- 特性の揃った複数個のOPアンプ

- 理論的に要求される半端な(なかなかカラー・コードに一致しない)値の抵抗

- 高精度のコンデンサ(数値の要求は抵抗と同様)を、多数(多段)並べた従来の「アクティブ・フィルタ回路」というものが、

- A-D 変換

- DSPによるデジタル・フィルタ

- D-A 変換

- という構成によって実現できます。これによって、

- 事実上アナログでは不可能であった理想的なフィルタ特性が実現できる

- 無調整・コンパクトに実現できる(DSPのプログラム次第)

〔図1.13〕 フィルタ回路の構成の例

(宮崎仁、「アクティブ・フィルタの実際」、『トランジスタ技術』、1991年8月号より)

#### 〈アナログ方式〉

$$\begin{cases} b = \frac{1}{R} \sqrt{\frac{1}{C_1 C_2}} \\ Q = \frac{1}{2} \sqrt{\frac{C_1}{C_2}} \\ \frac{C_1}{C_2} = 4Q^2 \\ f_c = 1000 \text{ (Hz)} \\ C_2 = C_2' = 1000 \text{ (pF)}, b = 2\pi f_c = 6283.2 \text{ (rad/s)} \\ C_1 = 1172 \text{ (pF)}, C_1' = 6829 \text{ (pF)} \\ R = R_2' = 147.0 \text{ (k}\Omega\text{)} \end{cases}$$

#### 〈デジタル方式〉

(実際にはアンチエイリアシングの LPF が入る)

といったメリットが得られる時代になってきました。つまり、OPアンプの仕事が、システム回路の中心から、デジタル・システムの「周辺部分」へと移っているわけです。

このような背景の中では、図1.14のようなOPアンプ回路の基本を知って、とりあえずアナログ信号のバッファ回路として活用できることが、まず必要になります。もちろん紙の上だけでなく、実際に手を使って実験しておくことが大切で、TTLなどのデジタル

回路との違い、電源ラインの注意、ノイズなどのテクニックもあります。つぎのセンサの実験とともに、少ししづつ慣れていきましょう。

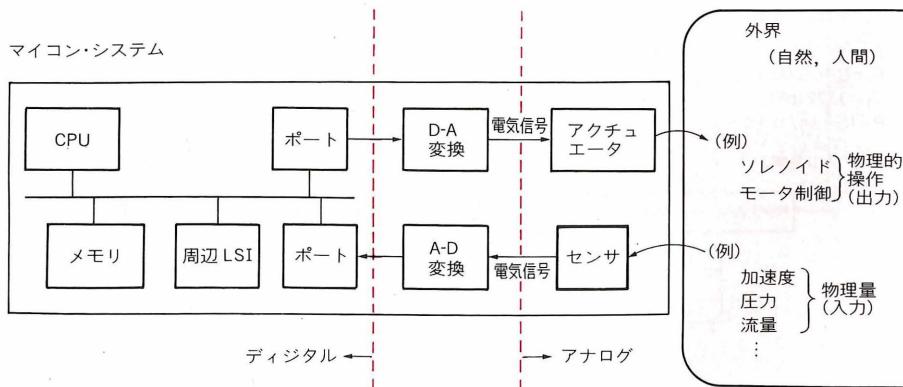

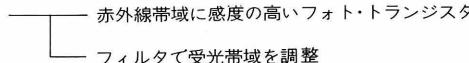

### ●センサ：外界との接点

マイコン・システムの中心のCPUはデジタルですが、人間の世界、あるいは自然界の物理現象はすべてアナログです。そこで図1.15のように、「アナログ↔デジタル変換」という処理がつねに必要になります。

〔図1.14〕 OPアンプ回路の基本

★パスコンは  $V^+$ ,  $V^-$  の両方のラインで ICパッケージのすぐ近くに付ける

〔図1.15〕 マイコン・システムと周囲との関係

そして、さらにその上流で、システムが外界のアナログ情報を取り込むために最初に必要なのがセンサということになります。

基本的には、ここでのセンサとは「いろいろな物理量を電気的な値に変換する」ものを指します。物理量というと大袈裟ですが、圧力とか温度とか明るさといった、人間の五感で検出できるもの、あるいは超音波や赤外線のようなものです。これらの情報がすべて電圧として出してくれるといいのですが、たとえば抵抗値とか周波数とかで得られるものも多く、この場合デジタルで取り込むために、まず「アナログ-アナログ変換」(これを「シグナル・コンディショニング」とも

いう)をする必要があります。

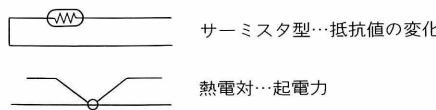

図1.16のように、センサの種類は文字通り(?)千差万別で、さらに同じ種類であっても、たとえば

- 液体圧力計測専用の測定器に使われる圧力センサ

- スポーツ腕時計の水圧表示のための圧力センサ

の二つを比較すると、部品としてのセンサ単体の値段に1000倍くらいの開きがあります。その分、計測レンジ、精度、安定性、再現性、応答速度、寿命などの特性がいろいろと違うわけです。新しいLSIと同じように、機会があるたびに各種のセンサをサンプル実験してみることが、「センサのセンス」獲得の近道でしょう。

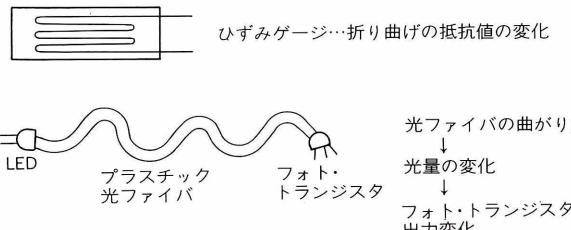

[図1.16] センサの例

• 温度センサ

• 圧力センサ

• 加速度センサ

• 赤外線センサ

## マイコン・システムの3形態とトレードオフ

ここでは、マイコン・システムの具体的な形態として、ボード上にシステムが搭載されているものを考えておきます。いわゆる「ボード・マイコン」や、普通のパソコンがこの分類に入ります。これら以外に、最近の技術は「システム全体を1チップ上にまとめる」という、「システム・オン・チップ」を誕生させていますが、これについては【ASIC技術】の項で紹介します。

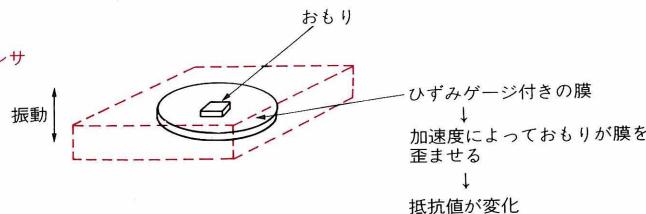

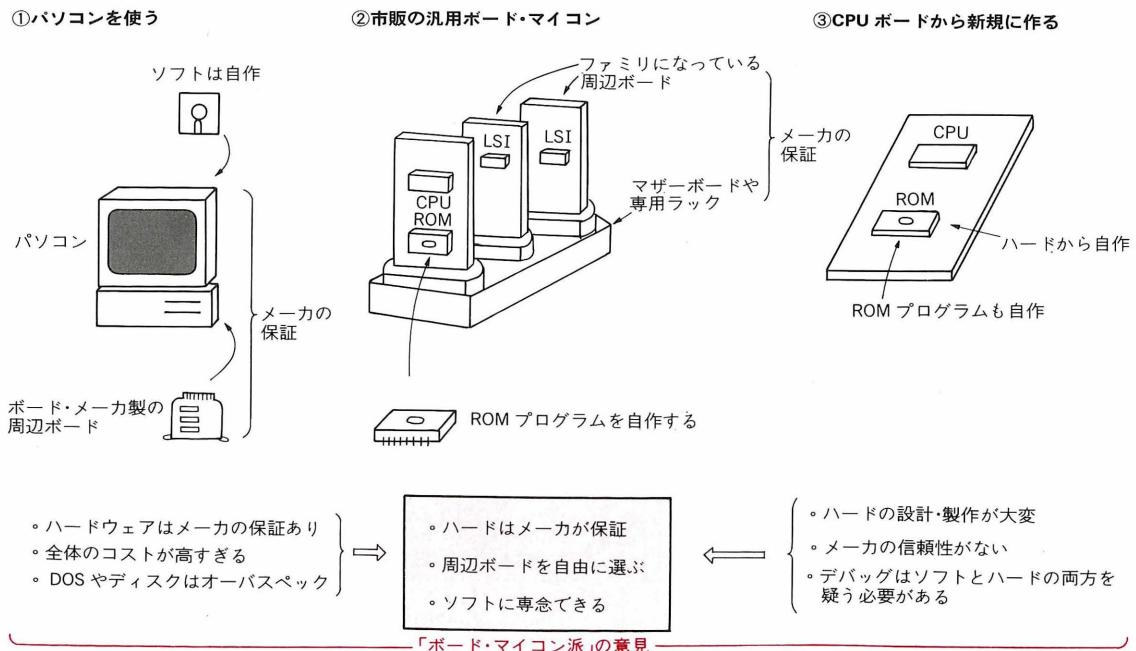

### ●マイコン・システムの3形態

なにか新しくマイコン・システムを開発する場合には、大きく3種類の形態が考えられます。これは図1.17のように、

- パソコンを使う(拡張ボードを使う)

- 市販のボード・マイコンを使う

- オリジナルのCPUボードを開発する

- というもので、使用言語の種類を別にすれば、いずれもソフトウェアは自分で開発することになります。

あるテーマが与えられて、新しいマイコン・システ

ムを開発していく場合には、この3種類のどのスタイルを採用していくか、という判断が必要になります。もちろんこれら3種類には、それぞれの長所と短所とがあって、いずれを採用するかは、それぞれのケースで何を優先するかによって異なります。たとえば、

- 開発期間が非常に短い(確実に仕上げることを優先)

- 実験・設計・試作段階での初期開発費用をなるべく抑える

- 場合により同じシステムを量産する可能性もある(一品料理とは限らない)

- 大量生産時の低コスト実現が最優先

- システムが何度もバージョンアップされて長期間使用される見込み

- 海外(極端には宇宙)で使用されるので、無補修の信頼性が第一

- 悪環境なので、故障しても簡単に修理できるようにしたい

- などのいろいろな条件が課せられるのが普通です。そこで、これらの制約要因に応じたトレードオフを考慮しながら、この3種類の形態も使い分けなければなりません。図1.17に書かれている「特徴」は、どちらかというと「ボード・マイコン派」の意見に重点を置いてみた視点の例になりますが、ちがう角度から見ると、

(図1.17) 新しくマイコン・システムを開発する場合の3種類の形態

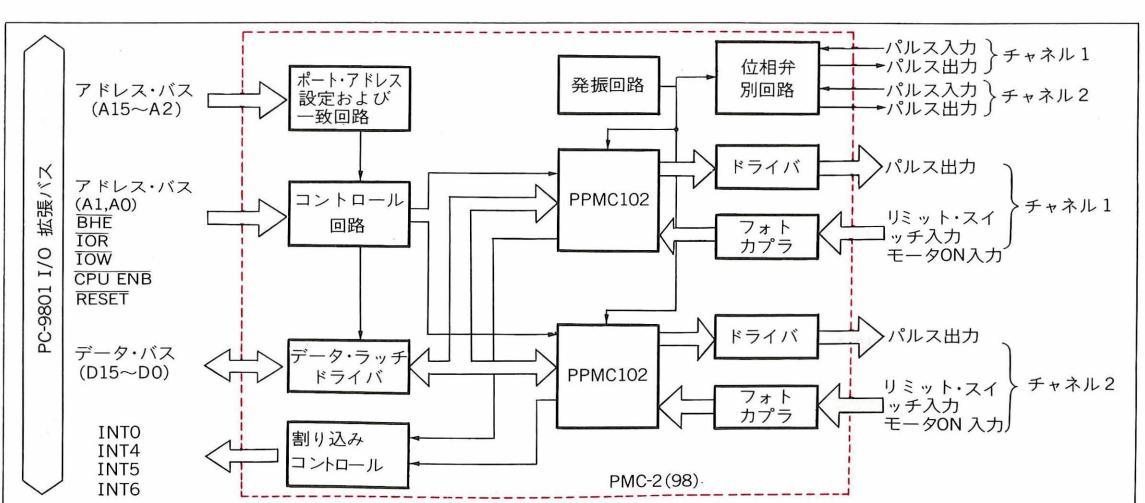

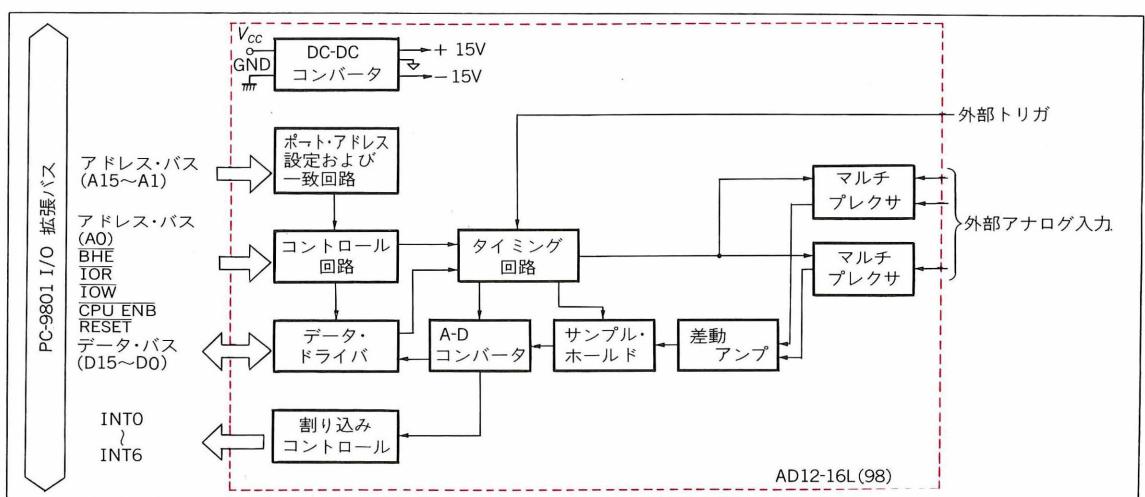

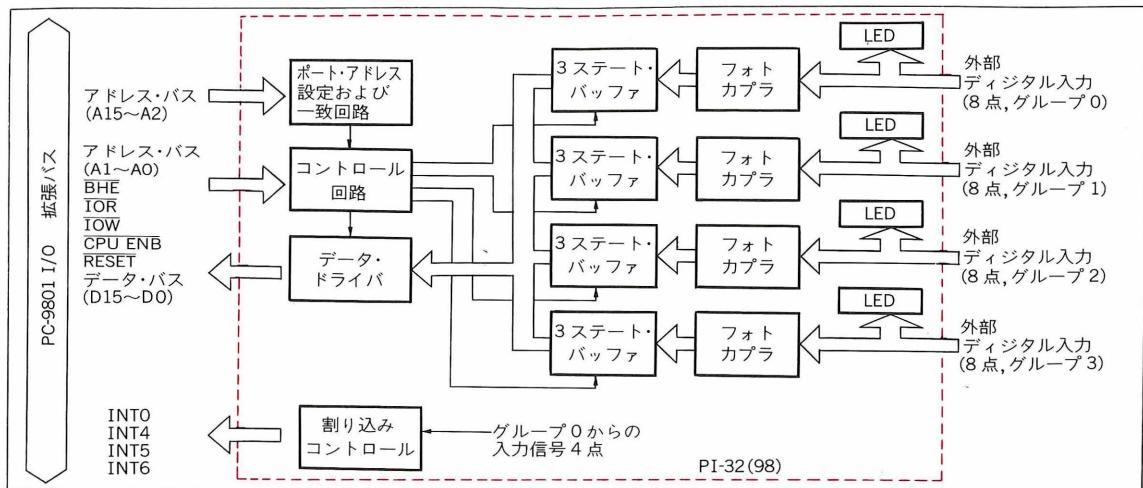

[図1.18] PC-9801バスの周辺ボードの例(コンテック社データブックより)

3派それぞれにメリットとデメリットがあります。

### ● [パソコン+ボード] システム

パソコン自体はプリンタとか RS-232-C とかディスプレイなどのコネクタぐらいしかもっていませんから、一般の用途のために外部とインターフェースするためには、なんらかの拡張方法が必要となります。そこで、パソコンの拡張スロットに挿入する各種の拡張ボードが、多くの専業メーカから提供されています。

図1.18は、パソコン PC-9801 シリーズ用のボードのデータブックから引用した例で、(a)は32ビットのデジタル入力ポート、(b)は多チャンネルの A-D コンバータ、(c)はステッピング・モータの制御ボードのブロック図です。これらはほんの一例で、PC-9801 シリーズであれば数社から数百種類のボードが提供されていて、わざわざ自作する必要がほとんどないほどです。この種のボードは、データシート、保証書、シリアル・ナンバーがついていて、しっかり品質が保証されていることと、その代償として「かなり高価」(自分で作った場合の数倍から10倍以上)である、などが特徴です。実験室の試作用にはオーバスペックなのですが、組み込み機器や FA を意識したことだと思えば、なんとか納得できます。

### ● [パソコン+ボード] システムの長所と短所

このような方法で新しいマイコン・システムを構築するというのは、かなり大げさで、明らかにコストもかかる方法です。短所は、

- パソコン本体のコストがまず「部品」としては高い

- 拡張ボードのコストもかなり高い

- パソコンの図体が邪魔になり、機動性・可搬性に乏しい

- (DOS 上の高級言語でソフト開発すると) アセンブラーよりも遅い

- などということになります。

- しかし、パソコンを活用するための長所も多くあり、

- ハードウェアはほぼすべての部分に、メーカの信頼性の保証済み

- 同じシステムを複製する場合にとても簡単(ハードを買い増せばよい)

- パソコンの豊富な情報量(キーボード入力・ディスプレイ出力)を活用できる

- ディスク・ドライブ、ハード・ディスクなどの記憶

### 媒体を活用できる

- ソフトウェア環境の充実により、短期間に開発可能

- バージョンアップなどのソフト修正が容易などの点も捨てがたいものです。また、最近のノート・パソコンやブック・パソコンを活用すれば、機動性も大きく改善されます。

パソコンを「部品」として使う、という発想はなかなか面白いものですが、「お役所」からの仕事の受注の場合に活躍する、という裏話もあります。「カネに糸目をつけない」、「開発期間と信頼性を最優先」といったプロジェクトでは、この [パソコン+ボード] をまず最初に検討してみるべきでしょう。

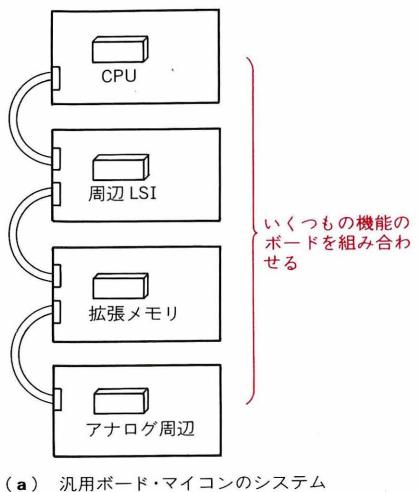

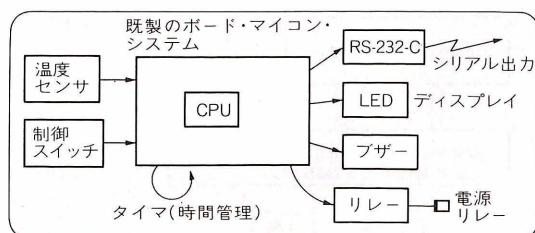

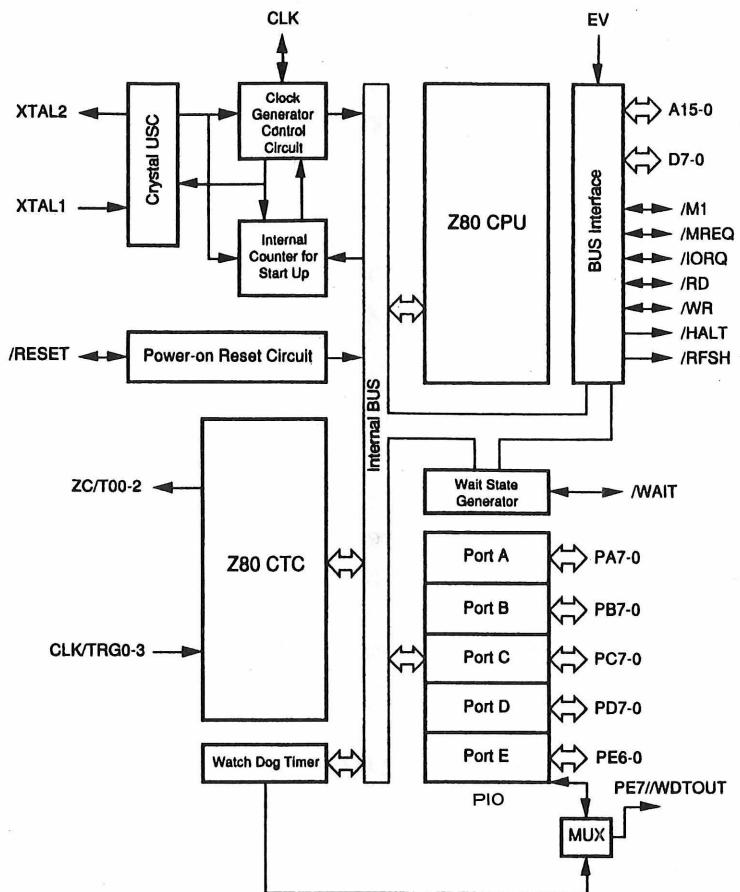

### ● 「ボード・マイコン」によるシステム

パソコンとは違って、ボード上にCPUと周辺LSIを搭載した、汎用の「ボード・マイコン」という製品を提供している専業メーカも多くあります。これには、メインCPUボードと各種周辺ボードとを組み合わせて使うシステムと、図1.19のように、1枚のボード上にコンパクトに各種機能をまとめたものとがあります。最近のCPUの発展にしたがった傾向としては、後者の1ボード汎用タイプのものが主流になりつつあるようで、図1.20にあるように、カード・サイズ(名刺サイズ)といっても、従来の8ビット・パソコンを軽く凌駕するくらいの、相当の能力を盛り込んでいます。

これらのボード・マイコンは、「CPUは68000シリーズ、共通バスはVMEバス」といった本格的なFA用ボードを別にすると、かなりのローコストで提供されています。そしてもちろん、ボード単体についての品質はメーカが保証しています。しかし、パソコンのDOSやコンパイラといった強力なソフトウェア環境とか、キーボード・ディスプレイなどの周辺入出力機器、さらにはディスク・ドライブのような外部記憶装置をもたないのが普通です。そこでマイコン・システム技術者としては、これらのソフトウェアとハードウェアの条件について、自分で解決して設計・開発ができなければなりません。開発のためのROMモニタ(後述)の付属したボードもありますが、場合によっては「モニタを自作する」必要もあるのです。

### ● ボード・マイコンによるシステムの長所と短所

上にあげた特徴から明らかですが、マイコン・システムとして汎用ボード・マイコンを採用する場合の長

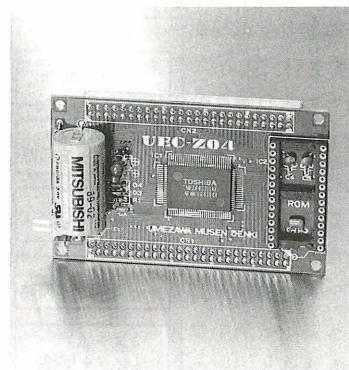

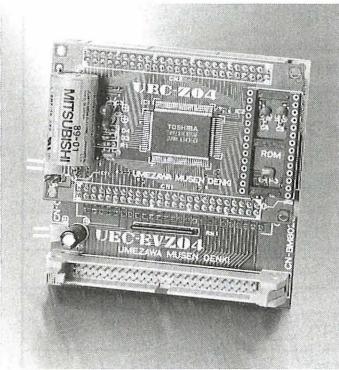

[図1.19] 汎用ボード・マイコンの例(梅沢無線電機製)

■UEC-Z01 9,100円(273)

UEC-Z02 9,800円(294)

• CPU84C015(Z80)

RAM 8Kバイト クロック 6MHz

システム・リセット バッテリ

バックアップ内蔵

■UEC-Z04 9,400円(282)

• CPU84C011(Z80)

RAM 8Kバイト クロック 4MHz

システム・リセット バッテリ

バックアップ内蔵

■UEC-EV01 22,000円(660)

UEC-EV02 22,000円(660)

UEC-EV04 22,000円(660)

開発ボード

■BM8027A 35,000円(1050)

015用アダプタ・ボード

■BM8026A 43,000円(1290)

011用アダプタ・ボード

所としては、

- ローコストである

- ボードの品質が保証されている

- 同じシステムを複製する場合に簡単(ボード・マイコンを買い増せばよい)

- システムの機能としてオーバスパックの無駄がない

- アセンブリで最適・高速なソフトウェアを開発できる

- というような点がありますが、逆に短所としては、

- 周辺ハードウェアを自作する必要がある

- ソフトウェアの環境はかなり機械寄りである

● ソフトの改訂は普通はROMの交換となる

- ハード、ソフトの開発手法に工夫が必要となる

というような点があげられます。

[パソコン+ボード] システムと比べてみると、エンジニア自身の技術力として、かなりの範囲の知識と力量が要求されています。ただし、技術的な壁をクリアしてこの方法でシステムを構築した場合には、たとえばパソコン応用のシステムの10倍以上のコスト・パフォーマンスを上げられるのが普通です。そのために、多くのシステムハウスが、各種の「開発支援ツール」を駆使して、この手法をフルに活用しています。

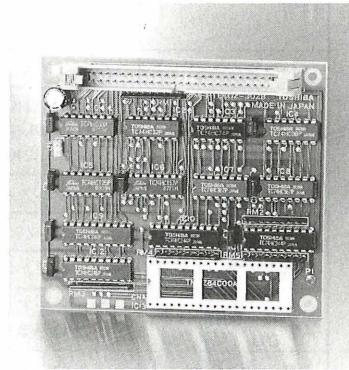

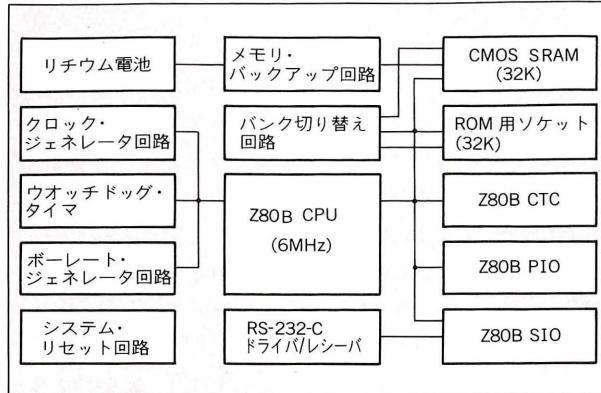

〔図1.20〕汎用ボード・マイコンの技術資料の例(梅沢無線電機製)

● ブロック

● 基本仕様

| 項目            | 内容                                                                                                                                                              |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU           | ・ TMPZ84C015AF-6 (東芝製)<br>Z80B CPU/PIO/SIO/CTC/GCC : クロック・ジェネレータ・コントローラ/<br>WDT : ウォッチドッグ・タイマ                                                                   |

| クロック          | ・ 6.1440MHz (内蔵取り付け水晶は 12.2880MHz)                                                                                                                              |

| メモリ           | ・ PROM 32K×8 ビット (27256/27C256) アドレス 0000H～7FFFH 32K バイト<br>基板埋め込み型超ロープロファイル丸ピン・ソケット付き (高さ 0.8mm)<br>・ SRAM 32K×8 ビット (TC55257AFL-10L) アドレス 8000H～FFFFH 32K バイト |

| バックアップ        | ・ リチウム・バッテリによるメモリ・バックアップ回路内蔵                                                                                                                                    |

| バンク切替え        | ・ メモリ・バンク切り替え回路内蔵 (切替え専用 I/O ポート回路内蔵)                                                                                                                           |

| DRAM リフレッシュ   | ・ 64K のほかに、256K チップの DRAM リフレッシュが可能                                                                                                                             |

| 暴走検出回路        | ・ ウォッチドッグ・タイマ(WDT)回路内蔵<br>(CPU 暴走時にシステム・リセット動作可能)                                                                                                               |

| スタンバイ機能       | ・ 各種動作モードをプログラム選択可能 (4種類)                                                                                                                                       |

| リセット          | ・ 電圧検出システム・リセット回路内蔵 M51944B-ML(三菱製)使用                                                                                                                           |

| RS-232-C      | ・ SIO の B チャネル側 RS-232-C シリアル・ドライバ/レシーバ回路内蔵                                                                                                                     |

| ポーレート・クロック    | ・ シリアル通信用に、ポーレート・ジェネレータ回路内蔵 (75～19200 bps)                                                                                                                      |

| 入力/出力インターフェース | ・ プログラマブル入出力ポート ..... 8 ビット × 2 ポート ..... (Z80B PIO)<br>・ プログラマブル・カウンタ・タイマ ..... (Z80B CTC)<br>・ シリアル入出力コントローラ ..... (Z80B SIO)                                 |

| ゲートアレイ        | ・ 54ゲート (プロセス 2 μm, HCMOS シリコン・ゲート・メタル 2 層配線)<br>・ 内容 (各種デコード、ポーレート発生回路など) 内部回路は標準ロジック IC 換算にてすべて公開                                                             |

| 使用コネクタ        | ・ パス・コネクタ・ボード・マウント ソケット (標準 2.54mm スタック・コネクタ) 50極 (金メッキ仕上げ) 9150-4500SC (住友 3M 社製) 2 個                                                                          |

| 外形寸法          | ・ 54(縦)×85.5(横)×14(高さ)mm 40g(重量)                                                                                                                                |

| 電源            | ・ 電源電圧 5V (±10%) 単 1 電源<br>・ 電源電流 標準 50mA (5V 標準動作時)                                                                                                            |

| 使用環境          | ・ 動作周囲温度 0～70°C, 濡度 90% 以下 (ただし結露なきこと)                                                                                                                          |

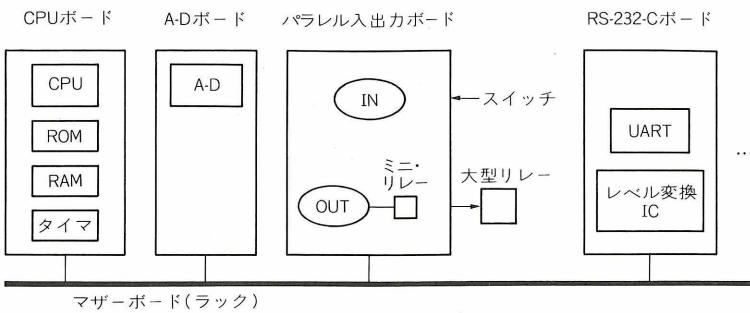

## ●オリジナル CPU ボード・システム

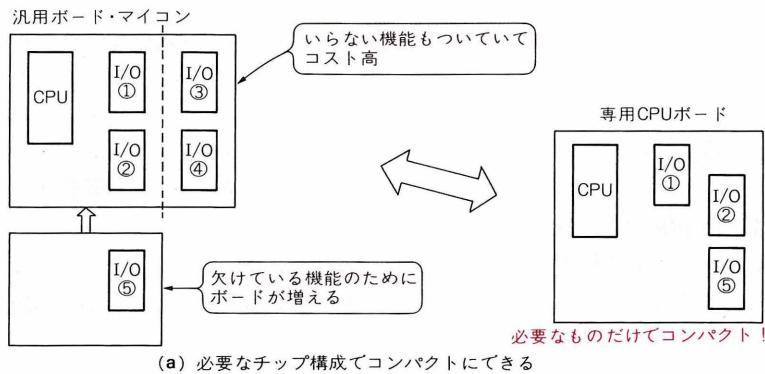

第3の選択肢は、中核となるCPUボードまで、すべてオリジナル設計で実現してしまう、というものです。図1.21(a)のように、汎用のボード・マイコンというものは、メーカが多くのユーザを対象として、ある意味で「最大公約数」的な機能をもたせています。そこで、目的によってはボード上に不要な機能が無駄に置かれたり、わざわざ欠けている機能を増設するためのもう1枚のボードを必要とする、というケースも出てきます。これに対して、オリジナル・ボードであれば、必要な機能だけをコンパクトにまとめたり、将来的な拡張機能の可能性を盛り込むこともできます。

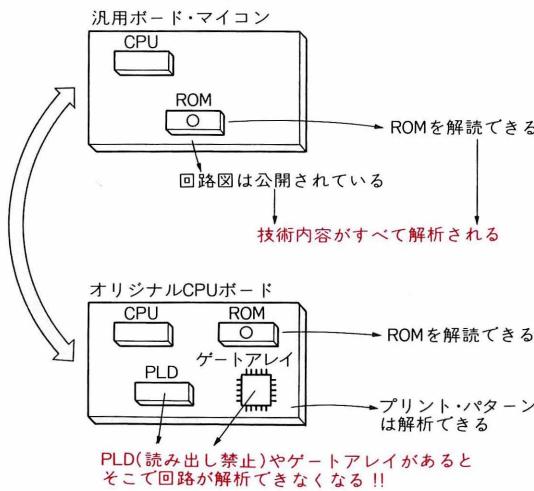

また、図1.21(b)のように、ボード上の回路の「秘密保持」という側面も重要です。汎用ボード・マイコンは一般に回路図が公開されていますから、ボード上の

CPUプログラムを格納したROMを解析すると、このシステムの中身がすべて明らかにされてしまいます。これはライバル・メーカや海賊版を作る者の存在が問題となる場合には、非常にデメリットとなります。ところがオリジナル・ボードであれば、まず基板パターンからの回路解析(4層とか6層の多層基板ではとくに効果的)という壁、さらにゲートアレイや読み出し禁止タイプのPLDを搭載するという壁によって、システムの解析を非常に困難にすることができます。

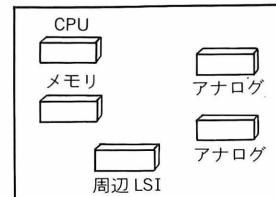

そして、家電機器とか自動車搭載システムなどの組み込み機器の場合には、大量生産が前提となって、なんといってもコストが最大の要因となります。そこで図1.22のように、1枚のボードに必要な機能を収めてしまうこと、場合によってはアナログまで混在させてしまうこと、あるいは基板の形状の条件(たとえばカメ

[図1.21] オリジナルCPUボードのメリット

(a) 必要なチップ構成でコンパクトにできる

(b) 回路上の秘密保持ができる

〔図I.22〕組み込み機器のCPUボード

★技術的にはデジアナ混在は難しい

(例) エアコン

ビデオ・カメラ

炊飯器

エンジン制御システム

⋮

ラ内部の、フィルム状のCPU基板)などがあると、これはオリジナルのCPUボードを開発するしかない、ということになります。

### ●オリジナル・ボードの長所と短所

- まとめると、オリジナル・ボードの長所は、

- もっともローコストで量産製品向き

- 無駄のない、最適なハードとソフトを盛り込める

- システムの秘密を保持できる

- といったものが上げられます。そして短所は、

- ソフトに加えて、ハードウェアの開発も開発者の責

任になる

- 初期投資として、開発期間・開発費用がもっとも多くかかる

- 信頼性は、ハードもソフトも自分で保証しなければならない

- ということになります。筆者の個人的な意見として、あとひとつだけこの方法の「長所」を追加するとすれば、

- エンジニアにとっていちばん面白い(やり甲斐がある)

- というところでしょうか。

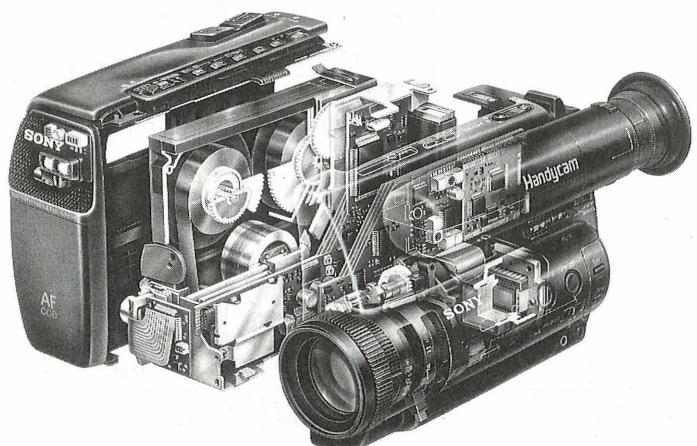

組み込みのオリジナル・ボードの例

(ソニーのビデオ・カメラ、CCD TR55

ハンディカムの内部)

## ヒューマン・インターフェース考

ここでは、マイコン・システムに共通の、外部から情報を入力したり外部へ情報を出力する、という部分に注目してみます。そして、多くの場合に対象となる「人間」を意識した「マン-マシン・インターフェース」とか、最近話題の「バーチャル・リアリティ」などの、やや未来物語の世界についても考えていきましょう。

### ●マイコン・システムの入力方式は？

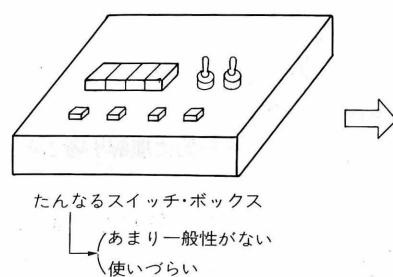

パソコンの文字キーボードのように、「単語」「文章」という豊富な情報を扱えないマイコン・システムの場合、入力手段としてどのような方法があるでしょうか。まず最初に基本となるのは、図1.23のようなスイッチ・ボックスの検討です。フルキーボードはかなり高価で、キャラクタ表示装置も必要となる方法ですから、コンパクトなマイコン・システムとしては適当ではありません。しかし、パラメータの数だけずらりと小さなスイッチ群が並んでいる、というのも、あまり使いやすいものではありません。

そこで「少ないキーで効率的に操作する」という発想は重要です。このいい例がファミコンのコントローラで、基本的には上下左右の十文字キーと、たった二つのボタン・スイッチで、あらゆるゲームをコントロールできます。この場合、表示装置（マイコン・システムであればLCDパネルなど）のほうで、仮想的なカーソルを移動させる、という処理が同時に進行することが必要です。

### ●より人間に近づいた入力手段は？

スイッチといえばONとOFFの2値を検出するものですが、人間の情報を対象とするならば、たとえばピアノ演奏の鍵盤操作（強弱）のような、連続した物理量をアナログ検出することも必要になります。現在のところでは、これを直ちにセンサからA-D変換する方法よりも、ジョイスティックとかマウスなどの、アナログ量を疑似的にデジタル化する入力装置のほうがコスト・パフォーマンスが高いようです。

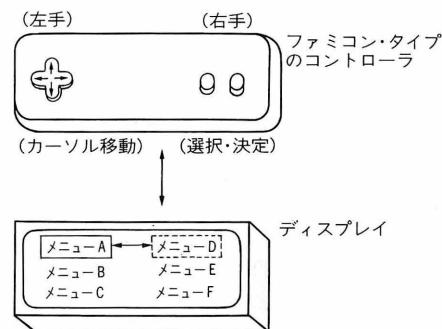

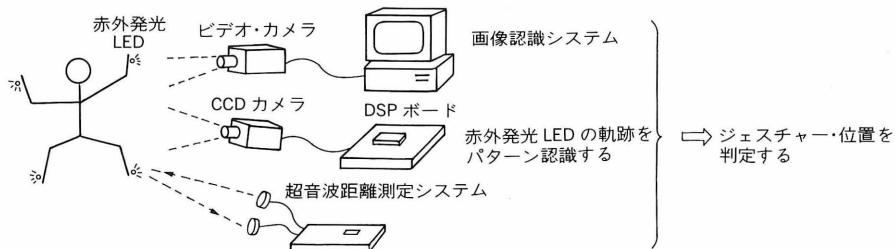

これを押し進めていくと、人間の「ボディ・ランゲージ」（身振りや動作）をシステムが検出するような、高度な入力方法が重要な要素となっていくでしょう。これには図1.24のように、

●具体的に身体に各種のセンサを取り付ける方法

●CCDカメラや赤外線センサなどで、離れたところから検出する方法などがあります。どれか1種類の高価な高精度センサを使おうとしても、人間の動作そのものがきわめてファジーですから、ローコストで低精度のセンサを複数種類、組み合わせる方法が有効でしょう。[チップ]の項にあるように、最近の1チップ・マイコンには、このような用途に最適の機能が内蔵されているものが多いので、機会があれば実験してみたいものです。

### ●システムの入力技術は永遠の課題

ここで技術的に問題となるのは、センサからの入力データの組み合わせから、人間のジェスチャーとしてシステムがその「意味を理解して判断」する、という点です。これは、パターン認識、意味理解、学習による成長、といったAI（人工知能）の重要な課題と直結した

[図1.23] マイコン・システムの入力スイッチ例

★ コントローラのカーソル移動キーと対応してディスプレイのカーソルが動くことが重要！

[図1.24] 人間の「ジェスチャー」を入力する方法

(1) 人間の身体のあちこちにセンサをつける

(2) 離れたところから人間の動きをとらえる

テーマで、多くの研究者が挑戦している先端の技術でもあります。フレッシュマン技術者としては、このアプローチに参加していく気概をもっていきたいものです。

また一方で、研究の歴史が長い入力手段の一つに「音声入力」もあります。これは「\*\*\*しなさい」とマイクに話し掛けると、システムがその音声メッセージを「認識」、「理解」、「判断」してくれる、というもの。技術的にはかなりのハードル(ほとんどが人間の発音の曖昧さに起因する)があって、なかなか汎用システムとしては難しい部分もあるようですが、いずれは入力方法のかなりの部分に活用されるでしょう。

そして究極のセンサといえば、「脳波とテレパシーのセンサ」です。機械が「以心伝心」するかどうかは疑問もありますが、未来を夢見るエンジニアとしては、頭のどこかに置いておきましょう。本当はそうでなくても、一見「人間の心がわかるような」システム、というブラックボックスを作って世間をアッといわせる、などというのはなかなか面白いテーマではないでしょうか。

### ●システムの出力手段：視覚的インターフェースの例

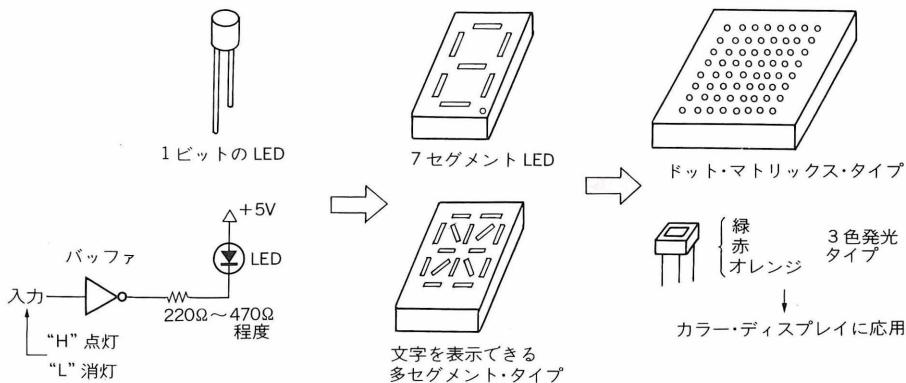

人間の五感の中では視覚がずば抜けて多量の情報を扱えるために、マイコン・システムの出力情報として

は、図1.25のLED(発光ダイオード)、図1.26のLCD(液晶)などの低価格なデバイスが活用されています。また、パソコンの世界ではCRTがテキスト表示からグラフィック表示へ、モノクロからカラーへと、他の周辺装置よりも先に進歩してきました。昔は文字表示だけのゲームがあった、という歴史も、ファミコン世代には理解できないかもしれません。そしてコンピュータ自身の表示能力(解像度・描画速度)の向上によって、マウスやディジタイザ、タッチパネルやトラックボールによって画面上のポイントを指定して、対話的にインターフェースできるようなソフトへと、システムの動作そのものが進歩しています。

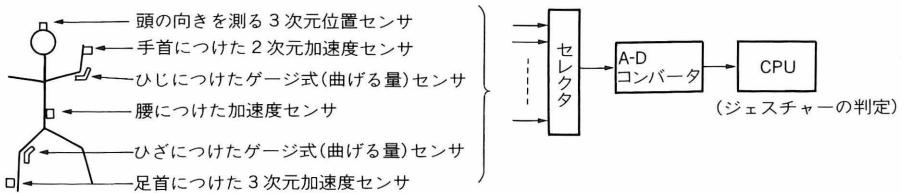

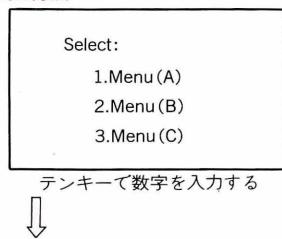

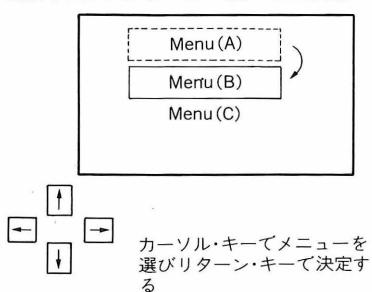

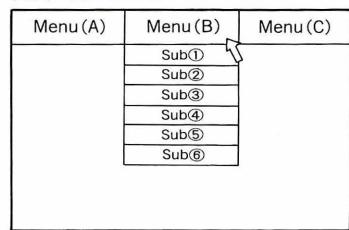

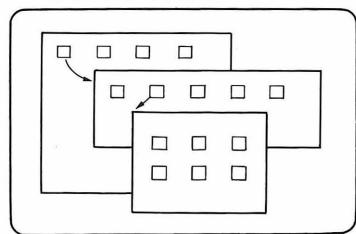

CPUパワーの向上と共に進んだソフトウェア技術としては、図1.27のように、それまでの「メニュー方式」ソフトから、階層の状態を視覚的に確認できる「ウインドウ方式」、あるいは複数のプロセスを並行して走らせるマルチタスクへと進みました。このようないろいろな技術の進歩というのは、人間とコンピュータ・システムの間に置かれて、それぞれのスムーズな活動を助けるための、マン-マシン・インターフェース技術の発展として、統一的に理解することができます。

### ●システムの出力技術も永遠の課題

この他の2次元ディスプレイとしては、ELパネルやプラズマ・ディスプレイがありますが、高性能とは

〔図1.25〕 LEDディスプレイ

〔図1.26〕 LCDディスプレイの例(スタンレー電気)

GMD1620AL\*

GMD2420AL\*

GMD1640AL\*

## ●製品規格

単位:mm

| 品名         | 表示容量<br>(文字×行) | 外形寸法<br>(W×H×D) | 有効表示寸法<br>(W×H) | 文字寸法<br>(W×H) | ドット寸法<br>(W×H) | Duty比 | 重量   |

|------------|----------------|-----------------|-----------------|---------------|----------------|-------|------|

| GMD1610FL* | 16×1           | 80×36×15        | 64.5×13.8       | 3.11×5.77     | 0.59×0.79      | 1/16  | 40g  |

| GMD1620AL* | 16×2           | 85×36×15        | 63.5×15.8       | 3.20×4.85     | 0.60×0.65      | 1/16  | 40g  |

| GMD1640AL* | 16×4           | 87×60×15        | 61.8×25.2       | 2.95×4.15     | 0.55×0.55      | 1/16  | 60g  |

| GMD2020AL* | 20×2           | 115×36×16       | 83.0×18.6       | 3.20×4.85     | 0.60×0.65      | 1/16  | 60g  |

| GMD2040AL* | 20×4           | 98×60×15        | 76.0×25.2       | 2.95×4.15     | 0.55×0.55      | 1/16  | 70g  |

| GMD2420AL* | 24×2           | 118×36×15       | 93.5×15.8       | 3.20×4.85     | 0.60×0.65      | 1/16  | 65g  |

| GMD4020AL* | 40×2           | 182×33.5×16     | 154.5×15.8      | 3.20×4.85     | 0.60×0.65      | 1/16  | 100g |

いえちょっとコストが高いものです。また、液晶シャッターを両目の視差を考慮して表示するHMD(ヘッド・マウント・ディスプレイ)の3次元表示も、まだまだこれからの技術です。

また、音声合成とか音響合成などの聴覚的な情報出力も、視覚表示の情報量に比べるとかなり少ないために、ちょっと単独では使えないようです。音楽演奏はできても、「再生」でなく「歌う」電子楽器がなかなか登場しないように、音声合成技術は発展途上段階ですから、しばらくの間は、いろいろな入力手段と組み合わせた上で、まだ視覚的な情報中心の時代が続くのか

かもしれません。

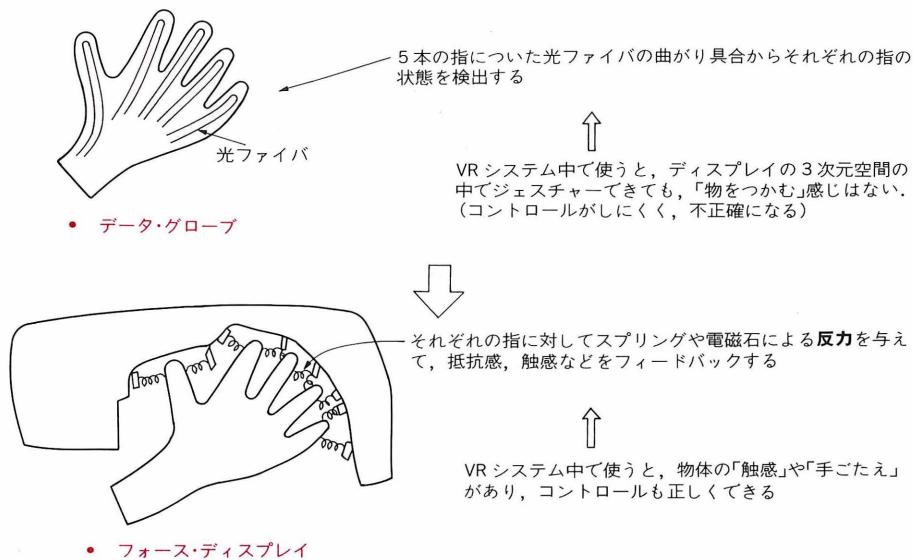

なお、たとえばデータ・グローブで動作を入力するのに対して、グローブの「手応え」をシステムから人間に物理的に返す、という「フォース・ディスプレイ」という情報出力技術もあります(図1.28)。これによって、人間は仮想的な物体の「質感」を実感するわけです。ゲームセンターのコックピットが動くものなども、同様の臨場感として有効でしょう。しかし、「頭に電極を突き刺して直接に脳に情報を伝える」「人間にテレパシーでメッセージを送る」というところまでは、たぶん行かないだろうと思います。

## ●ヒューマン・インターフェースとしてのバーチャル・リアリティ技術

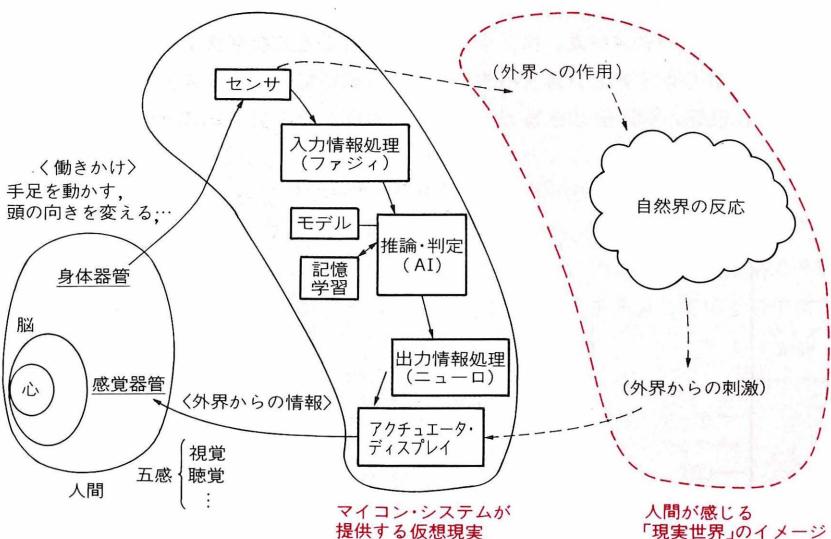

最後に、マイコン・システムと人間との接点(マンマシン・インターフェース)の重要な技術である、「ヒューマン・インターフェース」について考えてみましょう。マルチメディア技術の延長上にあるものとして、「仮想現実感」(バーチャル・リアリティ:VR、またはアーティフィシャル・リアリティ:AR)が流行していますが、これはまさに、ヒューマン・インターフェース技術の理想を追求しているのです。

この技術を検討するため、図1.29のように、マイコン・システムを、人間と「感覚される空間」との間に置いた、仮想的なインターフェースと想定してみま

す。人間は機械的なマイコン・システムを操作するのではなく、より自然なかたちで、この仮想現実空間に働きかけるのです。システム側ではこのインターフェースから必要な情報を抽出して、機械の形式の入力情報とします。また、マイコン・システムからの出力についても、機械の語法のままでは人間にとて理解が困難ですから、この仮想インターフェースが人間に優しいかたちに変換して提供することになります。このようなシステムは、まだまだ高価なセンサやEWSを駆使した大がかりな物ですが、発想の部分については、マイコン・システムでもおおいに参考となっていくでしょう。

〔図1.27〕 ソフトウェアのユーザ・インターフェースの進歩

### (メニュー方式)

#### • 古き時代の方法

#### • 疑似ウィンドウ・メニュー(カーソル方式)

### (ウィンドウ方式)

#### • プルダウン・メニュー

カーソルでメニューを選ぶ(クリックする)と、サブメニューが出てきて、さらに選ぶ。階層性はわかりやすい

#### • ウィンドウ・システム

オーバラップ・ウィンドウで、つぎつぎにメニューが開いていく

[図I.28] フォース・ディスプレイ

[図I.29] マン-マシン・インターフェースとしての仮想現実感(バーチャル・リアリティ)

# パソコン活用システム関連技術

## ハードウェア技術の基本

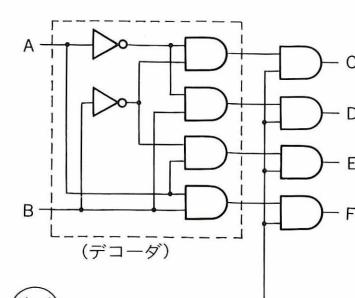

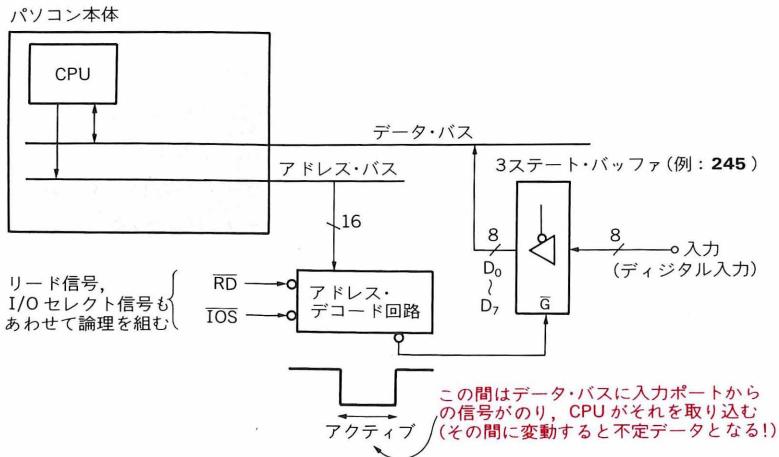

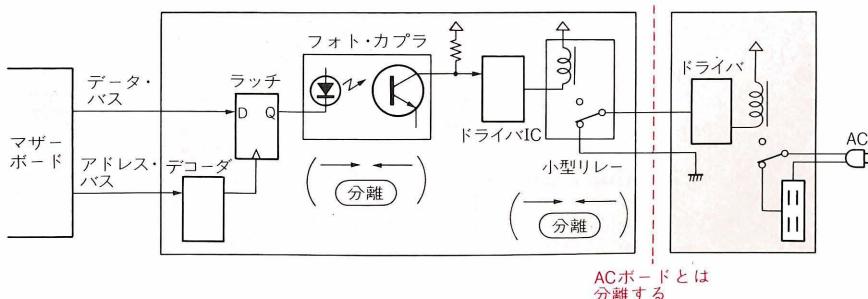

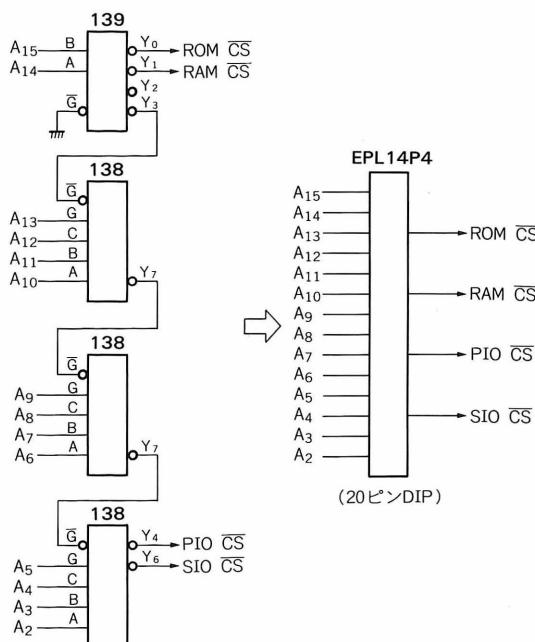

ここでは、パソコンの拡張スロットに外部インターフェース用のボードを拡張していくための、もっとも基本的なハードウェア技術を確認していきます。

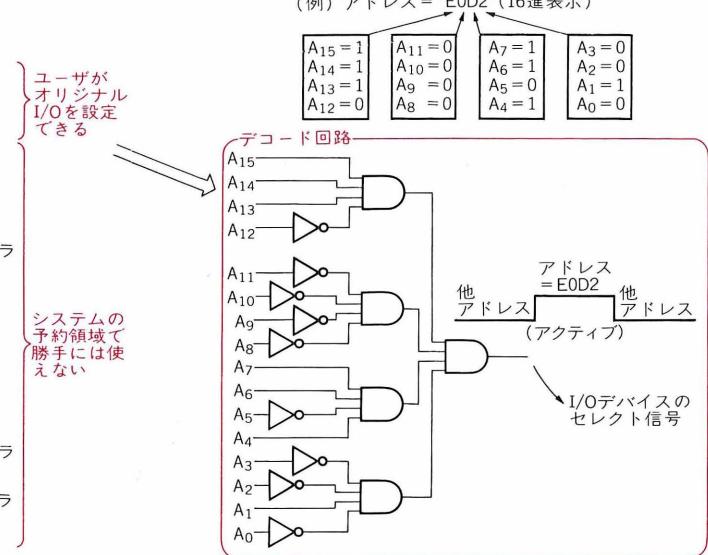

### ●アドレス・デコード

CPUチップ自身が外界とやりとりするための基本となるのは、

#### ●情報じたいをやりとりするデータ・バス

●そのデータがどこにあるかを示すアドレス・バスの2種類のバスです(それ以外の制御信号をまとめて

「コントロール・バス」と呼ぶ場合もある)。そしてこのバスには、各種のメモリとか周辺LSIなどが接続されますから、これらのチップをそれぞれ区別して制御しなければなりません。そのための最初の準備として、図2.1(a)のように、CPUのアドレス空間(CPUによっては、メモリ空間とI/O空間とがある)に周辺LSIなどを配置した「アドレス・マップ」が規定されます。パソコンの場合には、最初からメーカによって予約されているアドレスが多いので、ユーザとして新たに周辺を増設する場合には、メーカから自由エリアとして提供されている「ユーザ領域」を増設周辺用に割り当てることになります。

続いて、アドレス・マップ上で決定したアドレスに対応した、アドレス・デコード回路が必要になります。

(図2.1) アドレス・デコード

(a)

(b)

これは基本的には図2.1(b)のように、アドレス・バスの信号から論理積を作って、該当する周辺チップにだけアクティブ信号(データ・バスの使用権、あるいはデータ・バス上の信号がそのチップに対するものであるというサイン)を送る、という考え方です。したがって、二つ以上の周辺チップが同じアドレスでアクティブにならないように、正しくアドレス・デコード回路を設計することが必要となります。周辺チップは一つだけのアドレスを占有するとは限らない(ある一定幅の領域をもつ)場合も多いので、デコード回路の設計は慎重に行います。

デコード回路を節約するために、実際に使用する範囲よりも広いアドレスでアクティブになるような回路とする場合も多い(このときの、実際には使わないアドレス領域を「ゴースト」とか「シャドー・エリア」という)のですが、あとでシステムの周辺を増設したような場合に、思わぬアドレス衝突のトラブルの原因となることもありますから、設計完了時点での最終的なアドレス・マップをきちんと記録しておきましょう。

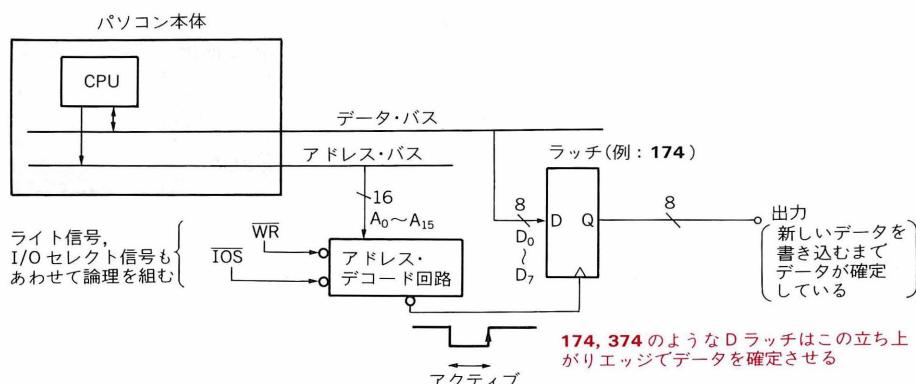

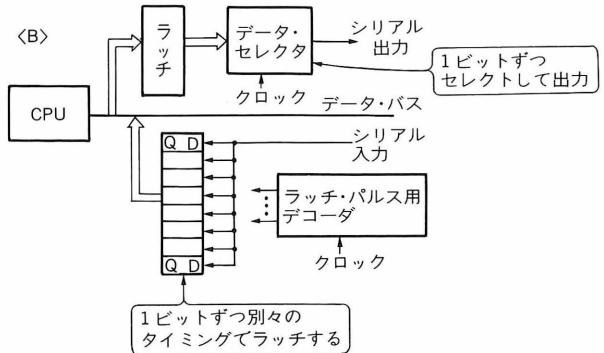

### ●出力ポート(ラッチ出力)

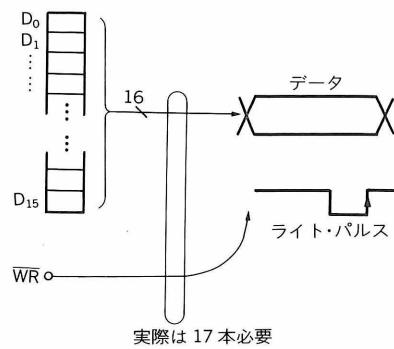

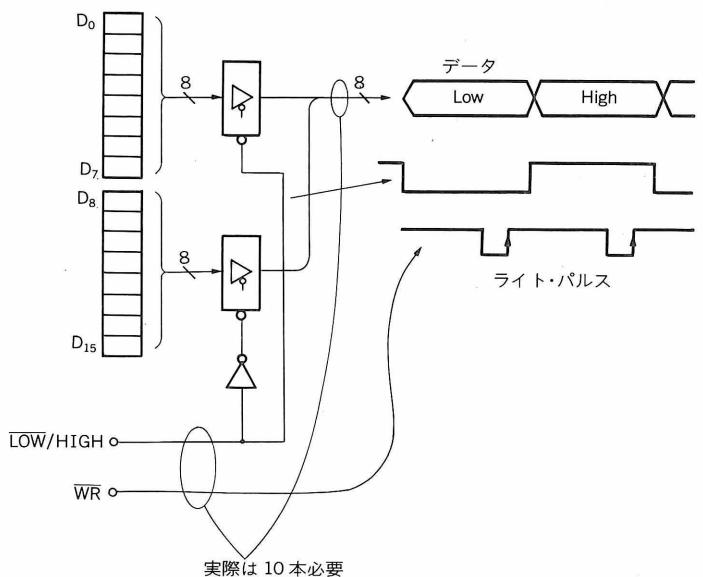

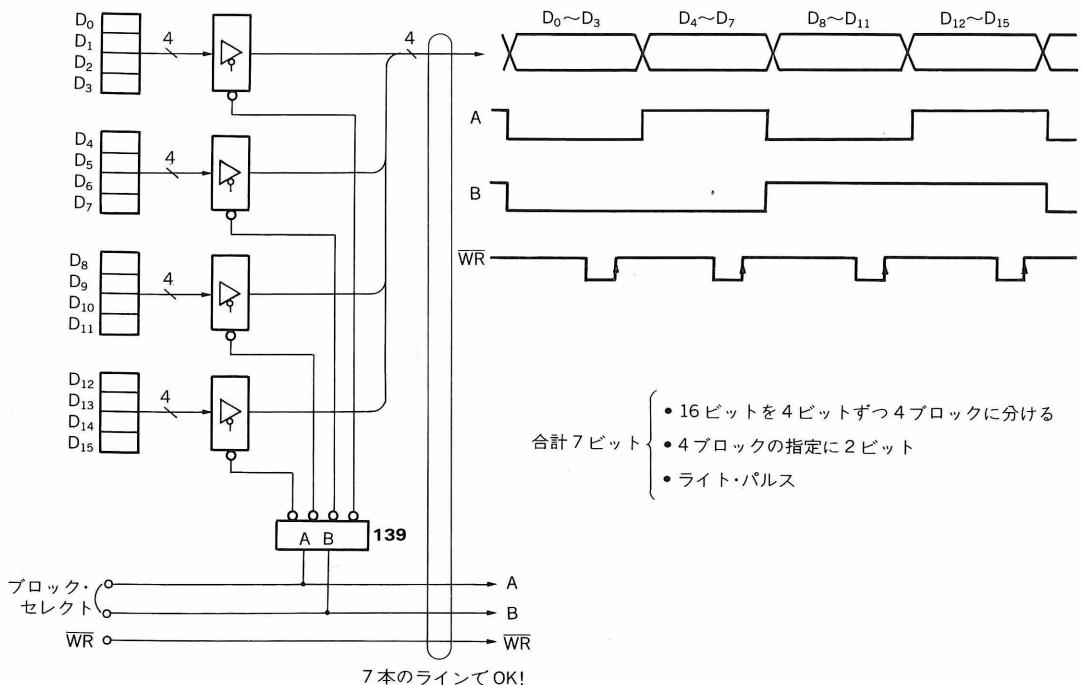

パソコンから外部に信号を出力する場合、CPUのデータ・バス上の信号を確定させて外部に取り出すために、図2.2のようなラッチが必要です(これをラッチ出力といいます)。普通は174や374のような、エッジトリガ・タイプのDラッチを使用しますが、もしここに373のようなGラッチ(トランスペアレント・ラッチ)を使うと、ラッチ・パルス(ライト・パルス)がアクティブであるデータの切り替え時に、CPUの特性やデータの

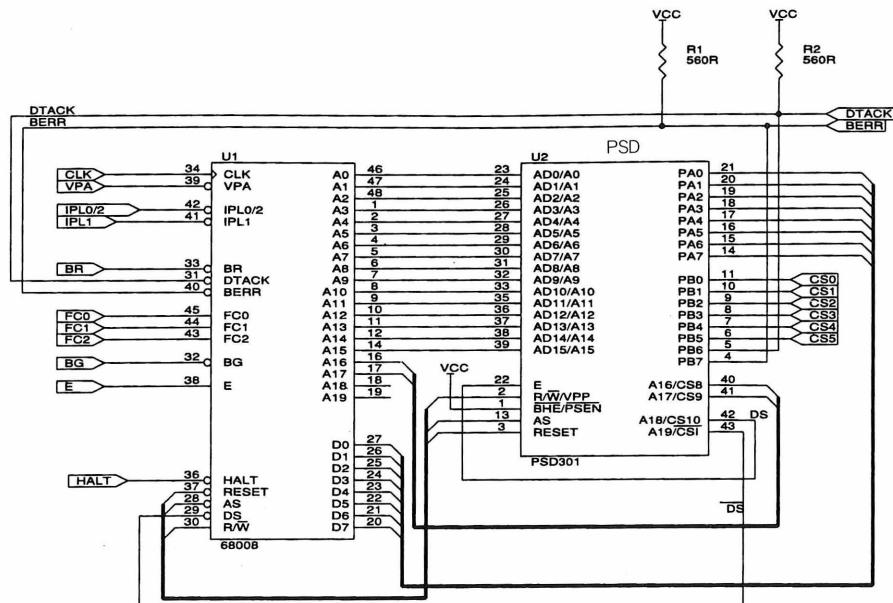

遅れによってはデータが変動する(不定)可能性があります。