# **Propeller**<sup>™</sup> P8X32A Datasheet

## 8-Cog Multiprocessor Microcontroller

### 1.0 PRODUCT OVERVIEW

#### 1.1. Introduction

The Propeller chip is designed to provide high-speed processing for embedded systems while maintaining low current consumption and a small physical footprint. In addition to being fast, the Propeller chip provides flexibility and power through its eight processors, called cogs, that can perform simultaneous tasks independently or cooperatively, all while maintaining a relatively simple architecture that is easy to learn and utilize. Two programming languages are available: Spin (a high-level object-based language) and Propeller Assembly. Both include custom commands to easily manage the Propeller chip's unique features.

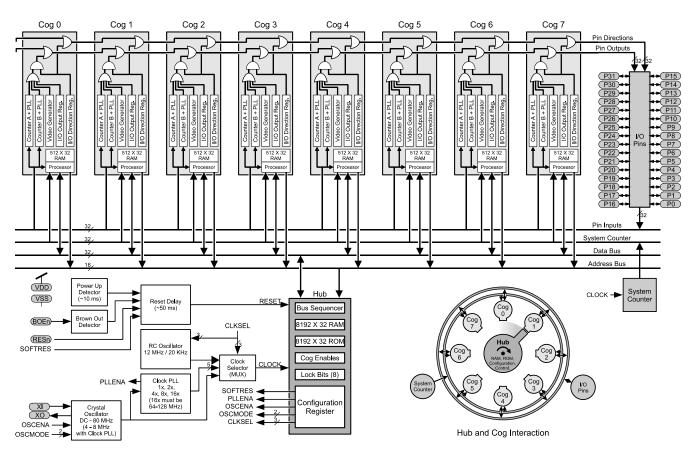

Figure 1: Propeller P8X32A Block Diagram

#### 1.2. Stock Codes

|                   | Table 1: Propeller Chip Stock Codes |             |                       |                            |                           |                                |                            |                          |  |  |

|-------------------|-------------------------------------|-------------|-----------------------|----------------------------|---------------------------|--------------------------------|----------------------------|--------------------------|--|--|

| Device<br>Stock # | Package Type                        | I/O<br>Pins | Power<br>Requirements | External<br>Clock<br>Speed | Internal RC<br>Oscillator | Internal<br>Execution<br>Speed | Global<br>ROM/RAM          | Cog RAM                  |  |  |

| P8X32A-D40        | 40-pin DIP                          |             |                       |                            |                           |                                | 64 K bytes;                |                          |  |  |

| P8X32A-Q44        | 44-pin LQFP                         | 32<br>CMOS  | 3.3 volts DC          | DC to 80<br>MHz            | 12 MHz or<br>20 kHz*      | 0 to 160 MIPS<br>(20 MIPS/cog) | 32768 bytes<br>ROM / 32768 | 512 x 32 bits<br>per cog |  |  |

| P8X32A-M44        | 44-pin QFN                          |             |                       |                            |                           | ( 1 1 1 3 )                    | bytes RAM                  |                          |  |  |

<sup>\*</sup>Approximate; may range from 8 MHz - 20 MHz, or 13 kHz - 33 kHz, respectively.

Parallax, Propeller, Spin, and the Parallax and Propeller logos are trademarks of Parallax, Inc. All other trademarks are the property of their respective holders.

### **Table of Contents**

|                  |                                                                                          |    | 5.1.4. | Math Function Tables                                        | 15 |

|------------------|------------------------------------------------------------------------------------------|----|--------|-------------------------------------------------------------|----|

| 1.0              | Product Overview                                                                         | 1  | 5.2.   | Cog RAM                                                     | 15 |

| 1.1.             | Introduction                                                                             | 1  |        |                                                             |    |

| 1.2.             | Stock Codes                                                                              | 1  | 6.0    | Programming Languages                                       | 16 |

| 1.3.             | Key Features                                                                             | 3  | 6.1.   | Reserved Word List                                          | 16 |

| 1.4.             | Programming Advantages                                                                   |    | 6.1.1. | Words Reserved for Future Use                               | 16 |

| 1.5.             | Applications                                                                             |    | 6.2.   | Math and Logic Operators                                    | 17 |

| 1.6.             | Programming Platform Support                                                             | 3  | 6.3.   | Spin Language Summary Table                                 |    |

| 1.7.             | Corporate and Community Support                                                          |    | 6.3.1. | Constants                                                   |    |

| 1.7.             | Corporate and Community Capport                                                          |    | 6.4.   | Propeller Assembly Instruction Table                        |    |

| 2.0              | Connection Diagrams                                                                      | 4  | 6.4.1. | Assembly Conditions                                         |    |

| 2.1.             | Pin Assignments                                                                          |    | 6.4.2. | Assembly Directives                                         | 23 |

| 2.1.             | Pin Descriptions                                                                         |    | 6.4.3. | Assembly Effects                                            | 23 |

| 2.3.             |                                                                                          |    | 6.4.4. | Assembly Operators                                          | 23 |

| 2.3.1.           | Typical Connection Diagrams<br>Propeller Clip or Propeller Plug Connection - Recommended |    |        |                                                             |    |

| 2.3.1.           | Alternative Serial Port Connection                                                       | 5  | 7.0    | Propeller Demo Board Schematic                              | 24 |

| 3.0              | Operating Precedures                                                                     | 6  | 8.0    | Electrical Characteristics                                  | 25 |

|                  | Operating Procedures                                                                     | 0  | 8.1.   | Absolute Maximum Ratings                                    | 25 |

| 3.1.             | Boot-Up Procedure                                                                        | 6  | 8.2.   | DC Characteristics                                          |    |

| 3.2.             | Run-Time Procedure                                                                       |    | 8.3.   | AC Characteristics                                          |    |

| 3.3.             | Shutdown Procedure                                                                       | 6  | 0.0.   | 7 C CHAIGCONGLOC                                            | 20 |

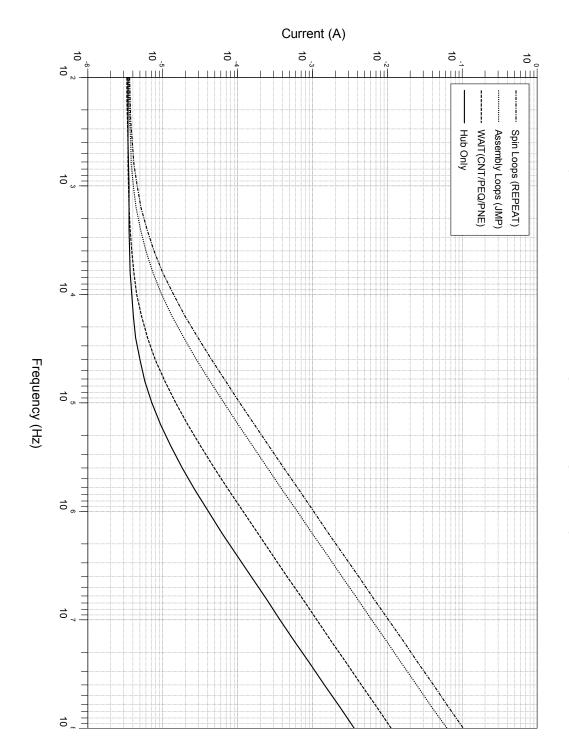

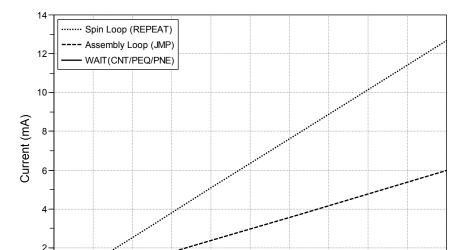

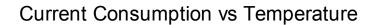

| 4.0              | System Organization                                                                      | 6  | 9.0    | Current Consumption Characteristics                         |    |

| 4.1.             | Shared Resources                                                                         | 6  | 9.1.   | Typical Current Consumption of 8 Cogs                       | 26 |

| 4.1.             |                                                                                          |    | 9.2.   | Typical Current of a Cog vs. Operating Frequency            | 27 |

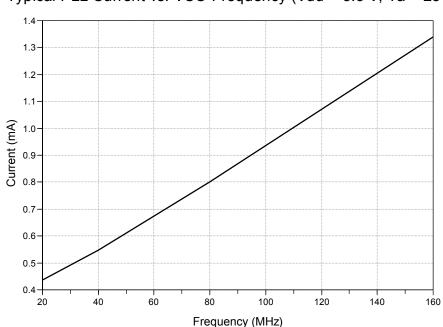

|                  | System Clock                                                                             |    | 9.3.   | Typical PLL Current vs. VCO Frequency                       | 27 |

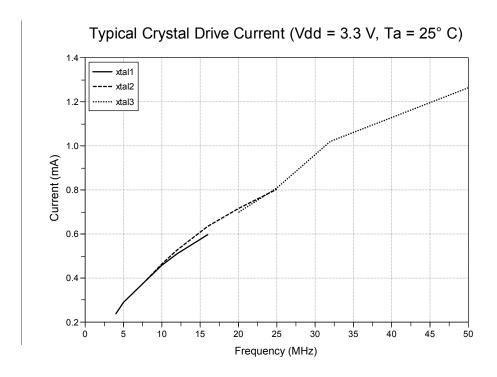

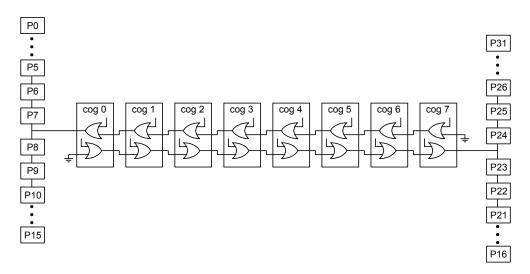

| 4.3.             | Cogs (processors)                                                                        |    | 9.4.   | Typical Crystal Drive Current                               |    |

| 4.4.             | Hub                                                                                      |    | 9.5.   | Cog and I/O Pin Relationship                                |    |

| 4.5.             | I/O Pins                                                                                 |    | 9.6.   | Current Profile at Various Startup Conditions               |    |

| 4.6.             | System Counter                                                                           |    | 0.0.   | Carrone 1 Tonio de Variodo Ciartap Conditiono               | 20 |

| 4.7.             | Locks                                                                                    |    | 10.0   | Temperature Characteristics                                 | 30 |

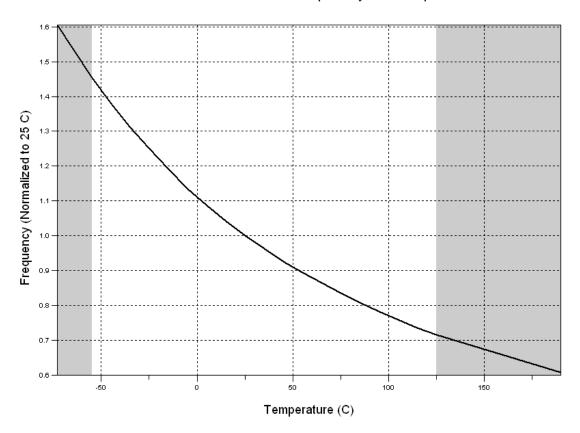

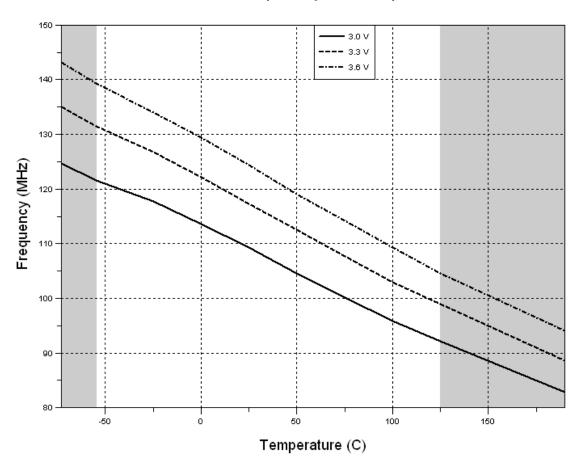

| 4.8.             | Cog Counters                                                                             |    | 10.1.  | Internal Oscillator Frequency as a Function of Temperature. |    |

| 4.8.1.           | CTRA / CTRB – Control register                                                           |    | 10.1.  | Fastest Operating Frequency as a Function of Temperature    |    |

| 4.8.2.           | FRQA / FRQB – Frequency register                                                         |    | 10.3.  | Current Consumption as a Function of Temperature            |    |

| 4.8.3.           | PHSA / PHSB – Phase register                                                             |    | 10.5.  | Current Consumption as a runction of Temperature            | 32 |

| 4.9.             | Video Generator                                                                          |    | 11.0   | Package Dimensions                                          | 33 |

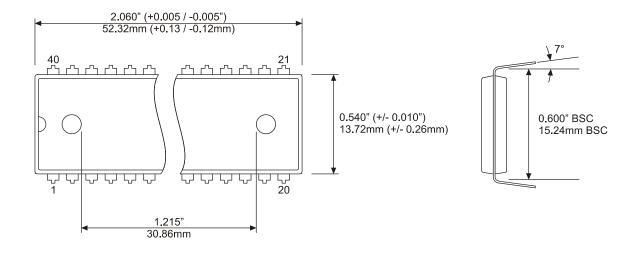

| 4.9.1.           | VCFG – Video Configuration Register                                                      |    | 11.1.  | P8X32A-D40 (40-pin DIP)                                     | 33 |

| 4.9.2.<br>4.9.3. | VSCL – Video Scale RegisterWAITVID Command/Instruction                                   |    |        | POX32A-D40 (40-pill DIP)                                    | აა |

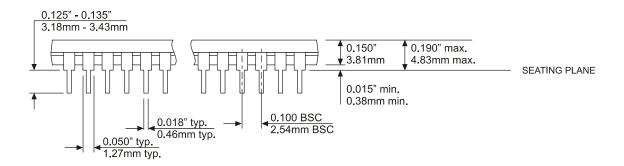

| 4.9.3.           | CLK Register                                                                             |    | 11.2.  | P8X32A-Q44 (44-pin LQFP)                                    |    |

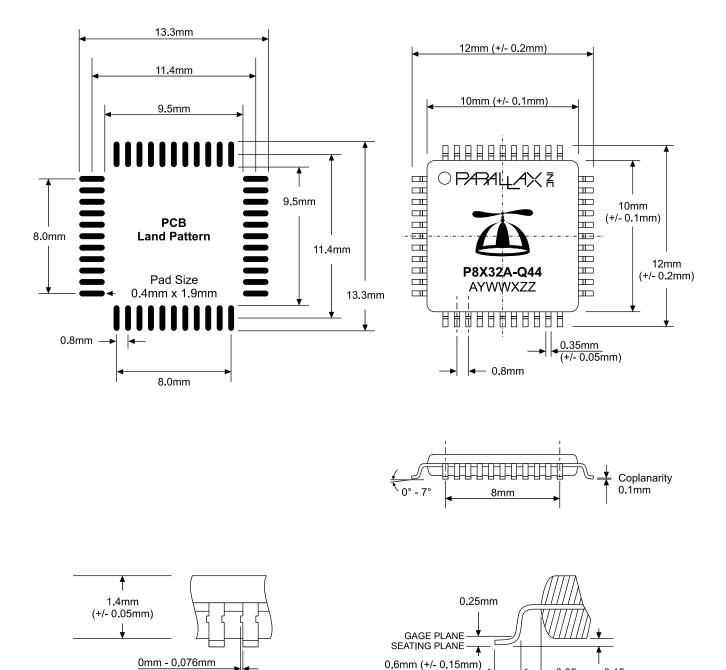

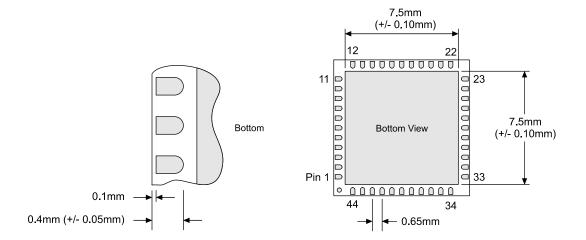

| 4.10.            | CLN Register                                                                             | 13 | 11.3.  | P8X32A-M44 (44-pin QFN)                                     | 35 |

| 5.0              | Memory Organization                                                                      |    | 12.0   | Manufacturing Information                                   | 36 |

| 5.1.             | Main Memory                                                                              |    | 12.1.  | Reflow Peak Temperature                                     | 36 |

| 5.1.1.           | Main RAM                                                                                 |    | 12.2.  | Green/RoHS Compliance                                       | 36 |

| 5.1.2.           | Main ROM                                                                                 |    |        | r                                                           |    |

| 513              | Character Definitions                                                                    | 14 |        |                                                             |    |

#### 1.3. Key Features

The design of the Propeller chip frees application developers from common complexities of embedded systems programming. For example:

- Eight processors (cogs) perform simultaneous processes independently or cooperatively, sharing common resources through a central hub. The Propeller application designer has full control over how and when each cog is employed; there is no compiler-driven or operating system-driven splitting of tasks among multiple cogs. This method empowers the developer to deliver absolutely deterministic timing, power consumption, and response to the embedded application.

- Asynchronous events are easier to handle than with devices that use interrupts. The Propeller has no need for interrupts; just assign some cogs to individual, high-bandwidth tasks and keep other cogs free and unencumbered. The result is a more responsive application that is easier to maintain.

- A shared System Clock allows each cog to maintain the same time reference, allowing true synchronous execution.

#### 1.4. Programming Advantages

- The object-based high-level Spin language is easy to learn, with special commands that allow developers to quickly exploit the Propeller chip's unique and powerful features.

- Propeller Assembly instructions provide conditional execution and optional flag and result writing for each individual instruction. This makes critical, multi-decision blocks of code more consistently timed; event handlers are less prone to jitter and developers spend less time padding, or squeezing, cycles.

#### 1.5. Applications

The Propeller chip is particularly useful in projects that can be vastly simplified with simultaneous processing, including:

- Industrial control systems

- Sensor integration, signal processing, and data acquisition

- Handheld portable human-interface terminals

- Motor and actuator control

- User interfaces requiring NTSC, PAL, or VGA output, with PS/2 keyboard and mouse input

- Low-cost video game systems

- Industrial, educational or personal-use robotics

- Wireless video transmission (NTSC or PAL)

### 1.6. Programming Platform Support

Parallax Inc. supports the Propeller chip with a variety of hardware tools and boards:

- Propeller Clip (#32200) and Propeller Plug (#32201). These boards provide convenient programming port connections, see the Typical Connection Diagrams on Page 5.

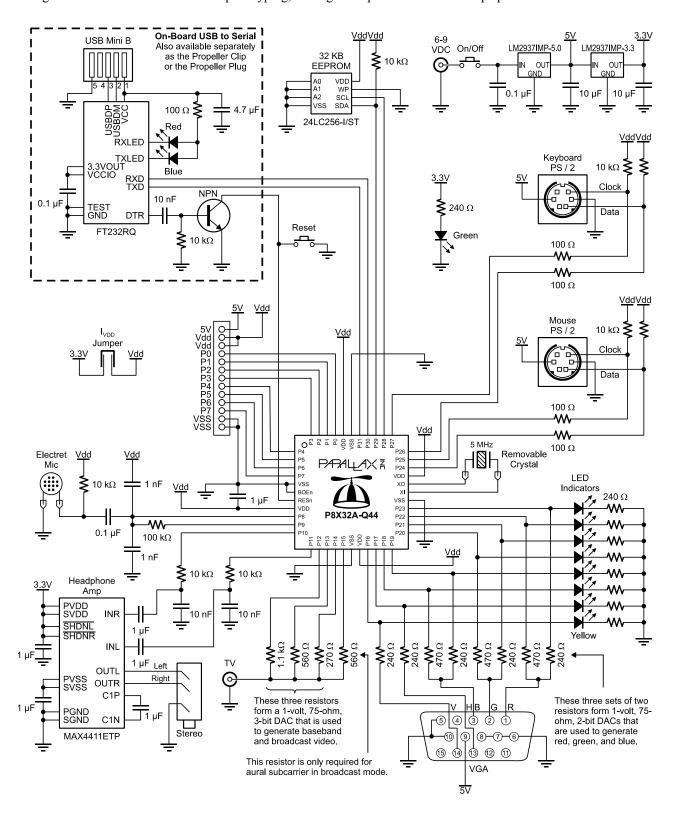

- The Propeller Demo Board (#32100) provides a convenient means to test-drive the Propeller chip's varied capabilities through a host of device interfaces on one compact board. The schematic is provided on page 24. Main features:

- o P8X32A-Q44 Propeller Chip

- o 24LC256-I/ST EEPROM for program storage

- o Replaceable 5.000 MHz crystal

- o 3.3 V and 5 V regulators with on/off switch

- USB-to-serial interface for programming and communication

- o VGA and TV output

- o Stereo output with 16  $\Omega$  headphone amplifier

- Electret microphone input

- o Two PS/2 mouse and keyboard I/O connectors

- o 8 LEDs (share VGA pins)

- o Pushbutton for reset

- o Big ground post for scope hookup

- o I/O pins P0-P7 are free and brought out to header

- o Breadboard for custom circuits

- The Propeller Proto Board (#32212) features a surface-mount Propeller chip with the necessary components to achieve a programming interface, with pads ready for a variety of I/O connectors and DIP/SIP chips, and a generous through-hole prototyping area.

- The PropStick USB (#32210) features a Propeller chip, EEPROM, 3.3 VDC and 5 VDC regulators, reset button, crystal and USB connection on a 0.6" wide DIP package for easy prototyping on perfboard and breadboard.

#### 1.7. Corporate and Community Support

- Parallax provides technical support free of charge. In the Continental US, call toll free (888) 512-1024; from outside please call (916) 624-8333. Or, email: <a href="mailto:support@parallax.com">support@parallax.com</a>.

- Parallax hosts a moderated public user's forum just for the Propeller: <a href="http://forums.parallax.com/forums">http://forums.parallax.com/forums</a>.

- Browse through community-created Propeller objects and share yours with others via Parallaxhosted Propeller Object Exchange Library: <a href="http://obex.parallax.com">http://obex.parallax.com</a>.

### 2.0 CONNECTION DIAGRAMS

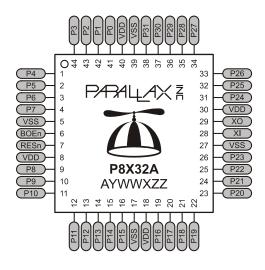

### 2.1. Pin Assignments

LQFP and QFN Packages

### 2.2. Pin Descriptions

|          |           | Table 2: Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

| P0 – P31 | I/O       | General purpose I/O Port A. Can source/sink 40 mA each at 3.3 VDC. CMOS level logic with threshold of ~ ½ VDD or 1.6 VDC @ 3.3 VDC.  The pins shown below have a special purpose upon power-up/reset but are general purpose I/O afterwards.  P28 - I2C SCL connection to optional, external EEPROM. P29 - I2C SDA connection to optional, external EEPROM. P30 - Serial Tx to host. P31 - Serial Rx from host. |

| VDD      |           | 3.3 volt power (2.7 – 3.6 VDC)                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS      |           | Ground                                                                                                                                                                                                                                                                                                                                                                                                          |

| BOEn     | 1         | Brown Out Enable (active low). Must be connected to either VDD or VSS. If low, RESn becomes a weak output (delivering VDD through 5 k $\Omega$ ) for monitoring purposes but can still be driven low to cause reset. If high, RESn is CMOS input with Schmitt Trigger.                                                                                                                                          |

| RESn     | I/O       | Reset (active low). When low, resets the Propeller chip: all cogs disabled and I/O pins floating. Propeller restarts 50 ms after RESn transitions from low to high.                                                                                                                                                                                                                                             |

| XI       | 1         | Crystal Input. Can be connected to output of crystal/oscillator pack (with XO left disconnected), or to one leg of crystal (with XO connected to other leg of crystal or resonator) depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                                                       |

| ХО       | 0         | Crystal Output. Provides feedback for an external crystal, or may be left disconnected depending on CLK Register settings. No external resistors or capacitors are required.                                                                                                                                                                                                                                    |

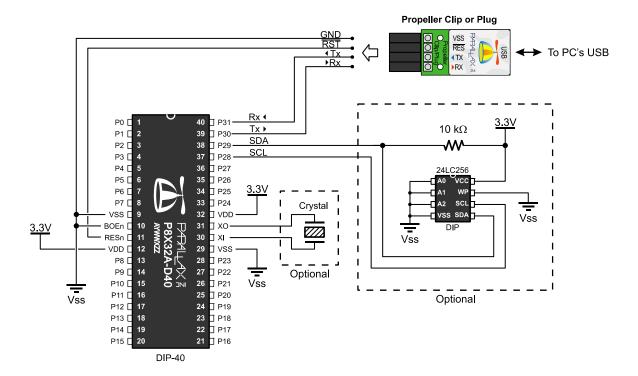

### 2.3. Typical Connection Diagrams

#### 2.3.1. Propeller Clip or Propeller Plug Connection - Recommended

Note that the connections to the external oscillator and EEPROM, which are enclosed in dashed lines, are optional.

Propeller Clip, Stock #32200; Propeller Plug, Stock #32201. The Propeller Clip/Plug schematic is available for download from www.parallax.com.

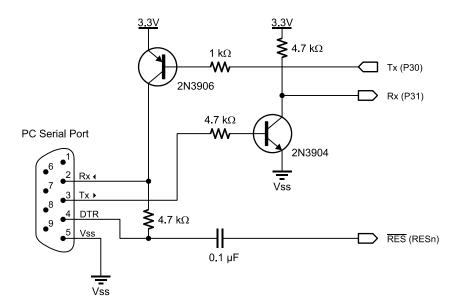

#### 2.3.2. Alternative Serial Port Connection

#### 3.0 OPERATING PROCEDURES

#### 3.1. Boot-Up Procedure

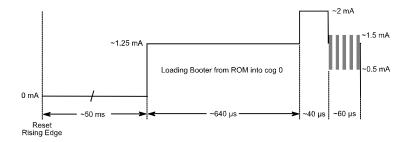

Upon power-up, or reset:

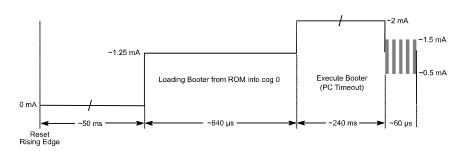

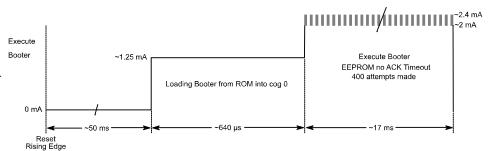

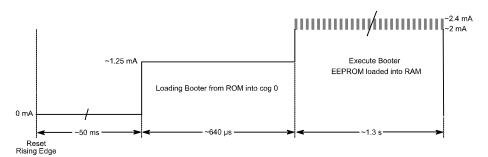

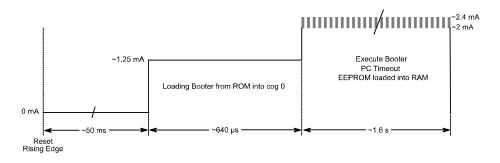

- 1. The Propeller chip's internal RC oscillator begins running at 20 kHz, then after a 50 ms reset delay, switches to 12 MHz. Then the first processor (Cog 0) loads and runs the built-in Boot Loader program.

- 2. The Boot Loader performs one or more of the following tasks, in order:

- a. Detects communication from a host, such as a PC, on pins P30 and P31. If communication from a host is detected, the Boot Loader converses with the host to identify the Propeller chip and possibly download a program into global RAM and optionally into an external 32 KB EEPROM.

- b. If no host communication was detected, the Boot Loader looks for an external 32 KB EEPROM on pins P28 and P29. If an EEPROM is detected, the entire 32 KB data image is loaded into the Propeller chip's global RAM.

- c. If no EEPROM was detected, the boot loader stops, Cog 0 is terminated, the Propeller chip goes into shutdown mode, and all I/O pins are set to inputs.

- 3. If either step 2a or 2b was successful in loading a program into the global RAM, and a suspend command was not given by the host, then Cog 0 is reloaded with the built-in Spin Interpreter and the user code is run from global RAM.

#### 3.2. Run-Time Procedure

A Propeller Application is a user program compiled into its binary form and downloaded to the Propeller chip's RAM or external EEPROM. The application consists of code written in the Propeller chip's Spin language (highlevel code) with optional Propeller Assembly language components (low-level code). Code written in the Spin language is interpreted during run time by a cog running the Spin Interpreter while code written in Propeller Assembly is run in its pure form directly by a cog. Every Propeller Application consists of at least a little Spin code and may actually be written entirely in Spin or with various amounts of Spin and assembly. The Propeller chip's Spin Interpreter is started in Step 3 of the Boot Up Procedure, above, to get the application running.

Once the boot-up procedure is complete and an application is running in Cog 0, all further activity is defined by the application itself. The application has complete control over things like the internal clock speed,

I/O pin usage, configuration registers, and when, what and how many cogs are running at any given time. All of this is variable at run time, as controlled by the application.

#### 3.3. Shutdown Procedure

When the Propeller goes into shutdown mode, the internal clock is stopped causing all cogs to halt and all I/O pins are set to input direction (high impedance). Shutdown mode is triggered by one of the three following events:

- 1. VDD falling below the brown-out threshold (~2.7 VDC), when the brown out circuit is enabled,

- 2. the RESn pin going low, or

- 3. the application requests a reboot (see the **REBOOT** command in the Propeller Manual).

Shutdown mode is discontinued when the voltage level rises above the brown-out threshold and the RESn pin is high.

#### 4.0 SYSTEM ORGANIZATION

#### 4.1. Shared Resources

There are two types of shared resources in the Propeller: 1) common, and 2) mutually-exclusive. Common resources can be accessed at any time by any number of cogs. Mutually-exclusive resources can also be accessed by any number of cogs, but only by one cog at a time. The common resources are the I/O pins and the System Counter. All other shared resources are mutually-exclusive by nature and access to them is controlled by the Hub. See Section 4.4 on page 7.

### 4.2. System Clock

The System Clock (shown as "CLOCK" in Figure 1, page 1) is the central clock source for nearly every component of the Propeller chip. The System Clock's signal comes from one of three possible sources:

- The internal RC oscillator (~12 MHz or ~20 kHz)

- The XI input pin (either functioning as a highimpedance input or a crystal oscillator in conjunction with the XO pin)

- The Clock PLL (phase-locked loop) fed by the XI input

The source is determined by the CLK register's settings, which is selectable at compile time and reselectable at run time. The Hub and internal Bus operate at half the System Clock speed.

#### 4.3. Cogs (processors)

The Propeller contains eight (8) identical, independent processors, called cogs, numbered 0 to 7. Each cog contains a Processor block, local 2 KB RAM configured as 512 longs (512 x 32 bits), two advanced counter modules with PLLs, a Video Generator, I/O Output Register, I/O Direction Register, and other registers not shown in the Block Diagram.

All eight cogs are driven from the System Clock; they each maintain the same time reference and all active cogs execute instructions simultaneously. They also all have access to the same shared resources.

Cogs can be started and stopped at run time and can be programmed to perform tasks simultaneously, either independently or with coordination from other cogs through Main RAM. Each cog has its own RAM, called Cog RAM, which contains 512 registers of 32 bits each. The Cog RAM is all general purpose RAM except for the last 16 registers, which are special purpose registers, as described in Table 15 on page 15.

#### 4.4. Hub

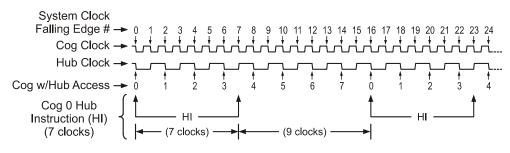

To maintain system integrity, mutually-exclusive resources must not be accessed by more than one cog at a time. The Hub controls access to mutually-exclusive resources by giving each cog a turn in a "round robin" fashion from Cog 0 through Cog 7 and back to Cog 0 again. The Hub and its bus run at half the System Clock rate, giving a cog access to mutually-exclusive resources once every 16 System Clock cycles. Hub instructions, the Propeller Assembly instructions that access mutually-exclusive resources, require 7 cycles to execute but they first need to be synchronized to the start of the Hub Access Window.

to synchronize to the Hub Access Window plus 7 cycles to execute the hub instruction, so hub instructions take from 7 to 22 cycles to complete.

Figure 2 and Figure 3 show examples where Cog 0 has a

It takes up to 15 cycles (16 minus 1, if we just missed it)

Figure 2 and Figure 3 show examples where Cog 0 has a hub instruction to execute. Figure 2 shows the best-case scenario; the hub instruction was ready right at the start of that cog's access window. The hub instruction executes immediately (7 cycles) leaving an additional 9 cycles for other instructions before the next Hub Access Window arrives.

Figure 3 shows the worst-case scenario; the hub instruction was ready on the cycle right after the start of Cog 0's access window; it just barely missed it. The cog waits until the next Hub Access Window (15 cycles later) then the hub instruction executes (7 cycles) for a total of 22 cycles for that hub instruction. Again, there are 9 additional cycles after the hub instruction for other instructions to execute before the next Hub Access Window arrives. To get the most efficiency out of Propeller Assembly routines that have to frequently access mutually-exclusive resources, it can be beneficial to interleave non-hub instructions with hub instructions to lessen the number of cycles waiting for the next Hub Access Window. Since most Propeller Assembly instructions take 4 clock cycles, two such instructions can be executed in between otherwise contiguous hub instructions.

Keep in mind that a particular cog's hub instructions do not, in any way, interfere with other cogs' instructions because of the Hub mechanism. Cog 1, for example, may start a hub instruction during System Clock cycle 2, in both of these examples, possibly overlapping its execution with that of Cog 0 without any ill effects. Meanwhile, all other cogs can continue executing non-hub instructions, or awaiting their individual hub access windows regardless of what the others are doing.

Figure 2: Cog-Hub Interaction – Best Case Scenario

Figure 3: Cog-Hub Interaction – Worst Case Scenario

System Clock

Falling Edge # → 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

Cog Clock → 1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

Cog W/Hub Access → 0 1 2 3 4 5 6 7 0 1 2 3 4

Cog 0 Hub

Instruction (HI)

(22 clocks)

(15 clocks) → (7 clocks) → (7 clocks)

#### 4.5. I/O Pins

The Propeller has 32 I/O pins, 28 of which are general purpose. I/O Pins 28 - 31 have a special purpose at boot up and are available for general purpose use afterwards; see section 2.2, page 4. After boot up, any I/O pins can be used by any cogs at any time. It is up to the application developer to ensure that no two cogs try to use the same I/O pin for different purposes during run time.

Each cog has its own 32-bit I/O Direction Register and 32-bit I/O Output Register. The state of each cog's Direction Register is OR'd with that of the previous cogs' Direction Registers, and each cog's output states is OR'd with that of the previous cogs' output states. Note that each cog's output states are made up of the OR'd states of its internal I/O hardware and that is all AND'd with its Direction Register's states. The result is that each I/O pin's direction and output state is the "wired-OR" of the entire cog collective. No electrical contention between cogs is possible, yet they can all still access the I/O pins simultaneously. The result of this I/O pin wiring configuration can be described in the following rules:

- A. A pin is an input <u>only</u> if no active cog sets it to an output.

- B. A pin outputs low <u>only</u> if all active cogs that set it to output also set it to low.

- C. A pin outputs high if <u>any</u> active cog sets it to an output and also sets it high.

Table 3 demonstrates a few possible combinations of the collective cogs' influence on a particular I/O pin, P12 in this example. For simplification, these examples assume that bit 12 of each cog's I/O hardware, other than its I/O Output Register, is cleared to zero (0).

Any cog that is shut down has its Direction Register and output states cleared to zero, effectively removing it from influencing the final state of the I/O pins that the remaining active cogs are controlling.

Each cog also has its own 32-bit Input Register. This input register is really a pseudo-register; every time it is read, the actual states of the I/O pins are read, regardless of their input or output direction.

|           | Table 3: I/O Sharing Examples          |  |   |   |          |     |     |       |            |     |     |          |          |      |   |   |   |             |          |

|-----------|----------------------------------------|--|---|---|----------|-----|-----|-------|------------|-----|-----|----------|----------|------|---|---|---|-------------|----------|

|           | Bit 12 of Cogs' I/O Direction Register |  |   |   | Bit 12 o | f C | ogs | ' I/C | <b>O</b> C | utp | out | Register | State of | Rule |   |   |   |             |          |

| Cog ID    | 0                                      |  | 1 | 2 | 3        | 4   | 5   | 6     | 7          | 0   | 1   | 2        | 3        | 4    | 5 | 6 | 7 | I/O Pin P12 | Followed |

| Example 1 | 0                                      |  | 0 | 0 | 0        | 0   | 0   | 0     | 0          | 0   | 0   | 0        | 0        | 0    | 0 | 0 | 0 | Input       | А        |

| Example 2 | 1                                      |  | 0 | 0 | 0        | 0   | 0   | 0     | 0          | 0   | 0   | 0        | 0        | 0    | 0 | 0 | 0 | Output Low  | В        |

| Example 3 | 1                                      |  | 0 | 0 | 0        | 0   | 0   | 0     | 0          | 1   | 0   | 0        | 0        | 0    | 0 | 0 | 0 | Output High | С        |

| Example 4 | 1                                      |  | 0 | 0 | 0        | 0   | 0   | 0     | 0          | 0   | 1   | 0        | 0        | 0    | 0 | 0 | 0 | Output Low  | В        |

| Example 5 | 1                                      |  | 1 | 0 | 0        | 0   | 0   | 0     | 0          | 0   | 1   | 0        | 0        | 0    | 0 | 0 | 0 | Output High | С        |

| Example 6 | 1                                      |  | 1 | 1 | 1        | 1   | 1   | 1     | 1          | 0   | 1   | 0        | 1        | 0    | 0 | 0 | 0 | Output High | С        |

| Example 7 | 1                                      |  | 1 | 1 | 1        | 1   | 1   | 1     | 1          | 0   | 0   | 0        | 1        | 0    | 0 | 0 | 0 | Output High | С        |

| Example 8 | 1                                      |  | 1 | 1 | 0        | 1   | 1   | 1     | 1          | 0   | 0   | 0        | 1        | 0    | 0 | 0 | 0 | Output Low  | В        |

Note: For the I/O Direction Register, a 1 in a bit location sets the corresponding I/O pin to the output direction; a 0 sets it to an input direction.

#### 4.6. System Counter

The System Counter is a global, read-only, 32-bit counter that increments once every System Clock cycle. Cogs can read the System Counter (via their CNT registers, see Table 15 on page 15) to perform timing calculations and can use the WAITCNT command (see section 6.3 on page 18 and section 6.4 on page 21) to create effective delays within their processes. The System Counter is a common resource which every cog can read simultaneously. The System Counter is not cleared upon startup since its practical use is for differential timing. If a cog needs to keep track of time from a specific, fixed moment in time, it simply needs to read and save the initial counter value at that moment in time, and compare subsequent counter values against that initial value.

#### 4.7. Locks

There are eight lock bits (semaphores) available to facilitate exclusive access to user-defined resources among multiple cogs. If a block of memory is to be used by two or more cogs at once and that block consists of more than one long (four bytes), the cogs will each have to perform multiple reads and writes to retrieve or update that memory block. This leads to the likely possibility of read/write contention on that memory block where one cog may be writing while another is reading, resulting in misreads and/or miswrites.

The locks are global bits accessed through the Hub via LOCKNEW, LOCKRET, LOCKSET, and LOCKCLR. Because locks are accessed only through the Hub, only one cog at a time can affect them, making this an effective control mechanism. The Hub maintains an inventory of which locks are in use and their current states; cogs can check out, return, set, and clear locks as needed during run time.

#### 4.8. Cog Counters

Each cog has two counter modules: CTRA and CTRB. Each counter module can control or monitor up to two I/O pins and perform conditional 32-bit accumulation of its FRQ register into its PHS register on every clock cycle.

Each counter module also has its own phase-locked loop (PLL) which can be used to synthesize frequencies up to 128 MHz.

With a little setup or oversight from the cog, a counter can be used for:

- frequency synthesis

- frequency measurement

- pulse counting

- pulse measurement

- multi-pin state measurement

- pulse-width modulation

- duty-cycle measurement

- digital-to-analog conversion

- analog-to-digital conversion

For some of these operations, the cog can be set up and left in a free-running mode. For others, it may use WAITCNT to time-align counter reads and writes within a loop, creating the effect of a more complex state machine.

Note that for a cog clock frequency of 80 MHz, the counter update period is a mere 12.5 ns. This high speed, combined with 32-bit precision, allows for very dynamic signal generation and measurement.

The design goal for the counter was to create a simple and flexible subsystem which could perform some repetitive task on every clock cycle, thereby freeing the cog to perform some computationally richer super-task. While the counters have only 32 basic operating modes, there is no limit to how they might be used dynamically through software. Integral to this concept is the use of the WAITPEQ, WAITPNE, and WAITCNT instructions, which can event-align or time-align a cog with its counters.

Each counter has three registers:

#### 4.8.1. CTRA / CTRB – Control register

The CTR (CTRA and CTRB) register selects the counter's operating mode. As soon as this register is written, the new operating mode goes into effect. Writing a zero to CTR will immediately disable the counter, stopping all pin output and PHS accumulation.

|    | Table 4: CTRA and CTRB Registers |        |   |      |   |      |  |  |  |

|----|----------------------------------|--------|---|------|---|------|--|--|--|

| 31 | 3026 2523 2215 149 86 50         |        |   |      |   |      |  |  |  |

| -  | CTRMODE                          | PLLDIV | - | BPIN | - | APIN |  |  |  |

The CTRMODE field selects one of 32 operating modes for the counter, conveniently written (along with PLLDIV) using the MOVI instruction. These modes of operation are listed in Table 6 on page 10.

|        | Table 5: PLLDIV Field |                  |           |                  |                 |          |          |                 |  |  |

|--------|-----------------------|------------------|-----------|------------------|-----------------|----------|----------|-----------------|--|--|

| PLLDIV | %000                  | %001             | %010      | %011             | %100            | %101     | %110     | %111            |  |  |

| Output | <u>VCO</u><br>128     | <u>VCO</u><br>64 | VCO<br>32 | <u>VCO</u><br>16 | <u>VCO</u><br>8 | VCO<br>4 | VCO<br>2 | <u>VCO</u><br>1 |  |  |

PLLDIV selects a PLL output tap and may be ignored if not used.

The PLL modes (%00001 to %00011) cause FRQ-to-PHS accumulation to occur every clock cycle. This creates a numerically-controlled oscillator (NCO) in PHS[31], which feeds the counter PLL's reference input. The PLL will multiply this frequency by 16 using its voltage-controlled oscillator (VCO). For stable operation, it is recommended that the VCO frequency be kept within 64 MHz to 128 MHz. This translates to an NCO frequency of 4 MHz to 8 MHz.

The PLLDIV field of the CTR register selects which power-of-two division of the VCO frequency will be used as the final PLL output. This affords a PLL range of 500 kHz to 128 MHz.

BPIN selects a pin to be the secondary I/O. It may be ignored if not used and may be written using the MOVD instruction.

APIN selects a pin to be the primary I/O. It may be ignored if not used and may be written using the MOVS instruction.

#### 4.8.2. FRQA / FRQB – Frequency register

FRQ (FRQA and FRQB) holds the value that will be accumulated into the PHS register. For some applications, FRQ may be written once, and then ignored. For others, it may be rapidly modulated.

#### 4.8.3. PHSA / PHSB – Phase register

The PHS (PHSA and PHSB) register can be written and read via cog instructions, but it also functions as a free-running accumulator, summing the FRQ register into itself on potentially every clock cycle. Any instruction writing to PHS will override any accumulation for that clock cycle. PHS can only be read through the source operand (same as PAR, CNT, INA, and INB). Beware that doing a read-modify-write instruction on PHS, like "ADD PHSA, #1", will cause the last-written value to be used as the destination operand input, rather than the current accumulation.

| T                                                        | Table 6: Counter Modes (C                                                             | TRMODE Field Va                                                                                                                                      | ilues)                   |                       |

|----------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------|

| CTRMODE                                                  | Description                                                                           | Accumulate FRQx to PHSx                                                                                                                              | APIN<br>Output*          | BPIN<br>Output*       |

| %00000                                                   | Counter disabled (off)                                                                | 0 (never)                                                                                                                                            | 0 (none)                 | 0 (none)              |

| %00001<br>%00010<br>%00011                               | PLL internal (video mode) PLL single-ended PLL differential                           | 1 (always)<br>1<br>1                                                                                                                                 | 0<br>PLLx<br>PLLx        | 0<br>0<br>!PLLx       |

| %00100<br>%00101                                         | NCO single-ended<br>NCO differential                                                  | 1                                                                                                                                                    | PHSx[31]<br>PHSx[31]     | 0<br>!PHSx[31]        |

| %00110<br>%00111                                         | DUTY single-ended<br>DUTY differential                                                | 1                                                                                                                                                    | PHSx-Carry<br>PHSx-Carry | 0<br>!PHSx-Carry      |

| %01000<br>%01001<br>%01010<br>%01011                     | POS detector POS detector with feedback POSEDGE detector POSEDGE detector w/ feedback | A <sup>1</sup><br>A <sup>1</sup><br>A <sup>1</sup> & !A <sup>2</sup><br>A <sup>1</sup> & !A <sup>2</sup>                                             | 0<br>0<br>0<br>0         | 0<br>!A1<br>0<br>!A1  |

| %01100<br>%01101<br>%01110<br>%01111                     | NEG detector NEG detector with feedback NEGEDGE detector NEGEDGE detector w/ feedback | !A <sup>1</sup><br>!A <sup>1</sup><br>!A <sup>1</sup> & A <sup>2</sup><br>!A <sup>1</sup> & A <sup>2</sup>                                           | 0<br>0<br>0              | 0<br>!A1<br>0<br>!A1  |

| %10000<br>%10001<br>%10010<br>%10011<br>%10100<br>%10101 | LOGIC never<br>LOGIC !A & !B<br>LOGIC A & !B<br>LOGIC !B<br>LOGIC !A & B<br>LOGIC !A  | 0<br>!A <sup>1</sup> & !B <sup>1</sup><br>A <sup>1</sup> & !B <sup>1</sup><br>!B <sup>1</sup><br>!A <sup>1</sup> & B <sup>1</sup><br>!A <sup>1</sup> | 0<br>0<br>0<br>0<br>0    | 0<br>0<br>0<br>0<br>0 |

| %10110<br>%10111<br>%11000<br>%11001                     | LOGIC A <> B<br>LOGIC !A   !B<br>LOGIC A & B<br>LOGIC A == B                          | $A^{1} <> B^{1}$<br>$ A^{1}   B^{1}$<br>$A^{1} & B^{1}$<br>$A^{1} == B^{1}$                                                                          | 0<br>0<br>0              | 0<br>0<br>0           |

| %11010<br>%11011<br>%11100<br>%11101                     | LOGIC A LOGIC A   !B LOGIC B LOGIC !A   B                                             | A <sup>1</sup>   !B <sup>1</sup>   B <sup>1</sup>   !A <sup>1</sup>   B <sup>1</sup>                                                                 | 0<br>0<br>0              | 0<br>0<br>0           |

| %11110<br>%11111                                         | LOGIC A   B<br>LOGIC always                                                           | A <sup>1</sup>   B <sup>1</sup>                                                                                                                      | 0                        | 0 0                   |

\*Must set corresponding DIR bit to affect pin. A1 = APIN input delayed by 1 clock. A2 = APIN input delayed by 2 clocks. B1 = BPIN input delayed by 1 clock.

#### 4.9. Video Generator

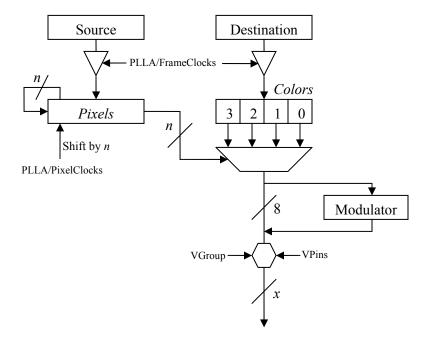

Each cog has a video generator module that facilitates transmitting video image data at a constant rate. There are two registers and one instruction which provide control and access to the video generator. Counter A of the cog must be running in a PLL mode and is used to generate the timing signal for the Video Generator. The Video Scale Register specifies the number of Counter A PLL (PLLA) clock cycles for each pixel and number of clock cycles before fetching another frame of data provided by the WAITVID instruction which is executed within the cog. The Video Configuration Register establishes the mode the Video Generator should operate, and can generate VGA or composite video (NTSC or PAL).

The Video Generator should be initialized by first starting Counter A, setting the Video Scale Register, setting the Video Configuration Register, then finally providing data via the WAITVID instruction. Failure to properly initialize the Video Generator by first starting PLLA will cause the cog to indefinitely hang when the WAITVID instruction is executed.

#### 4.9.1. VCFG - Video Configuration Register

The Video Configuration Register contains the configuration settings of the video generator and is shown in Table 7.

In Propeller Assembly, the VMode through AuralSub fields can conveniently be written using the MOVI instruction, the VGroup field can be written with the MOVD instruction, and the VPins field can be written with the MOVS instruction.

| Table 7: VCFG Register |       |       |         |         |          |      |        |   |       |

|------------------------|-------|-------|---------|---------|----------|------|--------|---|-------|

|                        |       |       |         |         |          |      |        |   |       |

| 31                     | 3029  | 28    | 27      | 26      | 2523     | 2212 | 119    | 8 | 70    |

| -                      | VMode | CMode | Chroma1 | Chroma0 | AuralSub | -    | VGroup | - | VPins |

The 2-bit VMode (video mode) field selects the type and orientation of video output, if any, according to Table 8.

|       | Table 8: The Video Mode Field                                   |

|-------|-----------------------------------------------------------------|

| VMode | Video Mode                                                      |

| 00    | Disabled, no video generated.                                   |

| 01    | VGA mode; 8-bit parallel output on VPins 7:0                    |

| 10    | Composite Mode 1; broadcast on VPins 7:4, baseband on VPins 3:0 |

| 11    | Composite Mode 2; baseband on VPins 7:4, broadcast on VPins 3:0 |

The CMode (color mode) field selects two or four color mode. 0 = two-color mode; pixel data is 32 bits by 1 bit and only colors 0 or 1 are used. 1 = four-color mode; pixel data is 16 bits by 2 bits, and colors 0 through 3 are used.

The Chromal (broadcast chroma) bit enables or disables chroma (color) on the broadcast signal. 0 = disabled, 1 = enabled.

The Chroma0 (baseband chroma) bit enables or disables chroma (color) on the baseband signal. 0 = disabled, 1 = enabled.

The AuralSub (aural sub-carrier) field selects the source of the FM aural (audio) sub-carrier frequency to be modulated on. The source is the PLLA of one of the cogs, identified by AuralSub's value. This audio must already be modulated onto the 4.5 MHz sub-carrier by the source PLLA.

| Tab      | Table 9: The AuralSub Field  |  |  |  |  |  |  |

|----------|------------------------------|--|--|--|--|--|--|

| AuralSub | Sub-Carrier Frequency Source |  |  |  |  |  |  |

| 000      | Cog 0's PLLA                 |  |  |  |  |  |  |

| 001      | Cog 1's PLLA                 |  |  |  |  |  |  |

| 010      | Cog 2's PLLA                 |  |  |  |  |  |  |

| 011      | Cog 3's PLLA                 |  |  |  |  |  |  |

| 100      | Cog 4's PLLA                 |  |  |  |  |  |  |

| 101      | Cog 5's PLLA                 |  |  |  |  |  |  |

| 110      | Cog 6's PLLA                 |  |  |  |  |  |  |

| 111      | Cog 7's PLLA                 |  |  |  |  |  |  |

The VGroup (video output pin group) field selects which group of 8 I/O pins to output video on.

|         | Table 10: The VGroup Field                    |  |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|--|

| VGroup  | Pin Group                                     |  |  |  |  |  |

| 000     | Group 0: P7P0                                 |  |  |  |  |  |

| 001     | Group 1: P15P8                                |  |  |  |  |  |

| 010     | Group 2: P23P16                               |  |  |  |  |  |

| 011     | Group 3: P31P24                               |  |  |  |  |  |

| 100-111 | <reserved for="" future="" use=""></reserved> |  |  |  |  |  |

The VPins (video output pins) field is a mask applied to the pins of VGroup that indicates which pins to output video signals on.

|          | Table 11: The VPins Field                                                |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| VPins    | Effect                                                                   |  |  |  |  |  |  |

| 00001111 | Drive Video on lower 4 pins only; composite                              |  |  |  |  |  |  |

| 11110000 | Drive Video on upper 4 pins only; composite                              |  |  |  |  |  |  |

| 11111111 | Drive video on all 8 pins; VGA                                           |  |  |  |  |  |  |

| XXXXXXX  | Any value is valid for this field; the above values are the most common. |  |  |  |  |  |  |

#### 4.9.2. VSCL - Video Scale Register

The Video Scale Register sets the rate at which video data is generated, and is shown in Table 12.

| Table 12: VSCL Register |             |             |  |  |  |  |  |

|-------------------------|-------------|-------------|--|--|--|--|--|

|                         | VSCL Bits   |             |  |  |  |  |  |

| 3120                    | 1912        | 110         |  |  |  |  |  |

| -                       | PixelClocks | FrameClocks |  |  |  |  |  |

The 8-bit PixelClocks field indicates the number of clocks per pixel; the number of clocks that should elapse before each pixel is shifted out by the video generator module. These clocks are the PLLA clocks, not the System Clock. A value of 0 for this field is interpreted as 256.

The 12-bit FrameClocks field indicates the number of clocks per frame; the number of clocks that will elapse before each frame is shifted out by the video generator module. These clocks are the PLLA clocks, not the System Clock. A frame is one long of pixel data (delivered via the WAITVID command). Since the pixel data is either 16 bits by 2 bits, or 32 bits by 1 bit (meaning 16 pixels wide with 4 colors, or 32 pixels wide with 2 colors, respectively), the FrameClocks is typically 16 or 32 times that of the PixelClocks value. A value of 0 for this field is interpreted as 4096.

#### 4.9.3. WAITVID Command/Instruction

The WAITVID instruction is the delivery mechanism for data to the cog's Video Generator hardware. Since the Video Generator works independently from the cog itself, the two must synchronize each time data is needed for the display device. The frequency at which this occurs is dictated by the frequency of PLLA and the Video Scale Register. The cog must have new data available before the moment the Video Generator needs it. The cog uses WAITVID to wait for the right time and then "hand off" this data to the Video Generator.

Two longs of data are passed to the Video Generator by with the syntax WAITVID Colors, Pixels.

The *Colors* parameter is a 32-bit value containing either four 8-bit color values (for 4 color mode) or two 8-bit color values in the lower 16 bits (for 2 color mode). For

VGA mode, each 8-bit color value is written to the pins specified by the VGroup and VPins field. For VGA typically the 8 bits are grouped into 2 bits per primary color and Horizontal and Vertical Sync control lines, but this is up to the software and application of how these bits are used. For composite video each 8-bit color value is composed of 3 fields. Bits 0-2 are the luminance value of the generated signal. Bit 3 is the modulation bit which dictates whether the chroma information will be generated and bits 4-7 indicate the phase angle of the chroma value. When the modulation bit is set to 0, the chroma information is ignored and only the luminance value is output to pins. When the modulation bit is set to 1 the luminance value is modulated  $\pm 1$  with a phase angle set by bits 4-7. In order to achieve the full resolution of the chroma value, PLLA should be set to 16 times the modulation frequency (in composite video this is called the color-burst frequency). The PLLB of the cog is used to generate the broadcast frequency; whether this is generated depends on if PLLB is running and the values of VMode and VPins.

The *Pixels* parameter describes the pixel pattern to display, either 16 pixels or 32 pixels depending on the color depth configuration of the Video Generator. When four-color mode is specified, *Pixels* is a 16x2 bit pattern where each 2-bit pixel is an index into *Colors* on which data pattern should be presented to the pins. When two-color mode is specified, *Pixels* is a 32x1 bit pattern where each bit specifies which of the two color patterns in the lower 16 bits of *Colors* should be output to the pins. The Pixel data is shifted out least significant bits (LSB) first.

When the FrameClocks value is greater than 16 times the PixelClocks value and 4-color mode is specified, the two most significant bits are repeated until FrameClocks PLLA cycles have occurred. When FrameClocks value is greater than 32 times PixelClocks value and 2-color mode is specified, the most significant bit is repeated until FrameClocks PLLA cycles have occurred. When FrameClocks cycles occur and the cog is not in a WAITVID instruction, whatever data is on the source and destination busses at the time will be fetched and used. So it is important to be in a WAITVID instruction before this occurs.

While the Video Generator was created to display video signals, its potential applications are much more diverse. The Composite Video mode can be used to generate phase-shift keying communications of a granularity of 16 or less and the VGA mode can be used to generate any bit pattern with a fully settable and predictable rate.

Figure 4 is a block diagram of how the VGA mode is organized. The two inverted triangles are the load mechanism for *Pixels* and *Colors; n* is 1 or 2 bits depending on the value of CMode. The inverted trapezoid is a 4-way 8-bit multiplexer that chooses which byte of *Colors* to output. When in composite video mode the Modulator transforms the byte into the luminance and chroma signal and outputs the broadcast signal. VGroup steers the 8 bits to a block of output pins and outputs to those pins which are set to 1 in VPins; this combined functionality is represented by the hexagon.

Figure 4: Video Generator

### 4.10. CLK Register

The CLK register is the System Clock configuration control; it determines the source and characteristics of the System Clock. It configures the RC Oscillator, Clock PLL, Crystal Oscillator, and Clock Selector circuits (See the Block Diagram, page 1). It is configured at compile time by the \_CLKMODE declaration and is writable at run time through the CLKSET command. Whenever the CLK register is written, a global delay of ~75  $\mu s$  occurs as the clock source transitions.

Whenever this register is changed, a copy of the value written should be placed in the Clock Mode value location (which is BYTE[4] in Main RAM) and the resulting master clock frequency should be written to the Clock Frequency value location (which is LONG[0] in Main RAM) so that objects which reference this data will have current information for their timing calculations.

Use Spin's **CLKSET** command when possible (see sections 6.3 and 6.4) since it automatically updates all the abovementioned locations with the proper information.

| T                                                                                       | Table 13: Valid Clock Modes                                                  |                                                                                    |                                                                              |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| Valid Expression                                                                        | CLK Reg. Value                                                               | Valid Expression                                                                   | CLK Reg. Value                                                               |  |  |  |  |  |  |

| RCFAST                                                                                  | 0_0_0_00_000                                                                 | XTAL1 + PLL1X<br>XTAL1 + PLL2X                                                     | 0_1_1_01_011<br>0 1 1 01 100                                                 |  |  |  |  |  |  |

| RCSLOW                                                                                  | 0_0_0_00_001                                                                 | XTAL1 + PLL4X<br>XTAL1 + PLL4X                                                     | 0_1_1_01_101<br>0_1_1_01_101<br>0_1_1_01_110                                 |  |  |  |  |  |  |

| XINPUT                                                                                  | 0_0_1_00_010                                                                 | XTAL1 + PLL16X                                                                     | 0_1_1_01_111                                                                 |  |  |  |  |  |  |

| XTAL1<br>XTAL2<br>XTAL3                                                                 | 0_0_1_01_010<br>0_0_1_10_010<br>0_0_1_11_010                                 | XTAL2 + PLL1X<br>XTAL2 + PLL2X<br>XTAL2 + PLL4X<br>XTAL2 + PLL8X<br>XTAL2 + PLL16X | 0_1_1_10_011<br>0_1_1_10_100<br>0_1_1_10_101<br>0_1_1_10_110<br>0_1_1_10_111 |  |  |  |  |  |  |

| XINPUT + PLL1X<br>XINPUT + PLL2X<br>XINPUT + PLL4X<br>XINPUT + PLL8X<br>XINPUT + PLL16X | 0_1_1_00_011<br>0_1_1_00_100<br>0_1_1_00_101<br>0_1_1_00_110<br>0_1_1_00_111 | XTAL3 + PLL1X<br>XTAL3 + PLL2X<br>XTAL3 + PLL4X<br>XTAL3 + PLL8X<br>XTAL3 + PLL16X | 0_1_1_11_011<br>0_1_1_11_100<br>0_1_1_11_101<br>0_1_1_11_110<br>0_1_1_11_111 |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            | Table 14        | : CLK Regist | er Fields     |                                   |                  |                |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------|--------------|---------------|-----------------------------------|------------------|----------------|--|--|--|--|

| Bit     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6                                                          | 5               | 4            | 3             | 2                                 | 1                | 0              |  |  |  |  |

| Name    | RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PLLENA                                                     | OSCENA          | OSCM1        | OSCM2         | CLKSEL2                           | CLKSEL1          | CLKSEL0        |  |  |  |  |

| RESET   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |                 | Eff          | ect           |                                   |                  |                |  |  |  |  |

| 0       | Always write '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Always write '0' here unless you intend to reset the chip. |                 |              |               |                                   |                  |                |  |  |  |  |

| 1       | Same as a har                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dware reset – re                                           | boots the chip. |              |               |                                   |                  |                |  |  |  |  |

| PLLENA  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                            |                 | Eff          | ect           |                                   |                  |                |  |  |  |  |

| 0       | Disables the Pl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LL circuit.                                                |                 |              |               |                                   |                  |                |  |  |  |  |

| 1       | Enables the PLL circuit. The PLL internally multiplies the XIN pin frequency by 16. OSCENA must be '1' to propagate the XIN signal to the PLL. The PLL's internal frequency must be kept within 64 MHz to 128 MHz – this translates to an XIN frequency range of 4 MHz to 8 MHz. Allow 100 µs for the PLL to stabilize before switching to one of its outputs via the CLKSEL bits. Once the OSC and PLL circuits are enabled and stabilized, you can switch freely among all clock sources by changing the CLKSEL bits.               |                                                            |                 |              |               |                                   |                  |                |  |  |  |  |

| OSCENA  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Effect                                                     |                 |              |               |                                   |                  |                |  |  |  |  |

| 0       | Disables the O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                            |                 |              |               |                                   |                  |                |  |  |  |  |

| 1       | Enables the OSC circuit so that a clock signal can be input to XIN, or so that XIN and XOUT can function together as a feedback oscillator. The OSCM bits select the operating mode of the OSC circuit. Note that no external resistors or capacitors are required for crystals and resonators. Allow a crystal or resonator 10 ms to stabilize before switching to an OSC or PLL output via the CLKSEL bits. When enabling the OSC circuit, the PLL may be enabled at the same time so that they can share the stabilization period. |                                                            |                 |              |               |                                   |                  |                |  |  |  |  |

| OSCM1   | OSCM2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XOUT Re                                                    | sistance        | XIN and XOU  | Γ Capacitance | F                                 | requency Rang    | je             |  |  |  |  |

| 0       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Infi                                                       | nite            | 6 pF (p      | ad only)      | DC to 80 MHz Input                |                  |                |  |  |  |  |

| 0       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 200                                                        | 0 Ω             | 36           | pF            | 4 MHz to 16 MHz Crystal/Resonator |                  |                |  |  |  |  |

| 1       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 100                                                        | 0 Ω             | 26           | pF            | 8 MHz to 32 MHz Crystal/Resonator |                  |                |  |  |  |  |

| 1       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 500                                                        | Ω Ω             | 16           | pF            | 20 MHz to 60 N                    | /IHz Crystal/Res | onator         |  |  |  |  |

| CLKSEL2 | CLKSEL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CLKSEL0                                                    | Master          | Clock        | Source        | Notes                             |                  |                |  |  |  |  |

| 0       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                          | ~12             | MHz          | Internal      | No external par                   | ts (8 to 20 MHz) | )              |  |  |  |  |

| 0       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                          | ~20             | kHz          | Internal      | No external par                   | ts, very low pow | er (13-33 kHz) |  |  |  |  |

| 0       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                          | X               | IN           | OSC           | OSCENA must be '1'                |                  |                |  |  |  |  |

| 0       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                          | XIN             | × 1          | OSC+PLL       | OSCENA and F                      | PLLENA must be   | e '1'          |  |  |  |  |

| 1       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                          | XIN             | × 2          | OSC+PLL       | OSCENA and F                      | e '1'            |                |  |  |  |  |

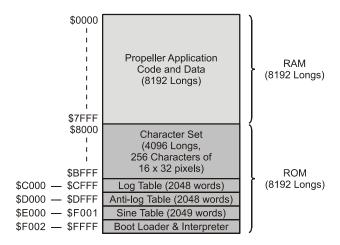

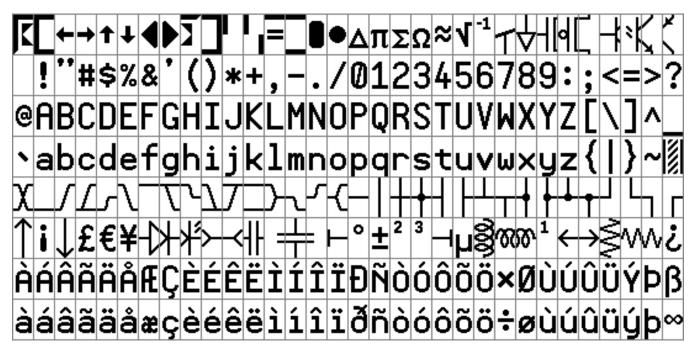

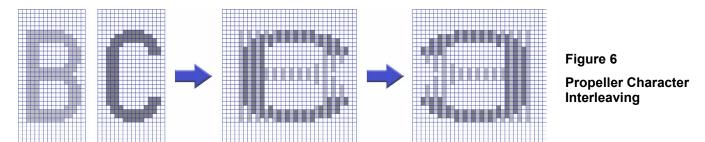

| 1       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                          | XIN             | × 4          | OSC+PLL       | OSCENA and F                      | PLLENA must be   | e '1'          |  |  |  |  |